Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19155-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Complementary Waveform Generator (CWG):

- Rising and falling edge dead-band control

- Full-bridge, half-bridge, 1-channel drive

Multiple signal sources

- Two Capture/Compare/PWM (CCP) module

- Two 10-Bit PWMs

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Communication:

- Two EUSART, RS-232, RS-485, LIN compatible

- One SPI/I<sup>2</sup>C, SMBus, PMBus™ compatible

- Up to 43 I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Input level selection control (ST or TTL)

- Digital open-drain enable

### Analog Peripherals

- Analog-to-Digital Converter with Computation (ADC<sup>2</sup>):

- 12-bit with up to 39 external channels

- Automates math functions on input signals: averaging, filter calculations, oversampling and threshold comparison

- Conversion available during Sleep

- Two Comparators:

- (1) Low-Power Clocked Comparator

- (1) High-Speed Comparator

- Fixed Voltage Reference at (non)inverting input(s)

- Comparator outputs externally accessible

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

- Zero-Cross Detect Module:

- AC high-voltage zero-crossing detection for simplifying TRIAC control

- Synchronized switching control and timing

#### **Flexible Oscillator Structure**

- High-Precision Internal Oscillator:

- Active Clock Tuning of HFINTOSC over voltage and temperature (ACT)

- Selectable frequency range up to 32 MHz ±1% typical

- x2/x4 PLL with Internal and External Sources

- Low-Power Internal 31 kHz Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- Oscillator Start-up Timer (OST)Ensures stability of crystal oscillator source

- External Oscillator Block with:

- Three external clock modes up to 32 MHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripherals clock stops

#### 8.15 Power Control (PCON) Registers

The Power Control (PCON) registers contain flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Timer Window Violation Reset

(WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

- VBAT Reset (VBATBOR)

The PCON0 register bits are shown in Register 8-2.

The PCON1 register bits are shown in Register 8-3.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no reset action will be generated.

All bits in PCON1 and PCON0 will maintain their state when either VDD or VBAT is powered.

# PIC16(L)F19155/56/75/76/85/86

| R/W-0/0                                                                                                                                                                                                                      | R/W-0/0                                                                                                                                                                                      | R/W-0/0                                               | R/W-0/0 | R/W-0/0        | R/W-0/0          | U-0              | U-0          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|----------------|------------------|------------------|--------------|

| EXTOEN                                                                                                                                                                                                                       | HFOEN                                                                                                                                                                                        | MFOEN                                                 | LFOEN   | SOSCEN         | ADOEN            | _                | _            |

| bit 7                                                                                                                                                                                                                        |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

|                                                                                                                                                                                                                              |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

| Legend:                                                                                                                                                                                                                      |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

| R = Readable                                                                                                                                                                                                                 | bit                                                                                                                                                                                          | W = Writable                                          | bit     | U = Unimpler   | mented bit, read | d as '0'         |              |

| u = Bit is unch                                                                                                                                                                                                              | anged                                                                                                                                                                                        | x = Bit is unkr                                       | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                                                                                                                             |                                                                                                                                                                                              | '0' = Bit is clea                                     | ared    |                |                  |                  |              |

| <ul> <li>bit 7</li> <li>EXTOEN: External Oscillator Manual Request Enable bit</li> <li>1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC</li> <li>0 = EXTOSC could be enabled by another module</li> </ul> |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

| bit 6                                                                                                                                                                                                                        | bit 6 <b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit<br>1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ<br>0 = HFINTOSC could be enabled by another module |                                                       |         |                |                  |                  |              |

| bit 5                                                                                                                                                                                                                        | 1 = MFINTC                                                                                                                                                                                   | NTOSC Oscilla<br>SC is explicitly<br>SC could be e    | enabled |                | bit              |                  |              |

| bit 4 LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit<br>1 = LFINTOSC is explicitly enabled<br>0 = LFINTOSC could be enabled by another module                                                                 |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

| bit 3 <b>SOSCEN:</b> Secondary (Timer1) Oscillator Manual Request bit<br>1 = Secondary oscillator is explicitly enabled, operating as specified by SOSCPWR<br>0 = Secondary oscillator could be enabled by another module    |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

| bit 2                                                                                                                                                                                                                        | 1 = FRC is e                                                                                                                                                                                 | COscillator Ma<br>explicitly enable<br>uld be enabled | ed      |                |                  |                  |              |

| bit 1-0                                                                                                                                                                                                                      |                                                                                                                                                                                              |                                                       |         |                |                  |                  |              |

#### **REGISTER 9-5:** OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|-----|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | —   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         | •   |         | •       |         |         | bit 0   |

|         |         |     |         |         |         |         |         |

| Legend: |         |     |         |         |         |         |         |

#### REGISTER 14-3: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 LATA<7:6>: RA<7:6> Output Latch Value bit | s <sup>(1)</sup> |

|---------------------------------------------------|------------------|

|---------------------------------------------------|------------------|

bit 5 **Unimplemented:** Read as '0'

bit 4-0 LATA<4:0>: RA<4:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 14-4: ANSELA: PORTA ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| ANSA7   | ANSA6   | —   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ANSA<7:6>**: Analog Select between Analog or Digital Function on pins RA<7:6>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

bit 5 Unimplemented: Read as '0'

bit 4-0 **ANSA<4:0>**: Analog Select between Analog or Digital Function on pins RA<4:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

### **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 229                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 229                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 230                 |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 230                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 231                 |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 231                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 232                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 232                 |

| HIDRVB  | _       | _       |         | —       | —       | —       | HIDB1   | —       | 232                 |

#### TABLE 14-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

#### 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. An output of 3.072V is also available as a voltage source to drive the LCD segments. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator positive and negative input

- 5-Bit Digital-to-Analog Converter (DAC1)

- · LCD Voltage Source to drive the LCD segments

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

#### 18.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. In addition, a 3x mode is also available to run the LCD module. The user must set the FVREN bit of the FVRCON register along with setting the LCD, LCDVSRC<3:0> of the LCDVCON2 register to 0b0011.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 19.0 "Analog-to-Digital Converter with Computation (ADC2) Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 22.0 "Comparator Module" for additional information.

#### 18.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. If an LF device, or the BOR enabled then FVRRDY will be high prior to setting FVREN as those module require the reference voltage.

#### 18.3 Register Definitions: FVR Control

#### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFVI   | R<1:0>  |

| bit 7   |                       |                     |                      |             |         |         | bit 0   |

| Legend:                   | abla bit                                                                                                                                                                                                                                       |                                                                                                                                                                     | $11 - 11$ minutes and a bit $r_{2} = 1 - 1 - 1$                                              |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| R = Read                  |                                                                                                                                                                                                                                                | W = Writable bit                                                                                                                                                    | U = Unimplemented bit, read as '0'                                                           |  |  |  |

|                           | unchanged                                                                                                                                                                                                                                      | x = Bit is unknown                                                                                                                                                  | -n/n = Value at POR and BOR/Value at all other Resets                                        |  |  |  |

| '1' = Bit is              | set                                                                                                                                                                                                                                            | '0' = Bit is cleared                                                                                                                                                | q = Value depends on condition                                                               |  |  |  |

| bit 7                     | 1 = Fixed                                                                                                                                                                                                                                      | ixed Voltage Reference Enal<br>Voltage Reference is enable<br>Voltage Reference is disable                                                                          | d <sup>(4)</sup>                                                                             |  |  |  |

| bit 6                     | 1 = Fixed                                                                                                                                                                                                                                      | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                            | ready for use                                                                                |  |  |  |

| bit 5                     | 1 = Temp                                                                                                                                                                                                                                       | nperature Indicator Enable b<br>erature Indicator is enabled<br>erature Indicator is disabled                                                                       | it <sup>(3)</sup>                                                                            |  |  |  |

| bit 4                     | 1 = Temp                                                                                                                                                                                                                                       | emperature Indicator Range<br>erature in High Range<br>erature in Low Range                                                                                         | Selection bit <sup>(3)</sup>                                                                 |  |  |  |

| bit 3-2                   | 11 = Com<br>10 = Com<br>01 = Com                                                                                                                                                                                                               | <b>C1:0&gt;:</b> Comparator FVR Buffer<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off | x, (4.096∨) <sup>(2)</sup><br>x, (2.048∨) <sup>(2)</sup>                                     |  |  |  |

| bit 1-0                   | <b>ADFVR&lt;1:0&gt;:</b> ADC FVR Buffer Gain Selection bit<br>11 = ADC FVR Buffer Gain is 4x, $(4.096V)^{(2)}$<br>10 = ADC FVR Buffer Gain is 2x, $(2.048V)^{(2)}$<br>01 = ADC FVR Buffer Gain is 1x, $(1.024V)$<br>00 = ADC FVR Buffer is off |                                                                                                                                                                     |                                                                                              |  |  |  |

| Note 1:<br>2:<br>3:<br>4: | Fixed Voltage F<br>See Section 20                                                                                                                                                                                                              | Reference output cannot exce                                                                                                                                        | 56/75/76/85/86 devices only.<br>eed VDD.<br><b>Module (TIM)"</b> for additional information. |  |  |  |

© 2017 Microchip Technology Inc.

#### REGISTER 19-30: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

| R-x      | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |

|----------|-----|-----|-----|-----|-----|-----|-------|

| ERR<7:0> |     |     |     |     |     |     |       |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:  |     |     |     |     |     |     |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 19-4 for more details.

#### REGISTER 19-31: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| LTH<15:8> |         |         |         |         |         |         |         |  |  |  |  |

| bit 7 bit |         |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **LTH<15:8>**: ADC Lower Threshold MSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 19-32: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| LTH<7:0> |         |         |         |         |         |         |         |  |  |  |  |

| bit 7    |         |         |         |         |         |         |         |  |  |  |  |

|          |         |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **LTH<7:0>**: ADC Lower Threshold LSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2017 Microchip Technology Inc.

PIC16(L)F19155/56/75/76/85/86

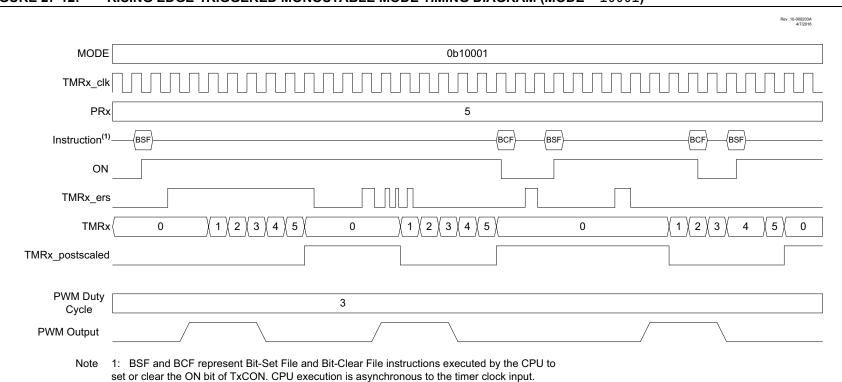

#### FIGURE 27-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

| <b>B</b> 44 6 15       | <b>B</b> 444 6 15                    | <b>D B B B B B B B B B B</b>                                                           | <b>B</b> # 4 / 6 / 7                                                                       | <b>B B B B B B B B B B</b>   | <b>D</b> # <b>M A</b> / <b>A</b> | <b>B</b> # 4 / 6 / 6 | <b>D M M M</b>   |  |  |  |

|------------------------|--------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------|----------------------------------|----------------------|------------------|--|--|--|

| R/W-0/0                | R/W-0/0                              | R/W-0/0                                                                                | R/W-0/0                                                                                    | R/W-0/0                      | R/W-0/0                          | R/W-0/0              | R/W-0/0          |  |  |  |

| PSYNC <sup>(1, 2</sup> | <sup>2)</sup> CKPOL <sup>(3)</sup>   | CKSYNC <sup>(4, 5)</sup>                                                               |                                                                                            | Ν                            | /IODE<4:0> <sup>(6, 7</sup>      | )                    |                  |  |  |  |

| bit 7                  |                                      |                                                                                        |                                                                                            |                              |                                  |                      | bit 0            |  |  |  |

|                        |                                      |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

| Legend:                |                                      |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

| R = Readab             | le bit                               | W = Writable b                                                                         | it                                                                                         | U = Unimplen                 | nented bit, read                 | l as '0'             |                  |  |  |  |

| u = Bit is un          | changed                              | x = Bit is unkno                                                                       | wn                                                                                         | -n/n = Value a               | at POR and BO                    | R/Value at all       | other Resets     |  |  |  |

| '1' = Bit is s         | et                                   | '0' = Bit is clear                                                                     | ed                                                                                         |                              |                                  |                      |                  |  |  |  |

|                        |                                      |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

| bit 7                  | PSYNC: Tim                           | ner2/4 Prescaler S                                                                     | Synchronizati                                                                              | on Enable bit <sup>(1,</sup> | 2)                               |                      |                  |  |  |  |

|                        |                                      | Prescaler Output is                                                                    |                                                                                            |                              |                                  |                      |                  |  |  |  |

|                        |                                      | Prescaler Output is                                                                    | •                                                                                          |                              |                                  |                      |                  |  |  |  |

| bit 6                  |                                      | ner2/4 Clock Pola                                                                      | •                                                                                          |                              |                                  |                      |                  |  |  |  |

|                        | Ų                                    | dge of input clock clocks timer/prescaler<br>dge of input clock clocks timer/prescaler |                                                                                            |                              |                                  |                      |                  |  |  |  |

|                        | •                                    | •                                                                                      |                                                                                            | •                            |                                  |                      |                  |  |  |  |

| bit 5                  |                                      | imer2/4 Clock Sy                                                                       |                                                                                            |                              |                                  |                      |                  |  |  |  |

|                        |                                      |                                                                                        | ter bit is synchronized to TMR2_clk input<br>ter bit is not synchronized to TMR2_clk input |                              |                                  |                      |                  |  |  |  |

| bit 4-0                | -                                    | : Timer2/4 Contro                                                                      |                                                                                            |                              |                                  |                      |                  |  |  |  |

| DIL 4-0                | See Table 27                         |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

|                        |                                      |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

|                        | •                                    | nsures that reading                                                                    | •                                                                                          |                              | alue.                            |                      |                  |  |  |  |

| 2:                     | When this bit is                     | '1', Timer2/4 canr                                                                     | not operate in                                                                             | Sleep mode.                  |                                  |                      |                  |  |  |  |

| 3:                     | CKPOL should r                       | not be changed w                                                                       | hile ON = 1.                                                                               |                              |                                  |                      |                  |  |  |  |

| 4:                     | Setting this bit e                   | nsures glitch-free                                                                     | operation wh                                                                               | nen the ON is e              | nabled or disab                  | led.                 |                  |  |  |  |

| 5:                     | When this bit is s                   | set then the timer of                                                                  | operation will                                                                             | be delayed by t              | wo TMRx input                    | clocks after the     | e ON bit is set. |  |  |  |

|                        | Unless otherwise<br>ing the value of | e indicated, all mo<br>TMRx).                                                          | odes start upo                                                                             | n ON = 1 and st              | top upon ON =                    | 0 (stops occur       | without affect-  |  |  |  |

| 7.                     |                                      |                                                                                        |                                                                                            |                              |                                  |                      |                  |  |  |  |

#### REGISTER 27-3: TxHLT: TIMER2/4 HARDWARE LIMIT CONTROL REGISTER

7: When TMRx = PRx, the next clock clears TMRx, regardless of the operating mode.

| U-0             | U-0                    | U-0                                                | R/W-0/0        | R/W-0/0        | R/W-0/0         | R/W-0/0            | R/W-0/0      |  |  |  |  |  |

|-----------------|------------------------|----------------------------------------------------|----------------|----------------|-----------------|--------------------|--------------|--|--|--|--|--|

| —               | —                      | —                                                  |                |                | SSEL<4:0>       |                    |              |  |  |  |  |  |

| bit 7           |                        |                                                    |                |                |                 |                    | bit          |  |  |  |  |  |

|                 |                        |                                                    |                |                |                 |                    |              |  |  |  |  |  |

| Legend:         |                        |                                                    |                |                |                 |                    |              |  |  |  |  |  |

| R = Readab      | le bit                 | W = Writable                                       | bit            | U = Unimpler   | nented bit, rea | d bit, read as '0' |              |  |  |  |  |  |

| u = Bit is un   | changed                | x = Bit is unk                                     | nown           | -n/n = Value a | at POR and BC   | R/Value at all     | other Resets |  |  |  |  |  |

| '1' = Bit is se | et                     | '0' = Bit is cle                                   | eared          | q = Value dep  | ends on condi   | tion               |              |  |  |  |  |  |

|                 |                        |                                                    |                |                |                 |                    |              |  |  |  |  |  |

| bit 7-5         | Unimplem               | ented: Read as                                     | '0'            |                |                 |                    |              |  |  |  |  |  |

| bit 4-0         | SSEL<4:0>              | SMTx Signal S                                      | Selection bits |                |                 |                    |              |  |  |  |  |  |

|                 | 11111 <b>= R</b>       | 11111 = Reserved                                   |                |                |                 |                    |              |  |  |  |  |  |

|                 | •                      |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | •                      |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 10001 <b>=</b> R       | eserved                                            |                |                |                 |                    |              |  |  |  |  |  |

|                 |                        | TCC_Seconds                                        |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01111 <b>= C</b>       | LC4OUT                                             |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01110 <b>= C</b>       |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01101 = C              |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01100 = C<br>01011 = Z |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01011 = 2              |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01001 <b>= C</b>       |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 01000 <b>=</b> P'      |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 00111 <b>= P</b>       |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 00110 = C              |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 | 00101 = C              |                                                    |                |                |                 |                    |              |  |  |  |  |  |

|                 |                        | 00100 = TMR4_postscaler<br>00011 = TMR2 postscaler |                |                |                 |                    |              |  |  |  |  |  |

|                 |                        | VIR1 overflow                                      |                |                |                 |                    |              |  |  |  |  |  |

|                 |                        | MR0_overflow                                       |                |                |                 |                    |              |  |  |  |  |  |

|                 | 00000 = S              | MTSIG pin                                          |                |                |                 |                    |              |  |  |  |  |  |

#### REGISTER 28-6: SMTxSIG: SMTx SIGNAL INPUT SELECT REGISTER

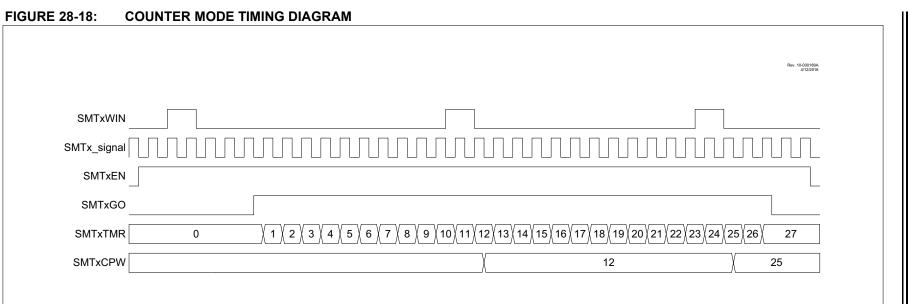

#### 28.7.11 WINDOWED COUNTER MODE

Windowed Counter mode counts pulses on the SMTx\_signal input, within a window dictated by the SMTxWIN input. It begins counting upon seeing a rising edge of the SMTxWIN input, updates the SMTxCPW register on a falling edge of the SMTxWIN input, and updates the SMTxCPR register on each rising edge of the SMTxWIN input beyond the first. See Figure 28-21 and Figure 28-22.

#### 33.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

| TABLE 33-1: | I <sup>2</sup> C BUS TERMS |

|-------------|----------------------------|

|-------------|----------------------------|

| TERM                | Description                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                     |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                    |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                       |

#### 33.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-12 shows wave forms for Start and Stop conditions.

33.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

#### 33.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 33-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

#### 33.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                  |            |                             |                |            |                             |                  |            |                             |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 299.9            | -0.02                         | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |  |

| 1200   | 1199             | -0.08                         | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |  |

| 2400   | 2404             | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |  |

| 9600   | 9615             | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | —                | _          | _                           |  |  |

| 10417  | 10417            | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |  |

| 19.2k  | 19.23k           | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | _                | _          | _                           |  |  |

| 57.6k  | 55556            | -3.55                         | 8                           | _                | _          | _                           | 57.60k         | 0.00       | 3                           | _                | _          | _                           |  |  |

| 115.2k | _                |                               | _                           | _                | _          | _                           | 115.2k         | 0.00       | 1                           | _                | —          | _                           |  |  |

#### TABLE 34-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |  |

|--------|-------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 32.000 MHz |                                                      |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300.0             | 0.00                                                 | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |  |  |

| 1200   | 1200              | 0.00                                                 | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |  |  |

| 2400   | 2400              | 0.01                                                 | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |  |  |

| 9600   | 9604              | 0.04                                                 | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |  |  |

| 10417  | 10417             | 0.00                                                 | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         |  |  |

| 19.2k  | 19.18k            | -0.08                                                | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |  |  |

| 57.6k  | 57.55k            | -0.08                                                | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |  |  |

| 115.2k | 115.9k            | 0.64                                                 | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |  |  |

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |  |

|--------|------------------|------------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |                                                      |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300.0            | 0.00                                                 | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |  |  |

| 1200   | 1200             | -0.02                                                | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |  |  |

| 2400   | 2401             | 0.04                                                 | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |  |  |

| 9600   | 9615             | 0.16                                                 | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |  |  |

| 10417  | 10417            | 0                                                    | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |  |  |

| 19.2k  | 19.23k           | 0.16                                                 | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |  |  |

| 57.6k  | 57.14k           | -0.79                                                | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |  |  |

| 115.2k | 117.6k           | 2.12                                                 | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | _          | _                           |  |  |

# PIC16(L)F19155/56/75/76/85/86

| Address   | Name    | Bit 7  | Bit 6                 | Bit 5                          | Bit 4           | Bit 3         | Bit 2       | Bit 1             | Bit 0    | Register<br>on page |

|-----------|---------|--------|-----------------------|--------------------------------|-----------------|---------------|-------------|-------------------|----------|---------------------|

| C0Ch      | RTCCON  | RTCEN  | _                     | RTCWREN                        | RTCSYNC         | HALFSEC       | _           | RTCCLK            | SEL<1:0> | 357                 |

| C0Dh      | RTCCAL  |        |                       |                                | C               | AL            |             |                   |          | 358                 |

| C0Eh      | ALRMCON | ALRMEN | CHIME                 |                                | AMASI           | <<3:0>        |             | _                 | _        | 361                 |

| C0Fh      | ALRMRPT |        |                       |                                | A               | RPT           |             |                   |          | 361                 |

| C10h      | YEAR    |        | YEARH<3:0> YEARL<3:0> |                                |                 |               |             |                   | 358      |                     |

| C11h      | MONTH   | -      | _                     | —                              | MONTHH          | MONTHL<3:0>   |             |                   | 358      |                     |

| C12h      | WEEKDAY | _      | _                     | _                              | _               | _             |             | WDAY<2:0>         |          | 359                 |

| C13h      | DAY     | _      | _                     | DAY                            | H<1:0>          |               | DA          | YL<3:0>           |          | 359                 |

| C14h      | HOURS   | _      | _                     | HRI                            | H<1:0>          |               | HF          | L<3:0>            |          | 359                 |

| C15h      | MINUTES | _      |                       | MINH<2:0>                      |                 |               | MI          | NL<3:0>           |          | 360                 |

| C16h      | SECONDS | _      |                       | SECH<2:0>                      |                 |               | SE          | CL<3:0>           |          | 360                 |

| C17h      | ALRMMTH | _      | _                     | -                              | ALRMH-<br>MONTH |               | ALRMLN      | 10NTH <3:0>       |          | 362                 |

| C18h      | ALRMWD  | —      | _                     | _                              | —               | _             |             | ALRMLWDAY<2:0     | )>       | 362                 |

| C19h      | ALRMDAY | —      | _                     | ALRMH                          | IDAY<1:0>       |               | MONTHL<3:0> |                   |          | 362                 |

| C1Ah      | ALRMHR  | —      | _                     | ALRM                           | HR<1:0>         |               |             |                   |          | 363                 |

| C1Bh      | ALRMMIN | —      | /                     | ALRMHMIN<2:0                   | )>              | ALRMLMIN<3:0> |             |                   |          | 363                 |

| C1Ch      | ALRMSEC | —      | ŀ                     | ALRMHSEC<2:                    | 0>              | ALRMLSEC<3:0> |             |                   |          | 363                 |

| C1Dh      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| C1Eh      | _       |        | Unimplemented         |                                |                 |               |             |                   |          |                     |

| C1Fh      | _       |        | Unimplemented         |                                |                 |               |             |                   |          |                     |

| C8Ch      | _       |        | Unimplemented         |                                |                 |               |             |                   |          |                     |

| C8Dh      | _       |        | Unimplemented         |                                |                 |               |             |                   |          |                     |

| C8Eh      | _       |        | Unimplemented         |                                |                 |               |             |                   |          |                     |

| C8Fh      | _       |        | ·                     |                                |                 |               |             |                   |          |                     |

| C90h      | _       |        |                       | Unimplemented<br>Unimplemented |                 |               |             |                   |          |                     |

| C91h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C92h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C93h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C94h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C95h      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| C96h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C97h      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| C98h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C99h      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C9Ah      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| C9Bh      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C9Ch      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| C9Dh      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| C9Eh      | _       |        |                       |                                | •               | emented       |             |                   |          |                     |

| C9Fh      | _       |        |                       |                                |                 | emented       |             |                   |          |                     |

| D0Ch      |         |        |                       |                                | · ·             |               |             |                   |          |                     |

| —<br>D1Fh | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| D8Ch      | _       |        |                       |                                | Unimp           | emented       |             |                   |          |                     |

| D9Fh      |         |        |                       |                                | -               |               |             | haded locations u |          |                     |

#### TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: Unimplemented data memory locations, read as '0'.

| Address   | Name     | Bit 7          | Bit 6         | Bit 5 | Bit 4           | Bit 3    | Bit 2      | Bit 1       | Bit 0    | Register<br>on page |

|-----------|----------|----------------|---------------|-------|-----------------|----------|------------|-------------|----------|---------------------|

| E0Ch      |          |                |               |       |                 |          |            |             |          |                     |

| —<br>E1Fh | _        |                |               |       | Unimpl          | emented  |            |             |          |                     |

| E8Ch      | VB0GPR   |                |               |       | VBC             | GPR      |            |             |          |                     |

| E8Dh      | VB1GPR   |                | VB1GPR        |       |                 |          |            |             |          |                     |

| E8Eh      | VB2GPR   | VB2GPR         |               |       |                 |          |            |             |          |                     |

| E8Fh      | VB3GPR   | VB3GPR         |               |       |                 |          |            |             |          |                     |

| E90h      | _        | Unimplemented  |               |       |                 |          |            |             |          |                     |