Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19155-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4          | Bit 3               | Bit 2     | Bit 1    | Bit 0  | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|---------|-------|-------|-------|----------------|---------------------|-----------|----------|--------|-----------------------|----------------------------|

| Bank 19 |         |       |       |       |                |                     |           |          |        |                       |                            |

|         |         |       |       | CPU   | CORE REGISTERS | ; see Table 4-3 for | specifics |          |        |                       |                            |

| 98Ch    | _       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 98Dh    | —       |       |       |       | Unimplei       | nented              |           |          |        |                       |                            |

| 98Eh    | —       |       |       |       | Unimplei       | nented              |           |          |        |                       |                            |

| 98Fh    | CMOUT   | —     |       | —     | —              | —                   | —         | MC2OUT   | MC10UT | 0000 0000             | 0000 0000                  |

| 990h    | CM1CON0 | ON    | OUT   | —     | POL            | —                   | —         | HYS      | SYNC   | 00-000                | 00-000                     |

| 991h    | CM1CON1 | —     |       | —     | —              | —                   | —         | INTP     | INTN   | 0000 0000             | 0000 0000                  |

| 992h    | CM1NSEL | —     |       | —     | —              | —                   |           | NCH<2:0> |        | 0000 0000             | 0000 0000                  |

| 992h    |         | —     |       | —     | —              | —                   | NCH2      | NCH1     | NCH0   | 0000 0000             | 0000 0000                  |

| 993h    | CM1PSEL | —     |       | —     | —              |                     | PCF       | 1<3:0>   |        | 0000 0000             | 0000 0000                  |

| 993h    |         | —     |       | _     | —              | —                   | PCH2      | PCH1     | PCH0   | 0000 0000             | 0000 0000                  |

| 994h    | CM2CON0 | ON    | OUT   | —     | POL            | —                   | —         | HYS      | SYNC   | 00-000                | 00-000                     |

| 995h    | CM2CON1 | —     | _     | —     | —              | —                   | —         | INTP     | INTN   | 0000 0000             | 0000 0000                  |

| 996h    | CM2NSEL | —     | _     | —     | —              | —                   |           | NCH<2:0> |        | 0000 0000             | 0000 0000                  |

| 996h    |         | —     | _     | —     | —              | —                   | NCH2      | NCH1     | NCH0   | 0000 0000             | 0000 0000                  |

| 997h    | CM2PSEL | —     | _     | —     | —              | —                   |           | PCH<2:0> |        | 0000 0000             | 0000 0000                  |

| 997h    |         | —     | _     | —     | —              | —                   | PCH2      | PCH1     | PCH0   | 0000 0000             | 0000 0000                  |

| 998h    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 999h    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Ah    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Bh    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Ch    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Dh    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Eh    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

| 99Fh    | —       |       |       |       | Unimplei       | mented              |           |          |        |                       |                            |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

|                    |                                                 |                | 1                |                      |                       | . ,              |                   |                  |            | ,                     |                            |

|--------------------|-------------------------------------------------|----------------|------------------|----------------------|-----------------------|------------------|-------------------|------------------|------------|-----------------------|----------------------------|

| Address            | Name                                            | Bit 7          | Bit 6            | Bit 5                | Bit 4                 | Bit 3            | Bit 2             | Bit 1            | Bit 0      | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Banks 30-5         | Sanks 30-57                                     |                |                  |                      |                       |                  |                   |                  |            |                       |                            |

|                    | CPU CORE REGISTERS; see Table 4-3 for specifics |                |                  |                      |                       |                  |                   |                  |            |                       |                            |

| F0Ch<br>—<br>1C9Fh | _                                               |                |                  |                      | Unimpler              | nented           |                   |                  |            |                       |                            |

| Legend:            | x = unknown, u                                  | = unchanged, g | = depends on cor | ndition, - = unimple | emented, read as '0', | r = reserved. Sh | aded locations un | implemented, rea | ad as '0'. |                       |                            |

**Note 1:** Unimplemented data memory locations, read as '0'.

| 1 | TABLE 4 | 4-12: SPEC | IAL FUNC | <b>FION REGIST</b> | ER SUMMA | RY BANKS 0- | 63 PIC16(L) | F19155/56/7 | 5/76/85/86 ( | CONTINUED | )         |  |

|---|---------|------------|----------|--------------------|----------|-------------|-------------|-------------|--------------|-----------|-----------|--|

|   | Addroop | Nomo       | Dit 7    | Dit 6              | Dit E    | Dit 4       | Dit 2       | Dit 2       | Dit 1        | Rit 0     | Value on: |  |

| Address    | Name                | Bit 7 | Bit 6         | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|------------|---------------------|-------|---------------|-------|----------|--------|-------|-------|-------|-----------------------|----------------------------|

| Bank 61 (C | Bank 61 (Continued) |       |               |       |          |        |       |       |       |                       |                            |

| 1EE5h      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EE6h      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EE7h      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EE8h      | _                   |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1EE9h      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EEAh      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EEBh      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EECh      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EEDh      | —                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EEEh      | _                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1EEFh      | _                   |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1          |                     |       |               |       |          |        |       |       |       |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| U-0            | U-0                                                              | R/W/HS-0/0                             | R-0                     | U-0               | U-0                | U-0              | R/W/HS-0/0          |

|----------------|------------------------------------------------------------------|----------------------------------------|-------------------------|-------------------|--------------------|------------------|---------------------|

|                |                                                                  | TMR0IF                                 | IOCIF                   | _                 | _                  | _                | INTF <sup>(1)</sup> |

| bit 7          |                                                                  |                                        |                         |                   |                    |                  | bit 0               |

|                |                                                                  |                                        |                         |                   |                    |                  |                     |

| Legend:        |                                                                  |                                        |                         |                   |                    |                  |                     |

| R = Reada      | able bit                                                         | W = Writable I                         | oit                     | U = Unimpler      | mented bit, read   | as '0'           |                     |

| u = Bit is u   | nchanged                                                         | x = Bit is unkn                        | own                     | -n/n = Value a    | at POR and BO      | R/Value at all o | other Resets        |

| '1' = Bit is : | set                                                              | '0' = Bit is clea                      | ared                    | HS= Hardwa        | re Set             |                  |                     |

|                |                                                                  |                                        |                         |                   |                    |                  |                     |

| bit 7-6        | Unimplemer                                                       | nted: Read as 'o                       | )'                      |                   |                    |                  |                     |

| bit 5          |                                                                  | er0 Overflow In                        |                         |                   |                    |                  |                     |

|                |                                                                  | register has ove<br>register did not   |                         | t be cleared in   | software)          |                  |                     |

| bit 4          | IOCIF: Interr                                                    | upt-on-Change                          | Interrupt Flag          | bit (read-only)   | (2)                |                  |                     |

|                |                                                                  | more of the IOC<br>d by the IOC mo     |                         | gister bits are o | currently set, ind | icating an ena   | bled edge was       |

|                |                                                                  | f the IOCAF-IOC                        |                         | oits are current  | ly set             |                  |                     |

| bit 3-1        | Unimplemer                                                       | nted: Read as 'o                       | )'                      |                   |                    |                  |                     |

| bit 0          | INTF: INT EX                                                     | ternal Interrupt                       | Flag bit <sup>(1)</sup> |                   |                    |                  |                     |

|                |                                                                  | Γexternal interru<br>Γexternal interru | •                       | •                 | ed in software)    |                  |                     |

| 2:             | The External Inter<br>The IOCIF bit is the<br>application firmwa | ne logical OR of                       | all the IOCAF           | -IOCEF flags.     | Therefore, to cl   |                  | flag,               |

| REGISTER 10-11: | PIR0: PERIPHERAL INTERRUPT STATUS REGISTER 0 |

|-----------------|----------------------------------------------|

|-----------------|----------------------------------------------|

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of |

|-------|-----------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the Global                                                    |

|       | Enable bit, GIE, of the INTCON register.                                                      |

|       | User software should ensure the                                                               |

|       | appropriate interrupt flag bits are clear                                                     |

|       | prior to enabling an interrupt.                                                               |

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O

- pinsCurrent draw from pins with internal weak

- pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

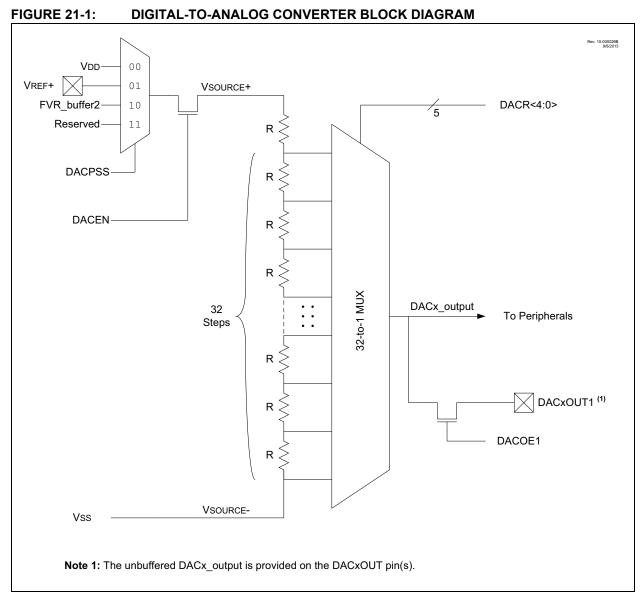

Any module with a clock source that is not Fosc can be enabled. Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module", Section 18.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 11.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.14 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WWDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

#### EXAMPLE 13-1: PFM PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

NVMCON1,NVMREGS ; Do not select Configuration Space

BCF

NVMCON1, RD

BSF

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDATL,W; Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

# EXAMPLE 13-3: ERASING ONE ROW OF PROGRAM FLASH MEMORY (PFM)

| ; This sampl | e row erase routine as  | sumes the following:                          |

|--------------|-------------------------|-----------------------------------------------|

| ; 1.A valid  | address within the era  | se row is loaded in variables ADDRH:ADDRL     |

| ; 2.ADDRH an | nd ADDRL are located in | x  common RAM (locations $0x70 - 0x7F$ )      |

| BANKSEL      | NVMADRL                 |                                               |

| MOVF         | ADDRL,W                 |                                               |

| MOVWF        | NVMADRL                 | ; Load lower 8 bits of erase address boundary |

| MOVF         | ADDRH,W                 | _                                             |

| MOVWF        | NVMADRH                 | ; Load upper 6 bits of erase address boundary |

| BCF          | NVMCON1, NVMREGS        | ; Choose PFM memory area                      |

| BSF          | NVMCON1, FREE           | ; Specify an erase operation                  |

| BSF          | NVMCON1,WREN            | ; Enable writes                               |

| BCF          | INTCON,GIE              | ; Disable interrupts during unlock sequence   |

| ;            | F                       | EOUIRED UNLOCK SEQUENCE:                      |

|              |                         | ~ ~                                           |

| MOVLW        | 55h                     | ; Load 55h to get ready for unlock sequence   |

| MOVWF        | NVMCON2                 | ; First step is to load 55h into NVMCON2      |

| MOVLW        | AAh                     | ; Second step is to load AAh into W           |

| MOVWF        | NVMCON2                 | ; Third step is to load AAh into NVMCON2      |

| BSF          | NVMCON1,WR              | ; Final step is to set WR bit                 |

| ;            |                         |                                               |

| 2.22         |                         |                                               |

| BSF          |                         | ; Re-enable interrupts, erase is complete     |

| BCF          | NVMCON1,WREN            | ; Disable writes                              |

|              |                         |                                               |

|              |                         |                                               |

### EXAMPLE 13-4: WRITING TO PROGRAM FLASH MEMORY (PFM)

; This write routine assumes the following:

| ; 1.3         | 32 bytes of d  | ata are loaded, startir | ng at the address in DATA_ADDR                                                 |

|---------------|----------------|-------------------------|--------------------------------------------------------------------------------|

| ; 2.E         | Each word of   | data to be written is m | nade up of two adjacent bytes in DATA_ADDR,                                    |

| ; 5           | stored in lit  | tle endian format       |                                                                                |

| ; 3. <i>I</i> | A valid start  | ing address (the least  | significant bits = 00000) is loaded in ADDRH:ADDRL                             |

| ; 4. <i>1</i> | ADDRH and ADD  | RL are located in commo | on RAM (locations 0x70 - 0x7F)                                                 |

| ; 5.1         | WM interrupt   | s are not taken into ac | count                                                                          |

|               | BANKSEL        | NVMADRH                 |                                                                                |

|               | MOVF           | ADDRH, W                |                                                                                |

|               | MOVWF          | NVMADRH                 | ; Load initial address                                                         |

|               | MOVF           | ADDRL,W                 |                                                                                |

|               | MOVWF          | NVMADRL                 |                                                                                |

|               | MOVLW          | LOW DATA ADDR           | ; Load initial data address                                                    |

|               | MOVWF          | FSR0L                   |                                                                                |

|               | MOVLW          | HIGH DATA_ADDR          |                                                                                |

|               | MOVWF          | FSR0H                   |                                                                                |

|               | BCF            | NVMCON1, NVMREGS        | ; Set Program Flash Memory as write location                                   |

|               | BSF            | NVMCON1, WREN           | ; Enable writes                                                                |

|               | BSF            | NVMCON1, LWLO           | ; Load only write latches                                                      |

|               |                |                         |                                                                                |

| LOOP          | MONTH          | ECDO                    |                                                                                |

|               | MOVIW          | FSR0++                  | · Trad Street date in the                                                      |

|               | MOVWF          | NVMDATL                 | ; Load first data byte                                                         |

|               | MOVIW<br>MOVWF | FSR0++<br>NVMDATH       | ; Load second data byte                                                        |

|               |                |                         | / Houd Second data byte                                                        |

|               | MOVF           | NVMADRL,W               | · Charle if lower bits of address and 00000                                    |

|               | XORLW          | 0x1F                    | ; Check if lower bits of address are 00000<br>; and if on last of 32 addresses |

|               | ANDLW<br>BTFSC | 0x1F                    | ; Last of 32 words?                                                            |

|               | GOTO           | STATUS,Z<br>START_WRITE | ; If so, go write latches into memory                                          |

|               |                |                         |                                                                                |

|               | CALL<br>INCF   | UNLOCK_SEQ              | ; If not, go load latch<br>; Increment address                                 |

|               | GOTO           | NVMADRL, F<br>LOOP      | , increment address                                                            |

|               | 0010           |                         |                                                                                |

| START         | _WRITE         |                         |                                                                                |

|               | BCF            | NVMCON1,LWLO            | ; Latch writes complete, now write memory                                      |

|               | CALL           | UNLOCK_SEQ              | ; Perform required unlock sequence                                             |

|               | BCF            | NVMCON1,WREN            | ; Disable writes                                                               |

| UNLOCI        | K_SEQ          |                         |                                                                                |

|               | MOVLW          | 55h                     |                                                                                |

|               | BCF            | INTCON, GIE             | ; Disable interrupts                                                           |

|               | MOVWF          | NVMCON2                 | ; Begin unlock sequence                                                        |

|               | MOVLW          | AAh                     |                                                                                |

|               | MOVWF          | NVMCON2                 |                                                                                |

|               | BSF            | NVMCON1,WR              |                                                                                |

|               | BSF            | INTCON,GIE              | ; Unlock sequence complete, re-enable interrupts                               |

|               | return         |                         |                                                                                |

|               |                |                         |                                                                                |

| R/W/HS-0/0       | R/W/HS-0/0 | U-0                           | R/W/HS-0/0 | R/W/HS-0/0                         | R/W/HS-0/0             | R/W/HS-0/0       | R/W/HS-0/0      |  |  |

|------------------|------------|-------------------------------|------------|------------------------------------|------------------------|------------------|-----------------|--|--|

| IOCCF7           | IOCCF6     |                               | IOCCF4     | IOCCF3                             | IOCCF2                 | IOCCF1           | IOCCF0          |  |  |

| bit 7            |            |                               |            |                                    |                        |                  | bit 0           |  |  |

|                  |            |                               |            |                                    |                        |                  |                 |  |  |

| Legend:          |            |                               |            |                                    |                        |                  |                 |  |  |

| R = Readable bit |            | W = Writable bit              |            | U = Unimplemented bit, read as '0' |                        |                  |                 |  |  |

| u = Bit is unch  | anged      | x = Bit is unkr               | iown       | -n/n = Value a                     | at POR and BO          | R/Value at all o | ther Resets     |  |  |

| '1' = Bit is set |            | '0' = Bit is clea             | ared       | HS - Bit is set                    | t in hardware          |                  |                 |  |  |

|                  |            |                               |            |                                    |                        |                  |                 |  |  |

| bit 7-6          |            | •                             | 0          | ORTC Flag bits                     |                        |                  |                 |  |  |

|                  |            | ed change was<br>IOCCPx = 1 a |            |                                    | pin<br>d on RCx, or wh | nen IOCCNx =     | 1 and a falling |  |  |

|         | edge was detected on RCx.                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 0 = No change was detected, or the user cleared the detected change                                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                            |

| bit 4-0 | IOCCF<4:0>: Interrupt-on-Change PORTC Flag bits<br>1 = An enabled change was detected on the associated pin           |

|         | Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx. |

|         |                                                                                                                       |

<sup>0 =</sup> No change was detected, or the user cleared the detected change

#### REGISTER 17-10: IOCEP: INTERRUPT-ON-CHANGE PORTE POSITIVE EDGE REGISTER

| U-0         | U-0 | U-0 | U-0 | R/W/HS-0/0            | U-0 | U-0 | U-0 |  |  |

|-------------|-----|-----|-----|-----------------------|-----|-----|-----|--|--|

| —           | —   | —   | —   | IOCEP3 <sup>(1)</sup> | —   | —   | —   |  |  |

| bit 7 bit 0 |     |     |     |                       |     |     |     |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 3 IOCEP3: Interrupt-on-Change PORTE Positive Edge Enable bit

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCEFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

bit 2-0 Unimplemented: Read as '0'

**Note 1:** If MCLRE = 1 or LVP = 1, RC port functionality is disabled and IOC is not available on RE3.

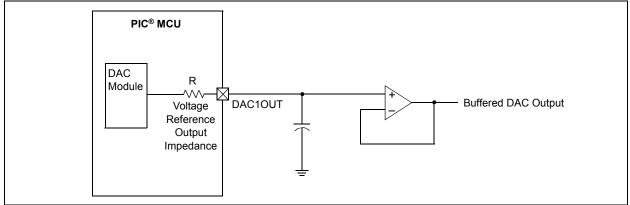

### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2017 Microchip Technology Inc.

# 21.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected.

# 21.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT1/2 pins.

- The DAC1R<4:0> range select bits are cleared.

| <b>B</b> 44 6 15       | <b>B</b> 444 6 15                                                                                                                         | <b>D B B B B B B B B B B</b>                | <b>B</b> # 4 / 6 / 7                                                   | <b>B B B B B B B B B B</b>   | <b>D</b> # <b>M A</b> / <b>A</b> | <b>B</b> # 4 / 6 / 6 | <b>D M M M</b>   |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------|------------------------------|----------------------------------|----------------------|------------------|--|--|--|

| R/W-0/0                | R/W-0/0                                                                                                                                   | R/W-0/0                                     | R/W-0/0                                                                | R/W-0/0                      | R/W-0/0                          | R/W-0/0              | R/W-0/0          |  |  |  |

| PSYNC <sup>(1, 2</sup> | <sup>2)</sup> CKPOL <sup>(3)</sup>                                                                                                        | CKSYNC <sup>(4, 5)</sup>                    |                                                                        | Ν                            | /IODE<4:0> <sup>(6, 7</sup>      | )                    |                  |  |  |  |

| bit 7                  |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      | bit 0            |  |  |  |

|                        |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

| Legend:                |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

| R = Readab             | le bit                                                                                                                                    | W = Writable b                              | = Writable bit U = Unimplemented bit, read as '0'                      |                              |                                  |                      |                  |  |  |  |

| u = Bit is un          | changed                                                                                                                                   | x = Bit is unkno                            | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |                              |                                  |                      |                  |  |  |  |

| '1' = Bit is s         | et                                                                                                                                        | '0' = Bit is clear                          | ed                                                                     |                              |                                  |                      |                  |  |  |  |

|                        |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

| bit 7                  | PSYNC: Tim                                                                                                                                | ner2/4 Prescaler S                          | Synchronizati                                                          | on Enable bit <sup>(1,</sup> | 2)                               |                      |                  |  |  |  |

|                        |                                                                                                                                           | Prescaler Output is                         |                                                                        |                              |                                  |                      |                  |  |  |  |

|                        |                                                                                                                                           | Prescaler Output is                         | •                                                                      |                              |                                  |                      |                  |  |  |  |

| bit 6                  |                                                                                                                                           | ner2/4 Clock Pola                           | •                                                                      |                              |                                  |                      |                  |  |  |  |

|                        | <ul> <li>1 = Falling edge of input clock clocks timer/prescaler</li> <li>0 = Rising edge of input clock clocks timer/prescaler</li> </ul> |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

|                        | •                                                                                                                                         | •                                           |                                                                        | •                            |                                  |                      |                  |  |  |  |

| bit 5                  |                                                                                                                                           | imer2/4 Clock Sy                            |                                                                        |                              |                                  |                      |                  |  |  |  |

|                        |                                                                                                                                           | ster bit is synchro<br>ster bit is not sync |                                                                        |                              |                                  |                      |                  |  |  |  |

| bit 4-0                | -                                                                                                                                         | : Timer2/4 Contro                           |                                                                        |                              |                                  |                      |                  |  |  |  |

| DIL 4-0                | See Table 27                                                                                                                              |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

|                        |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

|                        | •                                                                                                                                         | nsures that reading                         | •                                                                      |                              | alue.                            |                      |                  |  |  |  |

| 2:                     | When this bit is                                                                                                                          | '1', Timer2/4 canr                          | not operate in                                                         | Sleep mode.                  |                                  |                      |                  |  |  |  |

| 3:                     | CKPOL should r                                                                                                                            | not be changed w                            | hile ON = 1.                                                           |                              |                                  |                      |                  |  |  |  |

| 4:                     | Setting this bit e                                                                                                                        | nsures glitch-free                          | es glitch-free operation when the ON is enabled or disabled.           |                              |                                  |                      |                  |  |  |  |

| 5:                     | When this bit is s                                                                                                                        | set then the timer of                       | operation will                                                         | be delayed by t              | wo TMRx input                    | clocks after the     | e ON bit is set. |  |  |  |

|                        | Unless otherwise<br>ing the value of                                                                                                      | e indicated, all mo<br>TMRx).               | des start upo                                                          | n ON = 1 and st              | top upon ON =                    | 0 (stops occur       | without affect-  |  |  |  |

| 7.                     |                                                                                                                                           |                                             |                                                                        |                              |                                  |                      |                  |  |  |  |

# REGISTER 27-3: TxHLT: TIMER2/4 HARDWARE LIMIT CONTROL REGISTER

7: When TMRx = PRx, the next clock clears TMRx, regardless of the operating mode.

### 28.7.7 TIME OF FLIGHT MEASURE MODE

Time of Flight Measure mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMTx\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMTxCPR register and resetting the timer upon observing a rising edge on the SMTx\_signal input. In the event of two SMTWINx rising edges without an SMTx\_signal rising edge, it will update the SMTxCPW register with the current value of the timer and reset the timer value. See Figure 28-14 and Figure 28-15.

# 32.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR5 register will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · CLCxIE bit of the PIE5 register

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the PIR5 register, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 32.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the LCxOUT bits in the individual CLCxCON registers.

### 32.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 32.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 32.6 CLCx Setup Steps

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 32-2).

- Clear any associated ANSEL bits.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxGyPOL bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the PIE5 register.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

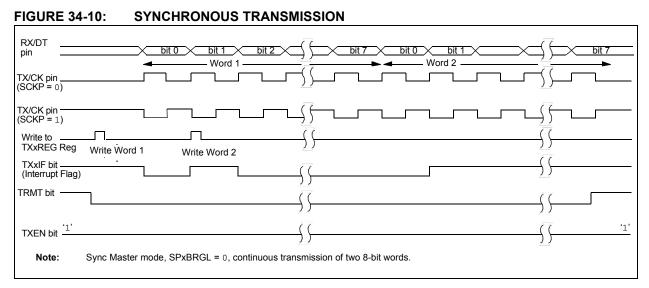

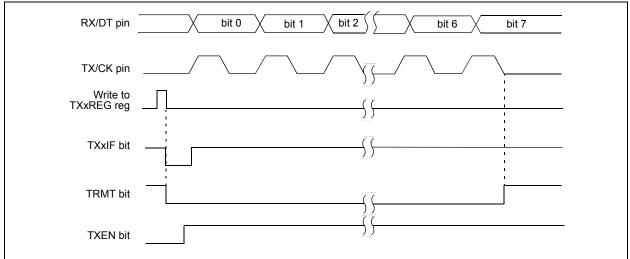

FIGURE 34-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 34.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RXxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RXxIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

| R/W-0        | R/W-0                                                                      | HS/C-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |  |

|--------------|----------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|-----------------|-----------------|--------|--|--|--|

| LCDEN        | SLPEN                                                                      | WERR                                | CS              | LMUX3            | LMUX2           | LMUX1           | LMUX0  |  |  |  |

| bit 7        |                                                                            |                                     |                 |                  |                 |                 | bit 0  |  |  |  |

| Legend:      |                                                                            | C = Clearable                       | e bit           | HS = Bit is se   | t by hardware   |                 |        |  |  |  |

| R = Readab   | le bit                                                                     | W = Writable                        | bit             | U = Unimplen     | nented bit, rea | id as '0'       |        |  |  |  |

| -n = Value a | t POR                                                                      | '1' = Bit is set                    |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |  |  |  |

| bit 7        | LCDEN: LCD                                                                 | Enable bit                          |                 |                  |                 |                 |        |  |  |  |

|              |                                                                            | lule is enabled<br>lule is disabled |                 |                  |                 |                 |        |  |  |  |

| bit 6        | SLPEN: LCD                                                                 | Display Sleep-                      | Enabled bit     |                  |                 |                 |        |  |  |  |

|              |                                                                            | vill stop driving                   |                 |                  |                 |                 |        |  |  |  |

|              |                                                                            | vill continue driv                  |                 |                  |                 |                 |        |  |  |  |

| bit 5        | WERR: LCD Write Failed Error bit <sup>(1)</sup>                            |                                     |                 |                  |                 |                 |        |  |  |  |

|              | 1 = Write failure to LCDDATA register occurred (must be reset in software) |                                     |                 |                  |                 |                 |        |  |  |  |

|              | 0 = No LCD write error                                                     |                                     |                 |                  |                 |                 |        |  |  |  |

| bit 4        | CS: Clock Source Select bit                                                |                                     |                 |                  |                 |                 |        |  |  |  |

|              | 1 = SOSC Selected<br>0 = LFINTOSC Selected                                 |                                     |                 |                  |                 |                 |        |  |  |  |

| bit 3-0      |                                                                            |                                     | tion hita Cna   | oifice the numb  | or of common    | _(2)            |        |  |  |  |

| DIT 3-0      |                                                                            | Common Selec                        | ction bits. Spe | cifies the numbe | er of commons   | 5(-)            |        |  |  |  |

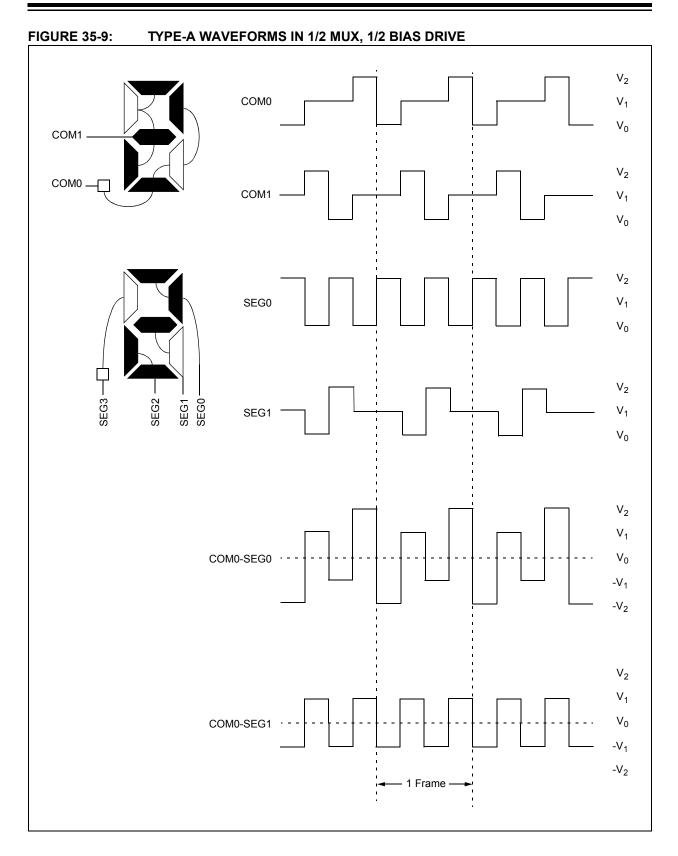

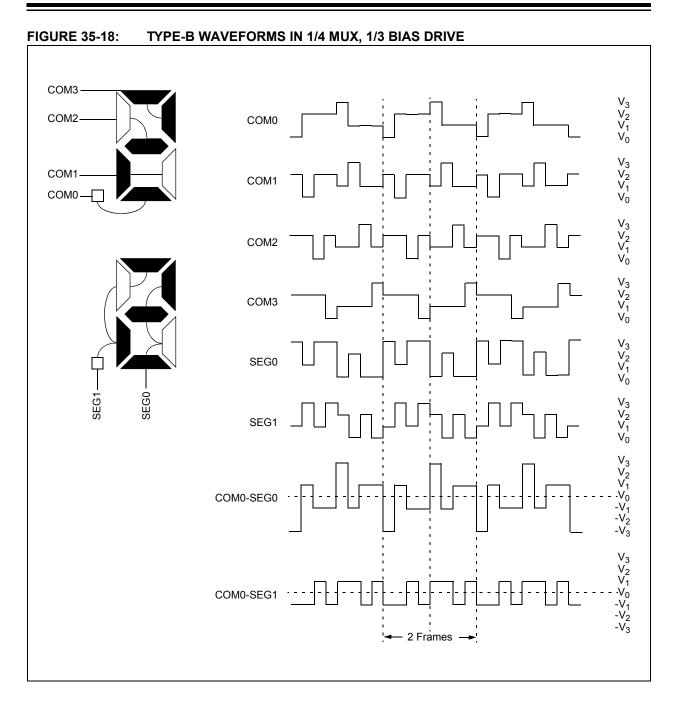

|              | LMUX<3                                                                     | :0>                                 |                 | Multiplex        |                 |                 | Bias   |  |  |  |

|              | 0000                                                                       |                                     |                 | All COMs off     |                 |                 | _      |  |  |  |

|              | 0001                                                                       |                                     |                 | Static (COM0)    |                 |                 | Static |  |  |  |

|              | 0010                                                                       |                                     | 1/2             | MUX (COM<1:0>)   |                 | 1/2             |        |  |  |  |

|              | 0011                                                                       |                                     | 1/3             | MUX (COM<2:0>)   |                 | 1/3             |        |  |  |  |

|              | 0100                                                                       |                                     | 1/4             | MUX (COM<3:0>)   |                 |                 | 1/3    |  |  |  |

|              | 0101                                                                       |                                     | 1/5             | MUX (COM<4:      | 0>)             |                 | 1/3    |  |  |  |

|              | 0110                                                                       |                                     | 1/6             | MUX (COM<5:0>)   |                 |                 | 1/3    |  |  |  |

|              | 0111                                                                       |                                     | 1/7             |                  | 1/3             |                 |        |  |  |  |

|              | 1000                                                                       |                                     | 1/8             | MUX (COM<7:      | 0>)             |                 | 1/3    |  |  |  |

#### REGISTER 35-1: LCDCON: LCD CONTROL REGISTER

Note 1: Bit can only be set by hardware and only cleared in software by writing to zero.

**2:** Cannot be changed when LCDEN = 1.

| Address | Name     | Bit 7 | Bit 6         | Bit 5     | Bit 4           | Bit 3     | Bit 2     | Bit 1            | Bit 0   | Register<br>on page |  |  |

|---------|----------|-------|---------------|-----------|-----------------|-----------|-----------|------------------|---------|---------------------|--|--|

| 212h    | _        |       |               | •         | Unimpl          | emented   |           | •                |         |                     |  |  |

| 213h    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 214h    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 215h    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 216h    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 217h    | —        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 218h    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 219h    | —        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 21Ah    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 21Bh    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 21Ch    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 21Dh    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 21Eh    | CCPTMRS0 | P4TS  | EL<1:0>       | P3TS      | SEL1:0>         | C2TSE     | EL<1:0>   | C1TSE            | EL<1:0> | 461                 |  |  |

| 21Fh    |          |       |               |           | Unimpl          | emented   |           | •                |         |                     |  |  |

| 28Ch    | T2TMR    |       | TMR2          |           |                 |           |           |                  |         |                     |  |  |

| 28Dh    | T2PR     |       |               |           | P               | R2        |           |                  |         |                     |  |  |

| 28Eh    | T2CON    | ON    |               | CKPS<2:0> |                 |           | OUT       | PS<3:0>          |         | 404                 |  |  |

| 28Fh    | T2HLT    | PSYNC | CKPOL         | CKSYNC    |                 | MODE<4:0> |           |                  |         | 405                 |  |  |

| 290h    | T2CLKCON | —     | _             | _         | _               |           | CS        | 6<3:0>           |         | 403                 |  |  |

| 291h    | T2RST    | _     | _             | _         | _               |           | RSI       | EL<3:0>          |         | 406                 |  |  |

| 292h    | T4TMR    |       |               |           | T               | /IR4      |           |                  |         |                     |  |  |

| 293h    | T4PR     |       |               |           | P               | R4        |           |                  |         |                     |  |  |

| 294h    | T4CON    | ON    |               | CKPS<2:0> |                 |           | OUT       | PS<3:0>          |         | 404                 |  |  |

| 295h    | T4HLT    | PSYNC | CKPOL         | CKSYNC    |                 |           | MODE<4:0> |                  |         | 405                 |  |  |

| 296h    | T4CLKCON | —     | _             | _         | _               |           | CS        | 6<3:0>           |         | 403                 |  |  |

| 297h    | T4RST    | _     | _             | _         | _               |           | RSI       | EL<3:0>          |         | 406                 |  |  |

| 298h    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 299h    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 29Ah    | —        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 29Bh    | —        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 29Ch    | _        |       |               |           | Unimpl          | emented   |           |                  |         |                     |  |  |

| 29Dh    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 29Eh    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| 29Fh    | —        |       | Unimplemented |           |                 |           |           |                  |         |                     |  |  |

| Leaend: |          |       |               |           | = unimplementer |           | 0         | hadad la settema |         |                     |  |  |

### TABLE 38-1: REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, g = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.