Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19155t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name | Bit 7 | Bit 6         | Bit 5 | Bit 4         | Bit 3               | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|------|-------|---------------|-------|---------------|---------------------|------------|-------|-------|-----------------------|----------------------------|

| Bank 63 |      |       |               |       |               | •                   |            |       | •     |                       |                            |

|         |      |       |               | CPU   | CORE REGISTER | S: see Table 4-3 fo | rspecifics |       |       |                       |                            |

|         |      |       |               |       |               |                     | opeeniee   |       |       |                       |                            |

| 1F8Ch   | —    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

| 1F8Dh   | —    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F8Eh   | —    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

| 1F8Fh   | —    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

| 1F90h   | —    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F91h   | —    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F92h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F93h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F94h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F95h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F96h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F97h   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F98h   |      |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F99h   |      |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F9Ah   |      |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F9Bh   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F9Ch   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F9Dh   | _    |       | Unimplemented |       |               |                     |            |       |       |                       |                            |

| 1F9Eh   | _    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

| 1F9Fh   | _    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

| 1FA0h   | —    |       |               |       | Unimple       | mented              |            |       |       |                       |                            |

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

© 2017 Microchip Technology Inc.

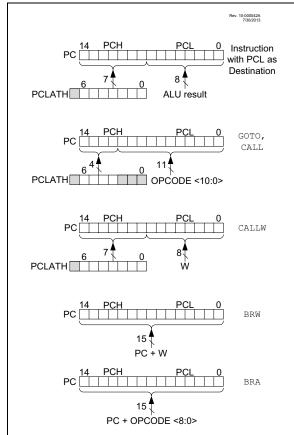

# 4.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-3 shows the five situations for the loading of the PC.

FIGURE 4-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

# 4.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 4.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 4.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 + the signed value of the operand of the BRA instruction.

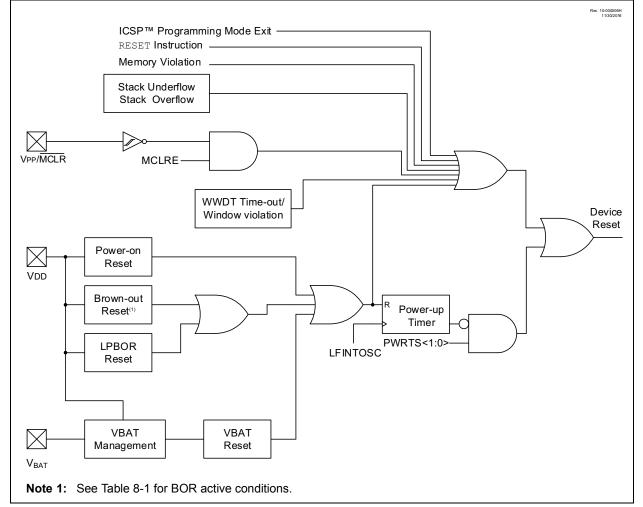

# 8.0 RESETS AND VBAT

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

- Memory Violation Reset (MEMV)

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 8-1.

# 8.1 VBAT

This device is equipped with a VBAT pin that allows the user to connect an external battery or an external supply. In the event of the VDD supply failing, the power source connected to the VBAT pin will keep the SOSC and RTCC modules running.

| R/W-0/0        | 0 R/W-0/0                                                   | U-0                                                    | U-0                          | U-0          | R/W-0/0           | R/W-0/0           | R/W-0/0    |

|----------------|-------------------------------------------------------------|--------------------------------------------------------|------------------------------|--------------|-------------------|-------------------|------------|

| LCDIE          | RTCCIE                                                      | —                                                      | —                            |              | SMT1PWAIE         | SMT1PRAIE         | SMT1IE     |

| bit 7          |                                                             |                                                        |                              |              |                   |                   | bit        |

| Legend:        |                                                             |                                                        |                              |              |                   |                   |            |

| R = Reada      | able bit                                                    | W = Writable                                           | bit                          | U = Unimple  | emented bit, read | l as '0'          |            |

| u = Bit is u   | inchanged                                                   | x = Bit is unkr                                        | nown                         | -n/n = Value | at POR and BO     | R/Value at all ot | her Resets |

| '1' = Bit is : | •                                                           | '0' = Bit is cle                                       | ared                         | HS = Hardv   | /are set          |                   |            |

|                |                                                             |                                                        |                              |              |                   |                   |            |

| bit 7          | 1 = Enables                                                 | Interrupt Enabl<br>the LCD interru<br>the LCD interru  | pt                           |              |                   |                   |            |

| bit 6          | 1 = Enables                                                 | IT1 Overflow In<br>the RTCC inter<br>the RTCC inter    | rupt                         | bit          |                   |                   |            |

| bit 5-3        | Unimpleme                                                   | nted: Read as '                                        | 0'                           |              |                   |                   |            |

| bit 2          | 1 = Enables                                                 | E: SMT1 Pulse-<br>the SMT acquis<br>the SMT acquis     | ition interrupt              | •            | Enable bit        |                   |            |

| bit 1          | 1 = Enables                                                 | : SMT1 Period<br>the SMT acquis<br>the SMT acqui       | ition interrupt              |              | e bit             |                   |            |

| bit 0          | <b>SMT1IE:</b> SM<br>1 = Enables                            | IT1 Overflow Int<br>the SMT overflo<br>the SMT overflo | errupt Enable<br>w interrupt |              |                   |                   |            |

| Note:          | Bit PEIE of the IN<br>set to enable a<br>controlled by regi | ITCON register                                         | must be<br>interrupt         |              |                   |                   |            |

# REGISTER 10-10: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

# 12.0 WINDOWED WATCHDOG TIMER (WWDT)

The Windowed Watchdog Timer (WWDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WWDT has the following features:

- Selectable clock source

- Multiple operating modes

- WWDT is always on

- WWDT is off when in Sleep

- WWDT is controlled by software

- WWDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- Multiple Reset conditions

- · Operation during Sleep

# 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 39-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.2.6 ANALOG CONTROL

The ANSELA register (Register 14-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |

#### 14.2.7 WEAK PULL-UP CONTROL

The WPUA register (Register 14-5) controls the individual weak pull-ups for each PORT pin.

#### 14.2.8 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

# 14.5 Register Definitions: PORTB

#### REGISTER 14-9: PORTB: PORTB REGISTER

| R/W-x/u        | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u                              | R/W-x/u | R/W-x/u | R/W-x/u |  |

|----------------|---------|--------------|---------|--------------------------------------|---------|---------|---------|--|

| RB7            | RB6     | RB5          | RB4     | RB3                                  | RB2     | RB1     | RB0     |  |

| bit 7          |         | •            |         | •                                    |         |         | bit 0   |  |

|                |         |              |         |                                      |         |         |         |  |

| Legend:        |         |              |         |                                      |         |         |         |  |

| R = Readable b | it      | W = Writable | hit     | II = II nimplemented bit read as '0' |         |         |         |  |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RB<7:0>**: PORTB I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

# REGISTER 14-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

# REGISTER 17-11: IOCEN: INTERRUPT-ON-CHANGE PORTE NEGATIVE EDGE REGISTER

| IOCEN3 <sup>(1)</sup> | U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0            | U-0 | U-0 | U-0   |

|-----------------------|-------|-----|-----|-----|-----------------------|-----|-----|-------|

| bit 7                 | —     | —   | —   | _   | IOCEN3 <sup>(1)</sup> | —   | —   | —     |

|                       | bit 7 |     |     |     |                       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | IOCEN3: Interrupt-on-Change PORTE Negative Edge Enable bit                                                                             |

|         | 1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCEFx bit and IOCIF flag will<br>be set upon detecting an edge. |

|         | 0 = Interrupt-on-Change disabled for the associated pin                                                                                |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                             |

| Note 1  | If MCL $PE = 1$ or $I \setminus PE = 1$ . $PE = 2$ port functionality is disabled and IOC is not available on $PE = 2$                 |

# **Note 1:** If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC is not available on RE3.

#### REGISTER 17-12: IOCEF: INTERRUPT-ON-CHANGE PORTE FLAG REGISTER

| U-0   | U-0         | U-0 | U-0 | R/W/HS-0/0 | U-0 | U-0 | U-0 |  |  |

|-------|-------------|-----|-----|------------|-----|-----|-----|--|--|

| —     | —           |     |     | IOCEF3     | —   |     | —   |  |  |

| bit 7 | bit 7 bit 0 |     |     |            |     |     |     |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>IOCEF3: Interrupt-on-Change PORTE Flag bit</li> <li>1 = An enabled change was detected on the associated pin<br/>Set when IOCEPx = 1 and a rising edge was detected on REx, or when IOCENx = 1 and a falling<br/>edge was detected on REx.</li> <li>0 = No change was detected, or the user cleared the detected change</li> </ul> |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                  |

# **19.3 ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 19-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 19-4. The maximum recommended impedance for analog sources is 1 k $\Omega$ . If the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 19-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified accuracy.

# EQUATION 19-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 1k Ω 5.0V VDD

TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 2µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$ ;[2] VCHOLD charge response to VAPPLIED

$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$ ;[2] VCHOLD charge response to VAPPLIED

$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right)$ ; combining [1] and [2]

Note: Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/8191)$$

= -28 pF(1k\Omega + 7k\Omega + 1k\Omega) \ln(0.0001221)

= 2.27\mus

Therefore:

$$TACQ = 2 \mu s + 4.54 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$$

= 5.52 \mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $1k\Omega$ . This is required to meet the pin leakage specification.

© 2017 Microchip Technology Inc.

### 19.5.5 BURST AVERAGE MODE

The Burst Average mode (ADMD = 011) acts the same as the Average mode in most respects. The one way it differs is that it continuously retriggers ADC sampling until the CNT value is greater than or equal to RPT, even if Continuous Sampling mode (see **Section 19.5.8 "Continuous Sampling mode**") is not enabled. This allows for a threshold comparison on the average of a short burst of ADC samples.

# 19.5.6 LOW-PASS FILTER MODE

The Low-Pass Filter mode (ADMD = 100) acts similarly to the Average mode in how it handles samples (accumulates samples until CNT value is greater than or equal to RPT, then triggers threshold comparison. CNT does not reset once it is greater or equal to RPT. Thus CNT will be greater than RPT for all subsequent samples until CNT is reset by the user), but instead of a simple average, it performs a low-pass filter operation on all of the samples, reducing the effect of high-frequency noise on the average, then performs a threshold comparison on the results. (see Table 19-2 for a more detailed description of the mathematical operation). In this mode, the ADCRS bits determine the cut-off frequency of the low-pass filter (as demonstrated by Table 19-3).

#### 19.5.7 THRESHOLD COMPARISON

At the end of each computation:

- The conversion results are latched and held stable at the end-of-conversion.

- The error is calculated based on a difference calculation which is selected by the ADCALC<2:0> bits in the ADCON3 register. The value can be one of the following calculations (see Register 19-4 for more details):

- The first derivative of single measurements

- The CVD result in CVD mode

- The current result vs. a setpoint

- The current result vs. the filtered/average result

- The first derivative of the filtered/average value

- Filtered/average value vs. a setpoint

- The result of the calculation (ERR) is compared to the upper and lower thresholds, UTH<ADUTHH:ADUTHL> and

LTH<ADLTHH:ADLTHL> registers, to set the ADUTHR and ADLTHR flag bits. The threshold logic is selected by ADTMD<2:0> bits in the ADCON3 register. The threshold trigger option can be one of the following:

- Never interrupt

- Error is less than lower threshold

- Error is greater than or equal to lower threshold

- Error is between thresholds (inclusive)

- Error is outside of thresholds

- Error is less than or equal to upper threshold

- Error is greater than upper threshold

- Always interrupt regardless of threshold test results

- If the threshold condition is met, the threshold interrupt flag ADTIF is set.

Note 1: The threshold tests are signed operations.

**2:** If OV is set, a threshold interrupt is signaled.

| R/W-0/         | 0 R/W-0/0          | R/W-0/0                                                                               | R/W-0/0         | R/W/HC-0                                            | R/W-0/0                                  | R/W-0/0                 | R/W-0/0      |

|----------------|--------------------|---------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------|------------------------------------------|-------------------------|--------------|

| PSIS           |                    | CRS<2:0>                                                                              |                 | ACLR                                                |                                          | MD<2:0>                 |              |

| bit 7          |                    |                                                                                       |                 |                                                     |                                          |                         | bit          |

| Locordi        |                    |                                                                                       |                 |                                                     |                                          |                         |              |

| Legend:        | -  -   -  - :4     |                                                                                       | L :4            |                                                     |                                          |                         |              |

| R = Reada      |                    | W = Writable bit                                                                      |                 | •                                                   | nented bit, rea                          |                         |              |

|                | unchanged          | x = Bit is unkr                                                                       |                 | -n/n = Value at POR and BOR/Value at all other Rese |                                          |                         | other Resets |

| '1' = Bit is   | set                | '0' = Bit is clea                                                                     | ared            | HC = Bit is cle                                     | eared by hardv                           | vare                    |              |

| bit 7          | PSIS: ADC          | Previous Sample                                                                       | e Input Select  | bits                                                |                                          |                         |              |

|                | 1 = PREV i         | is the FLTR value                                                                     | at start-of-co  | nversion                                            |                                          |                         |              |

| h:+ C 4        |                    |                                                                                       |                 |                                                     | a at hita                                |                         |              |

| bit 6-4        |                    | ADC Accumulat                                                                         | ed Calculation  | i Right Shift Sei                                   | ect dits                                 |                         |              |

|                | If ADMD =          | . <u>00</u> :<br>ter time constant is 2 <sup>ADCRS</sup> , filter gain is 1:1         |                 |                                                     |                                          |                         |              |

|                |                    |                                                                                       | 01, 010 or 011: |                                                     |                                          |                         |              |

|                | The accun          | nulated value is ri                                                                   | ght-shifted by  | CRS (divided b                                      | by 2 <sup>ADCRS</sup> ) <sup>(1,2)</sup> |                         |              |

|                | Otherwise:         |                                                                                       |                 |                                                     |                                          |                         |              |

|                | Bits are ign       |                                                                                       |                 | (a)                                                 |                                          |                         |              |

| bit 3          |                    | CLR: A/D Accumulator Clear Command bit <sup>(3)</sup>                                 |                 |                                                     |                                          |                         |              |

|                | 1 = ACC, A         | 1 = ACC, AOV and CNT registers are cleared                                            |                 |                                                     |                                          |                         |              |

|                | 0 = Clearin        | earing action is complete (or not started)                                            |                 |                                                     |                                          |                         |              |

| bit 2-0        | MD<2:0>: /         | ADC Operating N                                                                       | lode Selectior  | ı bits <sup>(4)</sup>                               |                                          |                         |              |

| 011 = Burst Av |                    | Reserved                                                                              |                 |                                                     |                                          |                         |              |

|                |                    | .ow-pass Filter mode                                                                  |                 |                                                     |                                          |                         |              |

|                |                    |                                                                                       |                 |                                                     |                                          |                         |              |

|                | 010 = Aver         | umulate mode                                                                          |                 |                                                     |                                          |                         |              |

|                | 000 = Basi         |                                                                                       |                 |                                                     |                                          |                         |              |

| Note 1:        | To correctly cald  | ulate an average                                                                      | , the number    | of samples (set                                     | in RPT) must                             | be 2 <sup>ADCRS</sup> . |              |

|                |                    | o correctly calculate an average, the number<br>DCRS = 3 ' b111 is a reserved option. |                 |                                                     | ,                                        |                         |              |

| 3:             | This bit is cleare | ed by hardware w<br>delay may be mar                                                  | hen the accur   |                                                     | on is complete;                          | depending on            | oscillator   |

#### REGISTER 19-3: ADCON2: ADC CONTROL REGISTER 2

**4:** See Table 19-2 for Full mode descriptions.

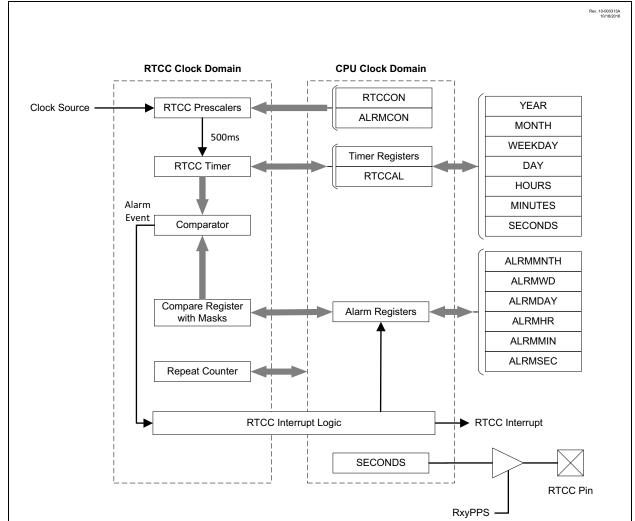

# 24.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The PIC16(L)F19155/56/75/76/85/86 family of devices is equipped with a Real-Time Clock and Calendar (RTCC) module, designed to maintain accurate time measurement for extended periods, with little or no intervention from the CPU. The module is optimized for low-power operation in order to provide extended battery life. The key features include:

- · Time: Hours, Minutes and Seconds

- 24-hour Format (Military Time)

- Calendar: Weekday, Date, Month and Year

- Year Range: 2000 to 2099

- Leap Year Correction

- Configurable Alarm

- BCD Format for Compact Firmware

- Half-second Synchronization and Visibility

- User Calibration with Auto-Adjust

- Multiple Clock Sources

- Low-Power Optimization

# 24.1 OPERATION

The RTCC consists of a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1st, 2000 to 23:59:59 on December 31st, 2099.

The hours use the 24-hour time format (military time) with no hardware provisions for regular time format (AM/PM). The clock provides a granularity of one second with additional visibility to the half-second.

The user has visibility to the half second field of the counter. This value is read-only and can be reset only by writing to the lower half of the SECONDS register.

#### 24.1.1 REGISTER INTERFACE

The RTCC register set is divided into the following categories:

# **Control Registers**

- RTCCON

- RTCCAL

- ALRMCON

- ALRMRPT

#### **Clock Value Registers**

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOURS

- MINUTES

- SECONDS

# **Alarm Value Registers**

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

**Note:** The WEEKDAY register is not automatically derived from the date, but it must be correctly set by the user.

The register interface for the RTCC and alarm values is implemented using the Binary Coded Decimal (BCD) format. This simplifies the firmware when using the module, as each of the digits is contained within its own 4-bit value (see **Section 24.1.3 "Clock Sources"** and Figure 24-3).

All timer registers containing a value of seconds or greater are writable. The user can configure the initial start date and time by writing the year, month, day, hour, minutes and seconds into the clock value registers and the timer will then proceed to count from the newly written values.

The RTCC module is enabled by setting the RTCEN bit (RTCCON<7>). Once the RTCC is enabled, the timer will continue incrementing, even while the clock value registers are being re-written. However, any time the SECONDS register is written to, all of the clock value prescalers are reset to '0'. This allows lower granularity of timer adjustments.

The Timer registers are updated in the same cycle as the WRITE instruction's execution by the CPU. The user must ensure that when RTCEN = 1, the updated registers will not be incremented at the same time. This can be accomplished in several ways:

- By checking the RTCSYNC bit (RTCCON<4>)

- By checking the preceding digits from which a carry can occur

- By updating the registers immediately following the seconds pulse (or alarm interrupt)

#### 24.1.2 WRITE LOCK

To perform a write to any of the RTCC timer registers, the RTCWREN bit must be set. To avoid accidental writes to the timer, it is recommended that the RTCWREN bit is kept clear at any other time.

The RTCEN bit can only be written to when RTCWREN = 1. A write attempt to this bit while RTCWREN = 0 will be ignored. The RTCC timer registers can be written with RTCEN = 0 or 1.

| Mode            | MODE<4:0> |       | Output                                                 | On creation                                               | Timer Control              |                       |                                 |

|-----------------|-----------|-------|--------------------------------------------------------|-----------------------------------------------------------|----------------------------|-----------------------|---------------------------------|

| wode            | <4:3>     | <2:0> | Operation                                              | Operation                                                 | Start                      | Reset                 | Stop                            |

|                 |           | 000   |                                                        | Software gate (Figure 27-4)                               | <b>ON =</b> 1              | _                     | ON = 0                          |

|                 |           | 001   | Period<br>Pulse                                        | Hardware gate, active-high<br>(Figure 27-5)               | ON = 1 and<br>TMRx_ers = 1 | _                     | ON = 0 or<br>TMRx_ers = 0       |

|                 |           | 010   | T uise                                                 | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _                     | ON = 0 or<br>TMRx_ers = 1       |

| Free<br>Running | 00        | 011   |                                                        | Rising or falling edge Reset                              |                            | TMRx_ers              |                                 |

| Period          | 00        | 100   | Period                                                 | Rising edge Reset (Figure 27-6)                           |                            | TMRx_ers ↑            | ON = 0                          |

|                 |           | 101   | Pulse                                                  | Falling edge Reset                                        |                            | TMRx_ers ↓            |                                 |

|                 |           | 110   | with<br>Hardware                                       | Low level Reset                                           | ON = 1                     | TMRx_ers = 0          | ON = 0 or<br>TMRx_ers = 0       |

|                 |           | 111   | Reset                                                  | High level Reset (Figure 27-7)                            |                            | TMRx_ers = 1          | ON = 0 or<br>TMRx_ers = 1       |

|                 |           | 000   | One-shot                                               | Software start (Figure 27-8)                              | <b>ON =</b> 1              | _                     |                                 |

| One-shot        | 01        | 001   | Edge                                                   | Rising edge start (Figure 27-9)                           | ON = 1 and<br>TMRx_ers ↑   | _                     |                                 |

|                 |           | 010   | triggered<br>start                                     | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | —                     |                                 |

|                 |           | 011   | (Note 1)                                               | Any edge start                                            | ON = 1 and<br>TMRx_ers     |                       | ON = 0<br>or<br>Next clock      |

|                 |           | 100   | Edge<br>triggered<br>start<br>and<br>hardware<br>Reset | Rising edge start and<br>Rising edge Reset (Figure 27-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑            | after<br>TMRx = PRx<br>(Note 2) |

|                 |           | 101   |                                                        | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers $\downarrow$ |                                 |

|                 |           | 110   |                                                        | Rising edge start and<br>Low level Reset (Figure 27-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0          |                                 |

|                 |           | 111   | (Note 1)                                               | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1          |                                 |

|                 |           | 000   |                                                        | Rese                                                      | rved                       |                       | -                               |

|                 |           | 001   | Edge                                                   | Rising edge start<br>(Figure 27-12)                       | ON = 1 and<br>TMRx_ers ↑   | _                     | ON = 0<br>or                    |

| Mono-stable     |           | 010   | triggered<br>start                                     | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                     | Next clock<br>after             |

|                 |           | 011   | (Note 1)                                               | Any edge start                                            | ON = 1 and<br>TMRx_ers     | -                     | TMRx = PRx<br>(Note 3)          |

| Reserved        | 10        | 100   |                                                        | Rese                                                      | rved                       |                       |                                 |

| Reserved        |           | 101   |                                                        | Rese                                                      | rved                       |                       |                                 |

| One-shot        |           | 110   | Level<br>triggered                                     | High level start and<br>Low level Reset (Figure 27-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0          | ON = 0 or                       |

|                 |           | 111   | start<br>and<br>hardware                               | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1          | Held in Reset<br>(Note 2)       |

|                 |           |       | Reset                                                  |                                                           |                            |                       |                                 |

# TABLE 27-1: TIMER2/4 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

PIC16(L)F19155/56/75/76/85/86

# 31.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 31-12.

#### 31.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External input

#### 31.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

#### 31.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT\_sync

- Timer2 TMR2\_postscaled

- CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 31-6).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

# 31.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- · CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

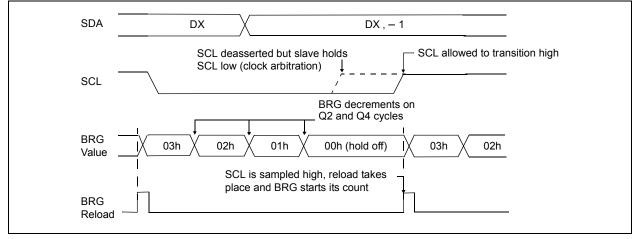

#### 33.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 33-25).

#### FIGURE 33-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 33.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |  |  |

|-------|--------------------------------------------|--|--|

|       | writing to the lower five bits of SSPxCON2 |  |  |

|       | is disabled until the Start condition is   |  |  |

|       | complete.                                  |  |  |

#### **Register Definitions: MSSPx Control** 33.8

# REGISTER 33-1: SSPxSTAT: SSPx STATUS REGISTER

| REGISTI<br>R/W-0 |                                                                                                          | R/HS/HC-0                                                                                                                                                                                                                                                                                           | R/HS/HC-0                                                  | R/HS/HC-0                      | R/HS/HC-0                                | R/HS/HC-0           | R/HS/HC-0         |

|------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------|---------------------|-------------------|

| SMP              | (4)                                                                                                      | D/A                                                                                                                                                                                                                                                                                                 | P <sup>(2)</sup>                                           | S <sup>(2)</sup>               | R/W                                      | UA                  | BF                |

| bit 7            |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            | _                              |                                          |                     | bit 0             |

|                  |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            |                                |                                          |                     |                   |

| Legend:          |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            |                                |                                          |                     |                   |

| R = Reada        | ble bit                                                                                                  | W = Writable bit                                                                                                                                                                                                                                                                                    |                                                            | U = Unimpleme                  | nted bit, read as '0                     | 2                   |                   |

| u = Bit is u     | nchanged                                                                                                 | x = Bit is unknow                                                                                                                                                                                                                                                                                   | vn                                                         | -n/n = Value at                | POR and BOR/Val                          | ue at all other Res | sets              |

| '1' = Bit is s   | set                                                                                                      | '0' = Bit is cleare                                                                                                                                                                                                                                                                                 | ed                                                         | HS/HC = Hardv                  | vare set/clear                           |                     |                   |

| bit 7            | SPI Master mod                                                                                           | Input Sample bit<br><u>te:</u><br>ampled at end of o                                                                                                                                                                                                                                                | data output time                                           |                                |                                          |                     |                   |

|                  | SPI Slave mode<br>SMP must be c<br>In I <sup>2</sup> C Master of<br>1 = Slew rate c                      | control disabled for                                                                                                                                                                                                                                                                                | s used in Slave r<br>Standard Speed                        | node<br>d mode (100 kHz        | and 1 MHz)                               |                     |                   |

| bit 6            |                                                                                                          | control enabled for<br>Edge Select bit (                                                                                                                                                                                                                                                            | •                                                          | . , ,                          |                                          |                     |                   |

| bit o            | In SPI Master o<br>1 = Transmit oc<br>0 = Transmit oc<br>In I <sup>2</sup> C mode onl<br>1 = Enable inpu | r Slave mode:<br>curs on transition<br>curs on transition                                                                                                                                                                                                                                           | from active to Id<br>from Idle to activ<br>sholds are comp | e clock state<br>e clock state | specification                            |                     |                   |

| bit 5            | 1 = Indicates th                                                                                         | <ul> <li>D/A: Data/Address bit (I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                                                       |                                                            |                                |                                          |                     |                   |

| bit 4            | 1 = Indicates th                                                                                         | <ul> <li>P: Stop bit<sup>(2)</sup></li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul>     |                                                            |                                |                                          |                     |                   |

| bit 3            | 1 = Indicates th                                                                                         | <ul> <li>S: Start bit <sup>(2)</sup></li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul> |                                                            |                                |                                          |                     |                   |

| bit 2            | This bit holds th<br>next Start bit, Sl<br>In I <sup>2</sup> C Slave mo<br>1 = Read<br>0 = Write         | top bit, or not ACK<br>i <u>de:</u>                                                                                                                                                                                                                                                                 | ion following the                                          | last address mat               | ch. This bit is only v                   | valid from the add  | ress match to the |

|                  | 0 = Transmit is                                                                                          | s in progress<br>s not in progress                                                                                                                                                                                                                                                                  | SEN, PEN, RCE                                              | N or ACKEN will i              | ndicate if the MSS                       | P is in IDLE mode   |                   |

| bit 1            | 1 = Indicates th                                                                                         | OR-ing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in IDLE mode.<br><b>UA:</b> Update Address bit (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSPxADD register<br>0 = Address does not need to be updated    |                                                            |                                |                                          |                     |                   |

| bit 0            | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C m</u><br>1 = Data transm                                  | nd I <sup>2</sup> C modes):<br>mplete, SSPxBUF<br>t complete, SSPxE<br>lode only):<br>nit in progress (doe                                                                                                                                                                                          | UF is empty<br>es not include the                          |                                | its), SSPxBUF is fi<br>s), SSPxBUF is em |                     |                   |

| Note 1:<br>2:    | Polarity of clock state<br>This bit is cleared on                                                        | •                                                                                                                                                                                                                                                                                                   |                                                            | •                              |                                          |                     |                   |

# PIC16(L)F19155/56/75/76/85/86

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                      |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow PC<14:11>$                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                    |

| Operands:        | $0 \leq k \leq 255$                                                                                                |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                         |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

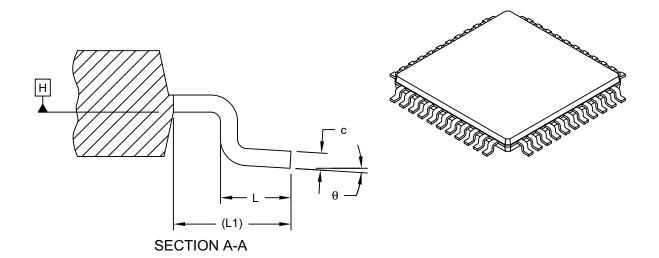

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Number of Leads          | N  | 44          |      |      |

| Lead Pitch               | е  | 0.80 BSC    |      |      |

| Overall Height           | A  | -           | -    | 1.20 |

| Standoff                 | A1 | 0.05        | -    | 0.15 |

| Molded Package Thickness | A2 | 0.95        | 1.00 | 1.05 |

| Overall Width            | E  | 12.00 BSC   |      |      |

| Molded Package Width     | E1 | 10.00 BSC   |      |      |

| Overall Length           | D  | 12.00 BSC   |      |      |

| Molded Package Length    | D1 | 10.00 BSC   |      |      |

| Lead Width               | b  | 0.30        | 0.37 | 0.45 |

| Lead Thickness           | С  | 0.09        | -    | 0.20 |