Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19155t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

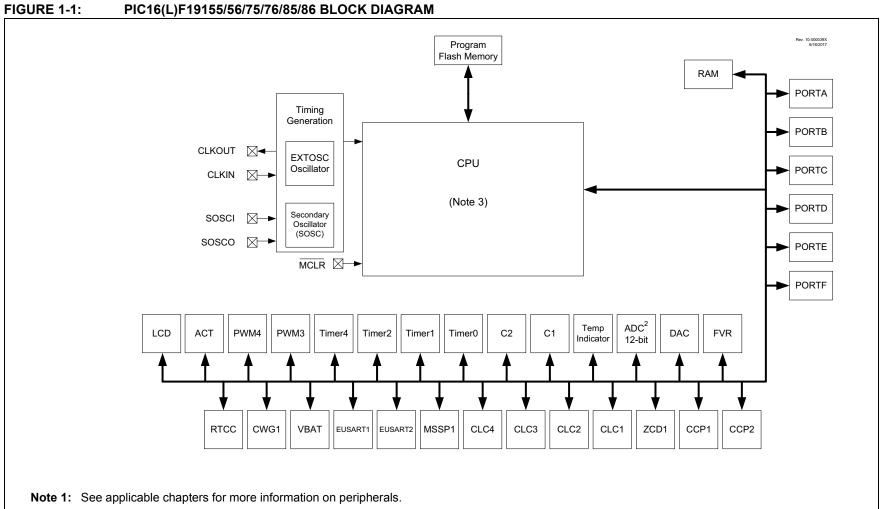

- 2: See Table 1-1 for peripherals available on specific devices.

- 3: See Figure 3-1.

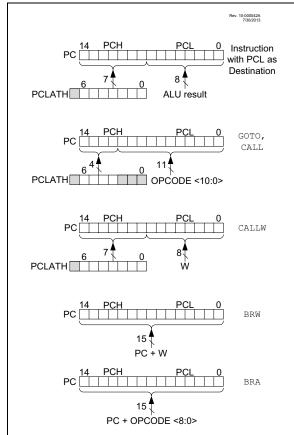

## 4.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-3 shows the five situations for the loading of the PC.

FIGURE 4-3: LOADING OF PC IN DIFFERENT SITUATIONS

## 4.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

## 4.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 4.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

## 4.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 + the signed value of the operand of the BRA instruction.

## REGISTER 12-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| U-0     | $R/W^{(3)}-q/q^{(1)}$ $R/W^{(3)}-q/q^{(1)}$ $R/W^{(3)}-q/q^{(1)}$ | U-0 | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |

|---------|-------------------------------------------------------------------|-----|----------------------------------------|----------------------------------------|----------------------------------------|

| -       | WDTCS<2:0>                                                        | -   |                                        | WINDOW<2:0>                            |                                        |

| bit 7   |                                                                   |     |                                        |                                        | bit 0                                  |

|         |                                                                   |     |                                        |                                        |                                        |

| Legend: |                                                                   |     |                                        |                                        |                                        |

| Legend | •  |

|--------|----|

| Legenu | •• |

| -      |    |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| Dit / Unimplemented: Read as 0 | bit 7 | Unimplemented: Read as '0' |

|--------------------------------|-------|----------------------------|

|--------------------------------|-------|----------------------------|

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

111 = Reserved

- 010 = SOSC 32.768 kHz

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 010 62.5 3                      |                                   |

| 001         | 001 75 25                       |                                   |

| 000         | 87.5                            | 12.5                              |

Note 1: If WDTCCS <2:0> in CONFIG3 = 111, the Reset value of WDTCS<2:0> is 000.

2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3 register.

3: If WDTCCS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

4: If WDTCWS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

| R/W-0/0                               | R/W-0/0                                 | R/W-0/0              | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------------------------------|-----------------------------------------|----------------------|-------------------------------------------------------|---------|---------|---------|---------|

| WPUA7                                 | WPUA6                                   | WPUA5 <sup>(2)</sup> | WPUA4                                                 | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| bit 7                                 |                                         |                      |                                                       |         |         |         | bit 0   |

|                                       |                                         |                      |                                                       |         |         |         |         |

| Legend:                               |                                         |                      |                                                       |         |         |         |         |

| R = Readable                          | R = Readable bit W = Writable bit       |                      | U = Unimplemented bit, read as '0'                    |         |         |         |         |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |                      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |

| '1' = Bit is set '0' = Bit is cleared |                                         |                      |                                                       |         |         |         |         |

#### REGISTER 14-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **2:** Bit not used when  $\overline{VBATEN} = 0$ .

## REGISTER 14-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| ODCA7   | ODCA6   | —   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | ODCA<7:6>: PORTA Open-Drain Enable bits                                     |

|---------|-----------------------------------------------------------------------------|

|         | For RA<7:6> pins, respectively                                              |

|         | 1 = Port pin operates as open-drain drive (sink current only)               |

|         | 0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 5   | Unimplemented: Read as '0'                                                  |

| bit 4-0 | ODCA<4:0>: PORTA Open-Drain Enable bits                                     |

|         | For RA<4:0> pins, respectively                                              |

|         | 1 = Port pin operates as open-drain drive (sink current only)               |

|         | 0 = Port pin operates as standard push-pull drive (source and sink current) |

## REGISTER 19-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|-----|-----|-----|-----|---------|

| PPOL    | IPEN    | GPOL    | -   | -   | —   | —   | DSEN    |

| bit 7   |         |         |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7 **PPOL:** Precharge Polarity bit If PRE>0x00:

| PPOL | Action During 1st Precharge Stage  |                                    |  |  |  |  |

|------|------------------------------------|------------------------------------|--|--|--|--|

| FFUL | External (selected analog I/O pin) | Internal (AD sampling capacitor)   |  |  |  |  |

| 1    | Connected to VDD                   | C <sub>HOLD</sub> connected to Vss |  |  |  |  |

| 0    | Connected to Vss                   | C <sub>HOLD</sub> connected to VDD |  |  |  |  |

- Otherwise:

- The bit is ignored

#### bit 6 IPEN: A/D Inverted Precharge Enable bit

#### If DSEN = 1

- 1 = The precharge and guard signals in the second conversion cycle are the opposite polarity of the first cycle

- 0 = Both Conversion cycles use the precharge and guards specified by ADPPOL and ADGPOL

## Otherwise:

The bit is ignored

#### bit 5 **GPOL:** Guard Ring Polarity Selection bit

- 1 = ADC guard Ring outputs start as digital high during Precharge stage

- 0 = ADC guard Ring outputs start as digital low during Precharge stage

#### bit 4-1 Unimplemented: Read as '0'

#### bit 0 DSEN: Double-sample enable bit

- 1 = Two conversions are performed on each trigger. Data from the first conversion appears in PREV

- 0 = One conversion is performed for each trigger

| R/W-0/                                                                 | 0 R/W-0/0          | R/W-0/0                              | R/W-0/0                                                       | R/W/HC-0                           | R/W-0/0                                  | R/W-0/0                 | R/W-0/0    |  |  |

|------------------------------------------------------------------------|--------------------|--------------------------------------|---------------------------------------------------------------|------------------------------------|------------------------------------------|-------------------------|------------|--|--|

| PSIS                                                                   |                    | CRS<2:0>                             |                                                               | ACLR                               |                                          | MD<2:0>                 |            |  |  |

| bit 7                                                                  |                    |                                      |                                                               |                                    |                                          |                         | bit        |  |  |

| Locordi                                                                |                    |                                      |                                                               |                                    |                                          |                         |            |  |  |

| Legend:                                                                | -  -   -  - :4     |                                      | L :4                                                          |                                    |                                          |                         |            |  |  |

| R = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknown |                    |                                      |                                                               | U = Unimplemented bit, read as '0' |                                          |                         |            |  |  |

|                                                                        | 0                  |                                      | x = Bit is unknown -n/n = Value at POR and BOR/Value at all c |                                    |                                          |                         |            |  |  |

| '1' = Bit is                                                           | set                | '0' = Bit is clea                    | ared                                                          | HC = Bit is cle                    | eared by hardv                           | vare                    |            |  |  |

| bit 7                                                                  | PSIS: ADC          | Previous Sample                      | e Input Select                                                | bits                               |                                          |                         |            |  |  |

|                                                                        | 1 = PREV i         | is the FLTR value                    | at start-of-co                                                | nversion                           |                                          |                         |            |  |  |

| h:+ C 4                                                                |                    |                                      |                                                               |                                    | a at hita                                |                         |            |  |  |

| bit 6-4                                                                |                    | ADC Accumulat                        | ed Calculation                                                | i Right Shift Sei                  | ect dits                                 |                         |            |  |  |

|                                                                        | If ADMD =          | <u>100</u> :<br>ilter time constant  | tic 2ADCRS fil                                                | ter agin is 1·1                    |                                          |                         |            |  |  |

|                                                                        |                    | 001, 010 or 01                       |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        | The accun          | nulated value is ri                  | ght-shifted by                                                | CRS (divided b                     | by 2 <sup>ADCRS</sup> ) <sup>(1,2)</sup> |                         |            |  |  |

|                                                                        | Otherwise:         |                                      |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        | Bits are ign       |                                      |                                                               | (a)                                |                                          |                         |            |  |  |

| bit 3                                                                  |                    | Accumulator Cle                      |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        | 1 = ACC, A         | OV and CNT reg                       | isters are clea                                               | ared                               |                                          |                         |            |  |  |

|                                                                        | 0 = Clearin        | g action is comple                   | ete (or not sta                                               | rted)                              |                                          |                         |            |  |  |

| bit 2-0                                                                | MD<2:0>: /         | ADC Operating N                      | lode Selectior                                                | ı bits <sup>(4)</sup>              |                                          |                         |            |  |  |

|                                                                        | 111-101 =          | Reserved                             |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        |                    | -pass Filter mode                    |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        |                    | t Average mode                       |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        | 010 = Aver         | umulate mode                         |                                                               |                                    |                                          |                         |            |  |  |

|                                                                        | 000 = Basi         |                                      |                                                               |                                    |                                          |                         |            |  |  |

| Note 1:                                                                | To correctly cald  | culate an average                    | , the number                                                  | of samples (set                    | in RPT) must                             | be 2 <sup>ADCRS</sup> . |            |  |  |

|                                                                        |                    | 11 is a reserved                     |                                                               |                                    | ,                                        |                         |            |  |  |

| 3:                                                                     | This bit is cleare | ed by hardware w<br>delay may be mar | hen the accur                                                 |                                    | on is complete;                          | depending on            | oscillator |  |  |

## REGISTER 19-3: ADCON2: ADC CONTROL REGISTER 2

**4:** See Table 19-2 for Full mode descriptions.

#### **REGISTER 19-9: ADPREL: ADC PRECHARGE TIME CONTROL REGISTER (LOW BYTE)**

| R/W-0/0                           | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                    | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|-----------------------------------|---------|--------------------|---------|--------------------------------------------|------------------|--------------|---------|

|                                   |         |                    | PRE     | <7:0>                                      |                  |              |         |

| bit 7                             |         |                    |         |                                            |                  |              | bit 0   |

|                                   |         |                    |         |                                            |                  |              |         |

| Legend:                           |         |                    |         |                                            |                  |              |         |

| R = Readable bit W = Writable bit |         |                    | bit     | U = Unimpler                               | nented bit, read | d as '0'     |         |

| u = Bit is unch                   | anged   | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all o |                  | other Resets |         |

| '1' = Bit is set                  |         | '0' = Bit is clea  | ared    |                                            |                  |              |         |

bit 7-0 **PRE<7:0>**: Precharge Time Select bits See Table 19-4.

#### REGISTER 19-10: ADPREH: ADC PRECHARGE TIME CONTROL REGISTER (HIGH BYTE)

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

|       | —   | —   |         |         | PRE<12:8> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **PRE<12:8>:** Precharge Time Select bits<sup>(1)</sup> See Table 19-4.

**Note:** If PRE is not equal to '0', then ADACQ = b' 0000000 means Acquisition time is 256 clocks of the selected ADC clock.

## TABLE 19-4: PRECHARGE TIME

| ADPRE            | Precharge time                            |

|------------------|-------------------------------------------|

| 1 1111 1111 1111 | 8191 clocks of the selected ADC clock     |

| 1 1111 1111 1110 | 8190 clocks of the selected ADC clock     |

| 1 1111 1111 1101 | 8189 clocks of the selected ADC clock     |

|                  |                                           |

| 0 0000 0000 0010 | 2 clocks of the selected ADC clock        |

| 0 0000 0000 0001 | 1 clock of the selected ADC clock         |

| 0 0000 0000 0000 | Not included in the data conversion cycle |

© 2017 Microchip Technology Inc.

## 20.2.1 CALIBRATION

## 20.2.1.1 Single-Point Calibration

Single-point calibration is performed by application software using Equation 20-1 and the assumed Mt. A reading of VTSENSE at a known temperature is taken, and the theoretical temperature is calculated by temporarily setting TOFFSET = 0. Then TOFFSET is computed as the difference of the actual and calculated temperatures. Finally, TOFFSET is stored in nonvolatile memory within the device, and is applied to future readings to gain a more accurate measurement.

## 20.2.1.2 Higher-Order Calibration

If the application requires more precise temperature measurement, additional calibrations steps will be necessary. For these applications, two-point or three-point calibration is recommended.

| Note 1: | The TOFFSET value may be determined by the user with a temperature test.                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | Although the measurement range is $-40^{\circ}$ C to $+125^{\circ}$ C, due to the variations in offset error, the single-point uncalibrated calculated TSENSE value may indicate a temperature from $-140^{\circ}$ C to $+225^{\circ}$ C, before the calibration offset is applied. |

| 3:      | The user must take into consideration<br>self-heating of the device at different<br>clock frequencies and output pin loading.<br>For package related thermal characteris-                                                                                                           |

tics information, refer to Table 39-13.

## 20.2.2 TEMPERATURE RESOLUTION

The resolution of the ADC reading, Ma (°C/count), depends on both the ADC resolution N and the reference voltage used for conversion, as shown in Equation 20-2. It is recommended to use the smallest VREF value, such as 2.048 FVR reference voltage, instead of VDD.

Note: Refer to Table 39-17 for FVR reference voltage accuracy.

## EQUATION 20-2: TEMPERATURE RESOLUTION (°C/LSb)

$$Ma = \frac{V_{REF}}{2^{N}} \times Mt$$

$$Ma = \frac{\frac{V_{REF}}{2^{N}}}{Mv}$$

Where:

Mv = sensor voltage sensitivity (V/°C)

VREF = Reference voltage of the ADC module (in Volts)

N = Resolution of the ADC

The typical Mv value for a single diode is approximately -1.267 to -1.32 mV/C.

The typical Mv value for a stack of two diodes (Low Range setting) is approximately -2.533 mV/C.

The typical Mv value for a stack of three diodes (High range setting) is approximately -3.8 mV/C.

## 20.3 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait a minimum of 25  $\mu$ s for the ADC value to settle, after the ADC input multiplexer is connected to the temperature indicator output, before the conversion is performed.

## 20.4 Minimum Operating VDD

When the temperature circuit is operated in Low range, the device may be operated at any operating voltage that is within specifications. When the temperature circuit is operated in High range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 20-1 shows the recommended minimum  $V \mbox{\scriptsize DD}$  vs. Range setting.

TABLE 20-1: RECOMMENDED VDD vs. RANGE

| Min.VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|--------------------|---------------------|

| (High Range)       | (Low Range)         |

| ≥ 2.5              | ≥ 1.8               |

## 20.5 Temperature Indicator Range

The temperature indicator circuit operates in either High or Low range. The High range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range. High range requires a higher-bias voltage to operate and thus, a higher VDD is needed. The Low range is selected by clearing the TSRNG bit of the FVRCON register. The Low range generates a lower sensor voltage and thus, a lower VDD voltage is needed to operate the circuit. The output voltage of the sensor is the highest value at  $-40^{\circ}$ C and the lowest value at  $+125^{\circ}$ C.

- **High Range:** The High range is used in applications with the reference for the ADC, VREF = 2.048V. This range may not be suitable for battery-powered applications.

- Low Range: This mode is useful in applications in which the VDD is too low for high-range operation. The VDD in this mode can be as low as 1.8V. VDD must, however, be at least 0.5V higher than the maximum sensor voltage depending on the expected low operating temperature.

## 20.6 DIA Information

DIA data provide ADC readings at one operating temperature. DIA data is taken during factory testing and stored within the device. The 90°C reading alone allows single-point calibration as described in Section 20.2.1, Calibration, by solving Equation 20-1 for TOFFSET.

Refer to **Section 6.0 "Device Information Area"** for more information on the data stored in the DIA and how to access them.

**Note:** The lower temperature range (e.g., - 40°C) will suffer in accuracy because temperature conversion must extrapolate below the reference points, amplifying any measurement errors.

## TABLE 20-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFVR<1:0> |       | ADFVF | R<1:0> | 285                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are unused by the temperature indicator module.

| U-0                                | R/W-x | R/W-x     | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

|------------------------------------|-------|-----------|-------|-----------------------------------------|-------|-------|-------|--|--|

| _                                  |       | MINH<2:0> |       | MINL<3:0>                               |       |       |       |  |  |

| bit 7                              |       |           |       |                                         |       |       | bit 0 |  |  |

|                                    |       |           |       |                                         |       |       |       |  |  |

| Legend:                            |       |           |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |           | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |           |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

## REGISTER 24-8: MINUTES<sup>(1)</sup>: MINUTE VALUE REGISTER

bit 7 Unimplemented: Read as '0'

| bit 6-4 <b>MINH&lt;2:0&gt;:</b> Binary Coded Decimal value of minutes '10' digit; valid values from 0 to 5 |

|------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------|

bit 3-0 MINL<3:0>: Binary Coded Decimal value of minutes '1' digit; valid values from 0 to 9

**Note 1:** Writes to the MINUTE registers are only allowed when RTCWREN = 1.

## REGISTER 24-9: SECONDS<sup>(1)</sup>: SECOND VALUE REGISTER

| U-0   | R/W-x | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-------|-----------|-------|-------|-------|-------|-------|

| —     |       | SECH<2:0> |       |       | SECL  | <3:0> |       |

| bit 7 |       |           |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 SECH<2:0>: Binary Coded Decimal value of seconds '10' digit; valid values from 0 to 5

bit 3-0 SECL<3:0>: Binary Coded Decimal value of seconds '1' digit; valid values from 0 to 9

**Note 1:** Writes to the SECOND registers are only allowed when RTCWREN = 1.

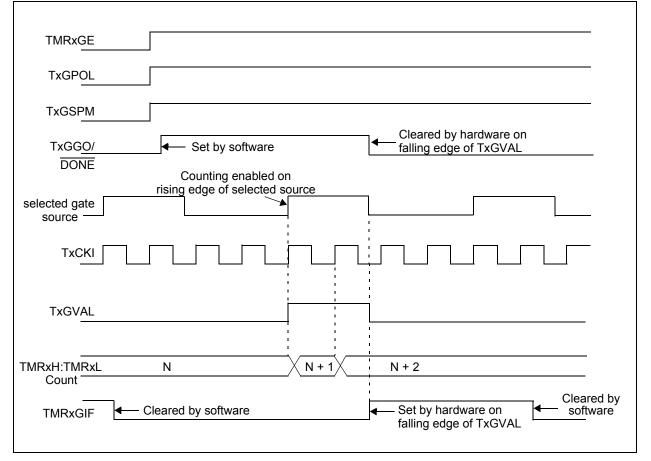

| FIGURE 26-4:           | TIMER1 GATE TOGGLE MODE                                                                                                                                            |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                    |

| TxGPOL                 |                                                                                                                                                                    |

| TxGT <u>M</u>          |                                                                                                                                                                    |

| selected<br>gate input |                                                                                                                                                                    |

| ТхСКІ                  |                                                                                                                                                                    |

| TxGVAL                 |                                                                                                                                                                    |

| TMRxH:TMRxL N<br>Count | $\frac{1}{N+1} \times \frac{1}{N+2} \times \frac{1}{N+3} \times \frac{1}{N+4} \times \frac{1}{N+5} \times \frac{1}{N+6} \times \frac{1}{N+7} \times \frac{1}{N+8}$ |

## FIGURE 26-5: TIMER1 GATE SINGLE-PULSE MODE

#### 27.5.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level -Triggered One-Shot mode the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

## REGISTER 28-13: SMTxCPWL: SMT CAPTURED PULSE WIDTH REGISTER – LOW BYTE

| R-x/x            | R-x/x | R-x/x             | R-x/x | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|------------------|-------|-------------------|-------|----------------|------------------|------------------|--------------|

|                  |       |                   | SMTxC | CPW<7:0>       |                  |                  |              |

| bit 7            |       |                   |       |                |                  |                  | bit 0        |

|                  |       |                   |       |                |                  |                  |              |

| Legend:          |       |                   |       |                |                  |                  |              |

| R = Readable     | bit   | W = Writable I    | oit   | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged | x = Bit is unkn   | own   | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared  |                |                  |                  |              |

bit 7-0 SMTxCPW<7:0>: Significant bits of the SMT PW Latch – Low Byte

#### REGISTER 28-14: SMTxCPWH: SMT CAPTURED PULSE WIDTH REGISTER - HIGH BYTE

| R-x/x            | R-x/x | R-x/x                                                                   | R-x/x  | R-x/x       | R-x/x           | R-x/x | R-x/x |

|------------------|-------|-------------------------------------------------------------------------|--------|-------------|-----------------|-------|-------|

|                  |       |                                                                         | SMTxCP | W<15:8>     |                 |       |       |

| bit 7            |       |                                                                         |        |             |                 |       | bit 0 |

|                  |       |                                                                         |        |             |                 |       |       |

| Legend:          |       |                                                                         |        |             |                 |       |       |

| D - Deedeble bit |       | $\lambda \lambda = \lambda \lambda r t t t t t t t t t t t t t t t t t$ |        | معاميمه الم | nonted bit read | 1 (0) |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<15:8>: Significant bits of the SMT PW Latch – High Byte

#### REGISTER 28-15: SMTxCPWU: SMT CAPTURED PULSE WIDTH REGISTER – UPPER BYTE

| R-x/x | R-x/x          | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x |  |  |

|-------|----------------|-------|-------|-------|-------|-------|-------|--|--|

|       | SMTxCPW<23:16> |       |       |       |       |       |       |  |  |

| bit 7 |                |       |       |       |       |       | bit 0 |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<23:16>: Significant bits of the SMT PW Latch – Upper Byte

## 29.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more details.

The CCP output can also be used as an input for other peripherals.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 29.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See **Section 26.0 "Timer1 Module with Gate Control"** for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 29.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to Section 19.2.6 "ADC Conversion Procedure (Basic Mode)" for more information.

| Note: | Removing the match condition by            |

|-------|--------------------------------------------|

|       | changing the contents of the CCPRxH        |

|       | and CCPRxL register pair, between the      |

|       | clock edge that generates the              |

|       | Auto-conversion Trigger and the clock      |

|       | edge that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring          |

#### 29.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

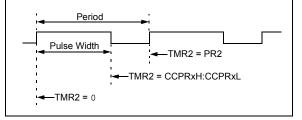

#### 29.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 29-3 shows a typical waveform of the PWM signal.

#### 29.3.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 29-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 29-3: CCP P

CCP PWM OUTPUT SIGNAL

| R/C/HS-0/0       | 0 R/C/HS-0/0                                                                                                                                                                                                                                                                                                    | R/W-0/0                                                                                                                                                 | R/W-0/0                                                                                                                                                                       | R/W-0/0                                                                                                                                                                                                                 | R/W-0/0                         | R/W-0/0                                               | R/W-0/0                                     |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------|---------------------------------------------|--|

| WCOL             | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                            | SSPEN                                                                                                                                                   | CKP                                                                                                                                                                           |                                                                                                                                                                                                                         | SSP                             | M<3:0>                                                |                                             |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                                                                                         |                                 |                                                       | bit (                                       |  |

|                  |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                                                                                         |                                 |                                                       |                                             |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                                                                                         |                                 |                                                       |                                             |  |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                             | W = Writable bit                                                                                                                                        |                                                                                                                                                                               | U = Unimplemented                                                                                                                                                                                                       | bit, read as '0'                |                                                       |                                             |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                                                                           | x = Bit is unknown                                                                                                                                      | ı                                                                                                                                                                             | -n/n = Value at POR                                                                                                                                                                                                     | and BOR/Value                   | e at all other Resets                                 |                                             |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                 | '0' = Bit is cleared                                                                                                                                    |                                                                                                                                                                               | HS = Bit is set by har                                                                                                                                                                                                  | rdware                          | C = User cleared                                      |                                             |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                                                                                               | y)<br>smitting the previous wor                                                                                                                                                                                         | d (must be clear                | red in software)                                      |                                             |  |

| bit 6            | <u>In SPI mode:</u><br>1 = A new byte<br>Overflow c:<br>setting over<br>SSPxBUF no<br>0 = No overflow<br><u>In I<sup>2</sup>C mode:</u><br>1 = A byte is re                                                                                                                                                     | an only occur in Slave<br>rflow. In Master mode<br>register (must be clea<br>w<br>eceived while the SS<br>leared in software).                          | SSPxBUF registe<br>e mode. In Slave<br>, the overflow bit i<br>ared in software).                                                                                             | er is still holding the previc<br>mode, the user must rea<br>s not set since each new<br>is still holding the previ                                                                                                     | d the SSPxBUF<br>reception (and | F, even if only transmit<br>transmission) is initiate | ting data, to avoid<br>ad by writing to the |  |

| bit 5            | In both modes, v<br>In <u>SPI mode</u> :<br>1 = Enables se<br>0 = Disables se<br>In <u>I<sup>2</sup>C mode</u> :<br>1 = Enables the                                                                                                                                                                             | rial port and configure<br>erial port and configu                                                                                                       | llowing pins mus<br>es SCK, SDO, SE<br>ures these pins a<br>gures the SDA an                                                                                                  | d SCL pins as the source                                                                                                                                                                                                | of the serial por               | t pins <sup>(2)</sup>                                 |                                             |  |

| bit 4            | 0 = Idle state for<br>In I <sup>2</sup> C Slave moo<br>SCL release con<br>1 = Enable clock                                                                                                                                                                                                                      | clock is a high level<br>clock is a low level<br><u>de:</u><br>htrol<br>(ow (clock stretch). (<br>ode:                                                  |                                                                                                                                                                               | lata setup time.)                                                                                                                                                                                                       |                                 |                                                       |                                             |  |

| bit 3-0          | 1111 = I <sup>2</sup> C Slaw<br>1110 = I <sup>2</sup> C Slaw<br>1101 = Reserve<br>1000 = Reserve<br>1011 = I <sup>2</sup> C firmv<br>1010 = SPI Mas<br>1001 = Reserve<br>1000 = I <sup>2</sup> C Mast<br>0111 = I <sup>2</sup> C Slaw<br>0110 = SPI Slaw<br>0100 = SPI Slaw<br>0011 = SPI Mas<br>0001 = SPI Mas | e mode, 7-bit addres<br>d<br>vare controlled Mast<br>ter mode, clock = Fc<br>d<br>ter mode, clock = Fc<br>e mode, 10-bit addres<br>e mode, 7-bit addres | ers with Start and<br>swith Start and<br>er mode (slave in<br>bsc/(4 * (SSPxAI<br>ss<br>K pin, <u>SS</u> pin cor<br>K pin, <u>SS</u> pin cor<br>Z_match/2<br>bsc/64<br>bsc/16 | d Stop bit interrupts ena<br>Stop bit interrupts enab<br>dle)<br>DD+1)) <sup>(5)</sup><br>.DD+1)) <sup>(4)</sup><br>ntrol disabled, <del>SS</del> can b                                                                 | led                             | bin                                                   |                                             |  |

| 2:               | In Master mode, the ov<br>When enabled, these p<br>RxyPPS to select the p                                                                                                                                                                                                                                       | verflow bit is not set<br>bins must be properly<br>bins.                                                                                                | since each new r<br>/ configured as ii                                                                                                                                        | ew reception (and transmission) is initiated by writing to the SSPxBUF regist<br>as input or output. Use SSPxSSPPS, SSPxCLKPPS, SSPxDATPPS, and<br>ed as inputs. Use SSPxCLKPPS, SSPxDATPPS, and RxyPPS to select the p |                                 |                                                       |                                             |  |

#### 3: When enabled, the SDA and SCL pins must be configured as inputs. Use SSPxCLKPPS, SSPxDATPPS, and RxyPPS to select the pins.

- 4: SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

5: SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

| R-0/0                | R/W-0/0                                                                                                                                                                                                                                                                                          | R/W-0/0                                                                                                                                                                            | R/W-0/0                                                                                                                                 | R/W-0/0                                                      | R/W-0/0                                                        | R/W-0/0             | R/W-0/0          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|---------------------|------------------|

| ACKTIM <sup>(3</sup> | <sup>3)</sup> PCIE                                                                                                                                                                                                                                                                               | SCIE                                                                                                                                                                               | BOEN                                                                                                                                    | SDAHT                                                        | SBCDE                                                          | AHEN                | DHEN             |

| bit 7                | ·                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                  |                                                                                                                                         | ·                                                            |                                                                |                     | bit              |

| Legend:              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                         |                                                              |                                                                |                     |                  |

| R = Readab           | e bit                                                                                                                                                                                                                                                                                            | W = Writable b                                                                                                                                                                     | it                                                                                                                                      | U = Unimplem                                                 | ented bit, read as                                             | ʻ0'                 |                  |

| u = Bit is und       | changed                                                                                                                                                                                                                                                                                          | x = Bit is unkno                                                                                                                                                                   | own                                                                                                                                     | -n/n = Value at                                              | t POR and BOR/V                                                | alue at all other   | Resets           |

| '1' = Bit is se      | t                                                                                                                                                                                                                                                                                                | '0' = Bit is clear                                                                                                                                                                 | red                                                                                                                                     |                                                              |                                                                |                     |                  |

| bit 7                | 1 = Indicates t                                                                                                                                                                                                                                                                                  | nowledge Time S<br>he I <sup>2</sup> C bus is in a<br>knowledge seque                                                                                                              | n Acknowledge                                                                                                                           | sequence, set o                                              | on 8 <sup>th</sup> falling edge<br>of SCL clock                | of SCL clock        |                  |

| bit 6                | 1 = Enable inte                                                                                                                                                                                                                                                                                  | ndition Interrupt l<br>errupt on detection<br>tion interrupts are                                                                                                                  | n of Stop condi                                                                                                                         |                                                              |                                                                |                     |                  |

| bit 5                | 1 = Enable inte                                                                                                                                                                                                                                                                                  | ndition Interrupt<br>errupt on detectio<br>tion interrupts ar                                                                                                                      | n of Start or Re                                                                                                                        | • /                                                          |                                                                |                     |                  |

| bit 4                | $\frac{\text{In SPI Slave m}}{1 = SSPx}$ $0 = \text{If nev}$ $\text{regist}$ $\frac{\text{In I}^2 \text{C Master i}}{\text{This bit is}}$ $\frac{\text{In I}^2 \text{C Slave m}}{1 = SSP}$ $\text{SSP}($ $0 = SSPx$                                                                              | BUF updates even<br>v byte is received<br>ter is set, and the<br><u>mode and SPI Ma</u><br>ignored.<br><u>ode:</u><br>(BUF is updated<br>DV bit only if the<br>BUF is only updated | ery time that a r<br>d with BF bit of<br>buffer is not up<br>aster mode:<br>and $\overline{ACK}$ is get<br>BF bit = 0.<br>ated when SSP | the SSPxSTAT r<br>odated<br>nerated for a rec<br>OV is clear | shifted in ignoring<br>egister already se<br>ceived address/da | et, SSPOV bit of    |                  |

| bit 3                | 1 = Minimum o                                                                                                                                                                                                                                                                                    | Hold Time Select<br>of 300 ns hold tim<br>of 100 ns hold tim                                                                                                                       | e on SDA after                                                                                                                          | the falling edge                                             |                                                                |                     |                  |

| bit 2                | SBCDE: Slave<br>If, on the rising<br>PIR3 register i<br>1 = Enable sla                                                                                                                                                                                                                           | Mode Bus Collis                                                                                                                                                                    | sion Detect Ena<br>DA is sampled lo<br>les idle<br>hterrupts                                                                            | ble bit (I <sup>2</sup> C Slav                               |                                                                | a high state, the E | 3CL1IF bit of th |

| bit 1                | <ul> <li>AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)</li> <li>1 = Following the eighth falling edge of SCL for a matching received address byte; CKP bit of the SS register will be cleared and the SCL will be held low.</li> <li>0 = Address holding is disabled</li> </ul> |                                                                                                                                                                                    |                                                                                                                                         |                                                              |                                                                |                     |                  |

| bit 0                | 1 = Following                                                                                                                                                                                                                                                                                    | N1 register and S                                                                                                                                                                  | edge of SCL f                                                                                                                           | or a received da                                             | ita byte; slave ha                                             | rdware clears the   | e CKP bit of th  |

|                      | For daisy-chained S<br>byte is received and<br>This bit has no effec                                                                                                                                                                                                                             | BF = 1, but hard                                                                                                                                                                   | ware continues                                                                                                                          | to write the mos                                             | t recent byte to SS                                            | SPxBUF.             |                  |

## REGISTER 33-4: SSPxCON3: SSPx CONTROL REGISTER 3

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

**3:** The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

## 34.5 EUSART Operation During Sleep