Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19156-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABL               | BLE 4: 40/44-PIN ALLOCATION TABLE (PIC16(L)F19175/76) |             |             |            |                               |           |                  |                   |          |                      |     |           |                       |                                        |                                          |                       |      |                |                     |              |         |                    |

|--------------------|-------------------------------------------------------|-------------|-------------|------------|-------------------------------|-----------|------------------|-------------------|----------|----------------------|-----|-----------|-----------------------|----------------------------------------|------------------------------------------|-----------------------|------|----------------|---------------------|--------------|---------|--------------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP                                           | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN | ADC                           | Reference | Comparator       | Zero-Cross Detect | DAC      | Timers/SMT           | ССР | MWG       | CWG                   | ASSM                                   | EUSART                                   | CLC                   | RTCC | ГСD            | Interrupt-on-Change | High Current | Pull-up | Basic              |

| RA0                | 2                                                     | 17          | 19          | 19         | ANA0                          | —         | C1IN0-<br>C2IN0- | —                 | —        | _                    | —   | _         | _                     | _                                      | —                                        | CLCIN0 <sup>(1)</sup> | _    | SEG0           | IOCA0               | —            | Υ       | —                  |

| RA1                | 3                                                     | 18          | 20          | 20         | ANA1                          | —         | C1IN1-<br>C2IN1- | —                 |          | _                    | —   | —         | -                     |                                        | —                                        | CLCIN1 <sup>(1)</sup> | —    | SEG1           | IOCA1               | -            | Y       | —                  |

| RA2                |                                                       |             |             | 21         | ANA2                          | _         | C1IN0+<br>C2IN0+ | _                 | DAC1OUT1 | _                    | _   | —         | _                     |                                        | _                                        | _                     | —    | SEG2           | IOCA2               |              | Y       | _                  |

| RA3                | 5                                                     | 20          | 22          | 22         | ANA3                          | VREF+     | C1IN1+           | -                 | DAC1REF+ | —                    | —   | <u> </u>  | —                     | —                                      | —                                        | —                     | —    | SEG3           | IOCA3               | —            | Υ       | —                  |

| RA4                | 6                                                     | 21          | 23          | 23         | ANA4                          | —         |                  | _                 | —        | тоскі <sup>(1)</sup> | —   | —         | -                     |                                        | —                                        | -                     | _    | SEG4<br>COM3   | IOCA4               | -            | Y       | —                  |

| RA5                | 7                                                     | 22          | 24          | 24         | —                             | —         | —                | —                 | —        | —                    | —   | —         | —                     | SS <sup>(1)</sup>                      | —                                        | —                     | —    | —              | IOCA5               | —            | $\Box$  | VBAT               |

| RA6                | 14                                                    | 29          | 31          | 33         | ANA6                          | —         | _                | —                 | —        |                      | —   | _         | -                     |                                        | —                                        | -                     | -    | SEG6           | IOCA6               | -            | Y       | CLKOUT<br>OSC2     |

| RA7                | 13                                                    | 28          | 30          | 32         | ANA7                          | —         | -                | —                 | —        | _                    | —   | —         | -                     | _                                      | —                                        | _                     | —    | SEG7           | IOCA7               | —            | Y       | OSC1<br>CLKIN      |

| RB0                | 33                                                    | 8           | 8           | 9          | ANB0                          | —         | C2IN1+           | ZCD               | —        | —                    | —   | $\square$ | CWG1IN <sup>(1)</sup> |                                        | —                                        | —                     | —    | SEG8           | IOCB0               | —            | Υ       | INTPPS             |

| RB1                | 34                                                    | 9           | 9           | 10         | ANB1                          | —         | C1IN3-<br>C2IN3- | —                 | —        | —                    | —   | —         |                       | SCL,<br>SDA <sup>(1, 3, 4, 5, 6)</sup> |                                          | _                     | —    | SEG9           | IOCB1               | HIB1         | Y       | _                  |

| RB2                | 35                                                    | 10          | 10          | 11         | ANB2                          | —         |                  | —                 | -        | —                    | -   | —         | -                     | SCL,<br>SDA <sup>(1, 3, 4, 5, 6)</sup> | —                                        | -                     | —    | SEG10<br>CFLY1 | IOCB2               | -            | Y       | —                  |

| RB3                | 36                                                    | 11          | 11          | 12         | ANB3                          | —         | C1IN2-<br>C2IN2- | —                 | —        | _                    | —   | _         | _                     | _                                      | —                                        | _                     | _    | SEG11<br>CFLY2 | IOCB3               | —            | Y       | —                  |

| RB4                | 37                                                    | 12          | 14          | 14         | ANB4<br>ADCACT <sup>(1)</sup> | _         |                  | _                 | -        | _                    | _   | _         | _                     | _                                      | _                                        | _                     | _    | COM0           | IOCB4               | _            | Υ       | _                  |

| RB5                | 38                                                    | 13          | 15          | 15         | ANB5                          | _         | <u> </u>         | _                 | —        | T1G <sup>(1)</sup>   | —   | _         | _                     | _                                      | _                                        | _                     | _    | SEG13<br>COM1  | IOCB5               | _            | Υ       | _                  |

| RB6                | 39                                                    | 14          | 16          | 16         | ANB6                          | _         |                  | _                 |          | —                    | —   | _         | -                     | -                                      | TX2 <sup>(1)</sup><br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> | _    | SEG14          | IOCB6               | _            | Υ       | ICDCLK/<br>ICSPCLK |

| RB7                | 40                                                    | 15          | 17          | 17         | ANB7                          | —         | <u> </u>         | _                 | DAC1OUT2 | _                    | —   | _         | _                     |                                        | RX2 <sup>(1)</sup><br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | —    | SEG15          | IOCB7               | _            | Y       | ICDDAT/<br>ICSPDAT |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or 4: SMBUS input buffer thresholds.

These are alternative I<sup>2</sup>C logic levels pins. 5:

In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins. 6:

DS40001923A-page 11

#### 4.3.3 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes of the data banks 0-59 and 100 bytes of the data banks 60-63, after the core registers.

The SFRs associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

4.3.4 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

| ADLE 4-4: | GENERAL PURPOSE RAM SIZE AND BANK LUCATION |                               |           |                             |  |  |  |  |  |  |  |  |

|-----------|--------------------------------------------|-------------------------------|-----------|-----------------------------|--|--|--|--|--|--|--|--|

| Bank      |                                            | , PIC16(L)F19175,<br>_)F19185 |           | PIC16(L)F19176,<br>_)F19186 |  |  |  |  |  |  |  |  |

|           | Address                                    | Size (Bytes)                  | Address   | Size (Bytes)                |  |  |  |  |  |  |  |  |

| 0         | 020h-07Fh                                  | 96                            | 020h-07Fh | 96                          |  |  |  |  |  |  |  |  |

| 1         | 0A0h-0EFh                                  | 80                            | 0A0h-0EFh | 80                          |  |  |  |  |  |  |  |  |

| 2         | 120h-16Fh                                  | 80                            | 120h-16Fh | 80                          |  |  |  |  |  |  |  |  |

| 3         | 1A0h-1EFh                                  | 80                            | 1A0h-1EFh | 80                          |  |  |  |  |  |  |  |  |

| 4         | 220h-26Fh                                  | 80                            | 220h-26Fh | 80                          |  |  |  |  |  |  |  |  |

| 5         | 2A0h-2EFh                                  | 80                            | 2A0h-2EFh | 80                          |  |  |  |  |  |  |  |  |

| 6         | 320h-36Fh                                  | 80                            | 320h-36Fh | 80                          |  |  |  |  |  |  |  |  |

| 7         | 3A0h-3EFh                                  | 80                            | 3A0h-EFh  | 80                          |  |  |  |  |  |  |  |  |

| 8         | 420h-46Fh                                  | 80                            | 420h-46Fh | 80                          |  |  |  |  |  |  |  |  |

| 9         | 4A0h-4EFh                                  | 80                            | 4A0h-4EFh | 80                          |  |  |  |  |  |  |  |  |

| 10        | 520h-560h                                  | 80                            | 520h-560h | 80                          |  |  |  |  |  |  |  |  |

| 11        | 5A0h-5EFh                                  | 80                            | 5A0h-5EFh | 80                          |  |  |  |  |  |  |  |  |

| 12        | 620h-64Fh                                  | 48                            | 620h-64Fh | 80                          |  |  |  |  |  |  |  |  |

| 13        |                                            |                               | 6A0h-6EFh | 80                          |  |  |  |  |  |  |  |  |

| 14        |                                            |                               | 720h-76Fh | 80                          |  |  |  |  |  |  |  |  |

| 15        |                                            |                               | 7A0h-7EFh | 80                          |  |  |  |  |  |  |  |  |

| 16        |                                            |                               | 820h-96Fh | 80                          |  |  |  |  |  |  |  |  |

| 17        |                                            |                               | 8A0h-8EFh | 80                          |  |  |  |  |  |  |  |  |

| 18        |                                            |                               | 920h-96Fh | 80                          |  |  |  |  |  |  |  |  |

| 19        |                                            |                               | 9A0h-9EFh | 80                          |  |  |  |  |  |  |  |  |

| 20        |                                            |                               | A20h-A6Fh | 80                          |  |  |  |  |  |  |  |  |

| 21        |                                            |                               | AA0h-AEFh | 80                          |  |  |  |  |  |  |  |  |

| 22        |                                            |                               | B20h-B6Fh | 80                          |  |  |  |  |  |  |  |  |

| 23        |                                            |                               | BA0h-BEFh | 80                          |  |  |  |  |  |  |  |  |

| 24        |                                            |                               | C20h-C6Fh | 80                          |  |  |  |  |  |  |  |  |

| 25        |                                            |                               | CA0h-CBFh | 32                          |  |  |  |  |  |  |  |  |

#### TABLE 4-4: GENERAL PURPOSE RAM SIZE AND BANK LOCATION

**Legend:** = Unimplemented GPR locations

| IADLE 4    | ABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED) |         |               |         |         |         |         |         |         |                       |                            |  |  |

|------------|---------------------------------------------------------------------------------------------------|---------|---------------|---------|---------|---------|---------|---------|---------|-----------------------|----------------------------|--|--|

| Address    | Name                                                                                              | Bit 7   | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |  |  |

| Bank 62 (C | continued)                                                                                        |         |               |         |         |         |         |         |         |                       |                            |  |  |

| 1F4Eh      | ANSELC                                                                                            | ANSC7   | ANSC6         |         | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                  |  |  |

| 1F4Fh      | WPUC                                                                                              | WPUC7   | WPUC6         |         | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                  |  |  |

| 1F50h      | ODCONC                                                                                            | ODCC7   | ODCC6         | —       | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                  |  |  |

| 1F51h      | SLRCONC                                                                                           | SLRC7   | SLRC6         |         | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                  |  |  |

| 1F52h      | INLVLC                                                                                            | INLVLC7 | INLVLC6       | —       | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                  |  |  |

| 1F53h      | IOCCP                                                                                             | IOCCP7  | IOCCP6        | —       | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                  |  |  |

| 1F54h      | IOCCN                                                                                             | IOCCN7  | IOCCN6        |         | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                  |  |  |

| 1F55h      | IOCCF                                                                                             | IOCCF7  | IOCCF6        | —       | IOCCF4  | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                  |  |  |

| 1F56h      | —                                                                                                 |         | Unimplemented |         |         |         |         |         |         |                       |                            |  |  |

| 1F57h      | _                                                                                                 |         | Unimplemented |         |         |         |         |         |         |                       |                            |  |  |

| 1F58h      | _                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F59h      | ANSELD                                                                                            | ANSD7   | ANSD6         | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   | 1111 1111             | 1111 1111                  |  |  |

| 1F5Ah      | WPUD                                                                                              | WPUD7   | WPUD6         | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   | 0000 0000             | 0000 0000                  |  |  |

| 1F5Bh      | ODCOND                                                                                            | ODCD7   | ODCD6         | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   | 0000 0000             | 0000 0000                  |  |  |

| 1F5Ch      | SLRCOND                                                                                           | SLRD7   | SLRD6         | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   | 1111 1111             | 1111 1111                  |  |  |

| 1F5Dh      | INLVLD                                                                                            | INLVLD7 | INLVLD6       | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 1111 1111             | 1111 1111                  |  |  |

| 1F5Eh      | —                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F5Fh      | —                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F60h      |                                                                                                   |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F61h      | —                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F62h      | —                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

| 1F63h      | —                                                                                                 |         |               |         | Unimple | mented  |         |         |         |                       |                            |  |  |

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| REGIST  | ER 5-7:              | REVISIONID: REVISION ID REGISTER |   |       |                  |   |   |                    |   |       |        |   |       |

|---------|----------------------|----------------------------------|---|-------|------------------|---|---|--------------------|---|-------|--------|---|-------|

| R       | R                    | R                                | R | R     | R                | R | R | R                  | R | R     | R      | R | R     |

| 1       | 0                    |                                  |   | MJRRE | V<5:0>           |   |   |                    |   | MNRRE | V<5:0> |   |       |

| bit 13  |                      |                                  |   |       |                  |   |   |                    |   |       |        |   | bit 0 |

|         |                      |                                  |   |       |                  |   |   |                    |   |       |        |   |       |

| Legend: |                      |                                  |   |       |                  |   |   |                    |   |       |        |   |       |

|         | R = Read             | able bit                         |   |       |                  |   |   |                    |   |       |        |   |       |

|         | '0' = Bit is cleared |                                  |   |       | '1' = Bit is set |   |   | x = Bit is unknown |   |       |        |   |       |

#### REGISTER 5-7: REVISIONID: REVISION ID REGISTER

These bits are fixed with value '10' for all devices included in this data sheet.

### bit 11-6 MJRREV<5:0>: Major Revision ID bits

These bits are used to identify a major revision. A major revision is indicated by an all layer revision (B0, C0, etc.)

#### bit 5-0 **MNRREV<5:0>**: Minor Revision ID bits These bits are used to identify a minor revision.

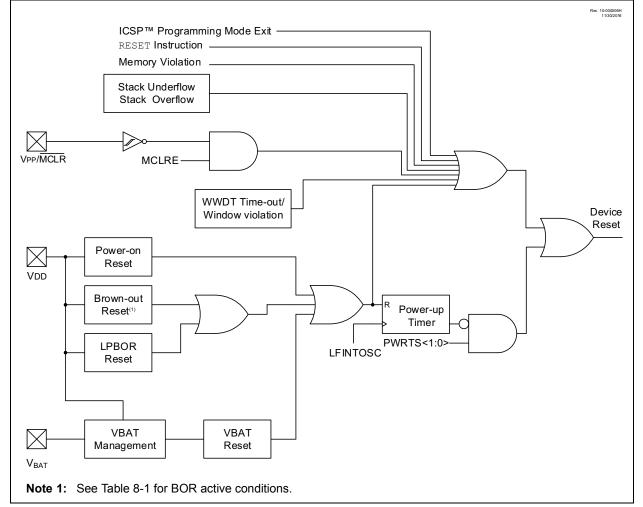

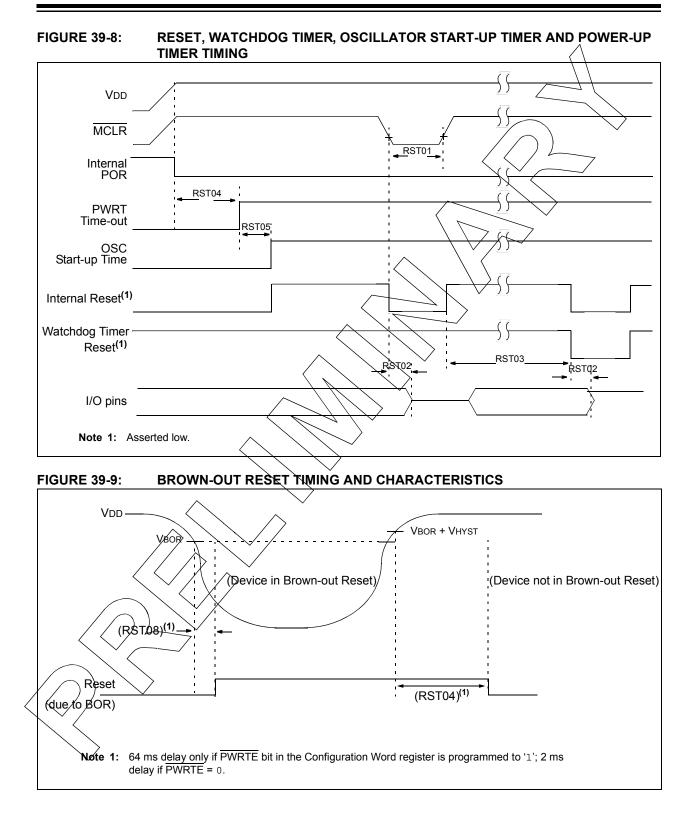

### 8.0 RESETS AND VBAT

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

- Memory Violation Reset (MEMV)

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 8-1.

### 8.1 VBAT

This device is equipped with a VBAT pin that allows the user to connect an external battery or an external supply. In the event of the VDD supply failing, the power source connected to the VBAT pin will keep the SOSC and RTCC modules running.

| R-q/q            | R-q/q          | R-q/q                                                          | R-q/q   | R-q/q                   | R-q/q               | U-0               | R-q/q  |

|------------------|----------------|----------------------------------------------------------------|---------|-------------------------|---------------------|-------------------|--------|

| EXTOR            | HFOR           | MFOR                                                           | LFOR    | SOR                     | ADOR                | _                 | PLLR   |

| bit 7            |                |                                                                |         |                         | · · · · · ·         |                   | bit    |

| Legend:          |                |                                                                |         |                         |                     |                   |        |

| R = Readable b   | bit            | W = Writable b                                                 | t       | U = Unimplem            | ented bit, read as  | '0'               |        |

| u = Bit is uncha | inged          | x = Bit is unkno                                               | wn      | -n/n = Value at         | POR and BOR/Va      | alue at all other | Resets |

| '1' = Bit is set |                | '0' = Bit is clear                                             | ed      |                         |                     |                   |        |

| bit 7            | 1 = The osci   | DSC (external) Os<br>Ilator is ready to<br>Ilator is not enab  | be used | bit<br>ready to be used | d.                  |                   |        |

| bit 6            | 1 = The osci   | OSC Oscillator R<br>llator is ready to<br>llator is not enab   | be used | ready to be used        | d.                  |                   |        |

| bit 5            | 1 = The oscill | OSC Oscillator F<br>ator is ready to b<br>ator is not enable   | e used  | ready to be used        |                     |                   |        |

| bit 4            | 1 = The osci   | DSC Oscillator Re<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d.                  |                   |        |

| bit 3            | 1 = The osci   | ary (Timer1) Osci<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d.                  |                   |        |

| bit 2            | 1 = The osci   | C Oscillator Read<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d                   |                   |        |

| bit 1            | Unimplemente   | ed: Read as '0'                                                |         |                         |                     |                   |        |

| bit 0            |                | is ready to be us                                              |         | ut source is not re     | eady, or the PLL is | not locked.       |        |

#### 14.8 PORTD Registers

| Note: | PORTD functionality is not available on  |

|-------|------------------------------------------|

|       | the PIC16(L)F19155/56 family of devices. |

#### 14.8.1 DATA REGISTER

PORTD is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 14-2). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., disable the output driver). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTD.

Reading the PORTD register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch.

The PORT data latch LATD (Register 14-3) holds the output port data, and contains the latest value of a LATD or PORTD write.

#### EXAMPLE 14-3: INITIALIZING PORTD

| ; initia<br>; other | <pre>; This code example illustrates<br/>; initializing the PORTD register. The<br/>; other ports are initialized in the same<br/>; manner.</pre> |                                 |  |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|--|--|

| BANKSEL             | PORTD                                                                                                                                             | ;                               |  |  |  |  |  |  |  |  |

| CLRF                | PORTD                                                                                                                                             | ;Init PORTD                     |  |  |  |  |  |  |  |  |

| BANKSEL             | LATD                                                                                                                                              | ;Data Latch                     |  |  |  |  |  |  |  |  |

| CLRF                | LATD                                                                                                                                              | ;                               |  |  |  |  |  |  |  |  |

| BANKSEL             | ANSELD                                                                                                                                            | ;                               |  |  |  |  |  |  |  |  |

| CLRF                | ANSELD                                                                                                                                            | ;digital I/O                    |  |  |  |  |  |  |  |  |

| BANKSEL             | TRISD                                                                                                                                             | ;                               |  |  |  |  |  |  |  |  |

| MOVLW               | B'00111000'                                                                                                                                       | ;Set RD<5:3> as inputs          |  |  |  |  |  |  |  |  |

| MOVWF               | TRISD                                                                                                                                             | ;and set RD<2:0> as<br>;outputs |  |  |  |  |  |  |  |  |

### 14.8.2 DIRECTION CONTROL

The TRISD register (Register 14-2) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.8.3 OPEN-DRAIN CONTROL

The ODCOND register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCOND bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCOND bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

#### 14.8.4 SLEW RATE CONTROL

The SLRCOND register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCOND bit is set, the corresponding port pin drive is slew rate limited. When an SLRCOND bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.8.5 INPUT THRESHOLD CONTROL

The INLVLD register (Register 14-8) controls the input voltage threshold for each of the available PORTD input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTD register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 39-4 for more information on threshold levels.

| Note: | Changing the input threshold selection<br>should be performed while all peripheral |

|-------|------------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                                 |

|       | threshold level during the time a module is                                        |

|       | active may inadvertently generate a                                                |

|       | transition associated with an input pin,                                           |

|       | regardless of the actual voltage level on                                          |

|       | that pin.                                                                          |

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                              | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|------------------|---------|-------------------|---------|------------------------------------------------------|---------|---------|---------|--|--|

| LATF7            | LATF6   | LATF5             | LATF4   | LATF3                                                | LATF2   | LATF1   | LATF0   |  |  |

| bit 7            |         |                   |         |                                                      |         |         | bit 0   |  |  |

|                  |         |                   |         |                                                      |         |         |         |  |  |

| Legend:          |         |                   |         |                                                      |         |         |         |  |  |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                   |         |         |         |  |  |

| u = Bit is uncha | anged   | x = Bit is unkn   | nown    | -n/n = Value at POR and BOR/Value at all other Reset |         |         |         |  |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                      |         |         |         |  |  |

#### REGISTER 14-43: LATF: PORTF DATA LATCH REGISTER

#### bit 7-0 LATF<7:0>: RF<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTF are actually written to corresponding LATF register. Reads from PORTF register is return of actual I/O pin values.

#### REGISTER 14-44: ANSELF: PORTF ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSF7   | ANSF6   | ANSF5   | ANSF4   | ANSF3   | ANSF2   | ANSF1   | ANSF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSF<7:0>**: Analog Select between Analog or Digital Function on pins RF<7:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 14-45: WPUF: WEAK PULL-UP PORTF REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUF7   | WPUF6   | WPUF5   | WPUF4   | WPUF3   | WPUF2   | WPUF1   | WPUF0   |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUF<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** The weak pull-up device is automatically disabled if the pin is configured as an output.

| Name    | Bit 7     | Bit 6  | Bit 5      | Bit 4      | Bit 3            | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|---------|-----------|--------|------------|------------|------------------|-----------|-----------|---------|---------------------|

| PIE8    | LCDIE     | RTCCIE | -          | _          | —                | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 173                 |

| PIR8    | LCDIF     | RTCCIF | _          | _          | —                | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 182                 |

| PMD2    | RTCCMD    | DACMD  | ADCMD      | _          | —                | CMP2MD    | CMP1MD    | ZCDMD   | 271                 |

| INTCON  | GIE       | PEIE   | _          | _          | —                | —         | _         | INTEDG  | 164                 |

| PCON1   | —         | _      | _          | —          | _                | _         | MEMV      | VBATBOR | 141                 |

| RTCCON  | RTCEN     | _      | RTCWREN    | RTCSYNC    | HALFSEC          | —         | RTCCLKS   | EL<1:0> | 357                 |

| RTCCAL  |           |        |            | CAL<       | 7:0>             |           |           |         | 358                 |

| ALRMCON | ALRMEN    | CHIME  |            | AMASK      | <3:0> — —        |           |           |         | 361                 |

| ALRMRPT | ARPT<7:0> |        |            |            |                  |           |           | 361     |                     |

| YEAR    |           | YE     | ARH<3:0>   |            |                  | 358       |           |         |                     |

| MONTH   | _         | _      | _          | MONTHH     | MONTHL<3:0>      |           |           |         | 358                 |

| WEEKDAY | _         | _      | _          | —          | — WDAY<2:0>      |           |           |         | 359                 |

| DAY     | _         | _      | DAY        | ′H<1:0>    |                  | 359       |           |         |                     |

| HOURS   | _         | _      | HR         | H<1:0>     |                  | 359       |           |         |                     |

| MINUTES | _         |        | MINH<2:0>  |            |                  | 360       |           |         |                     |

| SECONDS | _         |        | SECH<2:0>  |            |                  |           | 360       |         |                     |

| ALRMMTH | _         | _      | _          | ALRMHMONTH | ALRMLMONTH <3:0> |           |           |         | 362                 |

| ALRMWD  | _         | _      | _          | —          |                  |           |           |         | 362                 |

| ALRMDAY | _         | _      | ALRM       | HDAY<1:0>  |                  | ALRMLD    | AY<3:0>   |         | 362                 |

| ALRMHR  | —         | _      | ALRM       | HHR<1:0>   |                  | ALRMLH    | R<3:0>    |         | 363                 |

| ALRMMIN |           |        | ALRMHMIN<2 | :0>        |                  | ALRMLM    | IN<3:0>   |         | 363                 |

| ALRMSEC | —         |        | ALRMHSEC<2 | :0>        |                  | ALRMLS    | EC<3:0>   |         | 363                 |

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE RTCC MODULE

### 27.7 Register Definitions: Timer2/4 Control

| U-0            | U-0               | U-0                                 | U-0  | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |

|----------------|-------------------|-------------------------------------|------|----------------|------------------|----------------|--------------|--|--|--|

| _              |                   | _                                   | _    |                | CS<              | :3:0>          |              |  |  |  |

| bit 7          |                   |                                     |      |                |                  |                | bit (        |  |  |  |

| Legend:        |                   |                                     |      |                |                  |                |              |  |  |  |

| R = Reada      | ble bit           | W = Writable                        | bit  | U = Unimpler   | nented bit, read | d as '0'       |              |  |  |  |

| u = Bit is ur  | nchanged          | x = Bit is unkr                     | nown | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |  |  |

| '1' = Bit is s | •                 | '0' = Bit is cle                    | ared |                |                  |                |              |  |  |  |

|                |                   |                                     |      |                |                  |                |              |  |  |  |

| bit 7-4        | Unimplem          | ented: Read as '                    | 0'   |                |                  |                |              |  |  |  |

| bit 3-0        | CS<3:0>:          | CS<3:0>: Timer2/4 Clock Select bits |      |                |                  |                |              |  |  |  |

|                | 1111 <b>= Re</b>  | served                              |      |                |                  |                |              |  |  |  |

|                | -                 | 1110 = Reserved                     |      |                |                  |                |              |  |  |  |

|                | 1101 <b>= Re</b>  | 1101 = Reserved                     |      |                |                  |                |              |  |  |  |

|                | 1100 <b>= LC</b>  | 4_out                               |      |                |                  |                |              |  |  |  |

|                | 1011 <b>= LC</b>  | 3_out                               |      |                |                  |                |              |  |  |  |

|                | 1010 <b>= LC</b>  | 2_out                               |      |                |                  |                |              |  |  |  |

|                | 1001 <b>= LC</b>  | 1_out                               |      |                |                  |                |              |  |  |  |

|                | 1000 <b>= ZC</b>  | D1_output                           |      |                |                  |                |              |  |  |  |

|                | 0111 <b>= SC</b>  | DSC                                 |      |                |                  |                |              |  |  |  |

|                |                   | FINTOSC (31.25                      |      |                |                  |                |              |  |  |  |

|                |                   | FINTOSC (500 kH                     | lz)  |                |                  |                |              |  |  |  |

|                | 0100 <b>= LF</b>  |                                     |      |                |                  |                |              |  |  |  |

|                |                   | INTOSC (32 MH                       | z)   |                |                  |                |              |  |  |  |

|                | 0010 <b>= F</b> o |                                     |      |                |                  |                |              |  |  |  |

|                | 0001 <b>= F</b> o |                                     |      |                |                  |                |              |  |  |  |

|                | 0000 <b>= T2</b>  | CKIPPS                              |      |                |                  |                |              |  |  |  |

#### REGISTER 27-1: TxCLKCON: TIMER2/4 CLOCK SELECTION REGISTER

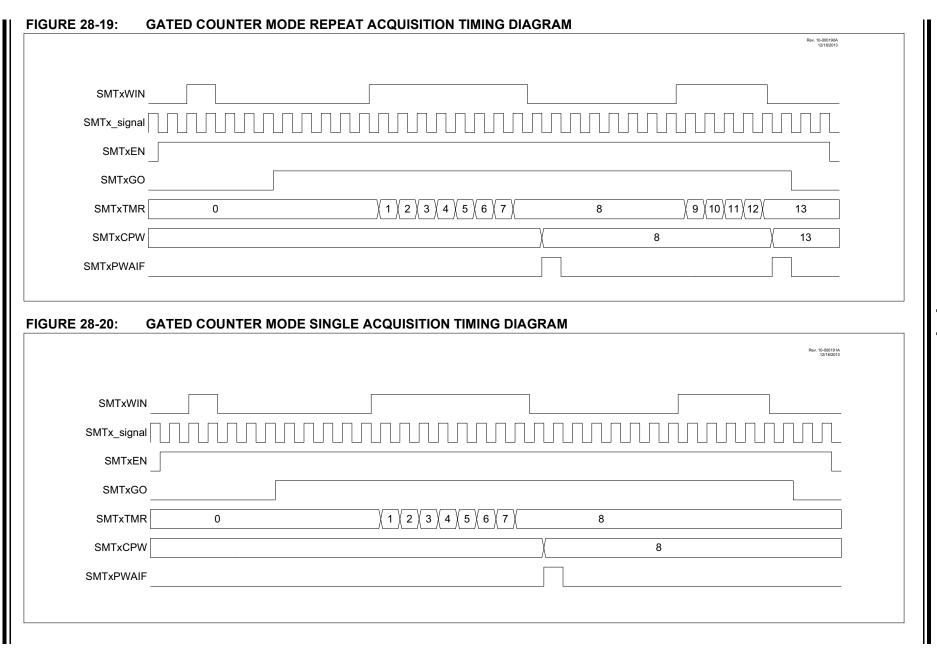

#### 28.7.5 WINDOWED MEASURE MODE

Windowed Measure mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMTxCPR register with the value of the timer and resets the timer on a second rising edge. See Figure 28-10 and Figure 28-11.

#### 28.8 Interrupts

The SMT can trigger an interrupt under three different conditions:

- PW Acquisition Complete

- PR Acquisition Complete

- Counter Period Match

The interrupts are controlled by the PIR8 and PIE8 registers of the device.

#### 28.8.1 PW AND PR ACQUISITION INTERRUPTS

The SMT can trigger interrupts whenever it updates the SMTxCPW and SMTxCPR registers, the circumstances for which are dependent on the SMT mode, and are discussed in each mode's specific section. The SMTxCPW interrupt is controlled by SMTxPWAIF and SMTxPWAIE bits in registers PIR8 and PIE8, respectively. The SMTxCPR interrupt is controlled by the SMTxPRAIF and SMTxPRAIE bits, also located in registers PIR8 and PIE8, respectively.

In Synchronous SMT modes, the interrupt trigger is synchronized to the SMTxCLK. In Asynchronous modes, the interrupt trigger is asynchronous. In either mode, once triggered, the interrupt will be synchronized to the CPU clock.

#### 28.8.2 COUNTER PERIOD MATCH INTERRUPT

As described in Section 28.2.2 "Period Match interrupt", the SMT will also interrupt upon SMTxTMR, matching SMTxPR with its period match limit functionality described in Section 28.4 "Halt Operation". The period match interrupt is controlled by SMTxIF and SMTxIE.

| Name     | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3    | Bit 2     | Bit 1     | Bit 0   | Register on<br>Page |

|----------|----------------|--------------|-------|--------|----------|-----------|-----------|---------|---------------------|

| PIE8     | LCDIE          | RTCCIE       | —     | —      | —        | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 173                 |

| PIR8     | LCDIF          | RTCCIF       | —     | —      | —        | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 182                 |

| SMT1CLK  | _              | _            | —     | _      | _        |           | CSEL<2:0> |         | 413                 |

| SMT1CON0 | EN             | _            | STP   | WPOL   | SPOL     | CPOL      | SMT1P     | 'S<1:0> | 410                 |

| SMT1CON1 | SMT1GO         | REPEAT       | —     | —      |          | MODE      | <3:0>     |         | 411                 |

| SMT1CPRH |                |              |       | SMT1CF | PR<15:8> |           |           |         | 417                 |

| SMT1CPRL |                | SMT1CPR<7:0> |       |        |          |           |           |         |                     |

| SMT1CPRU | SMT1CPR<23:16> |              |       |        |          |           |           |         | 417                 |

| SMT1CPWH | SMT1CPW<15:8>  |              |       |        |          |           |           |         | 418                 |

| SMT1CPWL | SMT1CPW<7:0>   |              |       |        |          |           |           |         | 418                 |

| SMT1CPWU | SMT1CPW<23:16> |              |       |        |          |           |           |         | 418                 |

| SMT1PRH  |                |              |       | SMT1PI | R<15:8>  |           |           |         | 419                 |

| SMT1PRL  |                |              |       | SMT1P  | PR<7:0>  |           |           |         | 419                 |

| SMT1PRU  |                |              |       | SMT1PF | ?<23:16> |           |           |         | 419                 |

| SMT1SIG  | —              | _            | _     |        |          | SSEL<4:0> |           |         | 415                 |

| SMT1STAT | CPRUP          | CPWUP        | RST   | —      | _        | TS        | WS        | AS      | 412                 |

| SMT1TMRH | SMT1TMR<15:8>  |              |       |        |          |           |           |         | 416                 |

| SMT1TMRL | SMT1TMR<7:0>   |              |       |        |          |           |           |         | 416                 |

| SMT1TMRU |                |              |       | SMT1TM | R<23:16> |           |           |         | 416                 |

| SMT1WIN  | _              | _            | —     |        |          | WSEL<4:0> |           |         | 414                 |

#### TABLE 28-3: SUMMARY OF REGISTERS ASSOCIATED WITH SMTx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for SMTx module.

# 34.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 34.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCxREG register. If the RXxIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 34.4.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RXxIF bit will be set when reception is complete. An interrupt will be generated if the RXxIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

© 2017 Microchip Technology Inc.

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                               |

| Operation:       | $\label{eq:W} \begin{split} & W \rightarrow INDFn \\ & \text{Effective address is determined by} \\ & FSR + 1 (\text{preincrement}) \\ & FSR + 1 (\text{predecrement}) \\ & FSR + k (\text{relative offset}) \\ & \text{After the Move, the FSR value will be} \\ & \text{either:} \\ & FSR + 1 (\text{all increments}) \\ & FSR + 1 (\text{all increments}) \\ & \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                            |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

#### NOP **No Operation** [label] NOP Syntax: Operands: None Operation: No operation Status Affected: None Description: No operation. Words: 1 Cycles: 1 Example: NOP

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.  |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                               |

| Example:         | RETFIE                                                                                                                                                                                                          |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |

#### TABLE 39-14: COMPARATOR SPECIFICATIONS

| VDD = 3.0V. TA = 25°C | `` |

|-----------------------|----|

|                       | ľ  |

| 0.01          | , IA 200               | ~ \                               |            |       |      |       |              |  |

|---------------|------------------------|-----------------------------------|------------|-------|------|-------|--------------|--|

| Param.<br>No. | Sym.                   | Characteristics                   | Min.       | утур. | Max. | Units | Comments     |  |

| CM01          | VIOFF                  | Input Offset Voltage              | $\searrow$ | ±30   |      | mV    | VICM = VDD/2 |  |

| CM02          | VICM                   | Input Common Mode Range           | ØND        | —     | Vdd  | V     |              |  |

| CM03          | CMRR                   | Common Mode Input Rejection Ratio | _          | 50    | _    | dB    |              |  |

| CM04          | VHYST                  | Comparator Hysteresis             | _          | 25    | _    | mV    |              |  |

| CM05          | TRESP <sup>(1)</sup>   | Response Time, Rising Edge        | _          | 300   | 600  | ns    |              |  |

|               |                        | Response Time, Falling Edge       |            | 220   | 500  | ns    |              |  |

| CMOS6         | TMCV2VO <sup>(2)</sup> | Mode Charige to Valid Output      | _          | —     | 10   | μs    |              |  |

| CMOS6         | Тмсv2vo <sup>(2)</sup> |                                   | —          | _     | 10   | μs    |              |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: A mode change includes changing any of the control register values, including module enable.

## TABLE 39-15: LOW-POWERED CLOCKED COMPARATOR SPECIFICATIONS

# Standard Operating Conditions (unless otherwise stated)

| $VDD = 3.0V, TA = 25^{\circ}C$ |                         |                                   |      |      |      |       |              |  |  |  |

|--------------------------------|-------------------------|-----------------------------------|------|------|------|-------|--------------|--|--|--|

| Param.<br>No.                  | Sym.                    | Characteristics                   | Min. | Тур. | Max. | Units | Comments     |  |  |  |

| CM07                           | VIOFF                   | Input Offset Voltage              |      | ±30  | —    | mV    | VICM = VDD/2 |  |  |  |

| CM08                           | VICM                    | Input Common Mode Range           | GND  |      | Vdd  | V     |              |  |  |  |

| CM09                           | CMRR                    | Common Mode Input Rejection Ratio |      | 50   | —    | dB    |              |  |  |  |

| CM010                          | VHYST                   | Comparator Hysteresis             |      | 25   | —    | mV    |              |  |  |  |

| CM011                          | TRESP <sup>(1)(3)</sup> | Response Time, Rising Edge        | _    | 300  | —    | ns    |              |  |  |  |

|                                |                         | Response Time, Falling Edge       | _    | 220  | _    | ns    |              |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: A mode change includes changing any of the control register values, including module enable.

3: Comparator output state change occurs on the rising edge of LFINTOSC.

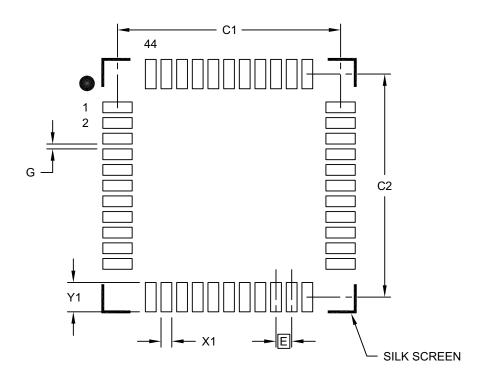

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension Limits         |             | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E           |      | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 11.40    |      |  |

| Contact Pad Spacing      | C2          |      | 11.40    |      |  |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |  |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |  |

| Distance Between Pads    | G           | 0.25 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B