Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuns                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19156-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## Customer Notification System

Register on our website at www.microchip.com to receive the most current information on all of our products.

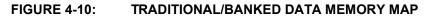

## 4.6.1 TRADITIONAL/BANKED DATA MEMORY

The traditional or banked data memory is a region from FSR address 0x000 to FSR address 0x1FFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

| NOSC<2:0>/<br>COSC<2:0> | Clock Source                                    |

|-------------------------|-------------------------------------------------|

| 111                     | EXTOSC <sup>(1)</sup>                           |

| 110                     | HFINTOSC <sup>(2)</sup>                         |

| 101                     | LFINTOSC                                        |

| 100                     | SOSC                                            |

| 011                     | Reserved (operates like<br>NOSC = 110)          |

| 010                     | EXTOSC with 4x PLL <sup>(1)</sup>               |

| 001                     | HFINTOSC with 2x PLL <sup>(1)</sup>             |

| 000                     | HFINTOSC with OSCFRQ<br>= 32 MHz and CDIV = 1:1 |

## TABLE 9-1: NOSC/COSC BIT SETTINGS

**Note 1:** EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

2: HFINTOSC settings are configured with the HFFRQ bits of the OSCFRQ register (Register 9-6).

| TABLE 9-2: NDIV/CDIV BIT SETTINGS |

|-----------------------------------|

|-----------------------------------|

| NDIV<3:0>/<br>CDIV<3:0> | Clock divider |  |  |

|-------------------------|---------------|--|--|

| 1111-1010               | Reserved      |  |  |

| 1001                    | 512           |  |  |

| 1000                    | 256           |  |  |

| 0111                    | 128           |  |  |

| 0110                    | 64            |  |  |

| 0101                    | 32            |  |  |

| 0100                    | 16            |  |  |

| 0011                    | 8             |  |  |

| 0010                    | 4             |  |  |

| 0001                    | 2             |  |  |

| 0000                    | 1             |  |  |

## 13.4.5 NVMREG WRITE TO PFM

Program memory is programmed using the following steps:

- 1. Load the address of the row to be programmed into NVMADRH:NVMADRL.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 13-4 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of NVMADRH:NVMADRL, (NVMADRH<6:0>:NVMADRL<7:5>) with the lower five bits of NVMADRL, (NVMADRL<7:5>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF.

The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch loaded with data from is the NVMDATH:NVMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- **Note:** The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the NVMCON1 register.

- Clear the NVMREGS bit of the NVMCON1 register.

- Set the LWLO bit of the NVMCON1 register. When the LWLO bit of the NVMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the NVMADRH:NVMADRL register pair with the address of the location to be written.

- 5. Load the NVMDATH:NVMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 13.4.2 "NVM Unlock Sequence"). The write latch is now loaded.

- 7. Increment the NVMADRH:NVMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the NVMCON1 register. When the LWLO bit of the NVMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the NVMDATH:NVMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 13.4.2 "NVM Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 13-4. The initial address is loaded into the NVMADRH:NVMADRL register pair; the data is loaded using indirect addressing.

| R/W-0/0                           | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------------|---------|------------------------------------|---------|------------|---------|---------|---------|

| WPUB7                             | WPUB6   | WPUB5                              | WPUB4   | WPUB3      | WPUB2   | WPUB1   | WPUB0   |

| bit 7                             |         | •                                  |         |            |         |         | bit 0   |

|                                   |         |                                    |         |            |         |         |         |

| Legend:                           |         |                                    |         |            |         |         |         |

| R = Readable bit W = Writable bit |         | U = Unimplemented bit, read as '0' |         |            |         |         |         |

| IX - IXcadabic                    | bit     | W Windbie                          |         | e enimpien |         | 40 0    |         |

## REGISTER 14-13: WPUB: WEAK PULL-UP PORTB REGISTER

'0' = Bit is cleared

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

'1' = Bit is set

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

## REGISTER 14-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODCB<7:0>:** PORTB Open-Drain Enable bits

For RB<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

## 19.4 Capacitive Voltage Divider (CVD) Features

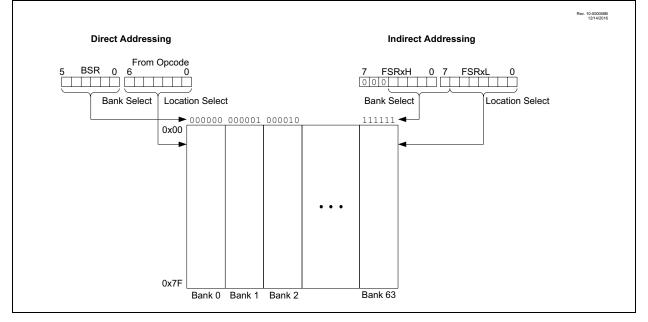

The ADC module contains several features that allow the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications. Figure 19-6 shows the basic block diagram of the CVD portion of the ADC module.

## FIGURE 19-6: HARDWARE CAPACITIVE VOLTAGE DIVIDER BLOCK DIAGRAM

## REGISTER 22-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | _   | —   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

## Legend:

| Logonan              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select bits |

|         | 111 = CxVN connects to AVss                             |

|         | 110 = CxVN connects to FVR Buffer 2                     |

|         | 101 = CxVN unconnected                                  |

|         | 100 = CxVN connects to CxIN4- pin                       |

|         | 011 = CxVN connects to CxIN3- pin                       |

|         | 010 = CxVN connects to CxIN2- pin                       |

|         | $0.01 - C_{\rm X}/N$ connects to C_{\rm X}/N1 nin       |

001 = CxVN connects to CxIN1- pin 000 = CxVN connects to CxIN0- pin

## REGISTER 22-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | —   | —   | —   | —   |         | PCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-2 Unimplemented: Read as '0'

- bit 5-3 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP LCD VREF<sup>(1)</sup>

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

Note 1: Applies to C2 comparator only.

## 28.1 Register Definitions: SMT Control

Long bit name prefixes for the SMT peripherals are shown in Table 28-1. Refer to **Section 1.1.2.2 "Long Bit Names"** for more information.

## TABLE 28-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| SMT1       | SMT1            |

## REGISTER 28-1: SMTxCON0: SMT CONTROL REGISTER 0

| R/W-0/0           | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    |  |

|-------------------|-----|---------|---------|---------|---------|---------|------------|--|

| EN <sup>(1)</sup> | —   | STP     | WPOL    | SPOL    | CPOL    | SMTxP   | ITxPS<1:0> |  |

| bit 7             |     |         |         |         |         |         | bit 0      |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: SMT Enable bit <sup>(1)</sup><br>1 = SMT is enabled<br>0 = SMT is disabled; internal states are reset, clock requests are disabled                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                                                  |

| bit 5   | <b>STP:</b> SMT Counter Halt Enable bit<br>When SMTxTMR = SMTxPR:<br>1 = Counter remains SMTxPR; period match interrupt occurs when clocked<br>0 = Counter resets to 24'h000000; period match interrupt occurs when clocked |

| bit 4   | WPOL: SMTxWIN Input Polarity Control bit<br>1 = SMTxWIN signal is active-low/falling edge enabled<br>0 = SMTxWIN signal is active-high/rising edge enabled                                                                  |

| bit 3   | <b>SPOL:</b> SMTxSIG Input Polarity Control bit<br>1 = SMTx_signal is active-low/falling edge enabled<br>0 = SMTx_signal is active-high/rising edge enabled                                                                 |

| bit 2   | <b>CPOL:</b> SMT Clock Input Polarity Control bit<br>1 = SMTxTMR increments on the falling edge of the selected clock signal<br>0 = SMTxTMR increments on the rising edge of the selected clock signal                      |

| bit 1-0 | SMTxPS<1:0>: SMT Prescale Select bits<br>11 = Prescaler = 1:8<br>10 = Prescaler = 1:4<br>01 = Prescaler = 1:2<br>00 = Prescaler = 1:1                                                                                       |

## **Note 1:** Setting EN to '0' does not affect the register contents.

## 28.7.10 GATED COUNTER MODE

Gated Counter mode counts pulses on the SMTx\_signal input, gated by the SMTxWIN input. It begins incrementing the timer upon seeing a rising edge of the SMTxWIN input and updates the SMTxCPW register upon a falling edge on the SMTxWIN input. See Figure 28-19 and Figure 28-20.

## 30.0 PULSE-WIDTH MODULATION (PWM)

The PWMx modules generate Pulse-Width Modulated (PWM) signals of varying frequency and duty cycle.

In addition to the CCP modules, the PIC16(L)F19155/56/75/76/85/86 devices contain two PWM modules (PWM3 and PWM4). The PWM modules reproduce the PWM capability of the CCP modules.

Note: The PWM3/4 modules are two instances of the same PWM module design. Throughout this section, the lower case 'x' in register and bit names is a generic reference to the PWM module number (which should be substituted with 3, or 4 during code development). For example, the control register is generically described in this chapter as PWMxCON, but the actual device registers are PWM3CON and PWM4CON. Similarly, the PWMxEN bit represents the PWM3EN and PWM4EN bits.

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully ON and fully OFF states. The PWM signal resembles a square wave where the high portion of the signal is considered the 'ON' state (pulse width), and the low portion of the signal is considered the 'OFF' state. The term duty cycle describes the proportion of the 'on' time to the 'off' time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and, in turn, the power that is applied to the load.

Figure 30-1 shows a typical waveform of the PWM signal.

# FIGURE 30-1: **PWM OUTPUT** FOSC Q1 Q2 Q3 Q4 Rev. 10.0000000 PWM Pulse Width PWM TMRx = $PWMxDC^{(1)}$ TMRx = $PRx^{(1)}$ Note 1: Timer dependent on PWMTMRS register settings.

#### 30.1.1 PWM CLOCK SELECTION

The PIC16(L)F19155/56/75/76/85/86 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

#### 30.1.2 USING THE TMR2 WITH THE PWM MODULE

This device has a newer version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to Section 27.5 "Operation Examples" for examples of PWM signal generation using the different modes of Timer2.

| Note: | PWM operation requires that the timer |  |  |  |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|--|--|--|

|       | used as the PWM time base has the     |  |  |  |  |  |  |  |  |

|       | FOSC/4 clock source selected.         |  |  |  |  |  |  |  |  |

#### 30.1.3 PWM PERIOD

Referring to Figure 30-1, the PWM output has a period and a pulse width. The frequency of the PWM is the inverse of the period (1/period).

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 30-1: **PWM PERIOD**

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC$ • (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- · The PWMx pin is set (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM pulse width is latched from PWMxDC.

| Note: | If the pu | ılse-v | vidth value | is great | ter than | the  |

|-------|-----------|--------|-------------|----------|----------|------|

|       | period,   | the    | assigned    | PWM      | pin(s)   | will |

|       | remain    | unch   | anged.      |          |          |      |

#### 30.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDC register. The PWMxDCH contains the eight MSbs and the PWMxDCL<7:6> bits contain the two LSbs.

The PWMDC register is double-buffered and can be updated at any time. This double buffering is essential for glitch-free PWM operation. New values take effect when TMR2 = PR2. Note that PWMDC is left-justified.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Equation 30-2 is used to calculate the PWM pulse width.

Equation 30-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 30-2: PULSE WIDTH

$Pulse Width = (PWMxDC) \cdot TOSC \cdot$ (TMR2 Prescale Value)

#### EQUATION 30-3: DUTY CYCLE RATIO

(PWMxDC) Duty Cycle Ratio =

```

4(PR2 + 1)

```

#### 30.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 30-4.

#### EQUATION 30-4: **PWM RESOLUTION**

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

#### **Register Definitions: MSSPx Control** 33.8

## REGISTER 33-1: SSPxSTAT: SSPx STATUS REGISTER

| REGISTI<br>R/W-0 |                                                                                                          | R/HS/HC-0                                                                                                  | R/HS/HC-0                                                  | R/HS/HC-0                      | R/HS/HC-0                                | R/HS/HC-0           | R/HS/HC-0         |

|------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------|---------------------|-------------------|

| SMP              | (4)                                                                                                      | D/A                                                                                                        | P <sup>(2)</sup>                                           | S <sup>(2)</sup>               | R/W                                      | UA                  | BF                |

| bit 7            |                                                                                                          |                                                                                                            |                                                            | _                              |                                          |                     | bit 0             |

|                  |                                                                                                          |                                                                                                            |                                                            |                                |                                          |                     |                   |

| Legend:          |                                                                                                          |                                                                                                            |                                                            |                                |                                          |                     |                   |

| R = Reada        | ble bit                                                                                                  | W = Writable bit                                                                                           |                                                            | U = Unimpleme                  | nted bit, read as '0                     | 2                   |                   |

| u = Bit is u     | nchanged                                                                                                 | x = Bit is unknow                                                                                          | vn                                                         | -n/n = Value at                | POR and BOR/Val                          | ue at all other Res | sets              |

| '1' = Bit is s   | set                                                                                                      | '0' = Bit is cleare                                                                                        | ed                                                         | HS/HC = Hardv                  | vare set/clear                           |                     |                   |

| bit 7            | SPI Master mod                                                                                           | Input Sample bit<br><u>de:</u><br>ampled at end of o                                                       | data output time                                           |                                |                                          |                     |                   |

|                  | SPI Slave mode<br>SMP must be c<br>In I <sup>2</sup> C Master of<br>1 = Slew rate c                      | control disabled for                                                                                       | s used in Slave r<br>Standard Speed                        | node<br>d mode (100 kHz        | and 1 MHz)                               |                     |                   |

| bit 6            |                                                                                                          | control enabled for<br>Edge Select bit (                                                                   | •                                                          | . , ,                          |                                          |                     |                   |

| bit o            | In SPI Master o<br>1 = Transmit oc<br>0 = Transmit oc<br>In I <sup>2</sup> C mode onl<br>1 = Enable inpu | r Slave mode:<br>curs on transition<br>curs on transition                                                  | from active to Id<br>from Idle to activ<br>sholds are comp | e clock state<br>e clock state | specification                            |                     |                   |

| bit 5            | 1 = Indicates th                                                                                         | ess bit (I <sup>2</sup> C mode<br>at the last byte rec<br>at the last byte rec                             | eived or transmi                                           |                                |                                          |                     |                   |

| bit 4            | 1 = Indicates th                                                                                         | This bit is cleared<br>at a Stop bit has b<br>s not detected last                                          |                                                            |                                | led, SSPEN is clea<br>Reset)             | red.)               |                   |

| bit 3            | 1 = Indicates th                                                                                         | This bit is cleared<br>at a Start bit has b<br>s not detected last                                         |                                                            |                                | led, SSPEN is clea<br>Reset)             | red.)               |                   |

| bit 2            | This bit holds th<br>next Start bit, Sl<br>In I <sup>2</sup> C Slave mo<br>1 = Read<br>0 = Write         | top bit, or not ACK<br>i <u>de:</u>                                                                        | ion following the                                          | last address mat               | ch. This bit is only v                   | valid from the add  | ress match to the |

|                  | 0 = Transmit is                                                                                          | s in progress<br>s not in progress                                                                         | SEN, PEN, RCE                                              | N or ACKEN will i              | ndicate if the MSS                       | P is in IDLE mode   |                   |

| bit 1            | 1 = Indicates th                                                                                         | dress bit (10-bit I <sup>2</sup><br>at the user needs<br>es not need to be                                 | to update the ad                                           | dress in the SSP               | kADD register                            |                     |                   |

| bit 0            | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C m</u><br>1 = Data transm                                  | nd I <sup>2</sup> C modes):<br>mplete, SSPxBUF<br>t complete, SSPxE<br>lode only):<br>nit in progress (doe | UF is empty<br>es not include the                          |                                | its), SSPxBUF is fi<br>s), SSPxBUF is em |                     |                   |

| Note 1:<br>2:    | Polarity of clock state<br>This bit is cleared on                                                        | •                                                                                                          |                                                            | •                              |                                          |                     |                   |

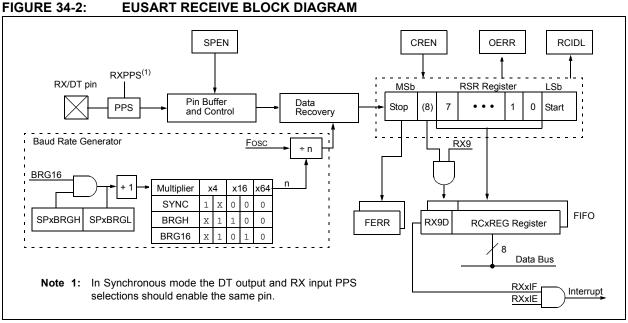

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 34-1, Register 34-2 and Register 34-3, respectively.

The RX input pin is selected with the RXPPS. The CK input is selected with the TXPPS register. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

## 34.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RXxIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCxREG is read after the overflow occurs but before the fifth rising edge then the fifth rising edge will set the RXxIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCxREG to clear RXxIF.

- 2. If RCIDL is '0' then wait for RDCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

## 34.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RXxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 34-7), and asynchronously if the device is in Sleep mode (Figure 34-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in IDLE mode waiting to receive the next character.

## 34.3.3.1 Special Considerations

### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

## Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## WUE Bit

The wake-up event causes a receive interrupt by setting the RXxIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## 35.7.4 35.6.4 INTERNAL RESISTOR WITH EXTERNAL CAPACITORS

In this configuration, the user can use the internal resistor ladders to generate the LCD bias levels, and use external capacitors to guard again burst currents. It is recommend the user utilize the external capacitors when driving large glass panels with a large pixels and a high pixel count. The external capacitors will help dampen current spikes during segment switching. Contrast is adjusted using the LCDCST<2:0> bits. The CFLYx pins are available as a GPIO. See Figure 35-7 for supported connections.

External capacitors can be used when voltage to the internal resistor ladder is supplied by VDD (LCDVSRC<3:0> = 0101) or an external source (LCDVSRC<3:0> = 0100). When supplying an external voltage to internal resistor ladder the external capacitors should be limited to VLCD2, and VLCD3.

© 2017 Microchip Technology Inc.

| R/W-0/0       | R/W-0/0                                                                                                                                                                      | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                            | R/W-0/0                                                                                                                                                                                    | R/W-0/0                                                                                                                                                        | R/W-0/0                                                                                                                                                     | R/W-0/0                                                                                   | R/W-0/0                                                                                                                                              |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                                                |                                                                                                                                                             |                                                                                           |                                                                                                                                                      |  |  |  |

| LRLAP1        | LRLAP0                                                                                                                                                                       | LRLBP1                                                                                                                                                                                                                                                                                                                                                                             | LRLBP0                                                                                                                                                                                     | LCDIRI                                                                                                                                                         | LRLAT2                                                                                                                                                      | LRLAT1                                                                                    | LRLAT0                                                                                                                                               |  |  |  |

| bit 7         |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                                                |                                                                                                                                                             |                                                                                           | bit 0                                                                                                                                                |  |  |  |

| Legend:       |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                                                |                                                                                                                                                             |                                                                                           |                                                                                                                                                      |  |  |  |

| -             | - h:t                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                    | h:+                                                                                                                                                                                        |                                                                                                                                                                | a anta d hit waar                                                                                                                                           |                                                                                           |                                                                                                                                                      |  |  |  |

| R = Readable  |                                                                                                                                                                              | W = Writable                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                            | -                                                                                                                                                              | nented bit, read                                                                                                                                            |                                                                                           |                                                                                                                                                      |  |  |  |

| -n = Value at | PUR                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                            | '0' = Bit is clea                                                                                                                                              | ared                                                                                                                                                        | x = Bit is unkr                                                                           | lown                                                                                                                                                 |  |  |  |

| bit 7-6       | During Time I<br>11 = Internal<br>10 = Internal<br>01 = Internal                                                                                                             | : LCD Reference<br>nterval A:<br>LCD reference<br>LCD reference<br>LCD reference<br>LCD reference                                                                                                                                                                                                                                                                                  | is the High-Po<br>ladder is powe<br>ladder is powe                                                                                                                                         | wer (HP) ladde<br>ered in Medium<br>ered in Low-Pov                                                                                                            | r<br>Power mode<br>wer mode                                                                                                                                 |                                                                                           |                                                                                                                                                      |  |  |  |

| bit 5-4       |                                                                                                                                                                              | : LCD Reference                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                          |                                                                                                                                                                |                                                                                                                                                             |                                                                                           |                                                                                                                                                      |  |  |  |

|               | 11 = Internal<br>10 = Internal<br>01 = Internal                                                                                                                              | During Time Interval B:<br>11 = Internal LCD reference ladder is powered in High-Power mode<br>10 = Internal LCD reference ladder is powered in Medium Power mode<br>01 = Internal LCD reference ladder is powered in Low-Power mode<br>00 = Internal LCD reference ladder is powered down and unconnected                                                                         |                                                                                                                                                                                            |                                                                                                                                                                |                                                                                                                                                             |                                                                                           |                                                                                                                                                      |  |  |  |

| bit 3         | Allows the Inte<br>mode 'B'<br>1 = When the<br>is disable                                                                                                                    | Internal Refere<br>ernal reference<br>LCD Reference<br>d<br>Internal Refere                                                                                                                                                                                                                                                                                                        | band gap buffe<br>e Ladder is in p                                                                                                                                                         | er to shut down<br>ower mode 'B',                                                                                                                              | the LCD Interna                                                                                                                                             | al Reference Ba                                                                           | and Gap buffer                                                                                                                                       |  |  |  |

| bit 2-0       | LRLAT<2:0>                                                                                                                                                                   | : LCD Reference                                                                                                                                                                                                                                                                                                                                                                    | e Ladder A Tir                                                                                                                                                                             | ne Interval Cor                                                                                                                                                | trol bits                                                                                                                                                   |                                                                                           |                                                                                                                                                      |  |  |  |

|               | Sets the num                                                                                                                                                                 | ber of 32 clock                                                                                                                                                                                                                                                                                                                                                                    | counts when t                                                                                                                                                                              | he A Time Inter                                                                                                                                                | val Power mod                                                                                                                                               | le is active.                                                                             |                                                                                                                                                      |  |  |  |

|               | 111 = Interna<br>110 = Interna<br>101 = Interna<br>100 = Interna<br>010 = Interna<br>001 = Interna<br>000 = Interna<br><u>For Type-B W</u><br>111 = Interna<br>110 = Interna | Aveforms (WF<br>I LCD reference<br>I LCD reference<br>Aveforms (WF<br>I LCD reference<br>I LCD reference | e ladder is in A<br>e ladder is alw<br>T = 1):<br>e ladder is in A<br>e ladder is in A | A Power mode f<br>A Power mode f<br>ays in B Power<br>A Power mode f<br>A Power mode f | or 6 clocks and<br>or 5 clocks and<br>or 4 clocks and<br>or 3 clocks and<br>or 2 clocks and<br>or 1 clock and<br>mode<br>or 7 clocks and<br>or 6 clocks and | I B Power mod<br>B Power mod<br>B Power mod<br>B Power mod<br>B Power mod<br>B Power mode | e for 10 clocks<br>e for 11 clocks<br>e for 12 clocks<br>e for 13 clocks<br>e for 14 clocks<br>e for 15 clocks<br>e for 25 clocks<br>e for 26 clocks |  |  |  |

|               | 100 = Interna<br>011 = Interna<br>010 = Interna<br>001 = Interna                                                                                                             | ILCD reference<br>ILCD reference<br>ILCD reference<br>ILCD reference<br>ILCD reference<br>ILCD reference                                                                                                                                                                                                                                                                           | e ladder is in A<br>e ladder is in A<br>e ladder is in A<br>e ladder is in A                                                                                                               | Power mode f<br>Power mode f<br>Power mode f<br>Power mode f                                                                                                   | or 4 clocks and<br>or 3 clocks and<br>or 2 clocks and<br>or 1 clock and                                                                                     | I B Power mod<br>I B Power mod<br>I B Power mod                                           | e for 28 clocks<br>e for 29 clocks<br>e for 30 clocks                                                                                                |  |  |  |

#### **REGISTER 35-7:** LCDRL: LCD INTERNAL REFERENCE LADDER CONTROL REGISTER

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                                                                                                                                       |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                                           |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                          |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |  |  |  |  |  |  |

| Address | Name   | Bit 7 | Bit 6         | Bit 5 | Bit 4              | Bit 3   | Bit 2       | Bit 1    | Bit 0   | Register<br>on page |  |  |  |

|---------|--------|-------|---------------|-------|--------------------|---------|-------------|----------|---------|---------------------|--|--|--|

| 1EEBh   | —      |       |               |       | Unimpl             | emented |             |          |         |                     |  |  |  |

| 1EECh   | _      |       |               |       | Unimpl             | emented |             |          |         |                     |  |  |  |

| 1EEDh   | _      |       |               |       | Unimpl             | emented |             |          |         |                     |  |  |  |

| 1EEEh   | _      |       | Unimplemented |       |                    |         |             |          |         |                     |  |  |  |

| 1EEFh   | —      |       | Unimplemented |       |                    |         |             |          |         |                     |  |  |  |

| 1F0Ch   |        |       |               |       | •                  | emented |             |          |         |                     |  |  |  |

| 1F0Dh   | _      |       |               |       | •                  | emented |             |          |         |                     |  |  |  |

| 1F0Eh   |        |       |               |       | •                  | emented |             |          |         |                     |  |  |  |

| 1F0Fh   | —      |       |               |       | · · ·              | emented |             |          |         | -                   |  |  |  |

| 1F10h   | RA0PPS | —     |               | —     | RA0PPS4            | RA0PPS3 | RA0PPS2     | RA0PPS1  | RA0PPS0 | 265                 |  |  |  |

| 1F11h   | RA1PPS | _     |               | _     | RA1PPS4            | RA1PPS3 | RA1PPS2     | RA1PPS1  | RA1PPS0 | 265                 |  |  |  |

| 1F12h   | RA2PPS | —     |               | _     | RA2PPS4            | RA2PPS3 | RA2PPS2     | RA2PPS1  | RA2PPS0 | 265                 |  |  |  |

| 1F13h   | RA3PPS | —     | —             | _     | RA3PPS4            | RA3PPS3 | RA3PPS2     | RA3PPS1  | RA3PPS0 | 265                 |  |  |  |

| 1F14h   | RA4PPS | —     | —             | —     | RA4PPS4            | RA4PPS3 | RA4PPS2     | RA4PPS1  | RA4PPS0 | 265                 |  |  |  |

| 1F15h   | RA5PPS | —     | —             | _     | RA5PPS4            | RA5PPS3 | RA5PPS2     | RA5PPS1  | RA5PPS0 | 265                 |  |  |  |

| 1F16h   | RA6PPS | —     | _             | _     | RA6PPS4            | RA6PPS3 | RA6PPS2     | RA6PPS1  | RA6PPS0 | 265                 |  |  |  |

| 1F17h   | RA7PPS | —     | _             | —     | RA7PPS4            | RA7PPS3 | RA7PPS2     | RA7PPS1  | RA7PPS0 | 265                 |  |  |  |

| 1F18h   | RB0PPS | _     | —             | _     | RB0PPS4            | RB0PPS3 | RB0PPS2     | RB0PPS1  | RB0PPS0 | 265                 |  |  |  |

| 1F19h   | RB1PPS | —     | —             | —     | RB1PPS4            | RB1PPS3 | RB1PPS2     | RB1PPS1  | RB1PPS0 | 265                 |  |  |  |

| 1F1Ah   | RB2PPS | —     | —             | _     | RB2PPS4            | RB2PPS3 | RB2PPS2     | RB2PPS1  | RB2PPS0 | 265                 |  |  |  |

| 1F1Bh   | RB3PPS | —     | —             | —     | RB3PPS4            | RB3PPS3 | RB3PPS2     | RB3PPS1  | RB3PPS0 | 265                 |  |  |  |

| 1F1Ch   | RB4PPS | —     | —             | _     | RB4PPS4            | RB4PPS3 | RB4PPS2     | RB4PPS1  | RB4PPS0 | 265                 |  |  |  |

| 1F1Dh   | RB5PPS | —     | —             | _     | RB5PPS4            | RB5PPS3 | RB5PPS2     | RB5PPS1  | RB5PPS0 | 265                 |  |  |  |

| 1F1Eh   | RB6PPS | _     | _             | _     | RB6PPS4            | RB6PPS3 | RB6PPS2     | RB6PPS1  | RB6PPS0 | 265                 |  |  |  |

| 1F1Fh   | RB7PPS | _     | _             | _     | RB7PPS4            | RB7PPS3 | RB7PPS2     | RB7PPS1  | RB7PPS0 | 265                 |  |  |  |

| 1F20h   | RC0PPS | _     | _             | _     | RC0PPS4            | RC0PPS3 | RC0PPS2     | RC0PPS1  | RC0PPS0 | 265                 |  |  |  |

| 1F21h   | RC1PPS | _     | —             | _     | RC1PPS4            | RC1PPS3 | RC1PPS2     | RC1PPS1  | RC1PPS0 | 265                 |  |  |  |

| 1F22h   | RC2PPS | _     | —             | _     | RC2PPS4            | RC2PPS3 | RC2PPS2     | RC2PPS1  | RC2PPS0 | 265                 |  |  |  |

| 1F23h   | RC3PPS | _     | _             | _     | RC3PPS4            | RC3PPS3 | RC3PPS2     | RC3PPS1  | RC3PPS0 | 265                 |  |  |  |

| 1F24h   | RC4PPS | _     |               | _     | RC4PPS4            | RC4PPS3 | RC4PPS2     | RC4PPS1  | RC4PPS0 | 265                 |  |  |  |

| 1F25h   | _      |       |               |       |                    | emented | 110 11 1 02 | 11011101 |         | 200                 |  |  |  |

| 1F26h   | RC6PPS | _     | _             | _     | RC6PPS4            | RC6PPS3 | RC6PPS2     | RC6PPS1  | RC6PPS0 | 265                 |  |  |  |

| 1F27h   | RC7PPS | _     |               | _     | RC7PPS4            | RC7PPS3 | RC7PPS2     | RC7PPS1  | RC7PPS0 | 265                 |  |  |  |

| 1F28h   | RD0PPS | _     | _             | _     | RD0PPS4            | RD0PPS3 | RD0PPS2     | RD0PPS1  | RD0PPS0 | 265                 |  |  |  |

| 1F29h   | RD1PPS | _     | _             | _     | RD1PPS4            | RD1PPS3 | RD1PPS2     | RD1PPS1  | RD1PPS0 | 265                 |  |  |  |

| 1F2Ah   | RD2PPS | _     | _             | _     | RD1PP34<br>RD2PPS4 | RD2PPS3 | RD2PPS2     |          | RD2PPS0 | 265                 |  |  |  |

|         |        | _     | _             | _     |                    |         |             | RD2PPS1  |         |                     |  |  |  |

| 1F2Bh   | RD3PPS |       |               | _     | RD3PPS4            | RD3PPS3 | RD3PPS2     | RD3PPS1  | RD3PPS0 | 265                 |  |  |  |

| 1F2Ch   | RD4PPS |       |               |       | RD4PPS4            | RD4PPS3 | RD4PPS2     | RD4PPS1  | RD4PPS0 | 265                 |  |  |  |

| 1F2Dh   | RD5PPS | _     | _             | _     | RD5PPS4            | RD5PPS3 | RD5PPS2     | RD5PPS1  | RD5PPS0 | 265                 |  |  |  |

| 1F2Eh   | RD6PPS | _     |               | _     | RD6PPS4            | RD6PPS3 | RD6PPS2     | RD6PPS1  | RD6PPS0 | 265                 |  |  |  |

| 1F2Fh   | RD7PPS | _     |               |       | RD7PPS4            | RD7PPS3 | RD7PPS2     | RD7PPS1  | RD7PPS0 | 265                 |  |  |  |

| 1F30h   | RE0PPS | —     | _             | _     | RE0PPS4            | RE0PPS3 | RE0PPS2     | RE0PPS1  | RE0PPS0 | 265                 |  |  |  |

| 1F31h   | RE1PPS | —     | —             | —     | RE1PPS4            | RE1PPS3 | RE1PPS2     | RE1PPS1  | RE1PPS0 | 265                 |  |  |  |

| 1F32h   | RE2PPS | —     |               | —     | RE2PPS4            | RE2PPS3 | RE2PPS2     | RE2PPS1  | RE2PPS0 | 265                 |  |  |  |

## TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

$Legend: \quad x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.$

**Note** 1: Unimplemented data memory locations, read as '0'.