Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 31x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

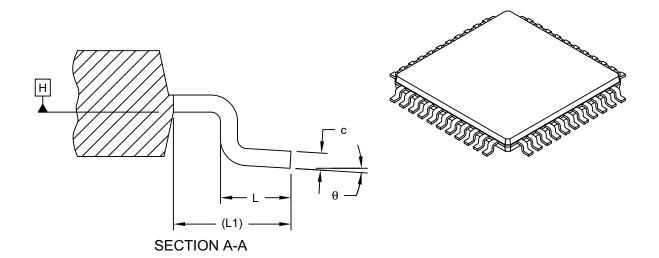

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19176-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

## 5.3.2 DATA MEMORY PROTECTION

The entire data EEPROM is protected from external reads and writes by the WRTD bit in the Configuration Words. When WRTD = 0, external reads and writes of EEPROM memory are inhibited and a read will return all '0's. The CPU can continue to read and write EEPROM memory, regardless of the protection bit settings.

## 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

## 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.4.7 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F191XX Memory Programming Specification"* (DS40001880).

| Name    | Bit 7   | Bit 6   | Bit 5     | Bit 4 | Bit 3   | Bit 2 | Bit 1     | Bit 0 | Register<br>on Page |

|---------|---------|---------|-----------|-------|---------|-------|-----------|-------|---------------------|

| OSCCON1 | —       |         | NOSC<2:0> |       |         | NDIV< | 3:0>      |       | 152                 |

| OSCCON2 | —       |         | COSC<2:0> |       |         | CDIV< | 3:0>      |       | 152                 |

| OSCCON3 | CWSHOLD | SOSCPWR | _         | ORDY  | NOSCR   | _     | _         | -     | 154                 |

| OSCFRQ  | _       | _       | _         | _     | _       | Н     | FFRQ<2:0> |       | 157                 |

| OSCSTAT | EXTOR   | HFOR    | MFOR      | LFOR  | SOR     | ADOR  | —         | PLLR  | 155                 |

| OSCTUNE | —       | _       |           |       | HFTUN   | <5:0> |           |       | 157                 |

| OSCEN   | EXTOEN  | HFOEN   | MFOEN     | LFOEN | SOSCEN  | ADOEN | _         | _     | 156                 |

| ACTCON  | ACTEN   | ACTUD   | _         | _     | ACTLOCK | _     | ACTORS    |       | 158                 |

## TABLE 9-3:SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 9-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2     | Bit 9/1 | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|--------------|---------|----------|---------------------|

| CONFIG1 | 13:8 | —       | _       | FCMEN      | _        | CSWEN    | LCDPEN       | VBATEN  | CLKOUTEN | 100                 |

| CONFIGT | 7:0  | —       | F       | RSTOSC<2:0 | >        | _        | FEXTOSC<2:0> |         |          | 120                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## 10.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) of the PIEx[y] registers for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers)

The PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, PIR7 and PIR8 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while interrupts are enabled:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 10.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupts operation, refer to its peripheral chapter.

| Note 1: | Individual interrupt flag bits are set, regardless of the state of any other enable bits.                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 2:      | All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced |

|         |                                                                                                                                  |

when the GIE bit is set again.

## 10.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The interrupt is sampled during Q1 of the instruction cycle. The actual interrupt latency then depends on the instruction that is executing at the time the interrupt is detected. See Figure 10-2 and Figure 10-3 for more details.

## 10.6 Register Definitions: Interrupt Control

## REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0        | /0 R/W-0/0                               | U-0                                    | U-0       | U-0          | U-0              | U-0            | R/W-1/1      |

|--------------|------------------------------------------|----------------------------------------|-----------|--------------|------------------|----------------|--------------|

| GIE          | PEIE                                     | —                                      | —         | _            | —                | _              | INTEDG       |

| bit 7        |                                          |                                        |           |              |                  |                | bit 0        |

|              |                                          |                                        |           |              |                  |                |              |

| Legend:      |                                          |                                        |           |              |                  |                |              |

| R = Read     | able bit                                 | W = Writable                           | bit       | U = Unimpler | mented bit, read | as '0'         |              |

| u = Bit is   | unchanged                                | x = Bit is unkr                        | nown      | -n/n = Value | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is | set                                      | '0' = Bit is cle                       | ared      |              |                  |                |              |

|              |                                          |                                        |           |              |                  |                |              |

| bit 7        | GIE: Global I                            | nterrupt Enable                        | e bit     |              |                  |                |              |

|              | 1 = Enables                              | all active interru                     | upts      |              |                  |                |              |

|              | 0 = Disables                             | all interrupts                         |           |              |                  |                |              |

| bit 6        |                                          | eral Interrupt E                       |           |              |                  |                |              |

|              |                                          | all active periph<br>all peripheral ir |           | 6            |                  |                |              |

| bit 5-1      |                                          | nted: Read as '                        | •         |              |                  |                |              |

| bit 0        | •                                        |                                        |           |              |                  |                |              |

|              |                                          | errupt Edge Sel<br>on rising edge      |           |              |                  |                |              |

|              |                                          | on falling edge                        |           |              |                  |                |              |

|              |                                          |                                        |           |              |                  |                |              |

| Note:        | Interrupt flag bits a                    |                                        |           |              |                  |                |              |

|              | condition occurs, r<br>its corresponding | •                                      |           |              |                  |                |              |

|              | Enable bit, GIE, o                       |                                        |           |              |                  |                |              |

|              | User software                            | should ensu                            | •         |              |                  |                |              |

|              | appropriate interr                       |                                        | are clear |              |                  |                |              |

|              | prior to enabling a                      | in interrupt.                          |           |              |                  |                |              |

| Name    | Bit 7   | Bit 6   | Bit 5      | Bit 4  | Bit 3     | Bit 2 | Bit 1    | Bit 0   | Register<br>on Page |

|---------|---------|---------|------------|--------|-----------|-------|----------|---------|---------------------|

| OSCCON1 | —       | 1       | NOSC<2:0>  |        |           | NDIV< | 3:0>     |         | 152                 |

| OSCCON2 | _       | (       | COSC<2:0>  |        |           | CDIV< | 3:0>     |         | 152                 |

| OSCCON3 | CSWHOLD | SOSCPWR | —          | ORDY   | NOSCR     | —     | —        | —       | 154                 |

| PCON0   | STKOVF  | STKUNF  | WDTWV      | RWDT   | RMCLR     | RI    | POR      | BOR     | 140                 |

| STATUS  | _       | —       | _          | TO     | PD        | Z     | DC       | С       | 50                  |

| WDTCON0 | _       | —       |            |        | WDTPS<4:0 | )>    |          | SWDTEN  | 196                 |

| WDTCON1 | _       | v       | VDTCS<2:0> |        | —         | WI    | NDOW<2:0 | >       | 197                 |

| WDTPSL  |         |         |            | PSCN   | T<7:0>    |       |          |         | 198                 |

| WDTPSH  |         |         |            | PSCN   | T<15:8>   |       |          |         | 198                 |

| WDTTMR  | —       |         | WDTTM      | R<3:0> |           | STATE | PSCNT    | <17:16> | 198                 |

## TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH WINDOWED WATCHDOG TIMER

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|----------|---------|----------|---------------------|

|         | 13:8 | —       |         | FCMEN      |          | CSWEN    | LCDPEN   | VBATEN  | CLKOUTEN | 100                 |

| CONFIG1 | 7:0  | _       | F       | RSTOSC<2:0 | >        | _        | F        | 120     |          |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

## 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 39-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 14.2.6 ANALOG CONTROL

The ANSELA register (Register 14-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 14.2.7 WEAK PULL-UP CONTROL

The WPUA register (Register 14-5) controls the individual weak pull-ups for each PORT pin.

#### 14.2.8 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| R/W-0/0                 | R/W-0/0                                                                        | U-0                                                                                                                            | R/W-0/0                          | U-0            | U-0              | U-0              | R/W-0/0      |

|-------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|------------------|------------------|--------------|

| UART2MD                 | UART1MD                                                                        | —                                                                                                                              | MSSP1MD                          | —              | —                | —                | CWG1MD       |

| bit 7                   |                                                                                |                                                                                                                                |                                  |                |                  |                  | bit 0        |

|                         |                                                                                |                                                                                                                                |                                  |                |                  |                  |              |

| Legend:                 |                                                                                |                                                                                                                                |                                  |                |                  |                  |              |

| R = Readable            | bit                                                                            | W = Writable b                                                                                                                 | bit                              | U = Unimplem   | ented bit, read  | as '0'           |              |

| u = Bit is unch         | nanged                                                                         | x = Bit is unkn                                                                                                                | own                              | -n/n = Value a | t POR and BOR    | R/Value at all o | other Resets |

| '1' = Bit is set        |                                                                                | '0' = Bit is clea                                                                                                              | ired                             | q = Value dep  | ends on conditio | on               |              |

| bit 7<br>bit 6<br>bit 5 | 1 = EUSART2<br>0 = EUSART2<br><b>UART1MD</b> : D<br>1 = EUSART2<br>0 = EUSART2 | isable EUSAR <sup>-</sup><br>2 module disab<br>2 module enabl<br>isable EUSAR <sup>-</sup><br>1 module disab<br>1 module enabl | led<br>ed<br>F1 bit<br>led<br>ed |                |                  |                  |              |

| bit 4                   | MSSP1MD: D<br>1 = MSSP1 m                                                      | ted: Read as '0<br>bisable MSSP1<br>nodule disablec<br>nodule enabled                                                          | bit                              |                |                  |                  |              |

| bit 3-1<br>bit 0        | -                                                                              | ted: Read as '0<br>sable CWG1 bi                                                                                               |                                  |                |                  |                  |              |

|                         | 1 = CWG1 m                                                                     | odule disabled<br>odule enabled                                                                                                | -                                |                |                  |                  |              |

## REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

#### REGISTER 19-8: ADPCH: ADC POSITIVE CHANNEL SELECTION REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | ADPC    | H<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

ADPCH<5:0>: ADC Positive Input Channel Selection bits

| ADPCH | Dev | vice Pin Co | ount | ADC Input  | ADPCH | Device Pin Cou                       | int |    | A          |

|-------|-----|-------------|------|------------|-------|--------------------------------------|-----|----|------------|

| <5:0> | 28  | 40          | 48   | Connection | <5:0> | 28                                   | 40  | 48 | Connection |

| 0x00  | •   | •           | •    | RA0        | 0x20  | _                                    | •   | •  |            |

| 0x01  | •   | •           | •    | RA1        | 0x21  | _                                    | •   | •  |            |

| 0x02  | •   | •           | •    | RA2        | 0x22  | _                                    | •   | •  |            |

| 0x03  | •   | •           | •    | RA3        | 0x23  | _                                    | _   | _  |            |

| 0x04  | •   | •           | •    | RA4        | 0x24  | _                                    | _   | _  | F          |

| 0x05  | _   | —           | _    | RA5        | 0x25  | _                                    | —   | _  | F          |

| 0x06  | •   | •           | •    | RA6        | 0x26  | _                                    | _   | _  | F          |

| 0x07  | •   | •           | •    | RA7        | 0x27  | _                                    | —   | _  | F          |

| 0x08  | •   | •           | •    | RB0        | 0x28  | _                                    | —   | •  | F          |

| 0x09  | •   | •           | •    | RB1        | 0x29  | _                                    | _   | •  | F          |

| 0x0A  | •   | •           | •    | RB2        | 0x2A  | —                                    | _   | •  | F          |

| 0x0B  | •   | •           | •    | RB3        | 0x2B  | _                                    | —   | •  | F          |

| 0x0C  | •   | •           | •    | RB4        | 0x2C  | _                                    | _   | •  | F          |

| 0x0D  | •   | •           | •    | RB5        | 0x2D  | _                                    | —   | •  | F          |

| 0x0E  | •   | •           | •    | RB6        | 0x2E  | _                                    | —   | •  | F          |

| 0x0F  | •   | •           | •    | RB7        | 0x2F  | _                                    | _   | •  | F          |

| 0x10  | _   | _           | _    | RC0        | 0x30  | _                                    | _   | _  | F          |

| 0x11  | _   | _           | _    | RC1        | 0x31  | _                                    |     | _  | F          |

| 0x12  | •   | •           | •    | RC2        | 0x32  | _                                    | —   | _  | F          |

| 0x13  | •   | •           | •    | RC3        | 0x33  | _                                    | —   | _  | F          |

| 0x14  | •   | •           | •    | RC4        | 0x34  | _                                    | —   | _  | F          |

| 0x15  | —   | —           | —    | RC5        | 0x35  | _                                    | —   | —  | F          |

| 0x16  | •   | •           | •    | RC6        | 0x36  | _                                    | —   | —  | F          |

| 0x17  | •   | •           | •    | RC7        | 0x37  | —                                    | —   | —  | F          |

| 0x18  | —   | •           | •    | RD0        | 0x38  | _                                    | —   | _  |            |

| 0x19  |     | •           | •    | RD1        | 0x39  | VLCD3 divided by 4 <sup>(4)</sup>    |     |    |            |

| 0x1A  |     | •           | •    | RD2        | 0x3A  | VBAT divided by 3 <sup>(5)</sup>     |     |    |            |

| 0x1B  | _   | •           | •    | RD3        | 0x3B  | AVss (Analog Ground)                 |     |    |            |

| 0x1C  | _   | •           | •    | RD4        | 0x3C  | Temperature Indicator <sup>(3)</sup> |     |    |            |

| 0x1D  | _   | •           | •    | RD5        | 0x3D  | DAC1 Output <sup>(1)</sup>           |     |    |            |

| 0x1E  | _   | •           | •    | RD6        | 0x3E  | FVR Buffer 1 <sup>(2)</sup>          |     |    |            |

| 0x1F  | _   | •           | •    | RD7        | 0x3F  | FVR Buffer 2 <sup>(2)</sup>          |     |    |            |

Note 1: See Section 19.0 "Analog-to-Digital Converter with Computation (ADC2) Module" for more information.

2: See Section 18.0 "Fixed Voltage Reference (FVR)" for more information.

3: See Section 20.0 "Temperature Indicator Module (TIM)" for more information.

4: See Section 35.0 "Liquid Crystal Display (LCD) Controller" for more information.

5: See Section 8.0 "Resets and Vbat" for more information.

## PIC16(L)F19155/56/75/76/85/86

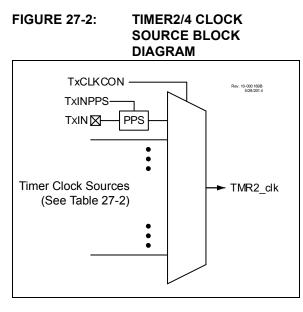

## 27.1 Timer2/4 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset

- · External Reset Source event that resets the timer.

Note: TMR2 is not cleared when T2CON is written.

## 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2

to 00h on the next rising TMR2\_clk edge and increments the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

## 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

## 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

## 27.2 Timer2/4 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 29.0 "Capture/Compare/PWM Modules"** for more details on setting up Timer2/4 for use with the CCP, as well as the timing diagrams in **Section 27.5 "Operation Examples"** for examples of how the varying Timer2 modes affect CCP PWM output.

## 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

## 29.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more details.

The CCP output can also be used as an input for other peripherals.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 29.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 29.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to Section 19.2.6 "ADC Conversion Procedure (Basic Mode)" for more information.

| Note: | Removing the match condition by            |

|-------|--------------------------------------------|

|       | changing the contents of the CCPRxH        |

|       | and CCPRxL register pair, between the      |

|       | clock edge that generates the              |

|       | Auto-conversion Trigger and the clock      |

|       | edge that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring          |

#### 29.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

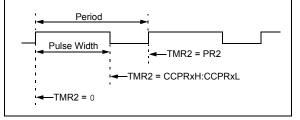

#### 29.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 29-3 shows a typical waveform of the PWM signal.

#### 29.3.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 29-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 29-3: CCP P

CCP PWM OUTPUT SIGNAL

## 31.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 31-12.

#### 31.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External input

#### 31.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

#### 31.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT\_sync

- · Timer2 TMR2\_postscaled

- CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 31-6).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

## 31.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

## 31.13 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripherals are shown in Section 1.1 "Register and Bit Naming Conventions".

#### REGISTER 31-1: CWG1CON0: CWG1 CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> |     | —   | _   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <ul> <li>EN: CWG1 Enable bit</li> <li>1 = Module is enabled</li> <li>0 = Module is disabled</li> </ul>                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | LD: CWG1 Load Buffer bits <sup>(1)</sup><br>1 = Buffers to be loaded on the next rising/falling event<br>0 = Buffers not loaded                                                                                                                                                                                                                                                         |

| bit 5-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0 | MODE<2:0>: CWG1 Mode bits<br>111 = Reserved<br>110 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>011 = CWG outputs operate in Reverse Full-Bridge mode<br>010 = CWG outputs operate in Forward Full-Bridge mode<br>001 = CWG outputs operate in Synchronous Steering mode<br>000 = CWG outputs operate in Steering mode |

**Note 1:** This bit can only be set after EN = 1 and cannot be set in the same instruction that EN is set.

#### 33.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

| TABLE 33-1: | I <sup>2</sup> C BUS TERMS |

|-------------|----------------------------|

|-------------|----------------------------|

| TERM                | Description                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one<br>master at a time controls the bus.<br>Winning arbitration ensures that<br>the message is not corrupted.                                                     |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                     |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                    |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                       |

#### 33.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-12 shows wave forms for Start and Stop conditions.

33.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

#### 33.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 33-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

#### 33.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

## 34.6 Register Definitions: EUSART Control

## REGISTER 34-1: TXxSTA: TRANSMIT STATUS AND CONTROL REGISTER

|                  | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0/0                                                                                                                                                                 | R/W-0/0                                                                                    | R/W-0/0       | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TXEN <sup>(1)</sup>                                                                                                                                                     | SYNC                                                                                       | SENDB         | BRGH             | TRMT             | TX9D         |

| pit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |                                                                                            |               |                  |                  | bit          |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |                                                                                            |               |                  |                  |              |

| egend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |                                                                                            |               |                  |                  |              |

| R = Readable b   | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | W = Writable                                                                                                                                                            | bit                                                                                        | •             | mented bit, read |                  |              |

| u = Bit is uncha | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x = Bit is unkr                                                                                                                                                         | nown                                                                                       | -n/n = Value  | at POR and BO    | R/Value at all o | other Resets |

| 1' = Bit is set  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '0' = Bit is cle                                                                                                                                                        | ared                                                                                       |               |                  |                  |              |

| oit 7            | CSPC: Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Source Select                                                                                                                                                           | hit                                                                                        |               |                  |                  |              |

| JIL 7            | Asynchronou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                         | DIL                                                                                        |               |                  |                  |              |

|                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | s mode – value                                                                                                                                                          | ianored                                                                                    |               |                  |                  |              |