Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 31x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19176t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

# 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack"** for more details.

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers, program memory, and data EEPROM, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6 "Indirect Addressing"** for more details.

# 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 37.0 "Instruction Set Summary"** for more details.

# 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM (GPR)

- Common RAM

- Data EEPROM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device         | Program Flash Memory Size (Words) | Last Program Memory Address |  |  |

|----------------|-----------------------------------|-----------------------------|--|--|

| PIC16(L)F19155 | 8k                                | 1FFFh                       |  |  |

| PIC16(L)F19175 | 8k                                | 1FFFh                       |  |  |

| PIC16(L)F19185 | 8k                                | 1FFFh                       |  |  |

| PIC16(L)F19156 | 16k                               | 3FFFh                       |  |  |

| PIC16(L)F19176 | 16k                               | 3FFFh                       |  |  |

| PIC16(L)F19186 | 16k                               | 3FFFh                       |  |  |

# 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing  $32K \times 14$  program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

| Address | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4          | Bit 3               | Bit 2     | Bit 1  | Bit 0   | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|----------|--------|--------|--------|----------------|---------------------|-----------|--------|---------|-----------------------|----------------------------|

| Bank 0  |          |        |        |        | •              | •                   | •         | •      | •       | •                     | •                          |

|         |          |        |        | CPU    | CORE REGISTERS | ; see Table 4-3 for | specifics |        |         |                       |                            |

|         | [        |        |        |        |                | ,<br>               |           |        |         |                       | Γ                          |

| 0Ch     | PORTA    | RA7    | RA6    | RA5    | RA4            | RA3                 | RA2       | RA1    | RA0     | XXXX XXXX             | uuuu uuuu                  |

| 0Dh     | PORTB    | RB7    | RB6    | RB5    | RB4            | RB3                 | RB2       | RB1    | RB0     | XXXX XXXX             | uuuu uuuu                  |

| 0Eh     | PORTC    | RC7    | RC6    | _      | RC4            | RC3                 | RC2       | RC1    | RC0     | xxxx xxxx             | uuuu uuuu                  |

| 0Fh     | PORTD    | RD7    | RD6    | RD5    | RD4            | RD3                 | RD2       | RD1    | RD0     | xxxx xxxx             | uuuu uuuu                  |

| 010h    | PORTE    | RE7    | RE6    | RE5    | RE4            | RE3                 | —         | RE1    | RE0     | xxxx xxxx             | uuuu uuuu                  |

| 011h    | PORTF    | RF7    | RF6    | RF5    | RF4            | RF3                 | RF2       | RF1    | RF0     | xxxx xxxx             | uuuu uuuu                  |

| 012h    | TRISA    | TRISA7 | TRISA6 | TRISA5 | TRISA4         | TRISA3              | TRISA2    | TRISA1 | TRISA0  | 1111 1111             | 1111 1111                  |

| 013h    | TRISB    | TRISB7 | TRISB6 | TRISB5 | TRISB4         | TRISB3              | TRISB2    | TRISB1 | TRISB0  | 1111 1111             | 1111 1111                  |

| 014h    | TRISC    | TRISC7 | TRISC6 | TRISC5 | TRISC4         | TRISC3              | TRISC2    | TRISC1 | TRISC0  | 1111 1111             | 1111 1111                  |

| 015h    | TRISD    | TRISD7 | TRISD6 | TRISD5 | TRISD4         | TRISD3              | TRISD2    | TRISD1 | TRISD0  | 1111 1111             | 1111 1111                  |

| 016h    | TRISE    | TRISE7 | TRISE6 | TRISE5 | TRISE4         | TRISE3              | _         | TRISE1 | TRISE0  | 1111 1111             | 1111 1111                  |

| 017h    | TRISF    | TRISF7 | TRISF6 | TRISF5 | TRISF4         | TRISF3              | TRISF2    | TRISF1 | TRISF0  | 1111 1111             | 1111 1111                  |

| 018h    | LATA     | LATA7  | LATA6  | LATA5  | LATA4          | LATA3               | LATA2     | LATA1  | LATA0   | xxxx xxxx             | uuuu uuuu                  |

| 019h    | LATB     | LATB7  | LATB6  | LATB5  | LATB4          | LATB3               | LATB2     | LATB1  | LATB0   | xxxx xxxx             | uuuu uuuu                  |

| 01Ah    | LATC     | LATC7  | LATC6  | LATC5  | LATC4          | LATC3               | LATC2     | LATC1  | LATC0   | xxxx xxxx             | uuuu uuuu                  |

| 01Bh    | LATD     | LATD7  | LATD6  | LATD5  | LATD4          | LATD3               | LATD2     | LATD1  | LATD0   | xxxx xxxx             | uuuu uuuu                  |

| 01Ch    | LATE     | LATE7  | LATE6  | LATE5  | LATE4          | LATE3               | _         | LATE1  | LATE0   | xxxx xxxx             | uuuu uuuu                  |

| 01Dh    | LATF     | LATF7  | LATF6  | LATF5  | LATF4          | LATF3               | LATF2     | LATF1  | LATF0   | xxxx xxxx             | uuuu uuuu                  |

| 01Eh    | _        |        |        |        | Unimpler       | nented              |           | •      |         |                       |                            |

| 01Fh    | ADCPCON0 | ADCPON | _      | _      | —              | —                   | —         | —      | ADCPRDY | xx                    | uu                         |

## TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| Address | Name     | Bit 7  | Bit 6             | Bit 5                 | Bit 4          | Bit 3                | Bit 2      | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|----------|--------|-------------------|-----------------------|----------------|----------------------|------------|-----------|-----------|-----------------------|----------------------------|

| Bank 2  |          |        |                   |                       |                |                      |            |           |           | •                     |                            |

|         |          |        |                   | CPU                   | CORE REGISTERS | S; see Table 4-3 for | specifics  |           |           |                       |                            |

| 10Ch    | ADACQL   |        |                   |                       | ACQ<           | :7:0>                |            |           |           | 0000 0000             | 0000 0000                  |

| 10Dh    | ADACQH   | _      | _                 | _                     |                |                      | ACQ<4:0>   |           |           | 0000 0000             | 0000 0000                  |

| 10Eh    | ADCAP    | _      | _                 | _                     |                |                      | ADCAP<4:0> |           |           | 0000 0000             | 0000 000                   |

| 10Fh    | ADPREL   |        |                   |                       | PRE<           | 7:0>                 |            |           |           | 0000 0000             | 0000 000                   |

| 110h    | ADPREH   |        | _                 |                       |                |                      | PRE<4:0>   |           |           | 0000 0000             | 0000 000                   |

| 111h    | ADCON0   | ON     | CONT              | _                     | CS             | _                    | FM         | _         | GO        | 00-0 -x-0             | 00-0 -0-                   |

| 112h    | ADCON1   | PPOL   | IPEN              | GPOL                  |                | _                    | _          | _         | DSEN      | 0000                  | 000                        |

| 113h    | ADCON2   | PSIS   |                   | CRS<2:0> ACLR MD<2:0> |                |                      |            |           | 0000 0000 | 0000 000              |                            |

| 114h    | ADCON3   | _      |                   | CALC<2:0>             |                | SOI                  |            | TMD<2:0>  |           | 0000 0000             | 0000 000                   |

| 115h    | ADSTAT   | OV     | UTHR              | LTHR                  | MATH           |                      |            | STAT<2:0> |           | 0000 -000             | 0000 -00                   |

| 116h    | ADREF    | _      | _                 | _                     | _              | _                    | _          | PRE       | F<1:0>    | 0000 0000             | 0000 000                   |

| 117h    | ADACT    | —      | _                 | _                     |                |                      | ACT<4:0>   |           |           | 0000 0000             | 0000 000                   |

| 118h    | ADCLK    | —      | —                 |                       |                | CS<5                 | :0>        |           |           | 0000 0000             | 0000 000                   |

| 119h    | RC1REG   |        |                   |                       | RC1F           | REG                  |            |           |           | 0000 0000             | 0000 000                   |

| 11Ah    | TX1REG   |        |                   |                       | TX1F           | REG                  |            |           |           | 0000 0000             | 0000 000                   |

| 11Bh    | SP1BRGL  |        | SP1BRGL 0000 0000 |                       |                |                      |            |           | 0000 000  |                       |                            |

| 11Ch    | SP1BRGH  |        |                   |                       | SP1B           | RGH                  |            |           |           | 0000 0000             | 0000 000                   |

| 11Dh    | RC1STA   | SPEN   | RX9               | SREN                  | CREN           | ADDEN                | FERR       | OERR      | RX9D      | 0000 0000             | 0000 000                   |

| 11Eh    | TX1STA   | CSRC   | TX9               | TXEN                  | SYNC           | SENDB                | BRGH       | TRMT      | TX9D      | 0000 0010             | 0000 001                   |

| 11Fh    | BAUD1CON | ABDOVF | RCIDL             | _                     | SCKP           | BRG16                | —          | WUE       | ABDEN     | 01-0 0-00             | 01-0 0-0                   |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

# 6.0 DEVICE INFORMATION AREA

The Device Information Area (DIA) is a dedicated region in the program memory space, it is a new feature in the PIC16(L)F19155/56/75/76/85/86 family of devices. The DIA contains the calibration data for the internal temperature indicator module, stores the Microchip Unique Identifier words and the Fixed Voltage Reference voltage readings measured in mV.

The complete DIA table is shown in Table 6-1, followed by a description of each region and its functionality. The data is mapped from 8100h to 811Fh in the PIC16(L)F19155/56/75/76/85/86 family. These locations are read-only and cannot be erased or modified. The data is programmed into the device during manufacturing.

TABLE 6-1: DEVICE INFORMATION AREA

| Address Range | Name of Region        | Standard Device Information                                    |  |  |  |  |

|---------------|-----------------------|----------------------------------------------------------------|--|--|--|--|

|               | MUI0                  |                                                                |  |  |  |  |

|               | MUI1                  |                                                                |  |  |  |  |

|               | MUI2                  |                                                                |  |  |  |  |

|               | MUI3                  |                                                                |  |  |  |  |

| 8100h-8108h   | MUI4                  | Microchip Unique Identifier (9 Words)                          |  |  |  |  |

|               | MUI5                  |                                                                |  |  |  |  |

|               | MUI6                  |                                                                |  |  |  |  |

|               | MUI7                  |                                                                |  |  |  |  |

|               | MUI8                  |                                                                |  |  |  |  |

| 8109h         | MUI9                  | 1 Word Reserved                                                |  |  |  |  |

|               | EUI0                  |                                                                |  |  |  |  |

| 810Ah-8111h   | EUI1                  |                                                                |  |  |  |  |

|               | EUI2                  |                                                                |  |  |  |  |

|               | EUI3                  |                                                                |  |  |  |  |

|               | EUI4                  | Unassigned (8 Words)                                           |  |  |  |  |

|               | EUI5                  |                                                                |  |  |  |  |

|               | EUI6                  | 7                                                              |  |  |  |  |

|               | EUI7                  |                                                                |  |  |  |  |

| 8112h         | TSLR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8113h         | TSLR2                 | Temperature indicator ADC reading at 90°C (low-range setting)  |  |  |  |  |

| 8114h         | TSLR3                 | Unassigned(1 word)                                             |  |  |  |  |

| 8115h         | TSHR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8116h         | TSHR2                 | Temperature indicator ADC reading at 90°C (high-range setting) |  |  |  |  |

| 8117h         | TSHR3                 | Unassigned (1 Word)                                            |  |  |  |  |

| 8118h         | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)                 |  |  |  |  |

| 8119h         | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)                 |  |  |  |  |

| 811Ah         | FVRA4X <sup>(1)</sup> | ADC FVR1 Output Voltage for 4x setting (in mV)                 |  |  |  |  |

| 811Bh         | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV)          |  |  |  |  |

| 811Ch         | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV)          |  |  |  |  |

| 811Dh         | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV)          |  |  |  |  |

| 811Eh-811Fh   |                       | Unassigned (1 Word)                                            |  |  |  |  |

**Note 1:** Value not present on LF devices.

|         |         |         | -       |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| R/W-1/1 |

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

# REGISTER 14-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRB<7:0>: PORTB Slew Rate Enable bits For RB<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 14-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

# Legend:

| Legena.              |                      |                                                       |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |  |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits

For RB<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

## REGISTER 14-17: HIDRVB: PORTB HIGH DRIVE CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|-----|-----|-----|-----|---------|-------|

| —     | —   | —   | —   | —   | —   | HIDB1   | —     |

| bit 7 |     |     |     |     |     |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'.              |

|---------|------------------------------------------|

| bit 1   | HIDB1: PORTB High Drive Enable bit       |

|         | For RB1 pin                              |

|         | 1 = High current source and sink enabled |

|         | 0 = Standard current source and sink     |

| bit 0   | Unimplemented: Read as '0'.              |

| R/W-1/1                                 | R/W-1/1 | R/W-1/1           | R/W-1/1        | R/W-1/1        | R/W-1/1          | R/W-1/1      | R/W-1/1 |

|-----------------------------------------|---------|-------------------|----------------|----------------|------------------|--------------|---------|

| SLRD7                                   | SLRD6   | SLRD5             | SLRD4          | SLRD3          | SLRD2            | SLRD1        | SLRD0   |

| bit 7                                   |         |                   |                |                |                  |              | bit 0   |

|                                         |         |                   |                |                |                  |              |         |

| Legend:                                 |         |                   |                |                |                  |              |         |

| R = Readable                            | bit     | W = Writable      | bit            | U = Unimpler   | mented bit, read | as '0'       |         |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value a | at POR and BOI | R/Value at all c | other Resets |         |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared           |                |                  |              |         |

# REGISTER 14-31: SLRCOND: PORTD SLEW RATE CONTROL REGISTER<sup>(1)</sup>

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits For RD<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

**Note 1:** Not available on the PIC16(L)F19155/56 family of devices.

## **REGISTER 14-32:** INLVLD: PORTD INPUT LEVEL CONTROL REGISTER<sup>(1)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

**Note 1:** Not available on the PIC16(L)F19155/56 family of devices.

## 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| FIGURE 27-5: | HARDWARE GATE MODE TIMING DIAGRAM ( | (MODE = 00001) |  |

|--------------|-------------------------------------|----------------|--|

|              |                                     |                |  |

|                                 | Rev. 10.001988<br>500/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| TMRx_clk                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| TMRx_ers_                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| TMRx                            | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1$ |  |

| TMRx_postscaled_                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

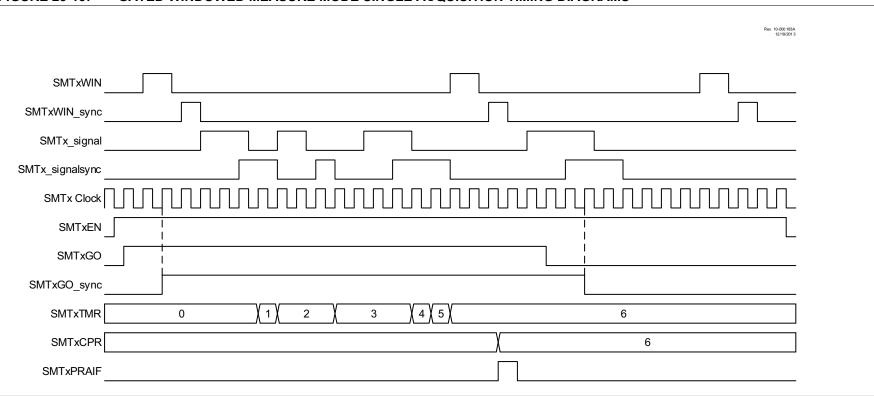

# FIGURE 28-13: GATED WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAMS

PIC16(L)F19155/56/75/76/85/86

## 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

### 29.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | CCPxCON     | ;Set Bank bits to point<br>;to CCPxCON |

|---------|-------------|----------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                   |

| CLRF    | CCPXCON     | , TUTH CCP MODULE OIL                  |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                   |

|         |             | ;the new prescaler                     |

|         |             | ;move value and CCP ON                 |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this                |

|         |             | ;value                                 |

| 1       |             |                                        |

## 29.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

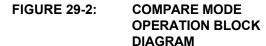

## 29.2 Compare Mode

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 29-2 shows a simplified diagram of the compare operation.

# 30.2 Register Definitions: PWM Control

# REGISTER 30-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0          | U-0                               | R-0               | R/W-0/0  | U-0                                | U-0           | U-0            | U-0          |  |  |

|------------------|-----------------------------------|-------------------|----------|------------------------------------|---------------|----------------|--------------|--|--|

| PWMxEN           | —                                 | PWMxOUT           | PWMxPOL  | —                                  | —             | —              | —            |  |  |

| bit 7            |                                   |                   |          |                                    |               |                | bit 0        |  |  |

|                  |                                   |                   |          |                                    |               |                |              |  |  |

| Legend:          |                                   |                   |          |                                    |               |                |              |  |  |

| R = Readable     | R = Readable bit W = Writable bit |                   | bit      | U = Unimplemented bit, read as '0' |               |                |              |  |  |

| u = Bit is unch  | nanged                            | x = Bit is unkr   | nown     | -n/n = Value a                     | at POR and BO | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                                   | '0' = Bit is clea | ared     |                                    |               |                |              |  |  |

|                  |                                   |                   |          |                                    |               |                |              |  |  |

| bit 7            | PWMxEN: P\                        | WM Module En      | able bit |                                    |               |                |              |  |  |

|                  |                                   | odule is enable   | ÷.       |                                    |               |                |              |  |  |

|                  | 0 = PWM mc                        | odule is disable  | d        |                                    |               |                |              |  |  |

| bit 6            | Unimplemen                        | ted: Read as '    | 0'       |                                    |               |                |              |  |  |

|                  |                                   |                   |          |                                    |               |                |              |  |  |

- bit 5 PWMxOUT: PWM Module Output Level when Bit is Read

- bit 4 **PWMxPOL:** PWMx Output Polarity Select bit

- 1 = PWM output is active-low

- 0 = PWM output is active-high

- bit 3-0 Unimplemented: Read as '0'

| Name     | Bit 7   | Bit 6   | Bit 5     | Bit 4                | Bit 3        | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------|---------|-----------|----------------------|--------------|-------------|---------|---------|---------------------|

| T2CON    | ON      |         | CKPS<2:0> | CKPS<2:0> OUTPS<3:0> |              |             |         |         | 404                 |

| T2TMR    |         |         | Holding   | Register for the     | 8-bit TMR2 R | egister     |         |         | 384*                |

| T2PR     |         |         |           | TMR2 Period          | d Register   |             |         |         | 384*                |

| RxyPPS   | —       | —       | —         |                      | F            | RxyPPS<4:0> |         |         | 265                 |

| CWG1ISM  | —       | _       | _         | — — IS<3:0>          |              |             |         |         | 492                 |

| CLCxSELy | —       | _       |           |                      | LCxDyS       | <5:0>       |         |         | 503                 |

| TRISA    | TRISA7  | TRISA6  | TRISA5    | TRISA4               | TRISA3       | TRISA2      | TRISA1  | TRISA0  | 222                 |

| TRISC    | TRISC7  | TRISC6  | TRISC5    | TRISC4               | TRISC3       | TRISC2      | TRISC1  | TRISC0  | 235                 |

| PWM3CON  | PWM3EN  | _       | PWM3OUT   | PWM3POL              | —            | —           | _       | —       |                     |

| PWM4CON  | PWM4EN  | _       | PWM4OUT   | PWM4POL              | —            | —           | _       | —       |                     |

| PWM3DCL  | PWM3DC1 | PWM3DC0 | _         | _                    | _            | _           | _       | _       |                     |

| PWM3DCH  | PWM3DC9 | PWM3DC8 | PWM3DC7   | PWM3DC6              | PWM3DC5      | PWM3DC4     | PWM3DC3 | PWM3DC2 |                     |

| PWM4DCL  | PWM4DC1 | PWM4DC0 | —         | —                    | —            | —           | —       | —       |                     |

| PWM4DCH  | PWM4DC9 | PWM4DC8 | PWM4DC7   | PWM4DC6              | PWM4DC5      | PWM4DC4     | PWM4DC3 | PWM4DC2 |                     |

## TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

\*Page provides register information.

| REGISTER 32-6: CLCxSEL3: GENERIC CLCx DATA 3 SELECT REGISTER |           |                  |         |                |                  |                  |              |  |  |  |  |

|--------------------------------------------------------------|-----------|------------------|---------|----------------|------------------|------------------|--------------|--|--|--|--|

| U-0                                                          | U-0       | R/W-x/u          | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |  |

|                                                              | _         |                  |         | LCxD4          | 4S<5:0>          |                  |              |  |  |  |  |

| bit 7                                                        |           |                  |         |                |                  |                  | bit 0        |  |  |  |  |

|                                                              |           |                  |         |                |                  |                  |              |  |  |  |  |

| Legend:                                                      |           |                  |         |                |                  |                  |              |  |  |  |  |

| R = Readable                                                 | bit       | W = Writable     | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |  |  |  |  |

| u = Bit is uncha                                             | anged     | x = Bit is unkr  | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is set                                             |           | '0' = Bit is cle | ared    |                |                  |                  |              |  |  |  |  |

|                                                              |           |                  |         |                |                  |                  |              |  |  |  |  |

| bit 7-6                                                      | Unimpleme | ented: Read as ' | 0'      |                |                  |                  |              |  |  |  |  |

bit 5-0 **LCxD4S<5:0>:** CLCx Data 4 Input Selection bits See Table 32-2.

| R/W-x/u                 | R/W-x/u      | R/W-x/u                                 | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |  |

|-------------------------|--------------|-----------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| LCxG1D4T                | LCxG1D4N     | LCxG1D3T                                | LCxG1D3N       | LCxG1D2T       | LCxG1D2N         | LCxG1D1T         | LCxG1D1N    |  |  |  |

| bit 7                   |              |                                         |                |                |                  |                  | bit (       |  |  |  |

|                         |              |                                         |                |                |                  |                  |             |  |  |  |

| Legend:<br>R = Readable | hit          | W = Writable                            | hit            | II – Unimplor  | nented bit, read | ac 'O'           |             |  |  |  |

|                         |              |                                         |                | •              |                  |                  | than Decete |  |  |  |

| u = Bit is uncha        | angeo        | x = Bit is unkr                         |                | -n/n = value a | at POR and BO    | R/value at all o | iner Resets |  |  |  |

| '1' = Bit is set        |              | '0' = Bit is clea                       | ared           |                |                  |                  |             |  |  |  |

| bit 7                   |              | Gate 0 Data 4 1                         | rue (non-inve  | rted) hit      |                  |                  |             |  |  |  |

|                         |              | (true) is gated i                       | · ·            |                |                  |                  |             |  |  |  |

|                         |              | (true) is not gat                       |                |                |                  |                  |             |  |  |  |

| bit 6                   |              | Gate 0 Data 4                           |                |                |                  |                  |             |  |  |  |

|                         |              | inverted) is ga                         | •              |                |                  |                  |             |  |  |  |

|                         |              | inverted) is no                         |                |                |                  |                  |             |  |  |  |

| bit 5                   | LCxG1D3T: @  | Gate 0 Data 3 1                         | rue (non-inve  | rted) bit      |                  |                  |             |  |  |  |

|                         |              | CLCIN2 (true) is gated into CLCx Gate 0 |                |                |                  |                  |             |  |  |  |

|                         | 0 = CLCIN2 ( | true) is not gat                        | ed into CLCx   | Gate 0         |                  |                  |             |  |  |  |

| bit 4                   | LCxG1D3N:    | Gate 0 Data 3 I                         | Negated (inver | rted) bit      |                  |                  |             |  |  |  |

|                         |              | (inverted) is gated into CLCx Gate 0    |                |                |                  |                  |             |  |  |  |

|                         |              | inverted) is no                         | •              |                |                  |                  |             |  |  |  |

| bit 3                   |              | Gate 0 Data 2 1                         |                | ,              |                  |                  |             |  |  |  |

|                         |              | true) is gated i                        |                |                |                  |                  |             |  |  |  |

|                         |              | true) is not gat                        |                |                |                  |                  |             |  |  |  |

| bit 2                   |              | Gate 0 Data 2                           | •              |                |                  |                  |             |  |  |  |

|                         |              | inverted) is ga<br>inverted) is no      |                |                |                  |                  |             |  |  |  |

| <b>b</b> :4 4           |              | . ,                                     | •              |                |                  |                  |             |  |  |  |

| bit 1                   |              | Bate 0 Data 1 1                         | •              | ,              |                  |                  |             |  |  |  |

|                         |              | (true) is gated i<br>(true) is not gat  |                |                |                  |                  |             |  |  |  |

| bit 0                   |              | Gate 0 Data 1                           |                |                |                  |                  |             |  |  |  |

|                         |              | inverted) is ga                         | •              | ,              |                  |                  |             |  |  |  |

|                         |              | inverted) is ga                         |                |                |                  |                  |             |  |  |  |

## REGISTER 32-7: CLCxGLS0: GATE 0 LOGIC SELECT REGISTER

## REGISTER 33-7: SSPxBUF: MSSPx BUFFER REGISTER

| R/W-x   | R/W-x | R/W-x | R/W-x  | R/W-x   | R/W-x | R/W-x | R/W-x |

|---------|-------|-------|--------|---------|-------|-------|-------|

|         |       |       | SSPxBl | JF<7:0> |       |       |       |

| bit 7   |       |       |        |         |       |       | bit 0 |

|         |       |       |        |         |       |       |       |

| Legend: |       |       |        |         |       |       |       |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SSPxBUF<7:0>: MSSP Buffer bits

#### TABLE 33-3: SUMMARY OF REGISTERS ASSOCIATED WITH MSSPx

| Name       | Bit 7       | Bit 6   | Bit 5 | Bit 4           | Bit 3           | Bit 2    | Bit 1 | Bit 0  | Register<br>on Page |  |  |

|------------|-------------|---------|-------|-----------------|-----------------|----------|-------|--------|---------------------|--|--|

| INTCON     | GIE         | PEIE    |       | —               | —               | —        | _     | INTEDG | 164                 |  |  |

| PIR1       | OSFIF       | CSWIF   | _     | —               | —               | —        | ADTIF | ADIF   | 175                 |  |  |

| PIE1       | OSFIE       | CSWIE   | _     | —               | —               | —        | ADTIE | ADIE   | 166                 |  |  |

| SSP1STAT   | SMP         | CKE     | D/Ā   | Р               | S               | R/W      | UA    | BF     | 557                 |  |  |

| SSP1CON1   | WCOL        | SSPOV   | SSPEN | CKP             |                 | SSPM     | <3:0> |        | 558                 |  |  |

| SSP1CON2   | GCEN        | ACKSTAT | ACKDT | ACKEN           | RCEN            | PEN      | RSEN  | SEN    | 559                 |  |  |

| SSP1CON3   | ACKTIM      | PCIE    | SCIE  | BOEN            | SDAHT           | SBCDE    | AHEN  | DHEN   | 560                 |  |  |

| SSP1MSK    | SSPMSK<7:0> |         |       |                 |                 |          |       |        |                     |  |  |

| SSP1ADD    | SSPADD<7:0> |         |       |                 |                 |          |       |        | 561                 |  |  |

| SSP1BUF    |             |         |       | SSPBU           | 562             |          |       |        |                     |  |  |

| SSP2STAT   | SMP         | CKE     | D/Ā   | Р               | S               | R/W      | UA    | BF     | 557                 |  |  |

| SSP2CON1   | WCOL        | SSPOV   | SSPEN | CKP             |                 | 558      |       |        |                     |  |  |

| SSP2CON2   | GCEN        | ACKSTAT | ACKDT | ACKEN           | RCEN            | PEN      | RSEN  | SEN    | 559                 |  |  |

| SSP2CON3   | ACKTIM      | PCIE    | SCIE  | BOEN            | SDAHT           | SBCDE    | AHEN  | DHEN   | 560                 |  |  |

| SSP2MSK    |             |         |       | SSPMS           | K<7:0>          |          |       |        | 561                 |  |  |

| SSP2ADD    |             |         |       | SSPAD           | D<7:0>          |          |       |        | 561                 |  |  |

| SSP2BUF    |             |         |       | SSPBU           | F<7:0>          |          |       |        | 562                 |  |  |

| SSP1CLKPPS |             | _       |       |                 | SSP1CLKPPS<4:0> |          |       |        |                     |  |  |

| SSP1DATPPS | —           | —       |       |                 | 264             |          |       |        |                     |  |  |

| SSP1SSPPS  | _           | —       |       |                 | 264             |          |       |        |                     |  |  |

| SSP2CLKPPS |             | —       | _     | SSP2CLKPPS<4:0> |                 |          |       |        |                     |  |  |

| SSP2DATPPS | —           | —       |       | SSP2DATPPS<4:0> |                 |          |       |        |                     |  |  |

| SSP2SSPPS  | —           | —       | _     |                 |                 | 2SSPPS<4 |       |        | 264                 |  |  |

| RxyPPS     | —           | _       | _     | RxyPPS<4:0>     |                 |          |       |        |                     |  |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx module.

© 2017 Microchip Technology Inc.

| Address    | Name                                                                                                                                           | Bit 7           | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Register<br>on page |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------|---------|--------|-------|-------|-------|---------------------|--|

| 1D20h      | LCDDATA8                                                                                                                                       | S23C1           | S22C1 | _     | S20C1   | S19C1  | S18C1 | —     | —     | 624                 |  |

| 1D21h      | LCDDATA9                                                                                                                                       | S31C1           | S30C1 | S29C1 | S28C1   | S27C1  | S26C1 | S25C1 | S24C1 | 624                 |  |

| 1D22h      | LCDDATA10                                                                                                                                      | —               | —     | —     | —       | —      | S34C1 | S33C1 | S32C1 | 624                 |  |

| 1D23h      | LCDDATA11                                                                                                                                      | S47C1           | S46C1 | S45C1 | S44C1   | S43C1  | S42C1 | S41C1 | S40C1 | 624                 |  |

| 1D24h      | LCDDATA12                                                                                                                                      | S07C2           | S06C2 | —     | S04C2   | S3C2   | S2C2  | S01C2 | S00C2 | 624                 |  |

| 1D25h      | LCDDATA13                                                                                                                                      | S15C2           | S14C2 | S13C2 | —       | S11C2  | S10C2 | S09C2 | S08C2 | 624                 |  |

| 1D26h      | LCDDATA14                                                                                                                                      | S23C2           | S22C2 | —     | S20C2   | S19C2  | S18C2 | —     | —     | 624                 |  |

| 1D27h      | LCDDATA15                                                                                                                                      | S31C2           | S30C2 | S29C2 | S28C2   | S27C2  | S26C2 | S25C2 | S24C2 | 624                 |  |

| 1D28h      | LCDDATA16                                                                                                                                      | _               | _     | _     | —       | —      | S34C2 | S33C2 | S32C2 | 624                 |  |

| 1D29h      | LCDDATA17                                                                                                                                      | S47C2           | S46C2 | S45C2 | S44C2   | S43C2  | S42C2 | S41C2 | S40C2 | 624                 |  |

| 1D2Ah      | LCDDATA18                                                                                                                                      | S15C3           | S14C3 | S13C3 | —       | SE11C3 | S10C3 | S09C3 | S08C3 | 624                 |  |

| 1D2Bh      | LCDDATA19                                                                                                                                      | S23C3           | S22C3 | —     | S20C3   | S19C3  | S18C3 | —     | _     | 624                 |  |

| 1D2Ch      | LCDDATA20                                                                                                                                      | S31C3           | S30C3 | S29C3 | S28C3   | S27C3  | S26C3 | S25C3 | S24C3 | 624                 |  |

| 1D2Dh      | LCDDATA21                                                                                                                                      | —               | —     | —     | —       | —      | S34C3 | S33C3 | S32C3 | 624                 |  |

| 1D2Eh      | LCDDATA22                                                                                                                                      | S47C3           | S46C3 | S45C3 | S44C3   | S43C3  | S42C3 | S41C3 | S40C3 | 624                 |  |

| 1D2Fh      | LCDDATA23                                                                                                                                      | S07C4           | S06C4 | _     | S04C4   | S03C4  | S02C4 | S01C4 | S00C4 | 624                 |  |

| 1D30h      | LCDDATA24                                                                                                                                      | S15C4           | S14C4 | S13C4 | —       | S11C4  | S10C4 | S09C4 | S08C4 | 624                 |  |

| 1D31h      | LCDDATA25                                                                                                                                      | S23C4           | S22C4 | _     | S20C4   | S19C4  | S18C4 | _     | _     | 624                 |  |

| 1D32h      | LCDDATA26                                                                                                                                      | S31C4           | S30C4 | S29C4 | S28C4   | S27C4  | S26C4 | S25C4 | S24C4 | 624                 |  |

| 1D33h      | LCDDATA27                                                                                                                                      | —               | —     | —     | —       | —      | S34C4 | S33C4 | S32C4 | 624                 |  |

| 1D34h      | LCDDATA28                                                                                                                                      | S47C4           | S46C4 | S45C4 | S44C4   | S43C4  | S42C4 | S41C4 | S40C4 | 624                 |  |

| 1D35h      | LCDDATA29                                                                                                                                      | S07C5           | S06C5 | _     | S04C5   | S03C5  | S02C5 | S01C5 | S00C5 | 624                 |  |

| 1D36h      | LCDDATA30                                                                                                                                      | S15C5           | S14C5 | S13C5 | —       | S11C5  | S10C5 | S09C5 | S08C5 | 624                 |  |

| 1D37h      | LCDDATA31                                                                                                                                      | S23C5           | S22C5 | —     | S20C5   | S19C5  | S18C5 | —     | —     | 624                 |  |

| 1D38h      | LCDDATA32                                                                                                                                      | S31C5           | S30C5 | S29C5 | S28C5   | S27C5  | S26C5 | S25C5 | S24C5 | 624                 |  |

| 1D39h      | LCDDATA33                                                                                                                                      | —               | —     | _     | —       | _      | S34C5 | S33C5 | S32C5 | 624                 |  |

| 1D3Ah      | LCDDATA34                                                                                                                                      | S47C5           | S46C5 | S45C5 | S44C5   | S43C5  | S42C5 | S41C5 | S40C5 | 624                 |  |

| 1D3Bh      | LCDDATA35                                                                                                                                      | S07C6           | S06C6 | _     | S04C6   | S03C6  | S02C6 | S01C6 | S00C6 | 624                 |  |

| 1D3Ch      | LCDDATA36                                                                                                                                      | S15C6           | S14C6 | S13C6 | —       | S11C6  | S10C6 | S09C6 | S08C6 | 624                 |  |

| 1D3Dh      | LCDDATA37                                                                                                                                      | S23C6           | S22C6 | _     | S20C6   | S19C6  | S18C6 | _     | —     | 624                 |  |

| 1D3Eh      | LCDDATA38                                                                                                                                      | S31C6           | S30C6 | S29C6 | S28C6   | S27C6  | S26C6 | S25C6 | S24C6 | 624                 |  |

| 1D3Fh      | LCDDATA39                                                                                                                                      | —               | —     | _     | —       | _      | S34C6 | S33C6 | S32C6 | 624                 |  |

| 1D40h      | LCDDATA40                                                                                                                                      | S47C6           | S46C6 | S45C6 | S44C6   | S43C6  | S42C6 | S41C6 | S40C6 | 624                 |  |

| 1D41h      | LCDDATA41                                                                                                                                      | S07C7           | S06C7 | _     | S04C7   | S03C7  | S02C7 | S01C7 | S00C7 | 624                 |  |

| 1D42h      | LCDDATA42                                                                                                                                      | S15C7           | S14C7 | S13C7 | —       | S11C7  | S10C7 | S09C7 | S08C7 | 624                 |  |

| 1D43h      | LCDDATA43                                                                                                                                      | S23C7           | S22C7 | —     | S20C7   | S19C7  | S18C7 | —     | —     | 624                 |  |

| 1D44h      | LCDDATA44                                                                                                                                      | S31C7           | S30C7 | S29C7 | S28C7   | S27C7  | S26C7 | S25C7 | S24C7 | 624                 |  |

| 1D45h      | LCDDATA45                                                                                                                                      | _               | _     | _     | _       | —      | S34C7 | S33C7 | S32C7 | 624                 |  |

| 1D46h      | LCDDATA46                                                                                                                                      | S47C7           | S46C7 | S45C7 | S44C7   | S43C7  | S42C7 | S41C7 | S40C7 | 624                 |  |

| 1D47h      | LCDDATA47                                                                                                                                      | S07C0           | S06C0 | _     | S04COM0 | S03C0  | S02C0 | S01C0 | S00C0 | 624                 |  |

| 1D48h<br>— | _                                                                                                                                              | - Unimplemented |       |       |         |        |       |       |       |                     |  |

| 1D6Fh      | x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0 |                 |       |       |         |        |       |       |       |                     |  |

# TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

| Address | Name   | Bit 7         | Bit 6         | Bit 5 | Bit 4   | Bit 3   | Bit 2    | Bit 1    | Bit 0    | Register<br>on page |  |  |

|---------|--------|---------------|---------------|-------|---------|---------|----------|----------|----------|---------------------|--|--|

| 1EEBh   | —      | Unimplemented |               |       |         |         |          |          |          |                     |  |  |

| 1EECh   | _      | Unimplemented |               |       |         |         |          |          |          |                     |  |  |

| 1EEDh   | _      | Unimplemented |               |       |         |         |          |          |          |                     |  |  |

| 1EEEh   | _      |               | Unimplemented |       |         |         |          |          |          |                     |  |  |

| 1EEFh   | _      |               | Unimplemented |       |         |         |          |          |          |                     |  |  |

| 1F0Ch   | _      |               | Unimplemented |       |         |         |          |          |          |                     |  |  |

| 1F0Dh   | _      |               | Unimplemented |       |         |         |          |          |          |                     |  |  |

| 1F0Eh   |        |               | Unimplemented |       |         |         |          |          |          |                     |  |  |

| 1F0Fh   | _      |               |               |       |         | emented |          |          |          |                     |  |  |

| 1F10h   | RA0PPS |               |               |       | RA0PPS4 | RA0PPS3 | RA0PPS2  | RA0PPS1  | RA0PPS0  | 265                 |  |  |

| 1F11h   | RA1PPS |               |               |       | RA1PPS4 | RA1PPS3 | RA1PPS2  | RA1PPS1  | RA1PPS0  | 265                 |  |  |

| 1F12h   | RA2PPS | _             |               |       | RA2PPS4 | RA2PPS3 | RA2PPS2  | RA2PPS1  | RA2PPS0  | 265                 |  |  |

| 1F13h   | RA3PPS | —             | _             | _     | RA3PPS4 | RA3PPS3 | RA3PPS2  | RA3PPS1  | RA3PPS0  | 265                 |  |  |

| 1F14h   | RA4PPS | —             | —             | —     | RA4PPS4 | RA4PPS3 | RA4PPS2  | RA4PPS1  | RA4PPS0  | 265                 |  |  |

| 1F15h   | RA5PPS | _             |               | _     | RA5PPS4 | RA5PPS3 | RA5PPS2  | RA5PPS1  | RA5PPS0  | 265                 |  |  |

| 1F16h   | RA6PPS | _             | —             | _     | RA6PPS4 | RA6PPS3 | RA6PPS2  | RA6PPS1  | RA6PPS0  | 265                 |  |  |

| 1F17h   | RA7PPS | _             |               | _     | RA7PPS4 | RA7PPS3 | RA7PPS2  | RA7PPS1  | RA7PPS0  | 265                 |  |  |

| 1F18h   | RB0PPS | —             | —             | _     | RB0PPS4 | RB0PPS3 | RB0PPS2  | RB0PPS1  | RB0PPS0  | 265                 |  |  |

| 1F19h   | RB1PPS | _             | _             | —     | RB1PPS4 | RB1PPS3 | RB1PPS2  | RB1PPS1  | RB1PPS0  | 265                 |  |  |

| 1F1Ah   | RB2PPS | -             | —             | -     | RB2PPS4 | RB2PPS3 | RB2PPS2  | RB2PPS1  | RB2PPS0  | 265                 |  |  |

| 1F1Bh   | RB3PPS | _             | —             | _     | RB3PPS4 | RB3PPS3 | RB3PPS2  | RB3PPS1  | RB3PPS0  | 265                 |  |  |

| 1F1Ch   | RB4PPS | —             | _             | —     | RB4PPS4 | RB4PPS3 | RB4PPS2  | RB4PPS1  | RB4PPS0  | 265                 |  |  |

| 1F1Dh   | RB5PPS | _             | _             | _     | RB5PPS4 | RB5PPS3 | RB5PPS2  | RB5PPS1  | RB5PPS0  | 265                 |  |  |

| 1F1Eh   | RB6PPS | _             | _             | _     | RB6PPS4 | RB6PPS3 | RB6PPS2  | RB6PPS1  | RB6PPS0  | 265                 |  |  |

| 1F1Fh   | RB7PPS | _             | _             | _     | RB7PPS4 | RB7PPS3 | RB7PPS2  | RB7PPS1  | RB7PPS0  | 265                 |  |  |

| 1F20h   | RC0PPS | _             |               | _     | RC0PPS4 | RC0PPS3 | RC0PPS2  | RC0PPS1  | RC0PPS0  | 265                 |  |  |

| 1F21h   | RC1PPS | _             | _             | _     | RC1PPS4 | RC1PPS3 | RC1PPS2  | RC1PPS1  | RC1PPS0  | 265                 |  |  |

| 1F22h   | RC2PPS | _             |               | _     | RC2PPS4 | RC2PPS3 | RC2PPS2  | RC2PPS1  | RC2PPS0  | 265                 |  |  |

| 1F23h   | RC3PPS | _             |               |       | RC3PPS4 | RC3PPS3 | RC3PPS2  | RC3PPS1  | RC3PPS0  | 265                 |  |  |

| 1F24h   | RC4PPS | _             |               | _     | RC4PPS4 | RC4PPS3 | RC4PPS2  | RC4PPS1  | RC4PPS0  | 265                 |  |  |

| 1F25h   | —      |               |               |       |         | emented | 11041102 | 11041101 | 11041100 | 200                 |  |  |

| 1F26h   | RC6PPS | _             | _             | _     | RC6PPS4 | RC6PPS3 | RC6PPS2  | RC6PPS1  | RC6PPS0  | 265                 |  |  |

| 1F27h   | RC7PPS | _             |               |       | RC7PPS4 | RC7PPS3 | RC7PPS2  | RC7PPS1  | RC7PPS0  | 265                 |  |  |

|         | RD0PPS | _             | _             | _     | RD0PPS4 | RD0PPS3 | RD0PPS2  | RD0PPS1  |          | 265                 |  |  |

| 1F28h   |        | _             | _             | _     |         |         |          |          | RD0PPS0  | 265                 |  |  |

| 1F29h   | RD1PPS |               |               |       | RD1PPS4 | RD1PPS3 | RD1PPS2  | RD1PPS1  | RD1PPS0  |                     |  |  |

| 1F2Ah   | RD2PPS |               |               |       | RD2PPS4 | RD2PPS3 | RD2PPS2  | RD2PPS1  | RD2PPS0  | 265                 |  |  |

| 1F2Bh   | RD3PPS | _             | _             |       | RD3PPS4 | RD3PPS3 | RD3PPS2  | RD3PPS1  | RD3PPS0  | 265                 |  |  |

| 1F2Ch   | RD4PPS |               |               |       | RD4PPS4 | RD4PPS3 | RD4PPS2  | RD4PPS1  | RD4PPS0  | 265                 |  |  |

| 1F2Dh   | RD5PPS |               |               |       | RD5PPS4 | RD5PPS3 | RD5PPS2  | RD5PPS1  | RD5PPS0  | 265                 |  |  |

| 1F2Eh   | RD6PPS |               | _             | _     | RD6PPS4 | RD6PPS3 | RD6PPS2  | RD6PPS1  | RD6PPS0  | 265                 |  |  |

| 1F2Fh   | RD7PPS |               |               |       | RD7PPS4 | RD7PPS3 | RD7PPS2  | RD7PPS1  | RD7PPS0  | 265                 |  |  |

| 1F30h   | RE0PPS | _             | _             | _     | RE0PPS4 | RE0PPS3 | RE0PPS2  | RE0PPS1  | RE0PPS0  | 265                 |  |  |

| 1F31h   | RE1PPS |               |               | _     | RE1PPS4 | RE1PPS3 | RE1PPS2  | RE1PPS1  | RE1PPS0  | 265                 |  |  |

| 1F32h   | RE2PPS | —             | _             | _     | RE2PPS4 | RE2PPS3 | RE2PPS2  | RE2PPS1  | RE2PPS0  | 265                 |  |  |

## TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

$Legend: \quad x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.$

**Note** 1: Unimplemented data memory locations, read as '0'.

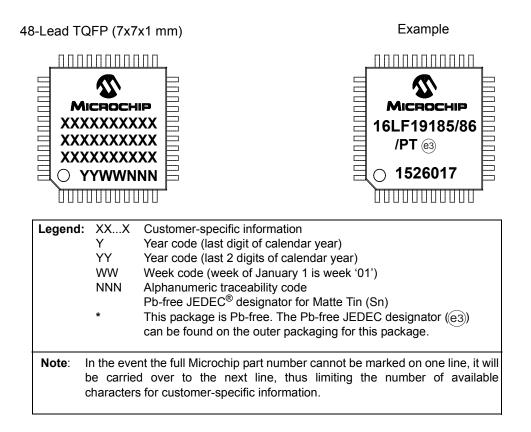

# 42.1 Package Marking Information (Continued)

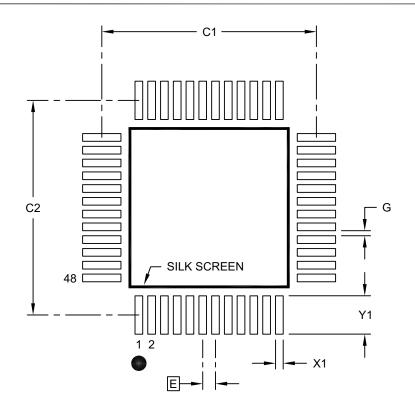

# 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units      | MILLIMETERS |      |      |  |

|--------------------------|------------|-------------|------|------|--|

| Dimension                | Limits     | MIN         | NOM  | MAX  |  |

| Contact Pitch            | E 0.50 BSC |             |      |      |  |

| Contact Pad Spacing      | C1         |             | 8.40 |      |  |

| Contact Pad Spacing      | C2         |             | 8.40 |      |  |

| Contact Pad Width (X48)  | X1         |             |      | 0.30 |  |

| Contact Pad Length (X48) | Y1         |             |      | 1.50 |  |

| Distance Between Pads    | G          | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2300-PT Rev A