Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 43                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19185t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F19155/56/75/76/85/86

| TABLE              | - 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2           | 8-PIN AL         | LOCA      | ATION          | ABL               | .E (PIC16 | (L)F19155                                      | /56) (C             | ONTIN        | UED)                             |                                              |                                          |                       |      |                        |                     |              |         |                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|-----------|----------------|-------------------|-----------|------------------------------------------------|---------------------|--------------|----------------------------------|----------------------------------------------|------------------------------------------|-----------------------|------|------------------------|---------------------|--------------|---------|--------------------|

| (2)O/I             | 28-Pin SPDIP/SSOP/SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28-Pin UQFN | ADC              | Reference | Comparator     | Zero-Cross Detect | DAC       | Timers/SMT                                     | CCP                 | WMd          | CWG                              | dssm                                         | EUSART                                   | CLC                   | RTCC | ГСD                    | Interrupt-on-Change | High Current | dn-IInd | Basic              |

| RB6                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24          | ANB6             | I         | _              |                   | _         | -                                              |                     | _            |                                  | —                                            | TX2 <sup>(1)</sup><br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> | _    | SEG14                  | IOCB6               | _            | Y       | ICDCLK/<br>ICSPCLK |

| RB7                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25          | ANB7             | I         | _              |                   | DAC1OUT2  |                                                |                     | _            |                                  | _                                            | RX2 <sup>(1)</sup><br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | _    | SEG15                  | IOCB7               | —            | Y       | ICDDAT/<br>ICSPDAT |

| RC0                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8           | _                |           | _              |                   | _         | T1CKI <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> |                     | _            | _                                | —                                            |                                          | —                     | _    |                        | IOCC0               | —            | Y       | SOSCO              |

| RC1                | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9           | _                | _         | _              | _                 | _         | SMTSIG1 <sup>(1)</sup><br>T4IN <sup>(1)</sup>  | CCP2 <sup>(1)</sup> | _            | _                                | —                                            | _                                        | _                     | _    | -                      | IOCC1               | _            | Y       | SOSCI              |

| RC2                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10          | ANC2             | -         | _              | _                 | -         | -                                              | CCP1 <sup>(1)</sup> | _            | _                                | —                                            | -                                        | -                     |      | COM2<br>SEG18          | IOCC2               | _            | Y       | _                  |

| RC3                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11          | ANC3             | -         | _              | _                 | -         | T2IN <sup>(1)</sup>                            | -                   | _            | _                                | SCK <sup>(1)</sup><br>SCL <sup>(1,3,4)</sup> |                                          | -                     | -    | SEG19                  | IOCC3               | _            | Y       | _                  |

| RC4                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12          | ANC4             | _         | _              | _                 | _         | —                                              | _                   | _            | _                                | SDI <sup>(1)</sup><br>SDA <sup>(1,3,4)</sup> | _                                        | -                     | _    | SEG20                  | IOCC4               | _            | Y       | _                  |

| RC6                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14          | ANC6             | Ι         | _              |                   | _         | _                                              | _                   |              | _                                | _                                            | TX1 <sup>(1)</sup><br>CK1 <sup>(1)</sup> | _                     | Ι    | COM5<br>SEG22<br>VLCD2 | IOCC6               | _            | Y       | _                  |

| RC7                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15          | ANC7             | Ι         | _              | _                 | -         | _                                              | _                   | -            | _                                | —                                            | RX1 <sup>(1)</sup><br>DT1 <sup>(1)</sup> | —                     | Ι    | SEG23<br>COM4<br>VLCD1 | IOCC7               | _            | Y       | _                  |

| RE3                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26          |                  | —         | —              |                   | _         |                                                | -                   | —            |                                  | _                                            | -                                        | —                     | _    | -                      | IOCE3               | _            | Υ       | MCLR               |

| VLCD3              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13          | _                | _         | —              |                   | _         | _                                              | _                   | —            | _                                | _                                            | _                                        | —                     | _    | VLCD3                  | —                   | _            | —       | _                  |

| Vdd                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17          | _                | —         | —              | _                 | _         | _                                              | _                   | —            | _                                | _                                            | —                                        | —                     | _    | _                      | —                   | _            | —       | Vdd                |

| Vss                | 8<br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5<br>16     | _                | _         | _              | —                 | _         | _                                              | _                   | _            | _                                | _                                            | _                                        | —                     | _    | _                      | —                   | —            | —       | Vss                |

| OUT <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _           | ADGRDA<br>ADGRDB | _         | C1OUT<br>C2OUT |                   | _         | TMR0                                           | CCP1<br>CCP2        | PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | SDO<br>SCK<br>SCL<br>SDA                     | TX1<br>DT1<br>CK1<br>TX2<br>DT2<br>CK2   | CLC1OUT               | RTCC | _                      | —                   | _            | _       | _                  |

| :                  | <ul> <li>Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.</li> <li>2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.</li> <li>3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.</li> </ul> |             |                  |           |                |                   |           |                                                |                     |              |                                  |                                              |                                          |                       |      |                        |                     |              |         |                    |

#### TABLE 3 28-PIN ALLOCATION TABLE (PIC16(L)E19155/56) (CONTINUED)

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or 4: SMBUS input buffer thresholds.

These are alternative I<sup>2</sup>C logic levels pins. 5:

In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins. 6:

© 2017 Microchip Technology Inc.

Preliminary

# 1.0 DEVICE OVERVIEW

The PIC16(L)F19155/56/75/76/85/86 are described within this data sheet. The PIC16(L)F19155/56/75/76/85/86 devices are available in 48-pin TQFP and UQFN, 44-pin TQFP and UQFN, 40-pin PDIP and 28-pin SPDIP, SOIC, SSOP and UQFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F19155/56/75/76/85/86 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUMMARY                                                                       |                        |                               |

|-------------------------------------------------------------------------------|------------------------|-------------------------------|

| Peripheral                                                                    |                        | PIC16(L)F19155/56/75/76/85/86 |

| Analog-to-Digital Converter with Computation                                  | on (ADC <sup>2</sup> ) | ٠                             |

| Digital-to-Analog Converter (DAC1)                                            |                        | ٠                             |

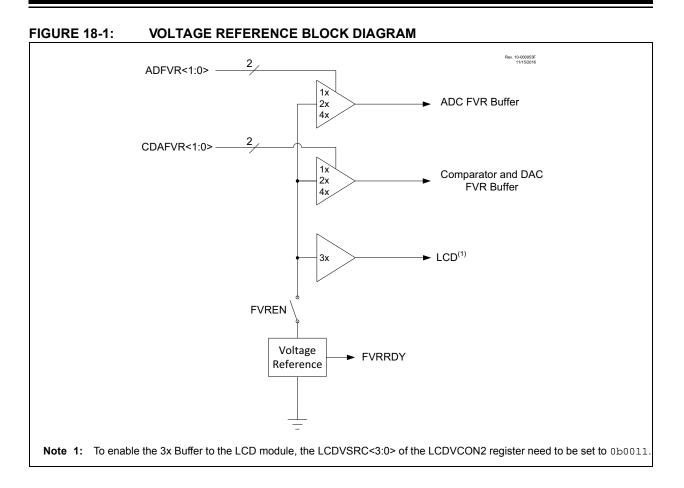

| Fixed Voltage Reference (FVR)                                                 |                        | •                             |

| Enhanced Universal Synchronous/Asynchron<br>Transmitter (EUSART1 and EUSART2) | nous Receiver/         | ٠                             |

| Temperature Indicator Module (TIM)                                            |                        | ٠                             |

| Zero-Cross Detect (ZCD1)                                                      |                        | ٠                             |

| Real-Time Calendar and Clock (RTCC)                                           |                        | ٠                             |

| Liquid Crystal Display (LCD)                                                  |                        | ٠                             |

| Capture/Compare/PWM Modules (CCP)                                             |                        |                               |

|                                                                               | CCP1                   | ٠                             |

| Composition Markela (Oci)                                                     | CCP2                   | ٠                             |

| Comparator Module (Cx)                                                        | C1                     | •                             |

|                                                                               | C1                     | •                             |

| Configurable Logic Cell (CLC)                                                 | 01                     |                               |

|                                                                               | CLC1                   | •                             |

|                                                                               | CLC2                   | •                             |

|                                                                               | CLC3                   | •                             |

|                                                                               | CLC4                   | ٠                             |

| Complementary Waveform Generator (CWG)                                        |                        |                               |

|                                                                               | CWG1                   | •                             |

| Master Synchronous Serial Ports (MSSP)                                        |                        |                               |

|                                                                               | MSSP1                  | ٠                             |

| Pulse-Width Modulator (PWM)                                                   |                        | 1                             |

|                                                                               | PWM3                   | ٠                             |

|                                                                               | PWM4                   | ٠                             |

| Signal Measure Timer (SMT)                                                    |                        |                               |

|                                                                               | SMT1                   | ٠                             |

| Timers                                                                        |                        |                               |

|                                                                               | Timer0                 | ٠                             |

|                                                                               | Timer1                 | ٠                             |

|                                                                               | Timer2                 | ٠                             |

|                                                                               | Timer4                 | ٠                             |

| R/W/HC-0/0                                                                                                                                                  | R/W-0/0      | U-0                                 | R-0/0           | R-0/0           | U-0                                   | U-0               | U-0          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------|-----------------|-----------------|---------------------------------------|-------------------|--------------|

| CSWHOLD                                                                                                                                                     | SOSCPWR      |                                     | ORDY            | NOSCR           | —                                     | _                 |              |

| bit 7                                                                                                                                                       |              |                                     |                 |                 |                                       |                   | bit 0        |

| Legend:                                                                                                                                                     |              |                                     |                 |                 |                                       |                   |              |

| R = Readable                                                                                                                                                | bit          | W = Writable                        | bit             | U = Unimpler    | mented bit, read                      | l as '0'          |              |

| u = Bit is unch                                                                                                                                             | anged        | x = Bit is unkr                     | iown            |                 | at POR and BO                         |                   | other Resets |

| '1' = Bit is set                                                                                                                                            | C            | '0' = Bit is clea                   | ared            |                 |                                       |                   |              |

|                                                                                                                                                             |              |                                     |                 |                 |                                       |                   |              |

| bit 7                                                                                                                                                       | CSWHOLD:     | Clock Switch H                      | old bit         |                 |                                       |                   |              |

|                                                                                                                                                             | 1 = Clock sv | witch will hold (                   | with interrupt) | when the oscil  | lator selected b                      | y NOSC is read    | dy           |

|                                                                                                                                                             |              | witch may proce<br>at the time that |                 |                 | ted by NOSC is<br>vitch will occur    | ready; if this bi | t            |

| bit 6                                                                                                                                                       | SOSCPWR:     | Secondary Osc                       | illator Power N | /lode Select bi | t                                     |                   |              |

|                                                                                                                                                             |              | ary oscillator op                   | • •             | •               |                                       |                   |              |

|                                                                                                                                                             | 0 = Seconda  | ary oscillator op                   | perating in Low | -power mode     |                                       |                   |              |

| bit 5                                                                                                                                                       | Unimplemen   | ted: Read as '                      | 0'.             |                 |                                       |                   |              |

| bit 4                                                                                                                                                       |              | ator Ready bit                      | • • •           |                 |                                       |                   |              |

|                                                                                                                                                             |              |                                     |                 | system clock    | is the clock spe                      | cified by NOSC    | 2            |

|                                                                                                                                                             |              | switch is in pro                    | •               |                 |                                       |                   |              |

| bit 3 <b>NOSCR:</b> New Oscillator is Ready bit (read-only)<br>1 = A clock switch is in progress and the oscillator selected by NOSC indicates a "ready" co |              |                                     |                 |                 | 1 7                                   |                   |              |

|                                                                                                                                                             |              |                                     | •               |                 | cted by NOSC ii<br>cted oscillator is |                   | •            |

| bit 2-0                                                                                                                                                     |              | ted: Read as '                      |                 |                 |                                       | shot yet ready    |              |

|                                                                                                                                                             | ommplemen    | ieu. Neau do                        | 0               |                 |                                       |                   |              |

# **REGISTER 9-3:** OSCCON3: OSCILLATOR CONTROL REGISTER 3

# 11.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes: DOZE mode, IDLE mode and SLEEP mode.

# 11.1 DOZE Mode

DOZE mode saves power by reducing CPU execution and program memory (PFM) access, without affecting peripheral operation.

## 11.1.1 DOZE OPERATION

When the Doze Enable bit is set (DOZEN = 1), the CPU executes one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. FOSC and FOSC/4 clock sources are unaffected in Doze mode and peripherals can continue using these sources.

#### 11.1.2 SYSTEM BEHAVIOR FOR INTERRUPTS DURING DOZE

If an interrupt occurs during Doze, it can be configured using the Recover-On-Interrupt bit (ROI) and the Doze-On-Exit bit (DOE). Refer to Table 11-1 for details about system behavior in all cases for a transition from <u>Main  $\rightarrow$  ISR  $\rightarrow$  Main.</u>

| DOZEN |     | Code flow         |                                                                              |                                                    |                                                            |  |  |  |  |

|-------|-----|-------------------|------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------|--|--|--|--|

| DOZEN | ROI | Main              | ISR (1)                                                                      | Return to Main                                     |                                                            |  |  |  |  |

| 0     | 0   | Normal operation  | Normal operation and DOE<br>= DOZEN (in hardware)<br>DOZEN = 0 (unchanged)   |                                                    |                                                            |  |  |  |  |

| 0     | 1   | Normal operation  | Normal operation and DOE<br>= DOZEN (in hardware)<br>DOZEN = 0 (in hardware) | If DOE = 1 when<br>return from interrupt;          | If DOE = 0 when return from                                |  |  |  |  |

| 1     | 0   | Doze<br>operation | Doze operation and DOE =<br>DOZEN (in hardware)<br>DOZEN = 1 (unchanged)     | Doze operation and<br>DOZEN = 1 (in hard-<br>ware) | interrupt; Normal operation and<br>DOZEN = 0 (in hardware) |  |  |  |  |

| 1     | 1   | Doze<br>operation | Normal operation and DOE<br>= DOZEN (in hardware)<br>DOZEN = 0 (in hardware) |                                                    |                                                            |  |  |  |  |

# TABLE 11-1: SYSTEM BEHAVIOR FOR INTERRUPT DURING DOZE

Note 1: User software can change the DOE bit in ISR.

For example, if ROI = 1 and DOZE<2:0> = 001, the instruction cycle ratio is 1:4. The CPU and memory operate for one instruction cycle and stay idle for the next three instruction cycles. The Doze operation is illustrated in Figure 11-1.

# REGISTER 14-20: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|-----|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | —   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

# Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 LATC<7:6>: PORTC Output Latch Value b | its |

|-----------------------------------------------|-----|

|-----------------------------------------------|-----|

bit 4-0 LATC<4:0>: PORTC Output Latch Value bits

#### REGISTER 14-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | —   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | WPUC<7:6>: Weak Pull-up Register bits <sup>(1)</sup><br>1 = Pull-up enabled<br>0 = Pull-up disabled |

|---------|-----------------------------------------------------------------------------------------------------|

| bit 5   | Unimplemented: Read as '0'.                                                                         |

| bit 4-0 | WPUC<4:0>: Weak Pull-up Register bits <sup>(1)</sup><br>1 = Pull-up enabled<br>0 = Pull-up disabled |

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

# PIC16(L)F19155/56/75/76/85/86

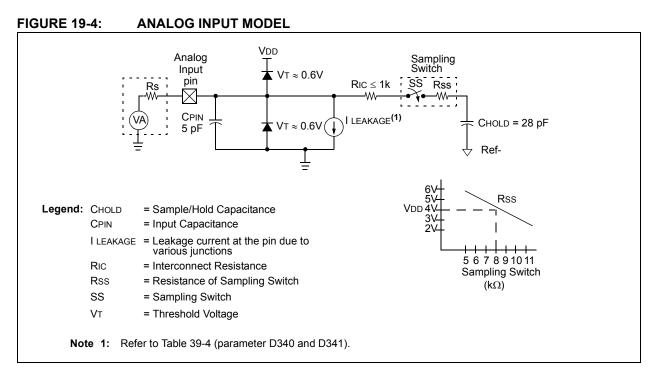

# 19.0 ANALOG-TO-DIGITAL CONVERTER WITH COMPUTATION (ADC<sup>2</sup>) MODULE

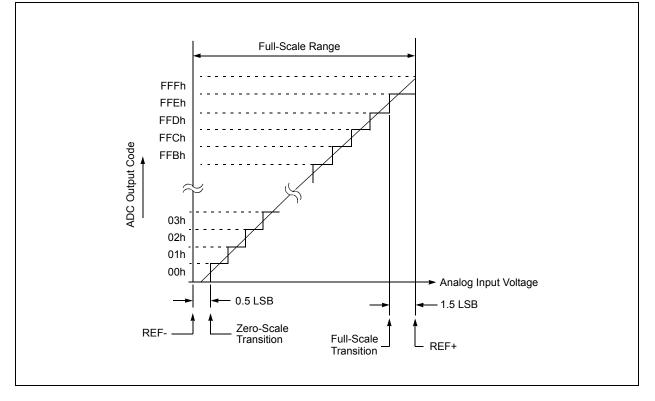

The Analog-to-Digital Converter with Computation (ADC<sup>2</sup>) allows conversion of an analog input signal to a 12-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 12-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair).

Additionally, the following features are provided within the ADC module:

- 13-bit Acquisition Timer

- Hardware Capacitive Voltage Divider (CVD)

Support:

- 13-bit Precharge Timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- Automatic Repeat and Sequencing:

- Automated double sample conversion for CVD

- Two sets of result registers (Result and Previous result)

- Auto-conversion trigger

- Internal retrigger

- Computation Features:

- Averaging and Low-Pass Filter functions

- Reference Comparison

- 2-level Threshold Comparison

- Selectable Interrupts

Figure 19-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion and upon threshold comparison. These interrupts can be used to wake-up the device from Sleep.

# PIC16(L)F19155/56/75/76/85/86

© 2017 Microchip Technology Inc.

DS40001923A-page 295

#### **REGISTER 19-9: ADPREL: ADC PRECHARGE TIME CONTROL REGISTER (LOW BYTE)**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PRE     | <7:0>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **PRE<7:0>**: Precharge Time Select bits See Table 19-4.

#### REGISTER 19-10: ADPREH: ADC PRECHARGE TIME CONTROL REGISTER (HIGH BYTE)

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

|       | —   | —   |         |         | PRE<12:8> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **PRE<12:8>:** Precharge Time Select bits<sup>(1)</sup> See Table 19-4.

**Note:** If PRE is not equal to '0', then ADACQ = b' 0000000 means Acquisition time is 256 clocks of the selected ADC clock.

# TABLE 19-4: PRECHARGE TIME

| ADPRE            | Precharge time                            |

|------------------|-------------------------------------------|

| 1 1111 1111 1111 | 8191 clocks of the selected ADC clock     |

| 1 1111 1111 1110 | 8190 clocks of the selected ADC clock     |

| 1 1111 1111 1101 | 8189 clocks of the selected ADC clock     |

|                  |                                           |

| 0 0000 0000 0010 | 2 clocks of the selected ADC clock        |

| 0 0000 0000 0001 | 1 clock of the selected ADC clock         |

| 0 0000 0000 0000 | Not included in the data conversion cycle |

© 2017 Microchip Technology Inc.

#### **REGISTER 19-18:** ADRESH: ADC RESULT REGISTER HIGH, FM = 0

|                  |         |                     |         | ,              |                  |                  |              |

|------------------|---------|---------------------|---------|----------------|------------------|------------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|                  |         |                     | ADRE    | S<11:4>        |                  |                  |              |

| bit 7            |         |                     |         |                |                  |                  | bit 0        |

|                  |         |                     |         |                |                  |                  |              |

| Legend:          |         |                     |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable bit    |         | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unknow   | vn      | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |                  |                  |              |

bit 7-0 **ADRES<11:4>**: ADC Result Register bits Upper eight bits of 12-bit conversion result.

#### **REGISTER 19-19: ADRESL: ADC RESULT REGISTER LOW, FM = 0**

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|------------|---------|---------|---------|-----|-----|-----|-------|

| ADRES<3:0> |         |         |         | —   | —   | —   | —     |

| bit 7      |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ADRES<3:0>: ADC Result Register bits. Lower four bits of 12-bit conversion result.

bit 3-0 Unimplemented: Read as '0'

# 23.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The OUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The OUT bit is affected by the polarity even if the module is disabled.

# 23.3 ZCD Logic Polarity

The POL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the POL bit is set, a OUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The POL bit affects the ZCD interrupts. See **Section 23.4 "ZCD Interrupts**".

# 23.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR2 register will be set when either edge detector is triggered and its associated enable bit is set. The INTP enables rising edge interrupts and the INTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- ZCDIE bit of the PIE2 register

- INTP bit of the ZCDxCON register (for a rising edge detection)

- INTN bit of the ZCDxCON register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

Changing the POL bit can cause an interrupt, regardless of the level of the EN bit.

The ZCDIF bit of the PIR2 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 23.5 Correcting for VCPINV offset

The actual voltage at which the ZCD switches is the reference voltage at the noninverting input of the ZCD op amp. For external voltage source waveforms other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late.

#### 23.5.1 CORRECTION BY AC COUPLING

When the external voltage source is sinusoidal then the effects of the VCPINV offset can be eliminated by isolating the external voltage source from the ZCD pin with a capacitor in addition to the voltage reducing resistor. The capacitor will cause a phase shift resulting in the ZCD output switch in advance of the actual zero-crossing event. The phase shift will be the same for both rising and falling zero crossings, which can be compensated for by either delaying the CPU response to the ZCD switch by a timer or other means, or selecting a capacitor value large enough that the phase shift is negligible.

To determine the series resistor and capacitor values for this configuration, start by computing the impedance, Z, to obtain a peak current of 300 uA. Next, arbitrarily select a suitably large non-polar capacitor and compute its reactance, Xc, at the external voltage source frequency. Finally, compute the series resistor, capacitor peak voltage, and phase shift by the formulas shown in Equation 23-2.

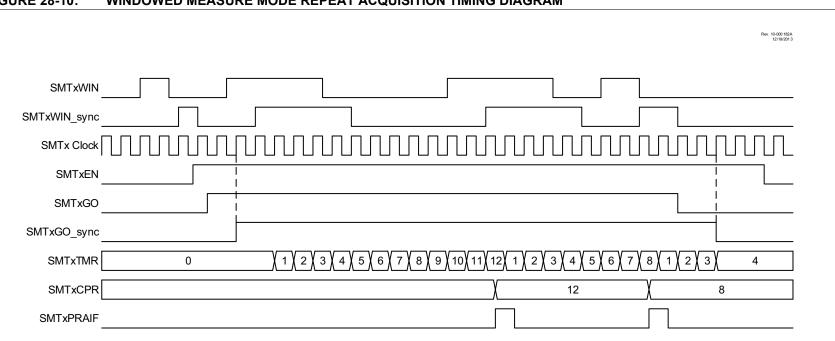

# 28.2 SMT Operation

The core of the module is the 24-bit counter, SMTxTMR combined with a complex data acquisition front-end. Depending on the mode of operation selected, the SMT can perform a variety of measurements summarized in Table .

# 28.2.1 CLOCK SOURCES

Clock sources available to the SMT include:

- Fosc

- Fosc/4

- HFINTOSC

- MFINTOSC (500 kHz and 31.25 kHz)

- LFINTOSC

- SOSC

The SMT clock source is selected by configuring the CSEL<2:0> bits in the SMTxCLK register. The clock source can also be prescaled using the PS<1:0> bits of the SMTxCON0 register. The prescaled clock source is used to clock both the counter and any synchronization logic used by the module.

# 28.2.2 PERIOD MATCH INTERRUPT

Similar to other timers, the SMT triggers an interrupt when SMTxTMR rolls over to '0'. This happens when SMTxTMR = SMTxPR, regardless of mode. Hence, in any mode that relies on an external signal or a window to reset the timer, proper operation requires that SMTxPR be set to a period larger than that of the expected signal or window.

# 28.3 Basic Timer Function Registers

The SMTxTMR time base and the SMTxCPW/SMTxPR/SMTxCPR buffer registers serve several functions and can be manually updated using software.

## 28.3.1 TIME BASE

The SMTxTMR is the 24-bit counter that is the center of the SMT. It is used as the basic counter/timer for measurement in each of the modes of the SMT. It can be reset to a value of 24'h00\_0000 by setting the RST bit of the SMTxSTAT register. It can be written to and read from software, but it is not guarded for atomic access, therefore reads and writes to the SMTxTMR should only be made when the GO = 0, or the software should have other measures to ensure integrity of SMTxTMR reads/writes.

# 28.3.2 PULSE-WIDTH LATCH REGISTERS

The SMTxCPW registers are the 24-bit SMT pulse width latch. They are used to latch in the value of the SMTxTMR when triggered by various signals, which are determined by the mode the SMT is currently in.

The SMTxCPW registers can also be updated with the current value of the SMTxTMR value by setting the CPWUP bit of the SMTxSTAT register.

## 28.3.3 PERIOD LATCH REGISTERS

The SMTxCPR registers are the 24-bit SMT period latch. They are used to latch in values of the SMTxTMR when triggered by various other signals, which are determined by the mode the SMT is currently in.

The SMTxCPR registers can also be updated with the current value of the SMTxTMR value by setting the CPRUP bit in the SMTxSTAT register.

# 28.4 Halt Operation

The counter can be prevented from rolling-over using the STP bit in the SMTxCON0 register. When halting is enabled, the period match interrupt persists until the SMTxTMR is reset (either by a manual Reset, **Section 28.3.1 "Time Base**") or by clearing the SMTxGO bit of the SMTxCON1 register and writing the SMTxTMR values in software.

# 28.5 Polarity Control

The three input signals for the SMT have polarity control to determine whether or not they are active high/positive edge or active low/negative edge signals.

The following bits apply to Polarity Control:

- WSEL bit (Window Polarity)

- SSEL bit (Signal Polarity)

- CSEL bit (Clock Polarity)

These bits are located in the SMTxCON0 register.

# 28.6 Status Information

The SMT provides input status information for the user without requiring the need to deal with the polarity of the incoming signals.

## 28.6.1 WINDOW STATUS

Window status is determined by the WS bit of the SMTxSTAT register. This bit is only used in Windowed Measure, Gated Counter and Gated Window Measure modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

## 28.6.2 SIGNAL STATUS

Signal status is determined by the AS bit of the SMTxSTAT register. This bit is used in all modes except Window Measure, Time of Flight and Capture modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

FIGURE 28-10:

PIC16(L)F19155/56/75/76/85/86

#### 28.8 Interrupts

The SMT can trigger an interrupt under three different conditions:

- PW Acquisition Complete

- PR Acquisition Complete

- Counter Period Match

The interrupts are controlled by the PIR8 and PIE8 registers of the device.

#### 28.8.1 PW AND PR ACQUISITION INTERRUPTS

The SMT can trigger interrupts whenever it updates the SMTxCPW and SMTxCPR registers, the circumstances for which are dependent on the SMT mode, and are discussed in each mode's specific section. The SMTxCPW interrupt is controlled by SMTxPWAIF and SMTxPWAIE bits in registers PIR8 and PIE8, respectively. The SMTxCPR interrupt is controlled by the SMTxPRAIF and SMTxPRAIE bits, also located in registers PIR8 and PIE8, respectively.

In Synchronous SMT modes, the interrupt trigger is synchronized to the SMTxCLK. In Asynchronous modes, the interrupt trigger is asynchronous. In either mode, once triggered, the interrupt will be synchronized to the CPU clock.

#### 28.8.2 COUNTER PERIOD MATCH INTERRUPT

As described in Section 28.2.2 "Period Match interrupt", the SMT will also interrupt upon SMTxTMR, matching SMTxPR with its period match limit functionality described in Section 28.4 "Halt Operation". The period match interrupt is controlled by SMTxIF and SMTxIE.

| Name     | Bit 7          | Bit 6  | Bit 5 | Bit 4  | Bit 3    | Bit 2     | Bit 1     | Bit 0   | Register on<br>Page |

|----------|----------------|--------|-------|--------|----------|-----------|-----------|---------|---------------------|

| PIE8     | LCDIE          | RTCCIE | —     | —      | —        | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 173                 |

| PIR8     | LCDIF          | RTCCIF | —     | —      | —        | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 182                 |

| SMT1CLK  | _              | _      | —     | _      | _        |           | CSEL<2:0> |         | 413                 |

| SMT1CON0 | EN             | _      | STP   | WPOL   | SPOL     | CPOL      | SMT1P     | 'S<1:0> | 410                 |

| SMT1CON1 | SMT1GO         | REPEAT | —     | —      |          | MODE      | <3:0>     |         | 411                 |

| SMT1CPRH |                |        |       | SMT1CF | PR<15:8> |           |           |         | 417                 |

| SMT1CPRL |                |        |       | SMT1CI | PR<7:0>  |           |           |         | 417                 |

| SMT1CPRU | SMT1CPR<23:16> |        |       |        |          | 417       |           |         |                     |

| SMT1CPWH | SMT1CPW<15:8>  |        |       |        |          |           | 418       |         |                     |

| SMT1CPWL | SMT1CPW<7:0>   |        |       |        |          |           | 418       |         |                     |

| SMT1CPWU |                |        |       | SMT1CP | W<23:16> |           |           |         | 418                 |

| SMT1PRH  |                |        |       | SMT1PI | R<15:8>  |           |           |         | 419                 |

| SMT1PRL  |                |        |       | SMT1P  | PR<7:0>  |           |           |         | 419                 |

| SMT1PRU  |                |        |       | SMT1PF | ?<23:16> |           |           |         | 419                 |

| SMT1SIG  | —              | _      | _     |        |          | SSEL<4:0> |           |         | 415                 |

| SMT1STAT | CPRUP          | CPWUP  | RST   | —      | _        | TS        | WS        | AS      | 412                 |

| SMT1TMRH |                |        |       | SMT1TM | 1R<15:8> |           |           |         | 416                 |

| SMT1TMRL |                |        |       | SMT1TM | /IR<7:0> |           |           |         | 416                 |

| SMT1TMRU |                |        |       | SMT1TM | R<23:16> |           |           |         | 416                 |

| SMT1WIN  | —              | _      | —     |        |          | WSEL<4:0> |           |         | 414                 |

#### TABLE 28-3: SUMMARY OF REGISTERS ASSOCIATED WITH SMTx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for SMTx module.

| Name      | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3          | Bit 2        | Bit 1    | Bit 0    |     |

|-----------|----------|----------|----------|----------|----------------|--------------|----------|----------|-----|

| CLC4GLS1  | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N | LC4G2D2T       | LC4G2D2N     | LC4G2D1T | LC4G2D1N | 506 |

| CLC4GLS2  | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N | LC4G3D2T       | LC4G3D2N     | LC4G3D1T | LC4G3D1N | 507 |

| CLC4GLS3  | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N | LC4G4D2T       | LC4G4D2N     | LC4G4D1T | LC4G4D1N | 508 |

| CLCIN0PPS | —        | -        | —        |          | (              | CLCIN0PPS<4: | 0>       |          | 264 |

| CLCIN1PPS | _        | _        | _        |          | CLCIN1PPS<4:0> |              |          |          | 264 |

| CLCIN2PPS | _        | _        | _        |          | CLCIN2PPS<4:0> |              |          | 264      |     |

| CLCIN3PPS | _        | _        | _        |          | CLCIN3PPS<4:0> |              |          | 264      |     |

# TABLE 32-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued)

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

# 33.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition generated

- · Stop condition generated

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 33.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 33.7** "**Baud Rate Generator**" for more detail.

#### 34.1.2.3 Receive Interrupts

The RXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RXxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RXxIF interrupts are enabled by setting all of the following bits:

- RXxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RXxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 34.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCxREG will not clear the FERR bit.

## 34.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

#### 34.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 34.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RXxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

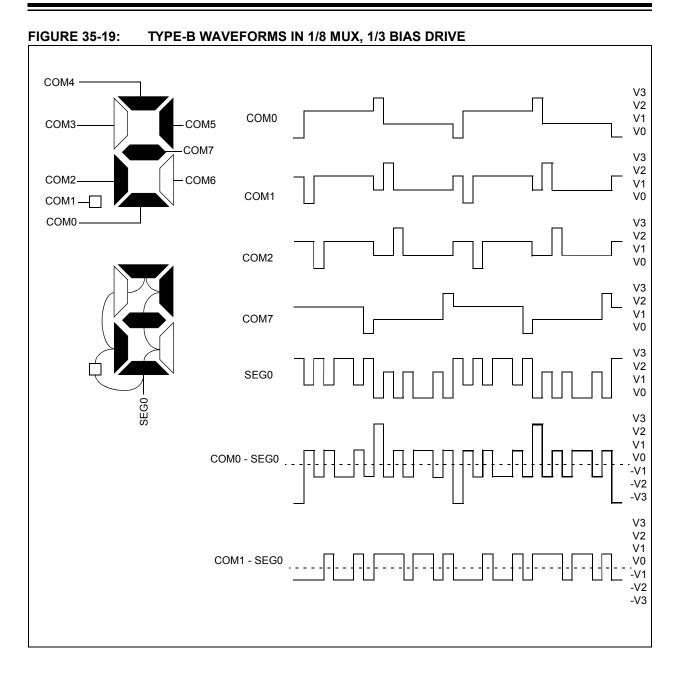

# PIC16(L)F19155/56/75/76/85/86

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SE(n) |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

#### REGISTER 35-3: LCDSEx: LCD SEGMENT x ENABLE REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-0 **SE(n+7):SE(n)** Segment Enable bits

| <u>For LCDSE0: n = 0-7</u>      |

|---------------------------------|

| <u>For LCDSE1: n = 8-15</u>     |

| For LCDSE2: n = 16-23           |

| <u>For LCDSE3: n = 24-31</u>    |

| <u>For LCDSE4: n = 32-39</u>    |

| For LCDSE5: n = 40-47           |

| 1 = Segment function of the pin |

1 = Segment function of the pin is enabled, digital I/O is disabled 0 = Segment function of the pin is disabled, digital I/O is enabled

## **REGISTER 35-4: LCDDATAX: LCD DATA x REGISTER**

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SEGxCOMy |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 SEGxCOMy: Pixel On bits

1 = Pixel on

0 = Pixel off

© 2017 Microchip Technology Inc.

# TABLE 39-11: RESET, WDT, OSCILLATOR START-UP TIMER, POWER-UP TIMER, BROWN-OUT RESET AND LOW-POWER BROWN-OUT RESET SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |                  |                                         |                 |                      |      |        |                                                                                                         |

|---------------------------------------------------------|------------------|-----------------------------------------|-----------------|----------------------|------|--------|---------------------------------------------------------------------------------------------------------|

| Param.<br>No.                                           | Sym.             | Characteristic                          | Min.            | Тур†                 | Max. | Units  | Conditions                                                                                              |

| RST01*                                                  | TMCLR            | MCLR Pulse Width Low to ensure Reset    | 2               |                      | —    | μS     |                                                                                                         |

| RST02*                                                  | Tioz             | I/O high-impedance from Reset detection | _               | _                    | 2    | μs     |                                                                                                         |

| RST03                                                   | TWDT             | Watchdog Timer Time-out Period          | _               | 16                   |      | ms     | 16 ms Wominal Reset Time                                                                                |

| RST04*                                                  | TPWRT            | Power-up Timer Period                   | _               | 65                   | _    | ms     |                                                                                                         |

| RST05                                                   | Vbor             | Brown-out Reset Voltage <sup>(4)</sup>  | _               | 2.70<br>2.45<br>1.90 | - <  | × ×    | BORV = 8<br>BORV = 1<br>(PIC16F)9155/56/75/76/85/86)<br>BORV = 1<br>(PIC16(L)F19155/56/75/76/85/<br>86) |

| RST06                                                   | VBORHYS          | Brown-out Reset Hysteresis              | _               | 40                   |      | _ mV∖_ |                                                                                                         |

| RST07                                                   | TBORDC           | Brown-out Reset Response Time           | — .             | 3                    | 1    | puş    |                                                                                                         |

| RST08                                                   | VLPBOR           | Low-Power Brown-out Reset Voltage       | $\overline{\ }$ | 2,45                 |      |        |                                                                                                         |

| RST07<br>RST08                                          | TBORDC<br>VLPBOR | Brown-out Reset Response Time           |                 | 3                    |      | × ×    |                                                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 39-12: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>

| Standard Operating Conditions (unless otherwise stated)       VDD = 3.0V, TA = 25°C |        |                                                   |          |           |        |       |                |

|-------------------------------------------------------------------------------------|--------|---------------------------------------------------|----------|-----------|--------|-------|----------------|

| Param.<br>No.                                                                       | Sym.   | Characteristic                                    | Min.     | ∨<br>Typ† | Max.   | Units | Conditions     |

| AD01                                                                                | NR     | Resolution                                        | <u> </u> | _         | 12     | bit   |                |

| AD02                                                                                | EIL    | Integral Error                                    | /-       | ±0.2      | ±1.0   | LSb   | ADCREF+ = 3.0V |

| AD03                                                                                | Edl    | Differential Error                                | —        | ±0.2      | ±1.0   | LSb   | ADCREF+ = 3.0V |

| AD04                                                                                | EOFF   | Offset Error                                      | —        | 6         |        | LSb   | ADCREF+ = 3.0V |

| AD05                                                                                | Egn    | Gain Error                                        | —        | 6         | —      | LSb   | ADCREF+ = 3.0V |

| AD06                                                                                | VADREF | ADC-Reference Voltage                             | 1.8      | _         | Vdd    | V     |                |

| AD07                                                                                | VAIN   | Full-Scale Range                                  | —        | _         | ADREF+ | V     |                |

| AD08                                                                                |        | Recommended Impedance of<br>Analog Voltage Source | —        | 1         | —      | kΩ    |                |

| AD09                                                                                | RVREF  | ADC Voltage Reference Ladder<br>Impedance         | —        | 50        | —      | kΩ    |                |

/ These parameters are characterized but not tested.

Data/in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Use of the ADC charge pump to improve linearity performance is recommended for VDD <= 2.5V

2: This is the impedance seen by the VREF pads when the external reference pads are selected.

Note 1: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.  $0.1 \ \mu$ F and  $0.01 \ \mu$ F values in parallel are recommended.