Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 43                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f19186-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

θ

Pull-up

Y

Υ

Y

Υ

Υ

Y

Y

Y

Y

Υ

Υ

Υ

Basic

\_

\_

VBAT

CLKOUT

OSC2 OSC1

CLKIN

INTPPS

\_

ICDCLK/

**ICSPCLK**

ICDDAT/

ICSPDAT

|   | 48-Pin TQFP/QFN | ADC                           | Reference | Comparator       | Zero-Cross Detect | DAC      | Timers/SMT           | ССР | WMd | CWG                   | dSSM                                   | EUSART                                   | СГС                   | RTCC | ГСD            | Interrupt-on-Change | High Current |   |

|---|-----------------|-------------------------------|-----------|------------------|-------------------|----------|----------------------|-----|-----|-----------------------|----------------------------------------|------------------------------------------|-----------------------|------|----------------|---------------------|--------------|---|

| 0 | 21              | ANA0                          | _         | C1IN0-<br>C2IN0- |                   | —        | —                    | _   |     | _                     | _                                      |                                          | CLCIN0 <sup>(1)</sup> | _    | SEG0           | IOCA0               | _            |   |

| 1 | 22              | ANA1                          |           | C1IN1-<br>C2IN1- |                   | —        | _                    |     |     |                       | _                                      |                                          | CLCIN1 <sup>(1)</sup> | -    | SEG1           | IOCA1               |              |   |

| 2 | 23              | ANA2                          | -         | C1IN0+<br>C2IN0+ |                   | DAC1OUT1 | —                    |     |     |                       | _                                      |                                          | _                     |      | SEG2           | IOCA2               | _            |   |

| 3 | 24              | ANA3                          | VREF+     | C1IN1+           | I                 | DAC1REF+ | _                    |     |     |                       | —                                      |                                          | —                     | -    | SEG3           | IOCA3               | —            | Ľ |

| 4 | 25              | ANA4                          | Ι         | -                |                   | —        | T0CKI <sup>(1)</sup> | -   | -   | -                     |                                        |                                          | -                     | Ι    | SEG4<br>COM3   | IOCA4               | Ι            |   |

| 5 | 26              | —                             | _         |                  |                   | —        | _                    | _   |     | _                     | SS <sup>(1)</sup>                      |                                          | —                     | _    | _              | IOCA5               | -            |   |

| 6 | 33              | ANA6                          | _         |                  |                   | _        | _                    |     |     |                       | _                                      |                                          | _                     | _    | SEG6           | IOCA6               | _            |   |

| 7 | 32              | ANA7                          | _         | _                | _                 | _        | _                    | _   | _   | _                     | _                                      | _                                        | _                     | _    | SEG7           | IOCA7               | —            |   |

| 0 | 8               | ANB0                          | —         | C2IN1+           | ZCD               | _        | _                    | —   | _   | CWG1IN <sup>(1)</sup> |                                        | _                                        | _                     | —    | SEG8           | IOCB0               | —            |   |

| 1 | 9               | ANB1                          | —         | C1IN3-<br>C2IN3- |                   | —        | _                    | _   |     | _                     | SCL,<br>SDA <sup>(1, 3, 4, 5, 6)</sup> | _                                        | —                     | -    | SEG9           | IOCB1               | HIB1         |   |

| 2 | 10              | ANB2                          | —         | _                | _                 | —        | —                    | _   | _   | _                     | SCL,<br>SDA <sup>(1, 3, 4, 5, 6)</sup> | -                                        | -                     | _    | SEG10<br>CFLY1 | IOCB2               | —            |   |

| 3 | 11              | ANB3                          | —         | C1IN2-<br>C2IN2- | _                 | —        | —                    | _   | _   | _                     | _                                      |                                          | —                     | -    | SEG11<br>CFLY2 | IOCB3               | —            |   |

| 4 | 16              | ANB4<br>ADCACT <sup>(1)</sup> | _         | _                | _                 | —        | —                    | _   | _   | _                     | —                                      | _                                        | —                     | _    | COM0           | IOCB4               | —            |   |

| 5 | 17              | ANB5                          | _         |                  |                   | —        | T1G <sup>(1)</sup>   | _   | _   | -                     | _                                      |                                          | —                     | —    | SEG13<br>COM1  | IOCB5               | _            |   |

| 6 | 18              | ANB6                          | _         | _                |                   | -        | _                    | _   |     | _                     | _                                      | TX2 <sup>(1)</sup><br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> | _    | SEG14          | IOCB6               | _            |   |

| 7 | 19              | ANB7                          | _         | _                |                   | DAC1OUT2 | _                    | _   | _   | _                     | _                                      | RX2 <sup>(1)</sup><br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | _    | SEG15          | IOCB7               | _            |   |

### 48-PIN ALLOCATION TABLE (PIC16(L)F19185/86) TABLE 5: ...

© 2017 Microchip Technology Inc.

I/O<sup>(2)</sup>

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

RB0

RB1

RB2

RB3

RB4

RB5

RB6

RB7

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note 1:

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific 4: or SMBUS input buffer thresholds.

These are alternative I<sup>2</sup>C logic levels pins. 5:

In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins. 6:

# 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing.

Refer to Table 7-1 for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

# TABLE 7-1: DEVICE CONFIGURATION INFORMATION FOR PIC16(L)F19155/56/75/76/85/86 FAMILY OF DEVICES

| ADDRESS | Name  | DESCRIPTION             | VALUE         | UNITS |

|---------|-------|-------------------------|---------------|-------|

| 8200h   | ERSIZ | Erase Row Size          | 32            | Words |

| 8201h   | WLSIZ | Number of write latches | 32            |       |

| 8202h   | URSIZ | Number of User Rows     | See Table 7-2 | Rows  |

| 8203h   | EESIZ | EE Data memory size     | 256           | Bytes |

| 8204h   | PCNT  | Pin Count               | 28/40/44/48   | Pins  |

### TABLE 7-2: MEMORY SIZE AND NUMBER OF USER ROWS

| Part Name      | Memory size | Number of User rows |

|----------------|-------------|---------------------|

| PIC16(L)F19155 | 8k          | 256                 |

| PIC16(L)F19175 | 8k          | 256                 |

| PIC16(L)F19185 | 8k          | 256                 |

| PIC16(L)F19156 | 16k         | 512                 |

| PIC16(L)F19176 | 16k         | 512                 |

| PIC16(L)F19186 | 16k         | 512                 |

# 7.1 DIA and DCI Access

The DIA and DCI addresses are read-only and cannot be erased or modified. See Section 13.4.7 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

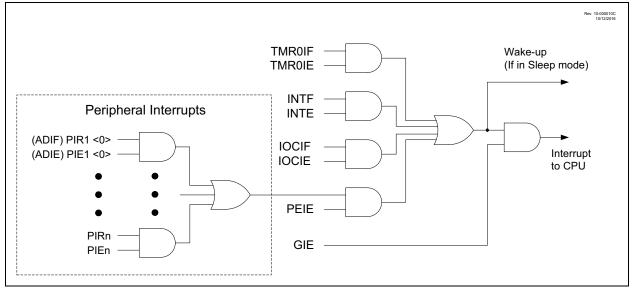

# **10.0 INTERRUPTS**

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

### FIGURE 10-1: INTERRUPT LOGIC

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|-----------|-----------|---------|---------------------|

| INTCON | GIE    | PEIE   | _      | _      | —      | —         | _         | INTEDG  | 164                 |

| PIE0   | _      | —      | TMR0IE | IOCIE  | —      | —         | _         | INTE    | 165                 |

| PIE1   | OSFIE  | CSWIE  | —      | -      | —      | —         | ADTIE     | ADIE    | 166                 |

| PIE2   | -      | ZCDIE  | _      |        | —      | —         | C2IE      | C1IE    | 167                 |

| PIE3   | RC2IE  | TX2IE  | RC1IE  | TX1IE  | _      | _         | BCL1IE    | SSP1IE  | 168                 |

| PIE4   | _      | —      | _      | _      | TMR4IE | —         | TMR2IE    | TMR1IE  | 169                 |

| PIE5   | CLC4IE | CLC3IE | CLC2IE | CLC1IE | —      | —         | _         | TMR1GIE | 170                 |

| PIE6   | CRIE   | —      | _      | -      | —      | —         | CCP2IE    | CCP1IE  | 171                 |

| PIE7   | _      | —      | NVMIE  | _      | —      | —         | _         | CWG1IE  | 172                 |

| PIE8   | LCDIE  | RTCCIE | _      | _      | —      | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 173                 |

| PIR0   | _      | —      | TMR0IF | IOCIF  | —      | —         | —         | INTF    | 174                 |

| PIR1   | OSFIF  | CSWIF  | _      |        | —      | —         | ADTIF     | ADIF    | 175                 |

| PIR2   | _      | ZCDIF  | _      | _      | _      | _         | C2IF      | C1IF    | 176                 |

| PIR3   | RC2IF  | TX2IF  | RC1IF  | TX1IF  | _      | _         | BCL1IF    | SSP1IF  | 177                 |

| PIR4   | _      | _      | _      | _      | TMR4IF | _         | TMR2IF    | TMR1IF  | 178                 |

| PIR5   | CLC4IF | CLC3IF | CLC2IF | CLC1IF | _      | _         | _         | TMR1GIF | 179                 |

| PIR6   | CRIF   | _      | _      | _      | _      | _         | CCP2IF    | CCP1IF  | 180                 |

| PIR7   | _      | _      | NVMIF  | _      | _      | _         | _         | CWG1IF  | 181                 |

| PIR8   | LCDIF  | RTCCIF | _      | _      | _      | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 182                 |

### TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2 | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|-------|---------|---------|---------------------|

| PORTE   | RE7     | RE6     | RE5     | RE4     | RE3     | _     | RE1     | RE0     | 248                 |

| TRISE   | TRISE7  | TRISE6  | TRISE5  | TRISE4  | TRISE3  | —     | TRISE1  | TRISE0  | 248                 |

| LATE    | LATE7   | LATE6   | LATE5   | LATE4   | LATE3   | —     | LATE1   | LATE0   | 249                 |

| ANSELE  | ANSE7   | ANSE6   | ANSE5   | ANSE4   | ANSE3   | —     | ANSE1   | ANSE0   | 249                 |

| WPUE    | WPUE7   | WPUE6   | WPUE5   | WPUE4   | WPUE3   | —     | WPUE1   | WPUE0   | 250                 |

| ODCONE  | ODCE7   | ODCE6   | ODCE5   | ODCE4   | ODCE3   | —     | ODCE1   | ODCE0   | 250                 |

| SLRCONE | SLRE7   | SLRE6   | SLRE5   | SLRE4   | SLRE3   | —     | SLRE1   | SLRE0   | 251                 |

| INLVLE  | INLVLE7 | INLVLE6 | INLVLE5 | INLVLE4 | INLVLE3 | _     | INLVLE1 | INLVLE0 | 251                 |

### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

| TABLE 15-3: | PPS OUTPUT SIGNAL ROUTING OPTIONS |

|-------------|-----------------------------------|

|             |                                   |

|                       | Outrast            |       | Remappable to Pins of PORTx |       |                   |       |       |       |                   |       |       |       |       |       |       |

|-----------------------|--------------------|-------|-----------------------------|-------|-------------------|-------|-------|-------|-------------------|-------|-------|-------|-------|-------|-------|

| Output Signal<br>Name | Output<br>Register | PIC   | C16(L)F1915                 | 5/56  | PIC16(L)F19175/76 |       |       |       | PIC16(L)F19185/86 |       |       |       |       |       |       |

|                       | Value              | PORTA | PORTB                       | PORTC | PORTA             | PORTB | PORTC | PORTD | PORTE             | PORTA | PORTB | PORTC | PORTD | PORTE | PORTF |

| RTCC                  | 0x18               | •     |                             | •     | •                 |       | •     |       |                   | •     |       | •     |       |       |       |

| ADGRDB                | 0x17               | •     |                             | •     | •                 |       | •     |       |                   | •     |       |       |       |       | •     |

| ADGRDA                | 0x16               | •     |                             | •     | •                 |       | •     |       |                   | •     |       |       |       |       | •     |

| TMR0                  | 0x15               |       | •                           | •     |                   | •     | •     |       |                   |       |       | •     |       |       | •     |

| SDO1/SDA1             | 0x14               |       | •                           | •     |                   | •     | •     |       |                   |       | •     | •     |       |       |       |

| SCK1/SCL1             | 0x13               |       | •                           | •     |                   | •     | •     |       |                   |       | •     | •     |       |       |       |

| C2OUT                 | 0x12               | •     |                             | •     | •                 |       |       |       | •                 | •     |       |       |       | •     |       |

| C1OUT                 | 0x11               | •     |                             | •     | •                 |       |       | •     |                   | •     |       |       | •     |       |       |

| DT2                   | 0x10               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| TX2/CK2               | 0x0F               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| DT1                   | 0x0E               |       | •                           | •     |                   | •     | •     |       |                   |       |       | •     |       |       | •     |

| TX1/CK1               | 0x0D               |       | •                           | •     |                   | •     | •     |       |                   |       |       | •     |       |       | •     |

| PWM4OUT               | 0x0C               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| PWM3OUT               | 0x0B               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CCP2                  | 0x0A               |       | •                           | •     |                   | •     | •     |       |                   |       |       | •     |       |       | •     |

| CCP1                  | 0x09               |       | •                           | •     |                   | •     | •     |       |                   |       |       | •     |       |       | •     |

| CWG1D                 | 0x08               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CWG1C                 | 0x07               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CWG1B                 | 0x06               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CWG1A                 | 0x05               |       | •                           | •     |                   | •     | •     |       |                   |       | •     | •     |       |       |       |

| CLC4OUT               | 0x04               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CLC3OUT               | 0x03               |       | •                           | •     |                   | •     |       | •     |                   |       | •     |       | •     |       |       |

| CLC2OUT               | 0x02               | •     |                             | •     | •                 |       | •     |       |                   | •     |       |       |       |       | •     |

| CLC1OUT               | 0x01               | •     |                             | •     | •                 |       | •     |       |                   | •     |       |       |       |       | •     |

© 2017 Microchip Technology Inc.

© 2017 Microchip Technology Inc.

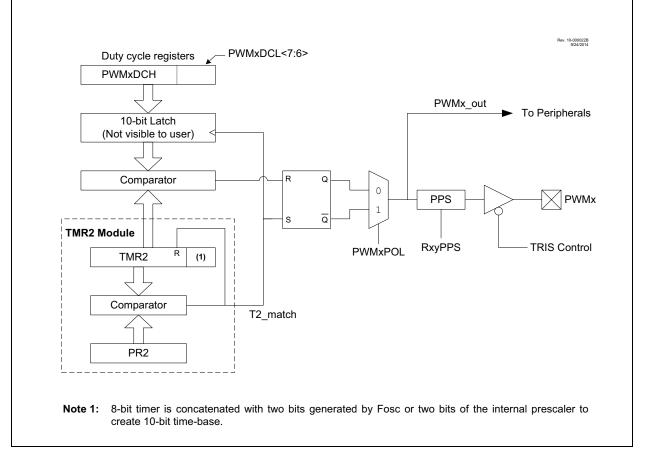

### 30.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 30-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = 0, the output will be the default state.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin.

- 2: Two identical Timer2 modules are implemented on this device. The timers are named Timer2 and Timer4. All references to Timer2 apply as well to Timer4. All references to T2PR apply as well to T4PR.

| R/W-x/u          | R/W-x/u      | R/W-x/u                              | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|--------------|--------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG4D4T         | LCxG4D4N     | LCxG4D3T                             | LCxG4D3N        | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |

| bit 7            |              |                                      |                 |                |                  |                  | bit         |

|                  |              |                                      |                 |                |                  |                  |             |

| Legend:          |              |                                      |                 |                |                  |                  |             |

| R = Readable     |              | W = Writable                         |                 | -              | nented bit, read |                  |             |

| u = Bit is uncha | anged        | x = Bit is unkr                      |                 | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |              | '0' = Bit is clea                    | ared            |                |                  |                  |             |

| bit 7            | LCxG4D4T: (  | Gate 3 Data 4 T                      | rue (non-inve   | rted) bit      |                  |                  |             |

|                  |              | (true) is gated i                    |                 | ,              |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 6            | LCxG4D4N:    | Gate 3 Data 4 I                      | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                     |                 |                |                  |                  |             |

|                  | 0 = CLCIN3   | (inverted) is no                     | t gated into Cl | Cx Gate 3      |                  |                  |             |

| bit 5            |              | Gate 3 Data 3 T                      | •               |                |                  |                  |             |

|                  |              | (true) is gated i                    |                 |                |                  |                  |             |

| 1.11.4           |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 4            |              | Gate 3 Data 3 I                      |                 |                |                  |                  |             |

|                  |              | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |

| bit 3            |              | Sate 3 Data 2 T                      | •               |                |                  |                  |             |

|                  |              | (true) is gated i                    |                 | ,              |                  |                  |             |

|                  | 0 = CLCIN1 ( | (true) is not gat                    | ed into CLCx    | Gate 3         |                  |                  |             |

| bit 2            | LCxG4D2N:    | Gate 3 Data 2 I                      | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                     |                 |                |                  |                  |             |

|                  | 0 = CLCIN1   | (inverted) is no                     | t gated into Cl | Cx Gate 3      |                  |                  |             |

| bit 1            | LCxG4D1T: (  | Gate 4 Data 1 T                      | rue (non-inve   | rted) bit      |                  |                  |             |

|                  |              | (true) is gated i                    |                 |                |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 0            |              | Gate 3 Data 1 I                      | •               |                |                  |                  |             |

|                  |              | (inverted) is ga                     |                 |                |                  |                  |             |

|                  | 0 = CLCINU(  | (inverted) is no                     | i galeu mio Cl  |                |                  |                  |             |

### REGISTER 32-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

| R/W-1/1          | R/W-1/1                  | R/W-1/1          | R/W-1/1                   | R/W-1/1                      | R/W-1/1                       | R/W-1/1                     | R/W-1/1      |

|------------------|--------------------------|------------------|---------------------------|------------------------------|-------------------------------|-----------------------------|--------------|

|                  |                          |                  | SSPxM                     | ISK<7:0>                     |                               |                             |              |

| bit 7            |                          |                  |                           |                              |                               |                             | bit 0        |

|                  |                          |                  |                           |                              |                               |                             |              |

| Legend:          |                          |                  |                           |                              |                               |                             |              |

| R = Readable     | e bit                    | W = Writable     | bit                       | U = Unimpler                 | nented bit, read              | l as '0'                    |              |

| u = Bit is uncl  | hanged                   | x = Bit is unkr  | nown                      | -n/n = Value a               | at POR and BO                 | R/Value at all c            | other Resets |

| '1' = Bit is set |                          | '0' = Bit is cle | ared                      |                              |                               |                             |              |

|                  |                          |                  |                           |                              |                               |                             |              |

| bit 7-1          | SSPxMSK<                 | 7:1>: Mask bits  |                           |                              |                               |                             |              |

|                  | 1 = The rec              | eived address b  | it n is compar            | ed to SSPxAD                 | <pre>D<n> to detect</n></pre> | I <sup>2</sup> C address ma | atch         |

|                  | 0 = The rec              | eived address b  | it n is not use           | d to detect I <sup>2</sup> C | address match                 |                             |              |

| bit 0            | SSPxMSK<                 | 0>: Mask bit for | I <sup>2</sup> C Slave mo | de, 10-bit Addr              | ess                           |                             |              |

|                  | I <sup>2</sup> C Slave m | ode, 10-bit addr | ess (SSPM<3               | 3:0> = 0111 or               | 1111):                        |                             |              |

|                  | 1 = The rec              | eived address b  | it 0 is compar            | ed to SSPxAD                 | D<0> to detect                | I <sup>2</sup> C address ma | atch         |

|                  | 0 = The rec              | eived address b  | it 0 is not use           | d to detect I <sup>2</sup> C | address match                 |                             |              |

|                  | l <sup>2</sup> C Slave m | ode, 7-bit addre | SS:                       |                              |                               |                             |              |

### REGISTER 33-5: SSPxMSK: SSPx MASK REGISTER

### REGISTER 33-6: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

|         |              |         |         |         |         | •       | ,       |  |  |  |

|---------|--------------|---------|---------|---------|---------|---------|---------|--|--|--|

| R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|         | SSPxADD<7:0> |         |         |         |         |         |         |  |  |  |

| bit 7   |              |         |         |         |         |         | bit 0   |  |  |  |

|         |              |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### Master mode:

| bit 7-0 | SSPxADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

### 10-Bit Slave mode – Most Significant Address Byte:

MSK0 bit is ignored.

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSPxADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 SSPxADD<7:0>: Eight Least Significant bits of 10-bit address

### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### 34.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RXxIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCxREG is read after the overflow occurs but before the fifth rising edge then the fifth rising edge will set the RXxIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCxREG to clear RXxIF.

- 2. If RCIDL is '0' then wait for RDCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

### 34.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RXxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 34-7), and asynchronously if the device is in Sleep mode (Figure 34-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in IDLE mode waiting to receive the next character.

### 34.3.3.1 Special Considerations

### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

### WUE Bit

The wake-up event causes a receive interrupt by setting the RXxIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

|        |        |           |                             |                | SYNC       | <b>C =</b> 0, <b>BRG</b>    | <b>i =</b> 0, BRG | <b>616 =</b> 1 |                             |                |                  |                             |  |

|--------|--------|-----------|-----------------------------|----------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos    | c = 8.000 | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc              | : = 3.686      | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | -      |           | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9  | -0.02     | 1666                        | 300.1          | 0.04       | 832                         | 300.0             | 0.00           | 767                         | 300.5          | 0.16             | 207                         |  |

| 1200   | 1199   | -0.08     | 416                         | 1202           | 0.16       | 207                         | 1200              | 0.00           | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404   | 0.16      | 207                         | 2404           | 0.16       | 103                         | 2400              | 0.00           | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615   | 0.16      | 51                          | 9615           | 0.16       | 25                          | 9600              | 0.00           | 23                          | —              | _                | _                           |  |

| 10417  | 10417  | 0.00      | 47                          | 10417          | 0.00       | 23                          | 10473             | 0.53           | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19.23k | 0.16      | 25                          | 19.23k         | 0.16       | 12                          | 19.20k            | 0.00           | 11                          | _              | _                | _                           |  |

| 57.6k  | 55556  | -3.55     | 8                           | _              | _          | _                           | 57.60k            | 0.00           | 3                           | _              | _                | _                           |  |

| 115.2k | —      |           | _                           | _              | _          | _                           | 115.2k            | 0.00           | 1                           | _              | —                | _                           |  |

### TABLE 34-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |            |                             |                |            |                             |                |                    |                             |  |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc                                                 | : = 32.00  | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc           | : = 18.43  | 2 MHz                       | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0          | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0          | 0.00               | 9215                        |  |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200           | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200           | 0.00               | 2303                        |  |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400           | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2400           | 0.00               | 1151                        |  |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597           | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9600           | 0.00               | 287                         |  |

| 10417  | 10417                                                | 0.00       | 767                         | 10417          | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10433          | 0.16               | 264                         |  |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k         | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.20k         | 0.00               | 143                         |  |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k         | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.60k         | 0.00               | 47                          |  |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k         | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 115.2k         | 0.00               | 23                          |  |

|        |                | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                |            |                             |                |            |                             |                |                  |                             |  |

|--------|----------------|------------------------------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | c = 8.000                                            | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Foso           | : = 3.686  | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0          | 0.00                                                 | 6666                        | 300.0          | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04             | 832                         |  |

| 1200   | 1200           | -0.02                                                | 1666                        | 1200           | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16             | 207                         |  |

| 2400   | 2401           | 0.04                                                 | 832                         | 2398           | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16             | 103                         |  |

| 9600   | 9615           | 0.16                                                 | 207                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16             | 25                          |  |

| 10417  | 10417          | 0                                                    | 191                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00             | 23                          |  |

| 19.2k  | 19.23k         | 0.16                                                 | 103                         | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16             | 12                          |  |

| 57.6k  | 57.14k         | -0.79                                                | 34                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _                | _                           |  |

| 115.2k | 117.6k         | 2.12                                                 | 16                          | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | —              | _                | _                           |  |

| R/W-0        | R/W-0                      | HS/C-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|----------------------------|-------------------------------------|-----------------|------------------|-----------------|-----------------|--------|

| LCDEN        | SLPEN                      | WERR                                | CS              | LMUX3            | LMUX2           | LMUX1           | LMUX0  |

| bit 7        |                            |                                     |                 |                  |                 |                 | bit 0  |

| Legend:      |                            | C = Clearable                       | e bit           | HS = Bit is se   | t by hardware   |                 |        |

| R = Readab   | le bit                     | W = Writable                        | bit             | U = Unimplen     | nented bit, rea | ıd as '0'       |        |

| -n = Value a | t POR                      | '1' = Bit is set                    |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

| bit 7        | LCDEN: LCD                 | Enable bit                          |                 |                  |                 |                 |        |

|              |                            | lule is enabled<br>lule is disabled |                 |                  |                 |                 |        |

| bit 6        | SLPEN: LCD                 | Display Sleep-                      | Enabled bit     |                  |                 |                 |        |

|              |                            | vill stop driving                   |                 |                  |                 |                 |        |

|              |                            | vill continue driv                  |                 |                  |                 |                 |        |

| bit 5        |                            | Write Failed Er                     |                 |                  |                 |                 |        |

|              |                            |                                     | A register occ  | urred (must be   | reset in softwa | are)            |        |

|              | 0 = No LCD                 |                                     |                 |                  |                 |                 |        |

| bit 4        |                            | urce Select bit                     |                 |                  |                 |                 |        |

|              | 1 = SOSC Se<br>0 = LFINTOS |                                     |                 |                  |                 |                 |        |

| bit 3-0      |                            |                                     | tion hita Cna   | oifice the numb  | or of common    | .(2)            |        |

| DIT 3-0      |                            | Common Selec                        | ction bits. Spe | cifies the numbe | er of commons   | 5(-)            |        |

|              | LMUX<3                     | :0>                                 |                 | Multiplex        |                 |                 | Bias   |

|              | 0000                       |                                     |                 | All COMs off     |                 |                 | _      |

|              | 0001                       |                                     |                 | Static (COM0)    |                 |                 | Static |

|              | 0010                       |                                     | 1/2             | MUX (COM<1:      | 0>)             |                 | 1/2    |

|              | 0011                       |                                     | 1/3             | MUX (COM<2:      | 0>)             |                 | 1/3    |

|              | 0100                       |                                     | 1/4             | MUX (COM<3:      | 0>)             |                 | 1/3    |

|              | 0101                       |                                     | 1/5             | MUX (COM<4:      | 0>)             |                 | 1/3    |

|              | 0110                       |                                     | 1/6             | MUX (COM<5:      | 0>)             |                 | 1/3    |

|              | 0111                       |                                     | 1/7             | MUX (COM<6:      | 0>)             |                 | 1/3    |

|              | 1000                       |                                     | 1/8             | MUX (COM<7:      | 0>)             |                 | 1/3    |

### REGISTER 35-1: LCDCON: LCD CONTROL REGISTER

Note 1: Bit can only be set by hardware and only cleared in software by writing to zero.

**2:** Cannot be changed when LCDEN = 1.

# 37.2 General Format for Instructions

|  | TABLE 37-3: | INSTRUCTION SET |

|--|-------------|-----------------|

|--|-------------|-----------------|

| Mnemonic, |         | Description                                 | Cycles        | 14-Bit Opcode |      |      |      | Status   | Notes    |

|-----------|---------|---------------------------------------------|---------------|---------------|------|------|------|----------|----------|

| Oper      | ands    | Description                                 | Cycles        | MSb           |      |      | LSb  | Affected | Note     |

|           |         | BYTE-ORIENTED FILE                          | REGISTER OPE  | RATIC         | ONS  |      |      |          |          |

| ADDWF     | f, d    | Add W and f                                 | 1             | 00            | 0111 | dfff | ffff | C, DC, Z | 2        |

| ADDWFC    | f, d    | Add with Carry W and f                      | 1             | 11            | 1101 | dfff | ffff | C, DC, Z | 2        |

| ANDWF     | f, d    | AND W with f                                | 1             | 00            | 0101 | dfff | ffff | Z        | 2        |

| ASRF      | f, d    | Arithmetic Right Shift                      | 1             | 11            | 0111 | dfff | ffff | C, Z     | 2        |

| LSLF      | f. d    | Logical Left Shift                          | 1             | 11            | 0101 | dfff | ffff | c.z      | 2        |

| LSRF      | f. d    | Logical Right Shift                         | 1             | 11            | 0110 | dfff | ffff | C, Z     | 2        |

| CLRF      | f       | Clear f                                     | 1             | 00            |      | lfff |      | Z        | 2        |

| CLRW      | _       | Clear W                                     | 1             | 00            | 0001 | 0000 | 00xx | Z        | -        |

| COMF      | f. d    | Complement f                                | 1             | 00            | 1001 | dfff | ffff | Z        | 2        |

| DECF      | f. d    | Decrement f                                 | 1             | 00            | 0011 | dfff | ffff | Z        | 2        |

| INCF      | f, d    | Increment f                                 | 1             |               |      |      |      | Z        |          |

|           | ,       |                                             | 1             | 00            | 1010 |      | ffff | Z        | 2<br>2   |

| IORWF     | f, d    | Inclusive OR W with f                       |               | 00            | 0100 |      | ffff |          |          |

| MOVF      | f, d    | Move f                                      | 1             | 00            | 1000 |      | ffff | Z        | 2        |

| MOVWF     | f       | Move W to f                                 | 1             | 00            | 0000 |      | ffff | _        | 2        |

| RLF       | f, d    | Rotate Left f through Carry                 | 1             | 00            | 1101 |      | ffff | С        | 2        |

| RRF       | f, d    | Rotate Right f through Carry                | 1             | 00            | 1100 |      | ffff | С        | 2        |

| SUBWF     | f, d    | Subtract W from f                           | 1             | 00            | 0010 | dfff | ffff | C, DC, Z | 2        |

| SUBWFB    | f, d    | Subtract with Borrow W from f               | 1             | 11            | 1011 | dfff | ffff | C, DC, Z | 2        |

| SWAPF     | f, d    | Swap nibbles in f                           | 1             | 00            | 1110 | dfff | ffff |          | 2        |

| XORWF     | f, d    | Exclusive OR W with f                       | 1             | 00            | 0110 | dfff | ffff | Z        | 2        |

|           |         | BYTE ORIENTED                               | SKIP OPERATIO | ONS           |      |      |      |          |          |

| DECFSZ    | f, d    | Decrement f, Skip if 0                      | 1(2)          | 00            | 1011 | dfff | ffff |          | 1, 2     |

| INCFSZ    | f, d    | Increment f, Skip if 0                      | 1(2)          | 00            | 1111 | dfff | ffff |          | 1, 2     |

|           |         | BIT-ORIENTED FILE                           | REGISTER OPER | RATIO         | NS   | •    | •    |          |          |

| BCF       | f, b    | Bit Clear f                                 | 1             | 01            | 00bb | bfff | ffff |          | 2        |

| BSF       | f, b    | Bit Set f                                   | 1             | 01            | 01bb | bfff | ffff |          | 2        |

|           |         | BIT-ORIENTED                                | SKIP OPERATIO | NS            |      | •    |      |          |          |

| BTFSC     | f, b    | Bit Test f, Skip if Clear                   | 1 (2)         | 01            | 10bb | bfff | ffff |          | 1, 2     |

| BTFSS     | f, b    | Bit Test f, Skip if Set                     | 1 (2)         | 01            |      |      | ffff |          | 1, 2     |

| LITERAL ( | OPERATI | -                                           |               | 1             |      |      |      |          | 1        |

| ADDLW     | k       | Add literal and W                           | 1             | 11            | 1110 | kkkk | kkkk | C, DC, Z |          |

| ANDLW     | k       | AND literal with W                          | 1             | 11            | 1001 | kkkk | kkkk | Z        | 1        |

| IORLW     | k       | Inclusive OR literal with W                 | 1             | 11            | 1000 |      | kkkk | Z        |          |

| MOVLB     | k       | Move literal to BSR                         | 1             | 00            | 000  | 0k   | kkkk |          |          |

| MOVLP     | k       | Move literal to PCLATH                      | 1             | 11            | 0001 |      | kkkk |          | 1        |

| MOVLW     | k       | Move literal to W                           | 1             | 11            | 0000 | kkkk |      |          |          |

| SUBLW     | k       | Subtract W from literal                     | 1             | 11            | 1100 |      | kkkk | C, DC, Z |          |

| XORLW     | k       | Exclusive OR literal with W                 | 1             | 11            |      | kkkk |      | Z, DO, Z |          |

| Note 1:   |         | ogram Counter (PC) is modified, or a condit |               |               |      |      |      |          | <u> </u> |

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Syntax:          | [ label ] BRA label                                                                                                                                                                                                                             | Syntax:    |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                                        | Operands   |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255                                                                                                                                                                                                                     |            |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                                            | Operation  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   | Status Aff |

| Status Affected: | None                                                                                                                                                                                                                                            | Descriptic |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |            |

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| X:        | [ label ] BTFSS f,b                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ands:     | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                    |

| ation:    | skip if (f <b>) = 1</b>                                                                                                                                                                             |

| Affected: | None                                                                                                                                                                                                |

| iption:   | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

Bit Test f, Skip if Set

Λ

### **TABLE 39-3**: POWER-DOWN CURRENT (IPD)<sup>(1,2)</sup>

| PIC16(L)F19155/56/75/76/85/86 |                  |                                          | Standard Operating Conditions (unless otherwise stated)               |       |                     |                     |       |      |                                                                                                                                                    |

|-------------------------------|------------------|------------------------------------------|-----------------------------------------------------------------------|-------|---------------------|---------------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16F19155/56/75/76/85/86    |                  |                                          | Standard Operating Conditions (unless otherwise stated)<br>VREGPM = 1 |       |                     |                     |       |      |                                                                                                                                                    |

| Param.<br>No.                 | Symbol           | Device Characteristics                   | Min.                                                                  | Typ.† | Max.<br>+85°C       | Max.<br>+125°C      | Units | VDD  | Conditions                                                                                                                                         |

| D200                          | IPD              | IPD Base                                 | _                                                                     | 0.05  | _                   | _                   | μA    | 3.00 |                                                                                                                                                    |

| D200                          | IPD              | IPD Base                                 | _                                                                     | 0.4   | _                   | $\sim$              | μA    | 3.0V | $\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{$ |

| D200A                         |                  |                                          | _                                                                     | 18    | _ <                 | F                   | μA    | 3.0V | VREGPM = 0                                                                                                                                         |

| D201                          | IPD_WDT          | Low-Frequency Internal<br>Oscillator/WDT | —                                                                     | 0.4   | -                   | $\langle - \rangle$ | μA    | 3.0V |                                                                                                                                                    |

| D201                          | IPD_WDT          | Low-Frequency Internal<br>Oscillator/WDT | —                                                                     | 0.6   |                     | 7                   | μΑ    | 3.0V |                                                                                                                                                    |

| D202                          | IPD_SOSC         | Secondary Oscillator (SOSC)              | _                                                                     | _0.6_ |                     | <u> </u>            | μA    | 3.0V |                                                                                                                                                    |

| D202                          | IPD_SOSC         | Secondary Oscillator (SOSC)              | — `                                                                   | _ 0.8 | -                   | $\rightarrow$       | μΑ    | 3.0V |                                                                                                                                                    |

| D203                          | IPD_FVR          | FVR                                      | A                                                                     | 28    |                     | $\rightarrow$       | μΑ    | 3.0V |                                                                                                                                                    |

| D203                          | IPD_FVR          | FVR                                      | X                                                                     | 33    | $\langle - \rangle$ | _                   | μΑ    | 3.0V |                                                                                                                                                    |

| D204                          | IPD_BOR          | Brown-out Reset (BOR)                    |                                                                       | 10    | $\geq$              | —                   | μΑ    | 3.0V |                                                                                                                                                    |

| D204                          | IPD_BOR          | Brown-out Reset (BOR)                    | X                                                                     | 74    | > -                 | —                   | μΑ    | 3.0V |                                                                                                                                                    |

| D205                          | IPD_LPBOR        | Low-Power Brown-out Reset (LPBOR)        | $\langle \succ \rangle$                                               | 0.5   | 1 —                 | —                   | μΑ    | 3.0V |                                                                                                                                                    |

| D205                          | IPD_LPBOR        | Low-Power Brown-out Reset (LPBOR)        | $\langle + \rangle$                                                   | 0.7   | -                   | —                   | μΑ    | 3.0V |                                                                                                                                                    |

| D206                          | IPD_ADCA         | ADC - Active                             | $\langle - \rangle$                                                   | 250   | —                   | —                   | μΑ    | 3.0V | ADC is converting (4)                                                                                                                              |

| D206                          | IPD_ADCA         | ADC - Active                             | $\geq$                                                                | 280   | —                   | —                   | μΑ    | 3.0V | ADC is converting (4)                                                                                                                              |