Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19155-e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name     | Bit 7  | Bit 6                                                   | Bit 5    | Bit 4          | Bit 3                | Bit 2     | Bit 1  | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|--------|---------------------------------------------------------|----------|----------------|----------------------|-----------|--------|-----------|-----------------------|----------------------------|

| Bank 4  | •        |        |                                                         |          |                |                      |           | •      |           | •                     |                            |

|         |          |        |                                                         | CPU      | CORE REGISTERS | S; see Table 4-3 for | specifics |        |           |                       |                            |

| 20Ch    | TMR1L    | TMR1L7 | TMR1L7 TMR1L6 TMR1L5 TMR1L4 TMR1L3 TMR1L2 TMR1L1 TMR1L0 |          |                |                      |           |        | 0000 0000 | uuuu uuu              |                            |

|         |          |        |                                                         | <u>.</u> | TMF            | R1L                  |           |        |           | 0000 0000             | uuuu uuu                   |

| 20Dh    | TMR1H    | TMR1H7 | TMR1H6                                                  | TMR1H5   | TMR1H4         | TMR1H3               | TMR1H2    | TMR1H1 | TMR1H0    | 0000 0000             | uuuu uuu                   |

|         |          |        |                                                         |          | TMF            | 1H                   |           |        |           | 0000 0000             | uuuu uuu                   |

| 20Eh    | T1CON    | _      | _                                                       | CKP      | S<1:0>         | _                    | SYNC      | RD16   | ON        | 0000 0000             | uu -u0                     |

| 20Fh    | T1GCON   | GE     | GPOL                                                    | GTM      | GSPM           | GGO/DONE             | GVAL      | —      | _         | 0000 0x               | uuuu ux-                   |

| 210h    | T1GATE   | _      | _                                                       | _        |                | GSS<4:0>             |           |        |           | 0000                  | u uuu                      |

| 211h    | T1CLK    | _      | —                                                       | —        | —              | CS<3:0>              |           |        |           | 0000                  | uuu                        |

| 212h    | —        |        | Unimplemented                                           |          |                |                      |           |        |           |                       |                            |

| 213h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 214h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 215h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 216h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 217h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 218h    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 219h    | _        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 21Ah    | _        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 21Bh    | _        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 21Ch    | _        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

| 21Dh    | _        |        |                                                         | -        | Unimple        | mented               |           | •      |           |                       |                            |

| 21Eh    | CCPTMRS0 | P4TS   | EL<1:0>                                                 | P3T5     | SEL1:0>        | C2TSE                | L<1:0>    | C1TS   | EL<1:0>   | 0101 0101             | 0101 010                   |

| 21Fh    | —        |        |                                                         |          | Unimple        | mented               |           |        |           |                       |                            |

## TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

DS40001923A-page 65

| Address | Name       | Bit 7    | Bit 6 | Bit 5 | Bit 4         | Bit 3                | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|------------|----------|-------|-------|---------------|----------------------|-----------|-----------|-------|-----------------------|----------------------------|

| Bank 12 |            |          |       |       |               |                      |           |           |       |                       |                            |

|         |            |          |       | CPU   | CORE REGISTER | S: see Table 4-3 for | specifics |           |       |                       |                            |

|         | 1          |          |       |       |               |                      |           |           |       | -                     |                            |

| 60Ch    | CWG1CLKCON | —        | —     | —     | —             | -                    | —         | —         | CS    | 0000 0000             | 0000 0000                  |

| 60Dh    | CWG1ISM    | —        | _     | —     | _             |                      | IS        | <3:0>     |       | 0000 0000             | 0000 0000                  |

| 60Eh    | CWG1DBR    | —        | _     |       |               | DBR<                 | 5:0>      |           |       | 0000 0000             | 0000 0000                  |

| 60Fh    | CWG1DBF    | —        | _     |       |               | DBF<                 | 5:0>      |           |       | 0000 0000             | 0000 0000                  |

| 610h    | CWG1CON0   | EN       | LD    | —     | —             | —                    |           | MODE<2:0> |       | 00000                 | 00000                      |

| 611h    | CWG1CON1   | _        | —     | IN    | —             | POLD                 | POLC      | POLB      | POLA  | x- 0000               | u- 0000                    |

| 612h    | CWG1AS0    | SHUTDOWN | REN   | LSB   | BD<1:0>       | LSAC                 | <1:0>     | _         | _     | 0001 01               | 0001 01                    |

| 613h    | CWG1AS1    | _        | _     | —     | AS4E          | AS3E                 | AS2E      | AS1E      | AS0E  | 0000 0000             | u 0000                     |

| 614h    | CWG1STR    | OVRD     | OVRC  | OVRB  | OVRA          | STRD                 | STRC      | STRB      | STRA  | 0000 0000             | 0000 0000                  |

| 615h    | _          | <u> </u> |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 616h    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 617h    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 618h    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 619h    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Ah    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Bh    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Ch    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Dh    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Eh    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

| 61Fh    | _          |          |       |       | Unimple       | mented               |           |           |       |                       |                            |

## TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(1) E19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

## 8.4 Register Definitions: Brown-out Reset Control

#### REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | —   | —   | —   | —   | —   | _   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words ≠ 01:                |

|         | SBOREN is read/write, but has no effect on the BOR.        |

|         | If BOREN <1:0> in Configuration Words = 01:                |

|         | 1 = BOR Enabled                                            |

|         | 0 = BOR Disabled                                           |

| bit 6-1 | Unimplemented: Read as '0'                                 |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit           |

|         | 1 = The Brown-out Reset circuit is active                  |

0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

#### EXAMPLE 13-1: PFM PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

NVMCON1,NVMREGS ; Do not select Configuration Space

BCF

NVMCON1, RD

BSF

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDATL,W; Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

## 18.3 Register Definitions: FVR Control

#### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|---------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAF\   | /R<1:0> | ADFVI   | R<1:0>  |

| bit 7   |                       |                     |                      |         |         |         | bit 0   |

| Legend:                   | abla bit                          |                                                                                                                                                                     | $11 - 11$ minutes and a bit $r_{2} = 1 - 1 - 1$                                              |  |  |  |  |

|---------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| R = Read                  |                                   | W = Writable bit                                                                                                                                                    | U = Unimplemented bit, read as '0'                                                           |  |  |  |  |

|                           | unchanged                         | x = Bit is unknown                                                                                                                                                  | -n/n = Value at POR and BOR/Value at all other Res                                           |  |  |  |  |

| '1' = Bit is set          |                                   | '0' = Bit is cleared                                                                                                                                                | q = Value depends on condition                                                               |  |  |  |  |

| bit 7                     | 1 = Fixed                         | ixed Voltage Reference Enal<br>Voltage Reference is enable<br>Voltage Reference is disable                                                                          | d <sup>(4)</sup>                                                                             |  |  |  |  |

| bit 6                     | 1 = Fixed                         | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                            | ready for use                                                                                |  |  |  |  |

| bit 5                     | 1 = Temp                          | nperature Indicator Enable b<br>erature Indicator is enabled<br>erature Indicator is disabled                                                                       | it <sup>(3)</sup>                                                                            |  |  |  |  |

| bit 4                     | 1 = Temp                          | emperature Indicator Range<br>erature in High Range<br>erature in Low Range                                                                                         | Selection bit <sup>(3)</sup>                                                                 |  |  |  |  |

| bit 3-2                   | 11 = Com<br>10 = Com<br>01 = Com  | <b>C1:0&gt;:</b> Comparator FVR Buffer<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off | x, (4.096∨) <sup>(2)</sup><br>x, (2.048∨) <sup>(2)</sup>                                     |  |  |  |  |

| bit 1-0                   | 11 = ADC<br>10 = ADC<br>01 = ADC  | <b>:0&gt;:</b> ADC FVR Buffer Gain S<br>FVR Buffer Gain is 4x, (4.09<br>FVR Buffer Gain is 2x, (2.04<br>FVR Buffer Gain is 1x, (1.02<br>FVR Buffer is off           | 06∨) <sup>(2)</sup><br>18∨) <sup>(2)</sup>                                                   |  |  |  |  |

| Note 1:<br>2:<br>3:<br>4: | Fixed Voltage F<br>See Section 20 | Reference output cannot exce                                                                                                                                        | 56/75/76/85/86 devices only.<br>eed VDD.<br><b>Module (TIM)"</b> for additional information. |  |  |  |  |

© 2017 Microchip Technology Inc.

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2    | Bit 1    | Bit 0 | Register<br>on page |

|----------|--------|-------|---------|---------|--------|----------|----------|-------|---------------------|

| DAC1CON0 | DAC1EN | —     | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0>  | _        | —     | 332                 |

| DAC1CON1 | _      | -     | _       |         |        | DAC1R<4: | 0>       |       | 332                 |

| CM1PSEL  | —      | _     | —       | —       | _      |          | PCH<2:0> |       | 342                 |

| CM2PSEL  | _      | _     | —       |         |        |          | PCH<2:0> |       | 342                 |

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC1 module.

### 25.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 25-2 displays the clock source selections.

#### 25.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 25.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### 25.3 Programmable Prescaler

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or the T0CON1 register.

#### 25.4 Programmable Postscaler

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS<3:0> bits of the TOCON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or the T0CON0 register.

#### 25.5 Operation during Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

#### 25.6 Timer0 Interrupts

The Timer0 Interrupt Flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (T0OUTPS<3:0>) are set to 1:1 operation (no division), the T0IF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every T0OUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = 1), the CPU will be interrupted and the device may wake from sleep (see Section 25.2 "Clock Source Selection" for more details).

### 25.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see Section 15.0 "Peripheral Pin Select (PPS) Module" for additional information). The Timer0 output can also be used by other peripherals, such as the Auto-conversion Trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (T0OUT) of the T0CON0 register (Register 25-1).

TMR0\_out will be one postscaled clock period when a match occurs between TMR0L and TMR0H in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

## 26.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is 16-bit timer/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- Clock source for optional comparator synchronization

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

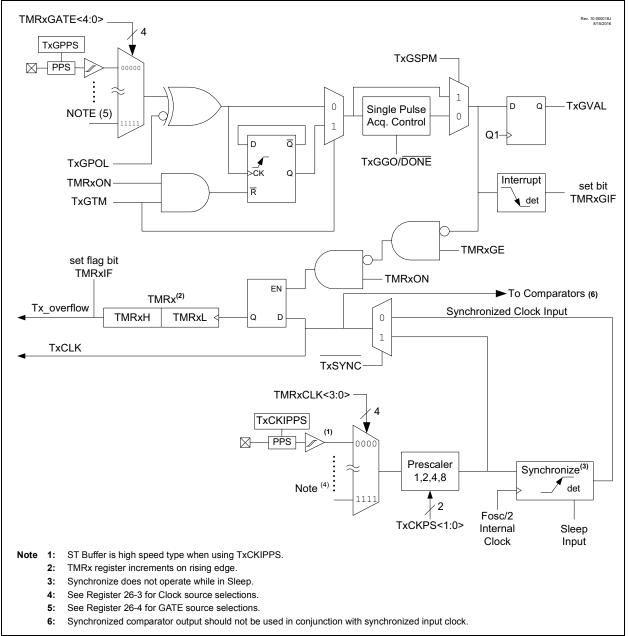

Figure 26-1 is a block diagram of the Timer1 module. This device has one instance of Timer1 type modules.

#### FIGURE 26-1: TIMER1 BLOCK DIAGRAM

#### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

#### 28.7.8 CAPTURE MODE

Capture mode captures the Timer value based on a rising or falling edge on the SMTWINx input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the SMTxGO bit being set, and updates the value of the SMTxCPR register on each rising edge of SMTWINx, and updates the value of the CPW register on each falling edge of the SMTWINx. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See Figure 28-16 and Figure 28-17.

| KEGISTER 51-3              |                              |                                              |                 |                                  |                 |                 |              |

|----------------------------|------------------------------|----------------------------------------------|-----------------|----------------------------------|-----------------|-----------------|--------------|

| R/W/HS-0/0                 | R/W-0/0                      | R/W-0/0                                      | R/W-1/1         | R/W-0/0                          | R/W-1/1         | U-0             | U-0          |

| SHUTDOWN <sup>(1, 2)</sup> | REN                          | LSBI                                         | D<1:0>          | LSAC                             | <1:0>           |                 | _            |

| bit 7                      |                              |                                              |                 |                                  |                 |                 | bit (        |

|                            |                              |                                              |                 |                                  |                 |                 |              |

| Legend:                    |                              |                                              |                 |                                  |                 |                 |              |

| HC = Bit is cleare         | d by hardware                |                                              |                 | HS = Bit is se                   | et by hardware  | 9               |              |

| R = Readable bit           |                              | W = Writable                                 | e bit           | U = Unimplei                     | mented bit, rea | ad as 'O'       |              |

| u = Bit is unchang         | ged                          | x = Bit is unk                               | nown            | -n/n = Value a                   | at POR and BO   | OR/Value at all | other Resets |

| '1' = Bit is set           |                              | '0' = Bit is cleared q = Value depends on co |                 | pends on conc                    | ndition         |                 |              |

| L:1 7                      |                              |                                              |                 | hua hit(1, 2)                    |                 |                 |              |

| bit 7                      |                              | Shutdown sta                                 | own Event Stat  | tus bit <sup>(1, -)</sup>        |                 |                 |              |

|                            |                              |                                              | ent has occurre | ed                               |                 |                 |              |

| bit 6                      | REN: Auto-R                  | estart Enable                                | bit             |                                  |                 |                 |              |

|                            | 1 = Auto-res                 | tart enabled                                 |                 |                                  |                 |                 |              |

|                            | 0 = Auto-res                 | tart disabled                                |                 |                                  |                 |                 |              |

| bit 5-4                    | LSBD<1:0>:                   | CWG1B and                                    | CWG1D Auto      | -Shutdown Sta                    | te Control bits |                 |              |

|                            |                              |                                              |                 | hen an auto-sh                   |                 |                 |              |

|                            | •                            | •                                            |                 | hen an auto-sh<br>an auto-shutdo |                 | •               |              |

|                            |                              |                                              |                 | g polarity, is pla               |                 |                 | equired dead |

|                            | band in                      | terval                                       |                 |                                  |                 |                 | ·            |

| bit 3-2                    | LSAC<1:0>:                   | CWG1A and                                    | CWG1C Auto      | -Shutdown Sta                    | te Control bits |                 |              |

|                            |                              |                                              |                 | hen an auto-sh                   |                 |                 |              |

|                            |                              |                                              |                 | hen an auto-sh<br>an auto-shutdo |                 |                 |              |

|                            |                              |                                              |                 | g polarity, is pla               |                 |                 | equired dead |

|                            | band in                      |                                              |                 |                                  |                 |                 | •            |

| bit 1-0                    | Unimplemer                   | nted: Read as                                | · '0'           |                                  |                 |                 |              |

| Note 1: This I             | bit may be writ<br>juration. | tten while EN                                | = 0 (CWG10      | CON0 register                    | ) to place the  | outputs into    | the shutdow  |

#### REGISTER 31-5: CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

| U-0                                                                                                            | U-0                                                               | R/W-x/u                                                                                                      | R/W-x/u                                                | R/W-x/u                                            | R/W-x/u                                                | R/W-x/u                                 | R/W-x/u       |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------|---------------|

| _                                                                                                              | _                                                                 | lotting                                                                                                      | 1011 /04                                               |                                                    | S<5:0>                                                 | 1017,00                                 | 1011700       |

| pit 7                                                                                                          |                                                                   |                                                                                                              |                                                        |                                                    |                                                        |                                         | bi            |

|                                                                                                                |                                                                   |                                                                                                              |                                                        |                                                    |                                                        |                                         |               |

| Legend:                                                                                                        | :.                                                                |                                                                                                              | L.11                                                   |                                                    |                                                        |                                         |               |

| R = Readable bi                                                                                                |                                                                   |                                                                                                              |                                                        | •                                                  | nented bit, read                                       |                                         |               |

| u = Bit is unchar                                                                                              | nged                                                              | x = Bit is unkr                                                                                              |                                                        | -n/n = Value a                                     | t POR and BO                                           | R/Value at all o                        | other Resets  |

| 1' = Bit is set                                                                                                |                                                                   | '0' = Bit is cle                                                                                             | ared                                                   |                                                    |                                                        |                                         |               |

| oit 7-6                                                                                                        | Unimpleme                                                         | nted: Read as '                                                                                              | 0'                                                     |                                                    |                                                        |                                         |               |

|                                                                                                                | LCxD1S<5:<br>See Table 32                                         | <b>0&gt;:</b> CLCx Data1<br>2-2.                                                                             | Input Selecti                                          | on bits                                            |                                                        |                                         |               |

| EGISTER 32                                                                                                     | -4· CLCx                                                          | SEL1: GENE                                                                                                   |                                                        | ATA 1 SELEO                                        |                                                        | R                                       |               |

| LOISIER 32                                                                                                     | T. OLOA                                                           |                                                                                                              |                                                        |                                                    |                                                        |                                         |               |

| U-0                                                                                                            | U-0                                                               | R/W-x/u                                                                                                      | R/W-x/u                                                | R/W-x/u                                            | R/W-x/u                                                | R/W-x/u                                 | R/W-x/เ       |

|                                                                                                                |                                                                   |                                                                                                              |                                                        | R/W-x/u                                            |                                                        |                                         | R/W-x/u       |

| U-0                                                                                                            |                                                                   |                                                                                                              |                                                        | R/W-x/u                                            | R/W-x/u                                                |                                         |               |

| U-0<br>—<br>Dit 7                                                                                              |                                                                   |                                                                                                              |                                                        | R/W-x/u                                            | R/W-x/u                                                |                                         | R/W-x/u<br>bi |

| U-0<br>— Dit 7<br>Legend:                                                                                      | U-0<br>—                                                          |                                                                                                              | R/W-x/u                                                | R/W-x/u<br>LCxD2                                   | R/W-x/u                                                | R/W-x/u                                 |               |

| U-0<br>—                                                                                                       | U-0<br>—                                                          | R/W-x/u                                                                                                      | R/W-x/u                                                | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0><br>nented bit, read                 | R/W-x/u                                 | bi            |

| U-0<br>—                                                                                                       | U-0<br>—                                                          | R/W-x/u<br>W = Writable                                                                                      | R/W-x/u<br>bit                                         | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0><br>nented bit, read                 | R/W-x/u                                 | bi            |

| U-0<br>—                                                                                                       | U-0<br>—                                                          | R/W-x/u<br>W = Writable<br>x = Bit is unkr                                                                   | R/W-x/u<br>bit                                         | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0><br>nented bit, read                 | R/W-x/u                                 | b             |

| U-0<br>—                                                                                                       | U-0<br>—<br>it<br>nged                                            | R/W-x/u<br>W = Writable<br>x = Bit is unkr                                                                   | R/W-x/u<br>bit<br>nown<br>ared                         | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0><br>nented bit, read                 | R/W-x/u                                 | b             |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable bin<br>u = Bit is unchar<br>1' = Bit is set<br>bit 7-6<br>bit 5-0 | U-0<br>—<br>it<br>nged<br>Unimpleme                               | R/W-x/u<br>W = Writable<br>x = Bit is unkr<br>'0' = Bit is clean<br>nted: Read as '<br>0>: CLCx Data 2       | R/W-x/u<br>bit<br>nown<br>ared                         | R/W-x/u<br>LCxD2<br>U = Unimplen<br>-n/n = Value a | R/W-x/u<br>2S<5:0><br>nented bit, read                 | R/W-x/u                                 | b             |

| U-0<br>—                                                                                                       | U-0<br>—<br>it<br>nged<br>Unimpleme<br>LCxD2S<5:(<br>See Table 32 | R/W-x/u<br>W = Writable<br>x = Bit is unkr<br>'0' = Bit is clean<br>nted: Read as '<br>0>: CLCx Data 2       | R/W-x/u<br>bit<br>nown<br>ared<br>0'<br>2 Input Select | R/W-x/u<br>LCxD2<br>U = Unimplen<br>-n/n = Value a | R/W-x/u<br>2S<5:0><br>hented bit, read<br>t POR and BO | R/W-x/u<br>I as '0'<br>R/Value at all c | bi            |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable bi<br>u = Bit is unchar<br>i1' = Bit is set<br>bit 7-6<br>bit 5-0 | U-0<br>—<br>it<br>nged<br>Unimpleme<br>LCxD2S<5:(<br>See Table 32 | R/W-x/u<br>W = Writable<br>x = Bit is unkr<br>'0' = Bit is cle<br>nted: Read as '<br>0>: CLCx Data 2<br>2-2. | R/W-x/u<br>bit<br>nown<br>ared<br>0'<br>2 Input Select | R/W-x/u<br>LCxD2<br>U = Unimplen<br>-n/n = Value a | R/W-x/u<br>2S<5:0><br>hented bit, read<br>t POR and BO | R/W-x/u<br>I as '0'<br>R/Value at all c | b             |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 7

bit 5-0 LCxD3S<5:0>: CLCx Data 3 Input Selection bits See Table 32-2.

$\ensuremath{\textcircled{}^{\odot}}$  2017 Microchip Technology Inc.

bit 0

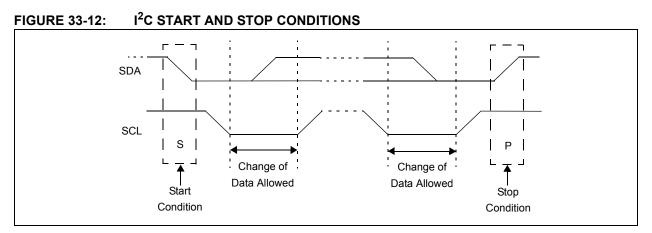

#### 33.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, the clock is stretched, allowing the slave time to change the ACK value before it is sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

### 34.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 34-3 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 34.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 34-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 34.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 34.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 34.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 34.4.1.2 "Clock Polarity"**.

#### 34.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

| Address         | Name     | Bit 7  | Bit 6         | Bit 5 | Bit 4                                                                                                  | Bit 3   | Bit 2     | Bit 1     | Bit 0   | Register<br>on page |  |  |  |

|-----------------|----------|--------|---------------|-------|--------------------------------------------------------------------------------------------------------|---------|-----------|-----------|---------|---------------------|--|--|--|

| 40Ch            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 40Dh            | HIDRVB   | _      | _             | —     | _                                                                                                      | _       | —         | HIDB1     | _       | 232                 |  |  |  |

| 40Eh            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 40Fh            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 410h            | —        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 411h            | —        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 412h            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 413h            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 414h            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 415h            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 416h            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 417h            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 418h            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 419h            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 41Ah            | _        |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 41Bh            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 41Ch            |          |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 41Dh            |          |        |               |       | Unimpl                                                                                                 | emented |           |           |         |                     |  |  |  |

| 41Eh            | _        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 41Fh            | —        |        | Unimplemented |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 48Ch            | SMT1TMRL |        | SMT1TMR       |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 48Dh            | SMT1TMRH |        | SMT1TMR       |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 48Eh            | SMT1TMRU |        | SMT1TMR       |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 48Fh            | SMT1CPRL |        |               |       | С                                                                                                      | PR      |           |           |         | 417                 |  |  |  |

| 490h            | SMT1CPRH |        |               |       | С                                                                                                      | PR      |           |           |         | 417                 |  |  |  |

| 491h            | SMT1CPRU |        |               |       | С                                                                                                      | PR      |           |           |         | 417                 |  |  |  |

| 492h            | SMT1CPWL |        |               |       | С                                                                                                      | PW      |           |           |         | 418                 |  |  |  |

| 493h            | SMT1CPWH |        |               |       | С                                                                                                      | PW      |           |           |         | 418                 |  |  |  |

| 494h            | SMT1CPWU |        |               |       |                                                                                                        | PW      |           |           |         | 418                 |  |  |  |

| 495h            | SMT1PRL  |        |               |       |                                                                                                        | T1PR    |           |           |         | 419                 |  |  |  |

| 496h            | SMT1PRH  |        |               |       |                                                                                                        |         |           |           |         | 419                 |  |  |  |

| 497h            | SMT1PRU  |        |               |       |                                                                                                        |         |           |           |         |                     |  |  |  |

| 497h<br>498h    | SMT1CON0 | EN     |               | STP   | WPOL                                                                                                   | SPOL    | CPOL      | CMT4      | PS<1.0> | 419<br>410          |  |  |  |

| 49011<br>499h   | SMT1CON0 | SMT1GO | REPEAT        |       | STP         WPOL         SPOL         CPOL         SMT1PS<1:0>             MODE<3:0>         MODE<3:0> |         |           |           |         |                     |  |  |  |

|                 |          |        |               | DOT   | _                                                                                                      |         | TS        |           | 48      | 411                 |  |  |  |

| 49Ah            | SMT1STAT | CPRUP  | CPWUP         | RST   |                                                                                                        | _       | 15        | WS        | AS      | 412                 |  |  |  |

| 49Bh            | SMT1CLK  |        |               |       |                                                                                                        |         |           | CSEL<2:0> |         | 413                 |  |  |  |

| 49Ch            | SMT1SIG  | _      |               | _     |                                                                                                        |         | SSEL<4:0> |           |         | 415                 |  |  |  |

| 49Dh<br>Legend: | SMT1WIN  |        |               |       | = unimplemented                                                                                        |         | WSEL<4:0> |           |         | 414                 |  |  |  |

### TABLE 38-1: REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

### TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

| Address | Name | Bit 7         | Bit 6         | Bit 5 | Bit 4   | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Register<br>on page |  |

|---------|------|---------------|---------------|-------|---------|---------|-------|-------|-------|---------------------|--|

| 49Eh    |      |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 49Fh    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 50Ch    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 50Dh    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 50Eh    | _    |               |               |       | Unimple | emented |       |       |       |                     |  |

| 50Fh    | _    | Unimplemented |               |       |         |         |       |       |       |                     |  |

| 510h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 511h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 512h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 513h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 514h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 515h    | _    |               |               |       | Unimple | emented |       |       |       |                     |  |

| 516h    | _    |               |               |       | Unimple | emented |       |       |       |                     |  |

| 517h    | _    | Unimplemented |               |       |         |         |       |       |       |                     |  |

| 518h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 519h    | _    |               | Unimplemented |       |         |         |       |       |       |                     |  |

| 51Ah    | _    | Unimplemented |               |       |         |         |       |       |       |                     |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

| Address   | Name     | Bit 7                                   | Bit 6         | Bit 5 | Bit 4           | Bit 3    | Bit 2    | Bit 1       | Bit 0    | Register<br>on page |  |  |

|-----------|----------|-----------------------------------------|---------------|-------|-----------------|----------|----------|-------------|----------|---------------------|--|--|

| E0Ch      |          |                                         |               |       |                 |          |          |             |          |                     |  |  |

| —<br>E1Fh | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E8Ch      | VB0GPR   |                                         | VB0GPR        |       |                 |          |          |             |          |                     |  |  |

| E8Dh      | VB1GPR   |                                         | VB1GPR        |       |                 |          |          |             |          |                     |  |  |

| E8Eh      | VB2GPR   |                                         | VB2GPR        |       |                 |          |          |             |          |                     |  |  |

| E8Fh      | VB3GPR   |                                         | VB3GPR        |       |                 |          |          |             |          |                     |  |  |

| E90h      | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E91h      | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E92h      | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E93h      | —        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E94h      | _        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E95h      | _        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E96h      | _        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E97h      | —        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E98h      | —        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E99h      | —        |                                         |               |       | Unimpl          | emented  |          |             |          |                     |  |  |

| E9Ah      | —        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E9Bh      | —        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E9Ch      | —        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E9Dh      | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| E9Eh      | _        | Unimplemented                           |               |       |                 |          |          |             |          |                     |  |  |

| E9Fh      | _        |                                         | Unimplemented |       |                 |          |          |             |          |                     |  |  |

| F0Ch      |          | Unimplemented                           |               |       |                 |          |          |             |          |                     |  |  |

| <br>1C9Fh | _        | Unimplemented                           |               |       |                 |          |          |             |          |                     |  |  |

| 1D0Ch     | LCDCON   | LCDEN                                   | SLPEN         | WERR  | CS              |          | LMU      | X<3:0>      |          | 622                 |  |  |

| 1D0Dh     | LCDPS    | WFT                                     | _             | LCDA  | WA              |          | LP       | <3:0>       |          | 623                 |  |  |

| 1D0Eh     | LCDSE0   | SE07                                    | SE06          | SE05  | SE04            | SE03     | SE02     | SE01        | SE00     | 624                 |  |  |

| 1D0Fh     | LCDSE1   | SE15                                    | SE14          | SE13  | SE12            | SE11     | SE10     | SE09        | SE08     | 624                 |  |  |

| 1D10h     | LCDSE2   | SE23                                    | SE22          | SE21  | SE20            | SE19     | SE18     | SE17        | SE16     | 624                 |  |  |

| 1D11h     | LCDSE3   | SE31                                    | SE30          | SE29  | SE28            | SE27     | SE26     | SE25        | SE24     | 624                 |  |  |

| 1D12h     | LCDSE4   | SE39                                    | SE38          | SE37  | SE36            | SE35     | SE34     | SE33        | SE32     | 624                 |  |  |

| 1D13h     | LCDSE5   | SE47                                    | SE46          | SE45  | SE44            | SE43     | SE42     | SE41        | SE40     | 624                 |  |  |

| 1D14h     | LCDVCON1 | LPEN EN5V — — — BIAS<2:0>               |               |       |                 |          |          |             |          | 625                 |  |  |

| 1D15h     | LCDVCON2 |                                         | _             |       |                 | LCDVSRC3 | LCDVSRC2 | LCDVSRC1    | LCDVSRC0 | 626                 |  |  |

| 1D16h     | LCDREF   | _                                       | —             | _     | —               | _        |          | LCDCST<2:0> |          | 628                 |  |  |

| 1D17h     | LCDRL    | LRLAP<1:0> LRLBP<1:0> LCDIRI LRLAT<2:0> |               |       |                 |          |          |             | 627      |                     |  |  |

| 1D18h     | LCDDATA0 | S07C0                                   | S06C0         | S05C0 | S04C0           | S03C0    | S02C0    | S01C0       | S00C0    | 624                 |  |  |

| 1D19h     | LCDDATA1 | S15C0                                   | S14C0         | S13C0 | S12C0           | S11C0    | S10C0    | S09C0       | S08C0    | 624                 |  |  |

| 1D1Ah     | LCDDATA2 | S23C0                                   | S22C0         | S21C0 | S20C0           | S19C0    | S18C0    | S17C0       | S16C0    | 624                 |  |  |

| 1D1Bh     | LCDDATA3 | S31C0                                   | S30C0         | S29C0 | S28C0           | S27C0    | S26C0    | S25C0       | S24C0    | 624                 |  |  |

| 1D1Ch     | LCDDATA4 | S39C0                                   | S38C0         | S37C0 | S36C0           | S35C0    | S34C0    | S33C0       | S32C0    | 624                 |  |  |

| 1D1Dh     | LCDDATA5 | _                                       | _             | S45C0 | S44C0           | S43C0    | S42C0    | S41C0       | S40C0    | 624                 |  |  |

| 1D1Eh     | LCDDATA6 | S07C1                                   | S06C1         | S05C1 | S04C1           | S03C1    | S02C1    | S01C1       | S00C1    | 624                 |  |  |

| 1D1Fh     | LCDDATA7 | S15C1                                   | S14C1         | S13C1 | S12C1           | S11C1    | S10C1    | S09C1       | S08C1    | 624                 |  |  |

| Legend:   |          |                                         |               |       | = unimplemented |          |          |             |          | read as '0'         |  |  |

### TABLE 38-1: REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend:

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note

1:

Unimplemented data memory locations, read as '0'.

#### TABLE 39-4: I/O PORTS

| Param.<br>No.      | Sym.                       | Characteristic                                                                                                       | Min.                     | Тур†                   | Max.                | Units             | Conditions                                                                     |  |  |  |  |

|--------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|---------------------|-------------------|--------------------------------------------------------------------------------|--|--|--|--|

|                    | VIL                        | Input Low Voltage                                                                                                    |                          |                        |                     |                   |                                                                                |  |  |  |  |

|                    |                            | I/O PORT:                                                                                                            |                          |                        |                     |                   |                                                                                |  |  |  |  |

| D300               |                            | with TTL buffer                                                                                                      | —                        | _                      | 0.8                 | V                 | 4.5V ≤ VDD ≤ 5.5V                                                              |  |  |  |  |