Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19155-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F19155/56/75/76/85/86

### TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F19185/86) (CONTINUED)

|                     |                                                |                                               |                     |                                              |                                              |                                          |                                          |       |       |               |               |       |       |       |       | 1     |               |               |       |

|---------------------|------------------------------------------------|-----------------------------------------------|---------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|-------|-------|---------------|---------------|-------|-------|-------|-------|-------|---------------|---------------|-------|

| Basic               | SOSCO                                          | SOSCI                                         | _                   | —                                            | —                                            | —                                        | _                                        | _     | _     | _             | —             | _     | _     | _     | _     | _     | —             | _             | MCLR  |

| dn-Iluq             | Y                                              | Y                                             | Y                   | Y                                            | Y                                            | Y                                        | Y                                        | Υ     | Υ     | Y             | Y             | Υ     | Υ     | Υ     | Υ     | Υ     | Y             | Y             | Υ     |

| High Current        | _                                              | _                                             | _                   | _                                            | _                                            | —                                        | _                                        | _     | _     | _             | —             | _     | —     | _     | _     | _     | _             | —             | _     |

| Interrupt-on-Change | IOCC0                                          | IOCC1                                         | IOCC2               | IOCC3                                        | IOCC4                                        | IOCC6                                    | IOCC7                                    | _     | _     | _             | —             | _     | —     | _     |       | _     | —             | —             | IOCE3 |

| ГСD                 |                                                | _                                             | COM2<br>SEG18       | SEG19                                        | SEG20                                        | SEG22<br>VLCD2                           | SEG23<br>VLCD1                           | SEG24 | SEG25 | COM5<br>SEG26 | COM4<br>SEG27 | SEG28 | SEG29 | SEG30 | SEG31 | SEG32 | COM6<br>SEG33 | COM7<br>SEG34 |       |

| RTCC                | _                                              | _                                             | _                   | _                                            | _                                            | _                                        | _                                        | _     | _     | _             | _             | _     | _     | _     | _     | _     | _             | —             | _     |

| CLC                 | _                                              | _                                             | _                   | —                                            | —                                            | —                                        | -                                        | _     | _     | —             | —             | —     | _     | _     |       | _     | —             | —             | _     |

| EUSART              | _                                              | —                                             | _                   | —                                            | _                                            | TX1 <sup>(1)</sup><br>CK1 <sup>(1)</sup> | RX1 <sup>(1)</sup><br>DT1 <sup>(1)</sup> | _     | _     | —             | _             | —     | _     | _     | _     | —     | _             | —             | _     |

| dssm                |                                                | _                                             | _                   | SCK <sup>(1)</sup><br>SCL <sup>(1,3,4)</sup> | SDI <sup>(1)</sup><br>SDA <sup>(1,3,4)</sup> |                                          | _                                        | _     | _     | _             | _             | _     | _     | _     | _     | _     | _             | _             | _     |

| CWG                 | _                                              | _                                             | _                   | _                                            | _                                            | _                                        | -                                        | _     | _     | _             | —             | —     | _     | _     | _     | —     | —             | _             | _     |

| MWG                 | _                                              | _                                             | _                   | _                                            | _                                            |                                          | _                                        | _     | _     | _             | -             | _     | _     |       | -     |       |               |               | _     |

| ССР                 | _                                              | CCP2 <sup>(1)</sup>                           | CCP1 <sup>(1)</sup> | _                                            | _                                            | _                                        | _                                        | _     | _     | _             | —             | —     | _     | _     | _     | _     | —             | _             | _     |

| Timers/SMT          | T1CKI <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | SMTSIG1 <sup>(1)</sup><br>T4IN <sup>(1)</sup> | _                   | T2IN <sup>(1)</sup>                          | —                                            | _                                        | —                                        | _     | —     | —             | —             | —     | _     | _     | _     | _     | _             | _             | _     |

| DAC                 | _                                              | _                                             | _                   | -                                            |                                              |                                          | _                                        | _     | _     | _             |               | —     | _     |       | _     | _     | _             | _             | _     |

| Zero-Cross Detect   | _                                              | _                                             | _                   | —                                            | —                                            | —                                        | _                                        | _     | —     | —             | —             | —     | —     | —     | —     | —     | —             | _             | _     |

| Comparator          | _                                              | _                                             | _                   | -                                            |                                              |                                          | _                                        | _     | _     | -             |               | —     | _     |       | _     |       |               | _             | _     |

| Reference           | _                                              | _                                             | _                   | _                                            | _                                            | _                                        |                                          | —     | _     | _             | _             | —     | _     | —     | —     | _     | _             | —             | —     |

| ADC                 | _                                              | _                                             | ANC2                | ANC3                                         | ANC4                                         | ANC6                                     | ANC7                                     | AND0  | AND1  | AND2          | AND3          | AND4  | AND5  | AND6  | AND7  | ANE0  | ANE1          | ANE2          | _     |

| 48-Pin TQFP/QFN     | 34                                             | 35                                            | 40                  | 41                                           | 46                                           | 48                                       | 1                                        | 42    | 43    | 44            | 45            | 2     | 3     | 4     | 5     | 27    | 28            | 29            | 20    |

| I/O <sup>(2)</sup>  | RC0                                            | RC1                                           | RC2                 | RC3                                          | RC4                                          | RC6                                      | RC7                                      | RD0   | RD1   | RD2           | RD3           | RD4   | RD5   | RD6   | RD7   | RE0   | RE1           | RE2           | RE3   |

|                     |                                                |                                               |                     |                                              |                                              |                                          |                                          |       |       |               |               |       |       |       |       |       |               |               |       |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

5: These are alternative  $I^2C$  logic levels pins.

6: In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins.

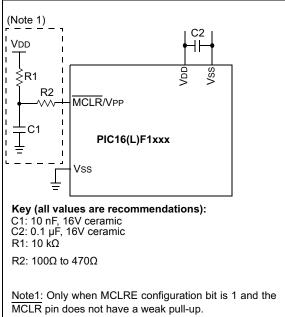

### 2.0 GUIDELINES FOR GETTING STARTED WITH PIC16(L)F19155/56/75/76/85/86 MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC16(L)F19155/56/75/76/85/86 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (when configured for external operation)

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- ICSPCLK/ICSPDAT pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP<sup>™</sup> Pins**")

- OSC1, OSC2, SOSCO and SOSCI pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+ pins are used when external voltage reference for analog modules is implemented

The minimum mandatory connections are shown in Figure 2-1.

### 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and VSS) is required. All VDD and VSS pins must be connected. None can be left floating.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1 μF (100 nF), 10-25V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

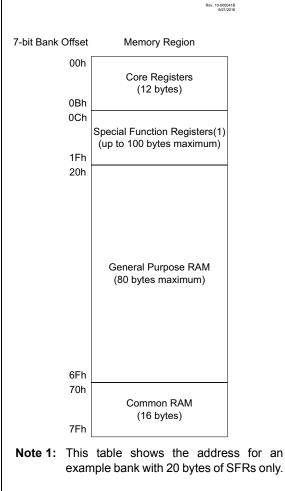

### 4.3 Data Memory Organization

The data memory is partitioned into 64 memory banks with 128 bytes in each bank. Each bank consists of (Section 4.3.6 "Device Memory Maps"):

| FIGURE 4-2: | BANKED MEMORY |

|-------------|---------------|

|             | PARTITIONING  |

|             |               |

- 12 core registers

- Up to 100 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

### 4.3.1 BANK SELECTION

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 4.6** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

### 4.3.2 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 4-3. For detailed information, see Table 4-3.

| TABLE 4-3: | CORE REGISTERS |

|------------|----------------|

|            |                |

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

### 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (refer to Section 37.0 "Instruction Set Summary").

**Note 1:** The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

### REGISTER 4-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                                                                     |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                           |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

### 4.3.3 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes of the data banks 0-59 and 100 bytes of the data banks 60-63, after the core registers.

The SFRs associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

4.3.4 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

| IADLE 4-4: | GENERAL FURF | OSE RAIN SIZE AND D           | ANK LOCATION |                             |

|------------|--------------|-------------------------------|--------------|-----------------------------|

| Bank       |              | , PIC16(L)F19175,<br>_)F19185 |              | PIC16(L)F19176,<br>_)F19186 |

|            | Address      | Size (Bytes)                  | Address      | Size (Bytes)                |

| 0          | 020h-07Fh    | 96                            | 020h-07Fh    | 96                          |

| 1          | 0A0h-0EFh    | 80                            | 0A0h-0EFh    | 80                          |

| 2          | 120h-16Fh    | 80                            | 120h-16Fh    | 80                          |

| 3          | 1A0h-1EFh    | 80                            | 1A0h-1EFh    | 80                          |

| 4          | 220h-26Fh    | 80                            | 220h-26Fh    | 80                          |

| 5          | 2A0h-2EFh    | 80                            | 2A0h-2EFh    | 80                          |

| 6          | 320h-36Fh    | 80                            | 320h-36Fh    | 80                          |

| 7          | 3A0h-3EFh    | 80                            | 3A0h-EFh     | 80                          |

| 8          | 420h-46Fh    | 80                            | 420h-46Fh    | 80                          |

| 9          | 4A0h-4EFh    | 80                            | 4A0h-4EFh    | 80                          |

| 10         | 520h-560h    | 80                            | 520h-560h    | 80                          |

| 11         | 5A0h-5EFh    | 80                            | 5A0h-5EFh    | 80                          |

| 12         | 620h-64Fh    | 48                            | 620h-64Fh    | 80                          |

| 13         |              |                               | 6A0h-6EFh    | 80                          |

| 14         |              |                               | 720h-76Fh    | 80                          |

| 15         |              |                               | 7A0h-7EFh    | 80                          |

| 16         |              |                               | 820h-96Fh    | 80                          |

| 17         |              |                               | 8A0h-8EFh    | 80                          |

| 18         |              |                               | 920h-96Fh    | 80                          |

| 19         |              |                               | 9A0h-9EFh    | 80                          |

| 20         |              |                               | A20h-A6Fh    | 80                          |

| 21         |              |                               | AA0h-AEFh    | 80                          |

| 22         |              |                               | B20h-B6Fh    | 80                          |

| 23         |              |                               | BA0h-BEFh    | 80                          |

| 24         |              |                               | C20h-C6Fh    | 80                          |

| 25         |              |                               | CA0h-CBFh    | 32                          |

### TABLE 4-4: GENERAL PURPOSE RAM SIZE AND BANK LOCATION

**Legend:** = Unimplemented GPR locations

| Address | Name | Bit 7 | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 5 | Bit 4          | Bit 3              | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|--------------------|-------------|-------|-------|-----------------------|----------------------------|

| Bank 15 |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                |                    |             |       |       |                       |                            |

|         |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CPU   | CORE REGISTERS | ; see Table 4-3 fo | r specifics |       |       |                       |                            |

| 78Ch    | _    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | Unimpler       | mented             |             |       |       |                       |                            |

| 78Dh    |      |       | - SMT1MD LCDMD CLC4MD CLC3MD CLC2MD CLC1MD -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                |                    |             |       |       |                       |                            |

| 78Eh    | _    |       | Image: Sector of the sector |       |                |                    |             |       |       |                       |                            |

| 78Fh    | —    |       | UnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplementedUnimplemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                |                    |             |       |       |                       |                            |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

# PIC16(L)F19155/56/75/76/85/86

| REGISTER              | 5-4: CONF                                                                     | GURATION                                                                                                                         | WORD 4: M                                                                              | EMORY                                                                                    |                                 |                     |                     |

|-----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------|---------------------|---------------------|

|                       |                                                                               | R/W-1                                                                                                                            | U-1                                                                                    | R/W-1                                                                                    | R/W-1                           | R/W-1               | R/W-1               |

|                       |                                                                               | LVP                                                                                                                              |                                                                                        | WRTSAF <sup>(1)</sup>                                                                    | WRTD <sup>(1)</sup>             | WRTC <sup>(1)</sup> | WRTB <sup>(1)</sup> |

|                       |                                                                               | bit 13                                                                                                                           | 12                                                                                     | 11                                                                                       | 10                              | 9                   | bit 8               |

| R/W-1                 | U-1                                                                           | U-1                                                                                                                              | R/W-1                                                                                  | R/W-1                                                                                    | R/W-1                           | R/W-1               | R/W-1               |

| WRTAPP <sup>(1)</sup> | 0-1                                                                           | 0-1                                                                                                                              | SAFEN <sup>(1)</sup>                                                                   | BBEN <sup>(1)</sup>                                                                      | BBSIZE2                         | BBSIZE1             |                     |

|                       |                                                                               | _                                                                                                                                |                                                                                        |                                                                                          |                                 |                     | BBSIZE0             |

| bit 7                 | 6                                                                             | 5                                                                                                                                | 4                                                                                      | 3                                                                                        | 2                               | 1                   | bit 0               |

| Legend:               |                                                                               |                                                                                                                                  |                                                                                        |                                                                                          |                                 |                     |                     |

| R = Readable          | ebit P=Pr                                                                     | ogrammable bit                                                                                                                   | x = Bit is                                                                             | unknown                                                                                  | U = Unimpler                    | mented bit, read    | d as '1'            |

| '0' = Bit is cle      | ared '1' = Bi                                                                 | it is set                                                                                                                        | W = Writ                                                                               | able bit                                                                                 | n = Value wh                    | en blank or afte    | er Bulk Erase       |

| bit 13                | 1 = Low voltignored.0 = HV on MThe LVP bit capurpose of thismode, or accie    | tage Programm<br>age programmin<br>ICLR/VPP must<br>annot be writter<br>s rule is to preve<br>dentally elimina<br>ioned (erased) | ng enabled. M<br>be used for pr<br>(to zero) whil<br>ent the user fro<br>ting LVP mode | CLR/VPP pin fu<br>rogramming.<br>le operating froi<br>om dropping ou<br>e from the confi | m the LVP prog<br>t of LVP mode | gramming interf     | ace. The            |

| bit 12                | -                                                                             | ted: Read as '1                                                                                                                  |                                                                                        |                                                                                          |                                 |                     |                     |

| bit 11                |                                                                               | prage Area Flas                                                                                                                  |                                                                                        | rtion hit                                                                                |                                 |                     |                     |

| bit 10                | 0 = SAF write<br>Unimplemente<br>WRTD: Data 1<br>1 = Data EEP<br>0 = Data EEP | ed, if SAF is not<br>EEPROM Write<br>ROM NOT write<br>ROM write-prot                                                             | supported in<br>Protection bit<br>e-protected<br>ected                                 |                                                                                          | ly and only app                 | blicable if SAFE    | <del>.</del> N = 0. |

| bit 9                 | WRTC: Config<br>1 = Configur                                                  | ed if data EEPR<br>guration Register I<br>ration Register I<br>ration Register v                                                 | er Write Protect                                                                       | ction bit<br>tected                                                                      |                                 |                     |                     |

| bit 8                 | 1 = Boot Blo<br>0 = Boot Blo                                                  | Block Write Pro<br>ock NOT write-p<br>ock write-protect<br>le if BBEN = 0.                                                       | rotected                                                                               |                                                                                          |                                 |                     |                     |

| bit 7                 | 1 = Applicati<br>0 = Applicati                                                | plication Block<br>ion Block NOT<br>ion Block write-                                                                             | write-protected<br>protected                                                           |                                                                                          |                                 |                     |                     |

| bit 6-5               |                                                                               | ted: Read as '1                                                                                                                  | •                                                                                      |                                                                                          |                                 |                     |                     |

| bit 4                 | SAFEN: SAF I           1 =         SAF disa           0 =         SAF ena     | abled<br>bled                                                                                                                    |                                                                                        |                                                                                          |                                 |                     |                     |

| bit 3                 | 1 = Boot Blog                                                                 | Block Enable bit<br>ck disabled<br>ck enabled                                                                                    |                                                                                        |                                                                                          |                                 |                     |                     |

| bit 2-0               | BBSIZE is use                                                                 | : Boot Block Si <u>ze</u><br>ed only when Bl<br>n only be writte                                                                 | <b>BEN =</b> 0                                                                         |                                                                                          | N = 0, BBSIZ is                 | s write-protecte    | d.                  |

| Note 1: Bits          |                                                                               | ed as sticky bits. C                                                                                                             |                                                                                        |                                                                                          |                                 |                     |                     |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTD   | RD7     | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     | 241                 |

| TRISD   | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  | 241                 |

| LATD    | LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   | 242                 |

| ANSELD  | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   | 242                 |

| WPUD    | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   | 243                 |

| ODCOND  | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   | 243                 |

| SLRCOND | SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   | 244                 |

| INLVLD  | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 244                 |

### TABLE 14-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

Note 1: Unimplemented, read as '1'.

-n/n = Value at POR and BOR/Value at all other Resets

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |         |         |         |         |         |         |         |

|----------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Legend:                                                              |         |         |         |         |         |         |         |

| bit 7                                                                |         |         |         |         |         |         | bit 0   |

| ODCF7                                                                | ODCF6   | ODCF5   | ODCF4   | ODCF3   | ODCF2   | ODCF1   | ODCF0   |

| R/W-0/0                                                              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

### REGISTER 14-46: ODCONF: PORTF OPEN-DRAIN CONTROL REGISTER

x = Bit is unknown

'0' = Bit is cleared

ODCF<7:0>: PORTF Open-Drain Enable bits

u = Bit is unchanged

'1' = Bit is set

bit 7-0

For RF<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

### REGISTER 14-47: SLRCONF: PORTF SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRF<7:0>:** PORTF Slew Rate Enable bits

For RF<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 14-48: INLVLF: PORTF INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLF<7:0>: PORTF Input Level Select bits

For RF<7:0> pins, respectively

$\ensuremath{\mathtt{1}}$  = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### 23.9 Register Definitions: ZCD Control

### REGISTER 23-1: ZCDCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-q/q          | U-0                                                                                                                                                                            | R-x/x                                                                                                                                                     | R/W-0/0        | U-0            | U-0            | R/W-0/0                           | R/W-0/0      |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|-----------------------------------|--------------|--|--|--|

| SEN              | —                                                                                                                                                                              | OUT                                                                                                                                                       | POL            | —              |                | INTP                              | INTN         |  |  |  |

| bit 7            |                                                                                                                                                                                |                                                                                                                                                           |                |                |                |                                   | bit 0        |  |  |  |

|                  |                                                                                                                                                                                |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

| Legend:          |                                                                                                                                                                                |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

| R = Readable     | le bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                     |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                          | x = Bit is unki                                                                                                                                           | nown           | -n/n = Value a | at POR and BO  | R/Value at all c                  | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                | '0' = Bit is cle                                                                                                                                          | ared           | q = value dep  | ends on Config | guration bits                     |              |  |  |  |

| bit 7            | 1 = Zero-cros                                                                                                                                                                  |                                                                                                                                                           | abled. ZCD pi  |                | •              | and sink currer<br>and TRIS contr |              |  |  |  |

| bit 6            | Unimplemented: Read as '0'                                                                                                                                                     |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

| bit 5            | OUT: Zero-Cr                                                                                                                                                                   | OUT: Zero-Cross Detection Logic Level bit                                                                                                                 |                |                |                |                                   |              |  |  |  |

|                  | POL bit = 1:<br>1 = ZCD pin is sourcing current<br>0 = ZCD pin is sinking current<br><u>POL bit = 0</u> :<br>1 = ZCD pin is sinking current<br>0 = ZCD pin is sourcing current |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

| bit 4            | 1 = ZCD logi                                                                                                                                                                   | ross Detection<br>c output is inve<br>c output is not                                                                                                     | erted          | Polarity bit   |                |                                   |              |  |  |  |

| bit 3-2          | Unimplemen                                                                                                                                                                     | ted: Read as '                                                                                                                                            | 0'             |                |                |                                   |              |  |  |  |

| bit 1            | INTP: Zero-C                                                                                                                                                                   | ross Positive E                                                                                                                                           | Edge Interrupt | Enable bit     |                |                                   |              |  |  |  |

|                  |                                                                                                                                                                                | <ul> <li>1 = ZCDIF bit is set on low-to-high ZCDx_output transition</li> <li>0 = ZCDIF bit is unaffected by low-to-high ZCDx_output transition</li> </ul> |                |                |                |                                   |              |  |  |  |

| bit 0            |                                                                                                                                                                                | ross Negative                                                                                                                                             | -              |                |                |                                   |              |  |  |  |

|                  | <ul> <li>1 = ZCDIF bit is set on high-to-low ZCDx_output transition</li> <li>0 = ZCDIF bit is unaffected by high-to-low ZCDx_output transition</li> </ul>                      |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

|                  |                                                                                                                                                                                |                                                                                                                                                           |                |                |                |                                   |              |  |  |  |

### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on page |

|---------|-------|-------|-------|-------|-------|-------|--------|--------|---------------------|

| PIE3    | RC2IE | TX2IE | RC1IE | TX1IE |       | _     | BCL1IE | SSP1IE | 168                 |

| PIR3    | RC2IF | TX2IF | RC1IF | TX1IF | _     | _     | BCL1IF | SSP1IF | 177                 |

| ZCDxCON | SEN   |       | OUT   | POL   |       | _     | INTP   | INTN   | 349                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

### TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 121                 |

| CONFIG2 | 7:0  | BOREN   | N <1:0> | LPBOREN  |          | _        | _        | PWRTE   | MCLRE   |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

| U-0   | U-0            | U-0 | R/W-x            | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|----------------|-----|------------------|-------|-------|-------|-------|

| —     | — — ALRMHMONTH |     | ALRMLMONTH <3:0> |       |       |       |       |

| bit 7 |                |     |                  |       |       |       | bit 0 |

|       |                |     |                  |       |       |       |       |

### REGISTER 24-12: ALRMMTH: ALARM MONTH CONTROL REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4 ALRMHMONTH: Binary Coded Decimal value of months '10' digit; valid value from 0 to 1

bit 3-0 ALRMLMONTH<3:0>: Binary Coded Decimal value of months '1' digit; valid value from 0 to 9

### REGISTER 24-13: ALRMWD: ALARM WEEKDAY CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x       | R/W-x |

|-------|-----|-----|-----|-----|-------|-------------|-------|

| —     | —   | _   | —   | —   | AL    | RMLWDAY<2:0 | )>    |

| bit 7 |     |     |     |     |       |             | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 ALRMLWDAY<2:0>: Binary Coded Decimal value of weekdays '1' digit; valid values from 0 to 6.

### REGISTER 24-14: ALRMDAY: ALARM DAY CONTROL REGISTER

| U-0   | U-0 | R/W-x         | R/W-x | R/W-x         | R/W-x | R/W-x | R/W-x |

|-------|-----|---------------|-------|---------------|-------|-------|-------|

| —     | —   | ALRMHDAY<1:0> |       | ALRMLDAY<3:0> |       |       |       |

| bit 7 |     |               |       |               | bit 0 |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 ALRMHDAY<1:0>: Binary Coded Decimal value of days '10' digit; valid value from 0 to 3

bit 3-0 ALRMLDAY<3:0>: Binary Coded Decimal value of days '1' digit; valid value from 0 to 9

### 25.0 TIMER0 MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- 8-bit timer/counter with programmable period

- Synchronous or asynchronous operation

- Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- Programmable postscaler

- Operation during Sleep mode

- Interrupt on match or overflow

- Output on I/O pin (via PPS) or to other peripherals

### 25.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

### 25.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

# 25.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is neither directly readable nor writable (see Figure 25-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### 25.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

The value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers