#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19155-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

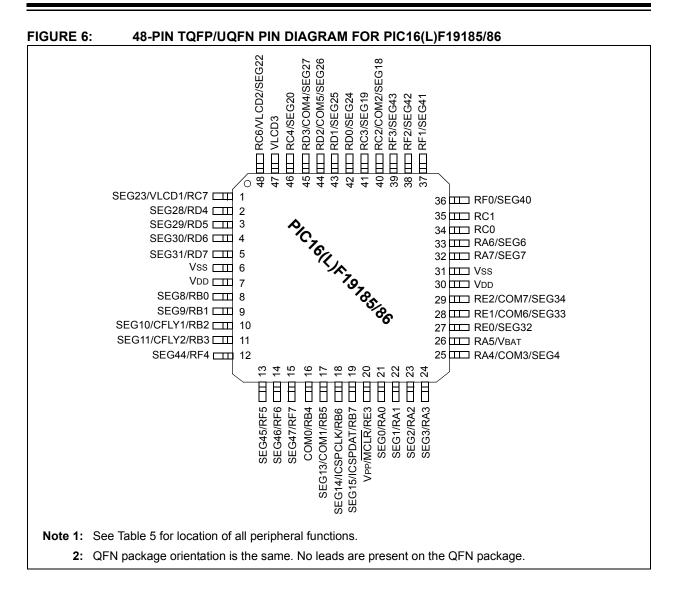

# TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F19185/86) (CONTINUED)

|                     |                                                |                                               |                     |                                              |                                              |                                          |                                          |       |       |               |               |       |       |       |       | 1     |               |               |       |

|---------------------|------------------------------------------------|-----------------------------------------------|---------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|-------|-------|---------------|---------------|-------|-------|-------|-------|-------|---------------|---------------|-------|

| Basic               | SOSCO                                          | SOSCI                                         | _                   | —                                            | —                                            | —                                        | _                                        | _     | _     | _             | —             | _     | _     | _     | _     | _     | —             | _             | MCLR  |

| dn-Iluq             | Y                                              | Y                                             | Y                   | Y                                            | Y                                            | Y                                        | Y                                        | Υ     | Υ     | Y             | Y             | Υ     | Υ     | Υ     | Υ     | Υ     | Y             | Y             | Υ     |

| High Current        | _                                              | _                                             | _                   | _                                            | _                                            | —                                        | _                                        | _     | _     | _             | —             | _     | —     | _     | _     | _     | _             | —             | _     |

| Interrupt-on-Change | IOCC0                                          | IOCC1                                         | IOCC2               | IOCC3                                        | IOCC4                                        | IOCC6                                    | IOCC7                                    | _     | _     | _             | —             | _     | —     | _     |       | _     | —             | —             | IOCE3 |

| ГСD                 |                                                | _                                             | COM2<br>SEG18       | SEG19                                        | SEG20                                        | SEG22<br>VLCD2                           | SEG23<br>VLCD1                           | SEG24 | SEG25 | COM5<br>SEG26 | COM4<br>SEG27 | SEG28 | SEG29 | SEG30 | SEG31 | SEG32 | COM6<br>SEG33 | COM7<br>SEG34 |       |

| RTCC                | _                                              | _                                             | _                   | _                                            | _                                            | _                                        | _                                        | _     | _     | _             | _             | _     | _     | _     | _     | _     | _             | —             | _     |

| CLC                 | _                                              | _                                             | _                   | —                                            | —                                            | —                                        | -                                        | _     | _     | _             | —             | —     | _     | _     |       | _     | —             | —             | _     |

| EUSART              | _                                              | —                                             | _                   | —                                            | _                                            | TX1 <sup>(1)</sup><br>CK1 <sup>(1)</sup> | RX1 <sup>(1)</sup><br>DT1 <sup>(1)</sup> | _     | _     | —             | _             | —     | _     | _     | _     | —     | _             | —             | _     |

| dssm                |                                                | _                                             | _                   | SCK <sup>(1)</sup><br>SCL <sup>(1,3,4)</sup> | SDI <sup>(1)</sup><br>SDA <sup>(1,3,4)</sup> |                                          | _                                        | _     | _     | _             | _             | _     | _     | _     | _     | _     | _             | _             | _     |

| CWG                 | _                                              | _                                             | _                   | _                                            | _                                            | _                                        | -                                        | _     | _     | _             | —             | —     | _     | _     | _     | —     | —             | _             | _     |

| MWG                 | _                                              | _                                             | _                   | _                                            | -                                            |                                          | _                                        | _     | _     | _             | -             | _     | _     |       | -     |       |               |               | _     |

| ССР                 | _                                              | CCP2 <sup>(1)</sup>                           | CCP1 <sup>(1)</sup> | _                                            | _                                            | _                                        | _                                        | _     | _     | _             | —             | —     | _     | _     | _     | _     | —             | _             | _     |

| Timers/SMT          | T1CKI <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | SMTSIG1 <sup>(1)</sup><br>T4IN <sup>(1)</sup> | _                   | T2IN <sup>(1)</sup>                          | —                                            | _                                        | —                                        | _     | —     | —             | —             | —     | _     | _     | _     | _     | _             | _             | _     |

| DAC                 | _                                              | _                                             | _                   | -                                            |                                              |                                          | _                                        | _     | _     | _             |               | —     | _     |       | _     | _     | _             | _             | _     |

| Zero-Cross Detect   | _                                              | _                                             | _                   | —                                            | —                                            | —                                        | _                                        | _     | —     | —             | —             | —     | —     | —     | —     | —     | —             | _             | _     |

| Comparator          | _                                              | _                                             | _                   | -                                            |                                              |                                          | _                                        | _     | _     | -             |               | —     | _     |       | _     |       |               | _             | _     |

| Reference           | _                                              | _                                             | _                   | _                                            | _                                            | _                                        |                                          | —     | _     | _             | _             | —     | _     | —     | —     | _     | _             | —             | —     |

| ADC                 | _                                              | _                                             | ANC2                | ANC3                                         | ANC4                                         | ANC6                                     | ANC7                                     | AND0  | AND1  | AND2          | AND3          | AND4  | AND5  | AND6  | AND7  | ANE0  | ANE1          | ANE2          | _     |

| 48-Pin TQFP/QFN     | 34                                             | 35                                            | 40                  | 41                                           | 46                                           | 48                                       | 1                                        | 42    | 43    | 44            | 45            | 2     | 3     | 4     | 5     | 27    | 28            | 29            | 20    |

| I/O <sup>(2)</sup>  | RC0                                            | RC1                                           | RC2                 | RC3                                          | RC4                                          | RC6                                      | RC7                                      | RD0   | RD1   | RD2           | RD3           | RD4   | RD5   | RD6   | RD7   | RE0   | RE1           | RE2           | RE3   |

|                     |                                                |                                               |                     |                                              |                                              |                                          |                                          |       |       |               |               |       |       |       |       |       |               |               |       |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

5: These are alternative  $I^2C$  logic levels pins.

6: In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins.

# TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F19185/86) (CONTINUED)

| I/O <sup>(2)</sup> | 48-Pin TQFP/QFN | ADC              | Reference | Comparator     | Zero-Cross Detect | DAC | Timers/SMT | ССР          | MWA          | cwe                              | MSSP                     | EUSART                                 | CLC     | RTCC | ГСD   | Interrupt-on-Change | High Current | Pull-up | Basic |

|--------------------|-----------------|------------------|-----------|----------------|-------------------|-----|------------|--------------|--------------|----------------------------------|--------------------------|----------------------------------------|---------|------|-------|---------------------|--------------|---------|-------|

| RF0                | 36              | ANF0             | —         | —              | —                 | _   | _          |              | —            | _                                | -                        | _                                      | _       | —    | SEG40 | _                   | _            | Υ       | —     |

| RF1                | 37              | ANF1             | —         | _              |                   | _   | -          | _            | _            | _                                | —                        | _                                      | _       | —    | SEG41 |                     | _            | Υ       | _     |

| RF2                | 38              | ANF2             | _         | _              | -                 | _   | -          | _            | _            | -                                | —                        | _                                      | _       | -    | SEG42 |                     | _            | Υ       | _     |

| RF3                | 39              | ANF3             | —         | _              |                   | _   | -          | _            | _            | _                                | —                        | _                                      | _       | —    | SEG43 |                     | _            | Υ       | _     |

| RF4                | 12              | ANF4             | _         | _              | -                 | _   | -          | _            | _            | -                                | —                        | _                                      | _       | -    | SEG44 |                     | _            | Υ       | _     |

| RF5                | 13              | ANF5             | —         | _              |                   | _   | -          | _            | _            | _                                | —                        | _                                      | _       | —    | SEG45 |                     | _            | Υ       | _     |

| RF6                | 14              | ANF6             | _         | _              | -                 | _   | -          | _            | _            | -                                | —                        | _                                      | _       | -    | SEG46 |                     | _            | Υ       | _     |

| RF7                | 15              | ANF7             |           | —              | _                 | —   | _          |              | —            | _                                |                          |                                        | —       | -    | SEG47 | _                   |              | Υ       | —     |

| VLCD3              | 47              |                  |           | _              | _                 | —   | _          |              | _            | _                                |                          | -                                      | _       | -    | VLCD3 | _                   |              | Υ       | —     |

| VDD                | 7<br>30         | _                | -         | —              | —                 | _   | _          | _            | _            | —                                | _                        | _                                      | —       | _    | _     | _                   | _            | Y       | Vdd   |

| Vss                | 6<br>31         | _                |           | —              | —                 | —   | —          |              | —            | —                                | _                        |                                        | —       | -    | —     | —                   |              | Y       | Vss   |

| OUT <sup>(2)</sup> | _               | ADGRDA<br>ADGRDB |           | C1OUT<br>C2OUT | _                 | _   | TMR0       | CCP1<br>CCP2 | PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | SDO<br>SCK<br>SCL<br>SDA | TX1<br>DT1<br>CK1<br>TX2<br>DT2<br>CK2 | CLC1OUT | RTCC | _     | _                   | _            | _       | _     |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

**5**: These are alternative I<sup>2</sup>C logic levels pins.

6: In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins.

| Name                                                                                 | Function              | Input<br>Types | Output<br>Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                       |

|--------------------------------------------------------------------------------------|-----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| RB3/C1IN2-/C2IN2-/IOCB3/ANB3/SEG11/SEGCFLY2                                          | RB3                   | TTL/ST         | CMOS/OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | General purpose I/O.                                              |

|                                                                                      | C1IN2-                | AN             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comparator negative input.                                        |

|                                                                                      | C2IN2-                | AN             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comparator negative input.                                        |

|                                                                                      | IOCB3                 | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt-on-change input.                                        |

|                                                                                      | ANB3                  | AN             | AN       LCD Analog output         —       LCD Drive Charge         CMOS/OD       General purpose I         —       ADC Auto-Conver         —       ADC Auto-Conver         —       ADC Channel input         AN       LCD Driver Comm         CMOS/OD       General purpose I         —       ADC Channel input         AN       LCD Driver Comm         CMOS/OD       General purpose I         —       Timer1 Gate input         —       ADC Channel input         —       ADC Channel input         AN       LCD Driver Comm         AN       LCD Driver Comm         AN       LCD Driver Comm         AN       LCD Driver Comm         CMOS/OD       General purpose I         —       EUSART synchro         —       EUSART asynchro         —       Interrupt-on-chang         —       ADC Channel input         AN       LCD Analog output         —       Interrupt-on-chang         —       ADC Channel input         AN       LCD Analog output         —       EUSART synchro         —       EUSART synchro         — | ADC Channel input.                                                |

|                                                                                      | SEG11                 | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCD Analog output.                                                |

|                                                                                      | SEGCFLY2              | AN             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LCD Drive Charge Pump Capacitor Inputs                            |

| RB4/ADCACT <sup>(1)</sup> /IOCB4/ANB4/COM0                                           | RB4                   | TTL/ST         | CMOS/OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | General purpose I/O.                                              |

|                                                                                      | ADCACT <sup>(1)</sup> | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC Auto-Conversion Trigger input                                 |

|                                                                                      | IOCB4                 | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt-on-change input.                                        |

|                                                                                      | ANB4                  | AN             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC Channel input.                                                |

|                                                                                      | COM0                  | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCD Driver Common Outputs.                                        |

| RB5/T1G <sup>(1)</sup> /IOCB5/ANB5/SEG13/COM1                                        | RB5                   | TTL/ST         | CMOS/OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | General purpose I/O.                                              |

|                                                                                      | T1G <sup>(1)</sup>    | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer1 Gate input.                                                |

|                                                                                      | IOCB5                 | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt-on-change input.                                        |

|                                                                                      | ANB5                  | AN             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC Channel input.                                                |

|                                                                                      | SEG13                 | _              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LCD Analog output.                                                |

|                                                                                      | COM1                  | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCD Driver Common Outputs.                                        |

| RB6/CK2 <sup>(3)</sup> /TX2 <sup>(1)</sup> /CLCIN2 <sup>(1)</sup> /IOCB6/ANB6/SEG14/ | RB6                   | TTL/ST         | CMOS/OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | General purpose I/O.                                              |

| ICSPCLK                                                                              | CK2 <sup>(3)</sup>    | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EUSART synchronous clock out                                      |

|                                                                                      | TX2 <sup>(1)</sup>    | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EUSART asynchronous TX data out                                   |

|                                                                                      | CLCIN2 <sup>(1)</sup> | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Configurable Logic Cell source input.                             |

|                                                                                      | IOCB6                 | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt-on-change input.                                        |

|                                                                                      | ANB6                  | AN             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC Channel input.                                                |

|                                                                                      | SEG14                 | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCD Analog output.                                                |

|                                                                                      | ICSPCLK               | ST             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | In-Circuit Serial Programming™ and debuggin<br>clock input.       |

| RB7/DK2 <sup>(3)</sup> /RX2 <sup>(1)</sup> /CLCIN3 <sup>(1)</sup> /IOCB7/ANB7/SEG15/ | RB7                   | TTL/ST         | CMOS/OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | General purpose I/O.                                              |

| DAC1OUT2/ICSPDAT                                                                     | DK2 <sup>(3)</sup>    | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EUSART synchronous data output                                    |

|                                                                                      | RX2 <sup>(1)</sup>    | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EUSART receive input.                                             |

|                                                                                      | CLCIN3 <sup>(1)</sup> | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Configurable Logic Cell source input.                             |

|                                                                                      | IOCB7                 | TTL/ST         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interrupt-on-change input.                                        |

|                                                                                      | ANB7                  | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADC Channel input.                                                |

|                                                                                      | SEG15                 | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCD Analog output.                                                |

|                                                                                      | DAC1OUT2              | _              | AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital-to-Analog Converter output.                               |

|                                                                                      | ICSPDAT               | TTL/ST         | TTL/ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | In-Circuit Serial Programming™ and debuggir<br>data input/output. |

#### TABLE 1-4. PIC16(I) E19185/86 PINOUT DESCRIPTION (CONTINUED)

XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note 1: Refer to Table 14-2 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as 2: described in Table 14-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

HV = High Voltage

# 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM (GPR)

- Common RAM

- Data EEPROM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device         | Program Flash Memory Size (Words) | Last Program Memory Address |

|----------------|-----------------------------------|-----------------------------|

| PIC16(L)F19155 | 8k                                | 1FFFh                       |

| PIC16(L)F19175 | 8k                                | 1FFFh                       |

| PIC16(L)F19185 | 8k                                | 1FFFh                       |

| PIC16(L)F19156 | 16k                               | 3FFFh                       |

| PIC16(L)F19176 | 16k                               | 3FFFh                       |

| PIC16(L)F19186 | 16k                               | 3FFFh                       |

# 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing  $32K \times 14$  program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

| Address | Name     | Bit 7  | Bit 6 | Bit 5 | Bit 4          | Bit 3                | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|--------|-------|-------|----------------|----------------------|------------|-------|-------|-----------------------|----------------------------|

| Bank 20 |          |        |       |       |                |                      |            |       |       |                       |                            |

|         |          |        |       | CPU   | CORE REGISTERS | 6; see Table 4-3 for | rspecifics |       |       |                       |                            |

| A0Ch    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A0Dh    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A0Eh    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A0Fh    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A10h    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A11h    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A12h    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A13h    | _        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A14h    | —        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A15h    | —        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A16h    | —        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A17h    | —        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A18h    | —        |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A19h    | RC2REG   |        |       |       | RC2F           | REG                  |            |       |       | 0000 0000             | 0000 0000                  |

| A1Ah    | TX2REG   |        |       |       | TX2F           | REG                  |            |       |       | 0000 0000             | 0000 000                   |

| A1Bh    | SP2BRGL  |        |       |       | SP2B           | RGL                  |            |       |       | 0000 0000             | 0000 0000                  |

| A1Ch    | SP2BRGH  |        |       |       | SP2B           | RGH                  |            |       |       | 0000 0000             | 0000 000                   |

| A1Dh    | RC2STA   | SPEN   | RX9   | SREN  | CREN           | ADDEN                | FERR       | OERR  | RX9D  | 0000 0000             | 0000 000                   |

| A1Eh    | TX2STA   | CSRC   | TX9   | TXEN  | SYNC           | SENDB                | BRGH       | TRMT  | TX9D  | 0000 0010             | 0000 001                   |

| A1Fh    | BAUD2CON | ABDOVF | RCIDL | _     | SCKP           | BRG16                | _          | WUE   | ABDEN | 01-0 0-00             | 01-0 0-0                   |

# TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

# 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

## 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

# 5.3.2 DATA MEMORY PROTECTION

The entire data EEPROM is protected from external reads and writes by the WRTD bit in the Configuration Words. When WRTD = 0, external reads and writes of EEPROM memory are inhibited and a read will return all '0's. The CPU can continue to read and write EEPROM memory, regardless of the protection bit settings.

# 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

# 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.4.7 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F191XX Memory Programming Specification"* (DS40001880).

# 5.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

# 5.7 Register Definitions: Device and Revision

# REGISTER 5-6: DEVID: DEVICE ID REGISTER

|         |      | R      | R   | R     | R      | R | R     |

|---------|------|--------|-----|-------|--------|---|-------|

|         |      |        |     | DEV<  | :13:8> |   |       |

|         |      | bit 13 |     |       |        |   | bit 8 |

|         |      |        |     |       |        |   |       |

| R       | R    | R      | R   | R     | R      | R | R     |

|         |      |        | DEV | <7:0> |        |   |       |

| bit 7   |      |        |     |       |        |   | bit 0 |

|         |      |        |     |       |        |   |       |

| Legend: |      |        |     |       |        |   |       |

|         | 1.11 |        |     |       |        |   |       |

R = Readable bit '1' = Bit is set

et '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device          |    | D    | EVID< | 13:0>` | Values  |

|-----------------|----|------|-------|--------|---------|

| PIC16F19155/56  | 11 | 0000 | 1001  | 1110   | (309Eh) |

| PIC16LF19155/56 | 11 | 0000 | 1001  | 1111   | (309Fh) |

| PIC16F19175/76  | 11 | 0000 | 1010  | 0000   | (30A0h) |

| PIC16LF19175/76 | 11 | 0000 | 1010  | 0001   | (30A1h) |

| PIC16F19185/86  | 11 | 0000 | 1010  | 0010   | (30A2h) |

| PIC16LF19185/86 | 11 | 0000 | 1010  | 0011   | (30A3h) |

# 9.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use an internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 9.3 "Clock Switching" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

# 9.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ<2:0> bits of the OSCFRQ register.

The MFINTOSC is an internal clock source within the HFINTOSC that provides two (500 kHz, 32 kHz) constant clock outputs. These constant clock outputs are available for selection to various peripherals, internally.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

## 9.2.2.2 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 9-7).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WWDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 9.2.2.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.