#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19155t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name     | Bit 7  | Bit 6           | Bit 5 | Bit 4          | Bit 3               | Bit 2     | Bit 1     | Bit 0   | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|----------|--------|-----------------|-------|----------------|---------------------|-----------|-----------|---------|-----------------------|----------------------------|

| Bank 9  |          |        |                 |       |                |                     |           |           |         |                       |                            |

|         |          |        |                 | CPU   | CORE REGISTERS | : see Table 4-3 for | specifics |           |         |                       |                            |

|         | 1        |        |                 |       |                | ,                   |           |           |         | -                     | 1                          |

| 48Ch    | SMT1TMRL |        |                 |       | SMT1           | ſMR                 |           |           |         | 0000 0000             | 0000 0000                  |

| 48Dh    | SMT1TMRH |        |                 |       | SMT1           | ſMR                 |           |           |         | 0000 0000             | 0000 0000                  |

| 48Eh    | SMT1TMRU |        |                 |       | SMT1           | ſMR                 |           |           |         | 0000 0000             | 0000 0000                  |

| 48Fh    | SMT1CPRL |        |                 |       | CPI            | R                   |           |           |         | xxxx xxxx             | XXXX XXXX                  |

| 490h    | SMT1CPRH |        |                 |       | CPI            | R                   |           |           |         | xxxx xxxx             | XXXX XXXX                  |

| 491h    | SMT1CPRU |        |                 |       | CPI            | R                   |           |           |         | xxxx xxxx             | xxxx xxxx                  |

| 492h    | SMT1CPWL |        |                 |       | CP\            | N                   |           |           |         | xxxx xxxx             | xxxx xxxx                  |

| 493h    | SMT1CPWH |        |                 |       | CP\            | N                   |           |           |         | xxxx xxxx             | xxxx xxxx                  |

| 494h    | SMT1CPWU |        |                 |       | CP\            | N                   |           |           |         | xxxx xxxx             | xxxx xxxx                  |

| 495h    | SMT1PRL  |        |                 |       | SMT1           | PR                  |           |           |         | 1111 1111             | 1111 1111                  |

| 496h    | SMT1PRH  |        |                 |       | SMT1           | PR                  |           |           |         | 1111 1111             | 1111 1111                  |

| 497h    | SMT1PRU  |        |                 |       | SMT1           | PR                  |           |           |         | 1111 1111             | 1111 1111                  |

| 498h    | SMT1CON0 | EN     | —               | STP   | WPOL           | SPOL                | CPOL      | SMT1      | PS<1:0> | 0-00 0000             | 0-00 0000                  |

| 499h    | SMT1CON1 | SMT1GO | REPEAT          | _     | _              |                     | MOD       | E<3:0>    |         | 00 0000               | 00 0000                    |

| 49Ah    | SMT1STAT | CPRUP  | CPWUP           | RST   | _              | _                   | TS        | WS        | AS      | 000000                | 000000                     |

| 49Bh    | SMT1CLK  | —      | —               |       | —              | —                   |           | CSEL<2:0> |         | 0000 0000             | 0000 0000                  |

| 49Ch    | SMT1SIG  | —      | —               |       |                | SSEL<4:0>           |           |           |         |                       | 0000 0000                  |

| 49Dh    | SMT1WIN  | —      | _               | _     | — WSEL<4:0>    |                     |           |           |         |                       | 0000 0000                  |

| 49Eh    |          |        |                 |       | Unimpler       | nented              |           |           |         |                       |                            |

| 49Fh    | _        |        | — Unimplemented |       |                |                     |           |           |         |                       |                            |

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, g = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

#### 8.2 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 8.3 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

#### TABLE 8-1: BOR OPERATING MODES

#### 8.3.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 8.3.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | х      | Х           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |

| 1.0        |        | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |

| 10         | X      | Sleep       | Disabled | Waits for BOR Reset release                                         |

| 0.1        | 1      | х           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |

| 01         | 0      | х           | Disabled | Paging immediately (POPDDY =)                                       |

| 00         | Х      | х           | Disabled | Begins immediately (BORRDY = $x$ )                                  |

**Note 1:** In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

# PIC16(L)F19155/56/75/76/85/86

| R-q/q            | R-q/q          | R-q/q                                                          | R-q/q   | R-q/q                   | R-q/q               | U-0               | R-q/q  |

|------------------|----------------|----------------------------------------------------------------|---------|-------------------------|---------------------|-------------------|--------|

| EXTOR            | HFOR           | MFOR                                                           | LFOR    | SOR                     | ADOR                | _                 | PLLR   |

| bit 7            |                |                                                                |         |                         | · · · · · ·         |                   | bit    |

| Legend:          |                |                                                                |         |                         |                     |                   |        |

| R = Readable b   | bit            | W = Writable b                                                 | t       | U = Unimplem            | ented bit, read as  | '0'               |        |

| u = Bit is uncha | inged          | x = Bit is unkno                                               | wn      | -n/n = Value at         | POR and BOR/Va      | alue at all other | Resets |

| '1' = Bit is set |                | '0' = Bit is clear                                             | ed      |                         |                     |                   |        |

| bit 7            | 1 = The osci   | DSC (external) Os<br>Ilator is ready to<br>Ilator is not enab  | be used | bit<br>ready to be used | d.                  |                   |        |

| bit 6            | 1 = The osci   | OSC Oscillator R<br>llator is ready to<br>llator is not enab   | be used | ready to be used        | d.                  |                   |        |

| bit 5            | 1 = The oscill | OSC Oscillator F<br>ator is ready to b<br>ator is not enable   | e used  | ready to be used        |                     |                   |        |

| bit 4            | 1 = The osci   | DSC Oscillator Re<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d.                  |                   |        |

| bit 3            | 1 = The osci   | ary (Timer1) Osci<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d.                  |                   |        |

| bit 2            | 1 = The osci   | C Oscillator Read<br>llator is ready to<br>llator is not enabl | be used | ready to be used        | d                   |                   |        |

| bit 1            | Unimplemente   | ed: Read as '0'                                                |         |                         |                     |                   |        |

| bit 0            |                | is ready to be us                                              |         | ut source is not re     | eady, or the PLL is | not locked.       |        |

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|-----|---------|

| —     | —   | TMR0IE  | IOCIE   | —   | —   | —   | INTE    |

| bit 7 |     |         |         |     |     |     | bit 0   |

|       |     |         |         |     |     |     |         |

### REGISTER 10-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                               |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 5   | <ul> <li>TMR0IE: Timer0 Overflow Interrupt Enable bit</li> <li>1 = Enables the Timer0 interrupt</li> <li>0 = Disables the Timer0 interrupt</li> </ul>                    |  |  |  |  |  |  |

| bit 4   | <ul> <li>IOCIE: Interrupt-on-Change Interrupt Enable bit</li> <li>1 = Enables the IOC change interrupt</li> <li>0 = Disables the IOC change interrupt</li> </ul>         |  |  |  |  |  |  |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                               |  |  |  |  |  |  |

| bit 0   | <ul> <li>INTE: INT External Interrupt Flag bit<sup>(1)</sup></li> <li>1 = Enables the INT external interrupt</li> <li>0 = Disables the INT external interrupt</li> </ul> |  |  |  |  |  |  |

#### Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).

| Note: | Bit PEIE of the INTCON register must be      |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | set to enable any peripheral interrupt       |  |  |  |  |  |  |  |

|       | controlled by PIE1-PIE8. Interrupt           |  |  |  |  |  |  |  |

|       | sources controlled by the PIE0 register do   |  |  |  |  |  |  |  |

|       | not require PEIE to be set in order to allow |  |  |  |  |  |  |  |

|       | interrupt vectoring (when GIE is set).       |  |  |  |  |  |  |  |

| U-0            | R/W-0/0            | U-0               | U-0            | U-0             | U-0              | R/W-0/0          | R/W-0/0     |

|----------------|--------------------|-------------------|----------------|-----------------|------------------|------------------|-------------|

| _              | ZCDIE              |                   | _              |                 |                  | C2IE             | C1IE        |

| bit 7          | ·                  |                   |                | ·               |                  |                  | bit 0       |

|                |                    |                   |                |                 |                  |                  |             |

| Legend:        |                    |                   |                |                 |                  |                  |             |

| R = Readal     | ole bit            | W = Writable      | bit            | U = Unimpler    | mented bit, read | l as '0'         |             |

| u = Bit is ur  | nchanged           | x = Bit is unkr   | iown           | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is s | et                 | '0' = Bit is clea | ared           |                 |                  |                  |             |

|                |                    |                   |                |                 |                  |                  |             |

| bit 7          | Unimpleme          | nted: Read as '   | )'             |                 |                  |                  |             |

| bit 6          | ZCDIE: Zero        | o-Cross Detectio  | n (ZCD) Inter  | rupt Enable bit |                  |                  |             |

|                | 1 = Enables        | s the ZCD interru | ıpt            |                 |                  |                  |             |

|                | 0 = Disables       | s the ZCD interr  | upt            |                 |                  |                  |             |

| bit 5-2        | Unimpleme          | nted: Read as '   | )'             |                 |                  |                  |             |

| bit 1          | C2IE: Comp         | arator C2 Interru | upt Enable bit |                 |                  |                  |             |

|                |                    | the Comparato     |                |                 |                  |                  |             |

|                | 0 = Disables       | s the Comparato   | or C2 interrup | t               |                  |                  |             |

| bit 0          | C1IE: Comp         | arator C1 Interru | ipt Enable bit |                 |                  |                  |             |

|                | 1 = Enables        | the Comparato     | r C1 interrupt |                 |                  |                  |             |

|                | 0 = Disables       | s the Comparato   | or C1 interrup | t               |                  |                  |             |

|                |                    |                   |                |                 |                  |                  |             |

| Note:          | Bit PEIE of the IN | NTCON register    | must be        |                 |                  |                  |             |

|                | set to enable a    |                   |                |                 |                  |                  |             |

|                | controlled by regi |                   |                |                 |                  |                  |             |

### REGISTER 10-4: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

# 12.6 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the OST, if enabled, completes. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

#### TABLE 12-2: WWDT CLEARING CONDITIONS

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 4.3.2.1 "STATUS Register" for more information.

| Conditions                                       | WWDT       |

|--------------------------------------------------|------------|

| WDTE<1:0> = 00                                   |            |

| WDTE<1:0> = 01 and SWDTEN = 0                    |            |

| WDTE<1:0> = 10 and enter Sleep                   | Cleared    |

| CLRWDT Command                                   | Cleared    |

| Oscillator Fail Detected                         |            |

| Exit Sleep + System Clock = SOSC, EXTOSC, INTOSC |            |

| Change INTOSC divider (IRCF bits)                | Unaffected |

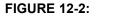

#### WINDOW PERIOD AND DELAY

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 222                 |

| TRISA   | TRISA7  | TRISA6  | (1)     | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 222                 |

| LATA    | LATA7   | LATA6   | —       | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 223                 |

| ANSELA  | ANSA7   | ANSA6   | —       | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 223                 |

| WPUA    | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 224                 |

| ODCONA  | ODCA7   | ODCA6   | —       | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 224                 |

| SLRCONA | SLRA7   | SLRA6   | —       | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 225                 |

| INLVLA  | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 225                 |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** Unimplemented, read as '1'.

-n/n = Value at POR and BOR/Value at all other Resets

| R = Readable | bit     | W = Writable | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |

|--------------|---------|--------------|---------|------------------------------------|---------|---------|---------|--|

| Legend:      |         |              |         |                                    |         |         |         |  |

| bit 7        |         |              |         |                                    |         |         | bit 0   |  |

| ODCF7        | ODCF6   | ODCF5        | ODCF4   | ODCF3                              | ODCF2   | ODCF1   | ODCF0   |  |

| R/W-0/0      | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

#### REGISTER 14-46: ODCONF: PORTF OPEN-DRAIN CONTROL REGISTER

x = Bit is unknown

'0' = Bit is cleared

ODCF<7:0>: PORTF Open-Drain Enable bits

u = Bit is unchanged

'1' = Bit is set

bit 7-0

For RF<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 14-47: SLRCONF: PORTF SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRF<7:0>:** PORTF Slew Rate Enable bits

For RF<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 14-48: INLVLF: PORTF INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLF<7:0>: PORTF Input Level Select bits

For RF<7:0> pins, respectively

$\ensuremath{\mathtt{1}}$  = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

#### 19.1.5 INTERRUPTS

The ADC module allows the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIEx register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all these bits are set, the PC will jump to the Interrupt Service Routine.

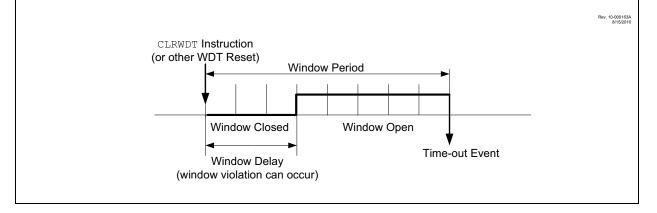

#### 19.1.6 RESULT FORMATTING

The 12-bit ADC conversion result can be supplied in two formats, left justified or right justified. The FM bits of the ADCON0 register controls the output format.

Figure 19-3 shows the two output formats.

Writes to the ADRES register pair are always right justified regardless of the selected format mode. Therefore, data read after writing to ADRES when ADFRM0 = 0 will be shifted left four places.

#### FIGURE 19-3: 12-BIT ADC CONVERSION RESULT FORMAT

# TABLE 19-2: COMPUTATION MODES

|                    |      | Bit Clear Conditions                         | Value after Trigg                                                            | Value after Trigger completion                          |                                                                                                                                                             | Threshold Operations |                   |              | Value at ADTIF Interrupt |       |  |

|--------------------|------|----------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|--------------|--------------------------|-------|--|

| Mode               | ADMD | ACC and CNT                                  | ACC                                                                          | CNT                                                     | Retrigger                                                                                                                                                   | Threshold<br>Test    | Interrupt         | OV           | FLTR                     | CNT   |  |

| Basic              | 0    | ADACLR = 1                                   | Unchanged                                                                    | Unchanged                                               | No                                                                                                                                                          | Every<br>Sample      | If threshold=true | N/A          | N/A                      | count |  |

| Accumulate         | 1    | ADACLR = 1                                   | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT,<br>otherwise: CNT+1                 | No                                                                                                                                                          | Every<br>Sample      | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup>   | count |  |

| Average            | 2    | ADACLR = 1 or CNT>=RPT<br>at GO or retrigger | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT,<br>otherwise: CNT+1                 | No                                                                                                                                                          | lf<br>CNT>=RPT       | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup>   |       |  |

| Burst<br>Average   | 3    | ADACLR = 1 or GO set or<br>retrigger         | Each repetition: same as<br>Average<br>End with sum of all<br>samples        | Each repetition: same as<br>Average<br>End with CNT=RPT | Repeat while<br>CNT <rpt< td=""><td>lf<br/>CNT&gt;=RPT</td><td>If threshold=true</td><td>ACC Overflow</td><td>ACC/2<sup>ADCRS</sup></td><td>RPT</td></rpt<> | lf<br>CNT>=RPT       | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup>   | RPT   |  |

| Low-pass<br>Filter | 4    | ADACLR = 1                                   | S+ACC-ACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ACC-ACC/2 <sup>ADCRS</sup> | Count up, stop counting<br>when CNT = 0xFF              | No                                                                                                                                                          | lf<br>CNT>=RPT       | If threshold=true | ACC Overflow | Filtered Value           | count |  |

PIC16(L)F19155/56/75/76/85/86

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = PREV and S2 = ADRES.

#### REGISTER 19-24: ADACCU: ADC ACCUMULATOR REGISTER UPPER

| U-0             | U-0                               | U-0 | U-0 | U-0          | U-0              | R/W-x/x  | R/W-x/x |

|-----------------|-----------------------------------|-----|-----|--------------|------------------|----------|---------|

| —               | —                                 | —   | —   | —            | —                | ACC<     | 17:16>  |

| bit 7           |                                   |     | •   |              |                  |          | bit 0   |

|                 |                                   |     |     |              |                  |          |         |

| Legend:         |                                   |     |     |              |                  |          |         |

| R = Readable bi | R = Readable bit W = Writable bit |     |     | U = Unimpler | nented bit, read | l as '0' |         |

| R – Reauable bil     |                      | 0 – Onimplemented bit, read as 0                      |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ACC<17:16>: ADC Accumulator MSB. Upper two bits of accumulator value. See Table 19-2 for more details.

#### REGISTER 19-25: ADACCH: ADC ACCUMULATOR REGISTER HIGH

| R/W-x/x   | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| ACC<15:8> |         |         |         |         |         |         |         |

| bit 7     |         |         |         |         |         |         | bit 0   |

|           |         |         |         |         |         |         |         |

|           |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: ADC Accumulator middle bits. Middle eight bits of accumulator value. See Table 19-2 for more details.

#### REGISTER 19-26: ADACCL: ADC ACCUMULATOR REGISTER LOW

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ACC<    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Logond  |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 ACC<7:0>: ADC Accumulator LSB. Lower eight bits of accumulator value. See Table 19-2 for more details.

© 2017 Microchip Technology Inc.

| R/W-0/0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0 |

|---------|-----|-----|-----|-----|-----|-----|-------|

| CPON    |     | —   | —   | _   | _   | _   | CPRDY |

| bit 7   |     | •   |     |     |     |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

## REGISTER 19-36: ADCP: ADC CHARGE PUMP CONTROL REGISTER

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS= Hardware set                                      |

|                      |                      |                                                       |

| bit 7   | <b>CPON</b> : Charge Pump On Control bit<br>1 = Charge Pump On when requested by the ADC<br>0 = Charge Pump Off    |

|---------|--------------------------------------------------------------------------------------------------------------------|

| bit 6-1 | Unimplemented: Read as '0'                                                                                         |

| bit 0   | CPRDY: Charge Pump Ready Status bit<br>1 = Charge Pump is ready<br>0 = Charge Pump is not ready (or never started) |

#### 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| FIGURE 27-5: | HARDWARE GATE MODE TIMING DIAGRAM ( | (MODE = 00001) |  |

|--------------|-------------------------------------|----------------|--|

|              |                                     |                |  |

|                                 | Rev. 10-000 1988<br>5030201 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| TMRx_clk                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| TMRx_ers                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TMRx                            | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 1$ |  |

| TMRx_postscaled                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

# PIC16(L)F19155/56/75/76/85/86

#### REGISTER 29-2: CCPxCAP: CAPTURE INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x  | R/W-0/x |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | —   | —   | —   | —   |         | CTS<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

#### Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

|----------------------|----------------------|------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 CTS<2:0>: Capture Trigger Input Selection bits

| CTS  | CCP1.capture | CCP2.capture |  |  |  |  |  |

|------|--------------|--------------|--|--|--|--|--|

| 1000 | RTCC_s       | econds       |  |  |  |  |  |

| 0111 | LC4_         | LC4_out      |  |  |  |  |  |

| 0110 | LC3_         | LC3_out      |  |  |  |  |  |

| 0101 | LC2_         | LC2_out      |  |  |  |  |  |

| 0100 | LC1_         | out          |  |  |  |  |  |

| 0011 | IOC_int      | errupt       |  |  |  |  |  |

| 0010 | C20          | UT           |  |  |  |  |  |

| 0001 | C10          | C10UT        |  |  |  |  |  |

| 0000 | CCP1PPS      | CCP2PPS      |  |  |  |  |  |

#### REGISTER 29-3: CCPRxL REGISTER: CCPx REGISTER LOW BYTE

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|------------|---------|---------|---------|---------|---------|---------|---------|

| CCPRx<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

CCPxMODE = Capture mode

CCPRxL<7:0>: Capture value of TMR1L

CCPxMODE = Compare mode

CCPRxL<7:0>: LS Byte compared to TMR1L

CCPxMODE = PWM modes when CCPxFMT = 0:

CCPRxL<7:0>: Pulse-width Least Significant eight bits

CCPxMODE = PWM modes when CCPxFMT = 1:

CCPxxL<7:6>: Pulse-width Least Significant two bits

CCPRxL<7:6>: Not used.

© 2017 Microchip Technology Inc.

bit 7-0

| Name     | Bit 7                                        | Bit 6   | Bit 5     | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------------------------------------------|---------|-----------|---------------|---------|---------|---------|---------|---------------------|

| T2CON    | ON                                           |         | CKPS<2:0> |               |         | OUTP    | S<3:0>  |         | 404                 |

| T2TMR    | Holding Register for the 8-bit TMR2 Register |         |           |               |         |         | 384*    |         |                     |

| T2PR     | TMR2 Period Register                         |         |           |               |         |         | 384*    |         |                     |

| RxyPPS   | —                                            | —       | —         | - RxyPPS<4:0> |         |         |         |         | 265                 |

| CWG1ISM  | —                                            | _       | _         | — — IS<3:0>   |         |         |         |         | 492                 |

| CLCxSELy | —                                            | _       |           |               | LCxDyS  | <5:0>   |         |         | 503                 |

| TRISA    | TRISA7                                       | TRISA6  | TRISA5    | TRISA4        | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 222                 |

| TRISC    | TRISC7                                       | TRISC6  | TRISC5    | TRISC4        | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 235                 |

| PWM3CON  | PWM3EN                                       | _       | PWM3OUT   | PWM3POL       | —       | —       | _       | —       |                     |

| PWM4CON  | PWM4EN                                       | _       | PWM4OUT   | PWM4POL       | —       | —       | _       | —       |                     |

| PWM3DCL  | PWM3DC1                                      | PWM3DC0 | _         | _             | _       | _       | _       | _       |                     |

| PWM3DCH  | PWM3DC9                                      | PWM3DC8 | PWM3DC7   | PWM3DC6       | PWM3DC5 | PWM3DC4 | PWM3DC3 | PWM3DC2 |                     |

| PWM4DCL  | PWM4DC1                                      | PWM4DC0 | —         | —             | —       | —       | —       | —       |                     |

| PWM4DCH  | PWM4DC9                                      | PWM4DC8 | PWM4DC7   | PWM4DC6       | PWM4DC5 | PWM4DC4 | PWM4DC3 | PWM4DC2 |                     |

#### TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

\*Page provides register information.

| KEGISTER 51-3              |                                                                                                                                                        |                                                            |                 |                           |                 |                 |              |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|---------------------------|-----------------|-----------------|--------------|--|

| R/W/HS-0/0                 | R/W-0/0                                                                                                                                                | R/W-0/0                                                    | R/W-1/1         | R/W-0/0                   | R/W-1/1         | U-0             | U-0          |  |

| SHUTDOWN <sup>(1, 2)</sup> | REN                                                                                                                                                    | LSBI                                                       | D<1:0>          | LSAC                      | <1:0>           |                 | _            |  |

| bit 7                      |                                                                                                                                                        |                                                            |                 |                           |                 |                 | bit (        |  |

|                            |                                                                                                                                                        |                                                            |                 |                           |                 |                 |              |  |

| Legend:                    |                                                                                                                                                        |                                                            |                 |                           |                 |                 |              |  |

| HC = Bit is cleare         | d by hardware                                                                                                                                          |                                                            |                 | HS = Bit is se            | et by hardware  | 9               |              |  |

| R = Readable bit           |                                                                                                                                                        | W = Writable                                               | e bit           | U = Unimplei              | mented bit, rea | ad as 'O'       |              |  |

| u = Bit is unchang         | ged                                                                                                                                                    | x = Bit is unk                                             | nown            | -n/n = Value a            | at POR and BO   | OR/Value at all | other Resets |  |

| '1' = Bit is set           |                                                                                                                                                        | '0' = Bit is cle                                           | eared           | q = Value de              | pends on conc   | dition          |              |  |

| L:1 7                      |                                                                                                                                                        |                                                            |                 | hua hit(1, 2)             |                 |                 |              |  |

| bit 7                      |                                                                                                                                                        | Shutdown sta                                               | own Event Stat  | tus bit <sup>(1, -)</sup> |                 |                 |              |  |

|                            |                                                                                                                                                        |                                                            | ent has occurre | ed                        |                 |                 |              |  |

| bit 6                      | <b>REN:</b> Auto-Restart Enable bit                                                                                                                    |                                                            |                 |                           |                 |                 |              |  |

|                            | 1 = Auto-restart enabled                                                                                                                               |                                                            |                 |                           |                 |                 |              |  |

|                            | 0 = Auto-res                                                                                                                                           | tart disabled                                              |                 |                           |                 |                 |              |  |

| bit 5-4                    | LSBD<1:0>:                                                                                                                                             | SBD<1:0>: CWG1B and CWG1D Auto-Shutdown State Control bits |                 |                           |                 |                 |              |  |

|                            | 11 =A logic '1' is placed on CWG1B/D when an auto-shutdown event is present                                                                            |                                                            |                 |                           |                 |                 |              |  |

|                            | 10 =A logic '0' is placed on CWG1B/D when an auto-shutdown event is present<br>01 =Pin is tri-stated on CWG1B/D when an auto-shutdown event is present |                                                            |                 |                           |                 |                 |              |  |

|                            | 00 = The inactive state of the pin, including polarity, is placed on CWG1B/D after the required dead-                                                  |                                                            |                 |                           |                 |                 |              |  |

|                            | band in                                                                                                                                                | terval                                                     |                 |                           |                 |                 | ·            |  |

| bit 3-2                    | LSAC<1:0>:                                                                                                                                             | CWG1A and                                                  | CWG1C Auto      | -Shutdown Sta             | te Control bits |                 |              |  |

|                            | 11 =A logic '1' is placed on CWG1A/C when an auto-shutdown event is present                                                                            |                                                            |                 |                           |                 |                 |              |  |

|                            | 10 =A logic '0' is placed on CWG1A/C when an auto-shutdown event is present<br>01 =Pin is tri-stated on CWG1A/C when an auto-shutdown event is present |                                                            |                 |                           |                 |                 |              |  |

|                            | 00 = The inactive state of the pin, including polarity, is placed on CWG1A/C after the required dead-                                                  |                                                            |                 |                           |                 |                 |              |  |

|                            | band in                                                                                                                                                |                                                            |                 |                           |                 |                 | •            |  |

| bit 1-0                    | Unimplemer                                                                                                                                             | nted: Read as                                              | · '0'           |                           |                 |                 |              |  |

| Note 1: This I             | bit may be writ<br>juration.                                                                                                                           | tten while EN                                              | = 0 (CWG10      | CON0 register             | ) to place the  | outputs into    | the shutdow  |  |

#### REGISTER 31-5: CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

# 32.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 32.1.1 DATA SELECTION

There are 40 signals available as inputs to the configurable logic. Four 40-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 32-2. Data inputs in the figure are identified by a generic numbered input name.

Table 32-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<5:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation to identify specific multiplexers: LCxD1S<5:0> through LCxD4S<5:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 32-3 through Register 32-6).

| TABLE 32-2: CLC | <b>DATA INPUT</b> | SELECTION |

|-----------------|-------------------|-----------|

|-----------------|-------------------|-----------|

| LCxDyS<5:0><br>Value | CLCx Input Source      |

|----------------------|------------------------|

| 100101 to 111111     | Reserved               |

| 100100               | EUSART2 (TX/CK) output |

| 100011               | EUSART2 (DT) output    |

| 100010               | CWG1B output           |

| 100001               | CWG1A output           |

| 100000               | RTCC seconds           |

| 011111               | MSSP1 SCK output       |

| 011110               | MSSP1 SDO output       |

| 011101               | EUSART1 (TX/CK) output |

| 011100               | EUSART1 (DT) output    |

| 011011               | CLC4 output            |

| 011010               | CLC3 output            |

| 011001               | CLC2 output            |

| 011000               | CLC1 output            |

| 010111               | IOCIF                  |

| 010110               | ZCD output             |

| 010101               | C2OUT                  |

| 010100               | C10UT                  |

| 010011               | PWM4 output            |

| 010010               | PWM3 output            |

| 010001               | CCP2 output            |

| 010000               | CCP1 output            |

| 001111               | SMT overflow           |

| 001110               | Timer4 overflow        |

| 001101               | Timer2 overflow        |

| 001100               | Timer1 overflow        |

| 001011               | Timer0 overflow        |

| 001010               | ADCRC                  |

| 001001               | SOSC                   |

| 001000               | MFINTOSC (32 kHz)      |

| 000111               | MFINTOSC (500 kHz)     |

| 000110               | LFINTOSC               |

| 000101               | HFINTOSC               |

| 000100               | FOSC                   |

| 000011               | CLCIN3PPS              |

| 000010               | CLCIN2PPS              |

| 000001               | CLCIN1PPS              |

| 000000               | CLCIN0PPS              |

|                      |                        |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                | _          | _                           |  |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | _                | _          | _                           |  |

| 57.6k  | 55556                         | -3.55      | 8                           | _                | _          | _                           | 57.60k            | 0.00       | 3                           | _                | _          | _                           |  |

| 115.2k | —                             |            | _                           | _                | _          | _                           | 115.2k            | 0.00       | 1                           | _                | —          | _                           |  |

#### TABLE 34-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   |            |                             | SYNC = 0       | = 1, BRG16 | 5 = 1 or SYNC = 1, BRG16 = 1 |                |            |                             |                |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|------------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |            | Fosc = 20.000 MHz           |                |            | Fosc = 18.432 MHz            |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal)  | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00       | 26666                       | 300.0          | 0.00       | 16665                        | 300.0          | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200              | 0.00       | 6666                        | 1200           | -0.01      | 4166                         | 1200           | 0.00       | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400              | 0.01       | 3332                        | 2400           | 0.02       | 2082                         | 2400           | 0.00       | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604              | 0.04       | 832                         | 9597           | -0.03      | 520                          | 9600           | 0.00       | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417             | 0.00       | 767                         | 10417          | 0.00       | 479                          | 10425          | 0.08       | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k            | -0.08      | 416                         | 19.23k         | 0.16       | 259                          | 19.20k         | 0.00       | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k            | -0.08      | 138                         | 57.47k         | -0.22      | 86                           | 57.60k         | 0.00       | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k            | 0.64       | 68                          | 116.3k         | 0.94       | 42                           | 115.2k         | 0.00       | 39                          | 115.2k         | 0.00       | 23                          |

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |            |                             |                |            |                             |                |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            | Fosc = 4.000 MHz            |                |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0          | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200           | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398           | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | _              | _          | _                           |

| R/W-0        | R-0                                                                                                                                                 | R-0                           | R-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| WFT          |                                                                                                                                                     | LCDA                          | WA           | LP<3:0>           |                  |                 |       |  |  |  |  |  |  |

| bit 7        | ·                                                                                                                                                   |                               |              |                   |                  |                 | bit ( |  |  |  |  |  |  |

|              |                                                                                                                                                     |                               |              |                   |                  |                 |       |  |  |  |  |  |  |

| Legend:      |                                                                                                                                                     |                               |              |                   |                  |                 |       |  |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                             | W = Writable                  | bit          | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |  |  |

| -n = Value a | It POR                                                                                                                                              | '1' = Bit is set              |              | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |  |  |  |

| L:1 7        |                                                                                                                                                     |                               |              |                   |                  |                 |       |  |  |  |  |  |  |