Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19156-e-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC16(L)F19155/56/75/76/85/86 are described within this data sheet. The PIC16(L)F19155/56/75/76/85/86 devices are available in 48-pin TQFP and UQFN, 44-pin TQFP and UQFN, 40-pin PDIP and 28-pin SPDIP, SOIC, SSOP and UQFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F19155/56/75/76/85/86 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUMMARY                                                                       |                        |                               |  |

|-------------------------------------------------------------------------------|------------------------|-------------------------------|--|

| Peripheral                                                                    |                        | PIC16(L)F19155/56/75/76/85/86 |  |

| Analog-to-Digital Converter with Computation                                  | on (ADC <sup>2</sup> ) | ٠                             |  |

| Digital-to-Analog Converter (DAC1)                                            |                        | ٠                             |  |

| Fixed Voltage Reference (FVR)                                                 |                        | •                             |  |

| Enhanced Universal Synchronous/Asynchron<br>Transmitter (EUSART1 and EUSART2) | nous Receiver/         | ٠                             |  |

| Temperature Indicator Module (TIM)                                            |                        | ٠                             |  |

| Zero-Cross Detect (ZCD1)                                                      |                        | ٠                             |  |

| Real-Time Calendar and Clock (RTCC)                                           |                        |                               |  |

| Liquid Crystal Display (LCD)                                                  |                        | ٠                             |  |

| Capture/Compare/PWM Modules (CCP)                                             |                        |                               |  |

|                                                                               | CCP1                   | ٠                             |  |

| Composition Markela (Oci)                                                     | CCP2                   | ٠                             |  |

| Comparator Module (Cx)                                                        | C1                     | •                             |  |

|                                                                               | C1                     | •                             |  |

| Configurable Logic Cell (CLC)                                                 | 01                     |                               |  |

|                                                                               | CLC1                   | •                             |  |

|                                                                               | CLC2                   | •                             |  |

|                                                                               | CLC3                   | •                             |  |

|                                                                               | CLC4                   | ٠                             |  |

| Complementary Waveform Generator (CWG)                                        |                        |                               |  |

|                                                                               | CWG1                   | •                             |  |

| Master Synchronous Serial Ports (MSSP)                                        |                        |                               |  |

|                                                                               | MSSP1                  | ٠                             |  |

| Pulse-Width Modulator (PWM)                                                   |                        | 1                             |  |

|                                                                               | PWM3                   | ٠                             |  |

|                                                                               | PWM4                   | ٠                             |  |

| Signal Measure Timer (SMT)                                                    |                        |                               |  |

|                                                                               | SMT1                   | ٠                             |  |

| Timers                                                                        |                        |                               |  |

|                                                                               | Timer0                 | ٠                             |  |

|                                                                               | Timer1                 | ٠                             |  |

|                                                                               | Timer2                 | ٠                             |  |

|                                                                               | Timer4                 | ٠                             |  |

| Address | Name              | Bit 7  | Bit 6 | Bit 5 | Bit 4          | Bit 3                | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-------------------|--------|-------|-------|----------------|----------------------|------------|-------|-------|-----------------------|----------------------------|

| Bank 20 |                   |        |       |       |                |                      |            |       |       |                       |                            |

|         |                   |        |       | CPU   | CORE REGISTERS | 6; see Table 4-3 for | rspecifics |       |       |                       |                            |

| A0Ch    | u — Unimplemented |        |       |       |                |                      |            |       |       |                       |                            |

| A0Dh    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A0Eh    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A0Fh    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A10h    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A11h    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A12h    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A13h    | _                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A14h    | —                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A15h    | —                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A16h    | —                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A17h    | —                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A18h    | —                 |        |       |       | Unimple        | mented               |            |       |       |                       |                            |

| A19h    | RC2REG            |        |       |       | RC2F           | REG                  |            |       |       | 0000 0000             | 0000 0000                  |

| A1Ah    | TX2REG            |        |       |       | TX2F           | REG                  |            |       |       | 0000 0000             | 0000 000                   |

| A1Bh    | SP2BRGL           |        |       |       | SP2B           | RGL                  |            |       |       | 0000 0000             | 0000 0000                  |

| A1Ch    | SP2BRGH           |        |       |       | SP2B           | RGH                  |            |       |       | 0000 0000             | 0000 000                   |

| A1Dh    | RC2STA            | SPEN   | RX9   | SREN  | CREN           | ADDEN                | FERR       | OERR  | RX9D  | 0000 0000             | 0000 000                   |

| A1Eh    | TX2STA            | CSRC   | TX9   | TXEN  | SYNC           | SENDB                | BRGH       | TRMT  | TX9D  | 0000 0010             | 0000 001                   |

| A1Fh    | BAUD2CON          | ABDOVF | RCIDL | _     | SCKP           | BRG16                | _          | WUE   | ABDEN | 01-0 0-00             | 01-0 0-0                   |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

## TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| r                   |      |       |               |       |          | . ,    |       |       |       | ,                     |                            |

|---------------------|------|-------|---------------|-------|----------|--------|-------|-------|-------|-----------------------|----------------------------|

| Address             | Name | Bit 7 | Bit 6         | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 63 (Continued) |      |       |               |       |          |        |       |       |       |                       |                            |

| 1FD0h               | _    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FD1h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD2h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD3h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD4h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD5h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD6h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD7h               | _    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FD8h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD9h               | —    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FDAh               | —    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FDBh               | —    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FDCh               | —    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FDDh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FDEh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FDFh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE0h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE1h               | —    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FE2h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE3h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

|                     |      |       |               |       |          |        |       |       |       |                       |                            |

Note 1: Unimplemented data memory locations, read as '0'.

Preliminary

### 8.15 Power Control (PCON) Registers

The Power Control (PCON) registers contain flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Timer Window Violation Reset

(WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

- VBAT Reset (VBATBOR)

The PCON0 register bits are shown in Register 8-2.

The PCON1 register bits are shown in Register 8-3.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no reset action will be generated.

All bits in PCON1 and PCON0 will maintain their state when either VDD or VBAT is powered.

| U-0                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                             | R/W/HS-0/0                           | R-0                     | U-0               | U-0                | U-0              | R/W/HS-0/0          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------|-------------------|--------------------|------------------|---------------------|--|--|

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 | TMR0IF                               | IOCIF                   | _                 | _                  | _                | INTF <sup>(1)</sup> |  |  |

| bit 7                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |                                      |                         |                   |                    |                  | bit 0               |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                      |                         |                   |                    |                  |                     |  |  |

| Legend:                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |                                      |                         |                   |                    |                  |                     |  |  |

| R = Reada                                                                                                                                                                                                                                                                                          | able bit                                                                                                                                        | W = Writable I                       | oit                     | U = Unimpler      | mented bit, read   | as '0'           |                     |  |  |

| u = Bit is u                                                                                                                                                                                                                                                                                       | nchanged                                                                                                                                        | x = Bit is unkn                      | own                     | -n/n = Value a    | at POR and BO      | R/Value at all o | other Resets        |  |  |

| '1' = Bit is :                                                                                                                                                                                                                                                                                     | set                                                                                                                                             | '0' = Bit is clea                    | ared                    | HS= Hardwa        | re Set             |                  |                     |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                      |                         |                   |                    |                  |                     |  |  |

| bit 7-6                                                                                                                                                                                                                                                                                            | Unimplemer                                                                                                                                      | nted: Read as 'o                     | )'                      |                   |                    |                  |                     |  |  |

| bit 5                                                                                                                                                                                                                                                                                              |                                                                                                                                                 | er0 Overflow In                      |                         |                   |                    |                  |                     |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 | register has ove<br>register did not |                         | t be cleared in   | software)          |                  |                     |  |  |

| bit 4                                                                                                                                                                                                                                                                                              | IOCIF: Interr                                                                                                                                   | upt-on-Change                        | Interrupt Flag          | bit (read-only)   | (2)                |                  |                     |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 | more of the IOC<br>d by the IOC mo   |                         | gister bits are o | currently set, ind | icating an ena   | bled edge was       |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 | f the IOCAF-IOC                      |                         | oits are current  | ly set             |                  |                     |  |  |

| bit 3-1                                                                                                                                                                                                                                                                                            | Unimplemer                                                                                                                                      | nted: Read as 'o                     | )'                      |                   |                    |                  |                     |  |  |

| bit 0                                                                                                                                                                                                                                                                                              | INTF: INT EX                                                                                                                                    | ternal Interrupt                     | Flag bit <sup>(1)</sup> |                   |                    |                  |                     |  |  |

|                                                                                                                                                                                                                                                                                                    | <ul> <li>1 = The INT external interrupt occurred (must be cleared in software)</li> <li>0 = The INT external interrupt did not occur</li> </ul> |                                      |                         |                   |                    |                  |                     |  |  |

| <ul> <li>Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).</li> <li>2: The IOCIF bit is the logical OR of all the IOCAF-IOCEF flags. Therefore, to clear the IOCIF flag, application firmware must clear all of the lower level IOCAF-IOCEF register bits.</li> </ul> |                                                                                                                                                 |                                      |                         |                   |                    |                  |                     |  |  |

| REGISTER 10-11: | PIR0: PERIPHERAL INTERRUPT STATUS REGISTER 0 |

|-----------------|----------------------------------------------|

|-----------------|----------------------------------------------|

| Note: | Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the Global                                                 |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.                                                   |  |  |  |  |  |  |  |

|       | User software should ensure the                                                            |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear                                                  |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.                                                            |  |  |  |  |  |  |  |

#### REGISTER 10-13: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|------------|-----|-----|-----|-----|------------|------------|

| _     | ZCDIF      |     |     | _   | _   | C2IF       | C1IF       |

| bit 7 |            |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ZCDIF: Zero-Cross Detect (ZCD1) Interrupt Flag bit                                                                                                             |

|         | <ul> <li>1 = An enabled rising and/or falling ZCD1 event has been detected (must be cleared in software)</li> <li>0 = No ZCD1 event has occurred</li> </ul>    |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1   | <b>C2IF</b> : Comparator C2 Interrupt Flag bit<br>1 = Comparator 2 interrupt asserted (must be cleared in software)<br>0 = Comparator 2 interrupt not asserted |

| bit 0   | <b>C1IF:</b> Comparator C1 Interrupt Flag bit<br>1 = Comparator 1 interrupt asserted (must be cleared in software)<br>0 = Comparator 1 interrupt not asserted  |

| Note:   | Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of                                                                     |

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 222                 |

| TRISA   | TRISA7  | TRISA6  | (1)     | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 222                 |

| LATA    | LATA7   | LATA6   | —       | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 223                 |

| ANSELA  | ANSA7   | ANSA6   | —       | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 223                 |

| WPUA    | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 224                 |

| ODCONA  | ODCA7   | ODCA6   | —       | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 224                 |

| SLRCONA | SLRA7   | SLRA6   | —       | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 225                 |

| INLVLA  | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 225                 |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** Unimplemented, read as '1'.

-n/n = Value at POR and BOR/Value at all other Resets

| R/W-x/u                           | R/W-x/u | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------------------------------|---------|---------|--------------|------------------|---------|---------|---------|

| LATB7                             | LATB6   | LATB5   | LATB4        | LATB3            | LATB2   | LATB1   | LATB0   |

| bit 7                             |         |         |              |                  |         |         | bit 0   |

|                                   |         |         |              |                  |         |         |         |

| Legend:                           |         |         |              |                  |         |         |         |

| R = Readable bit W = Writable bit |         |         | U = Unimpler | mented bit, read | as '0'  |         |         |

#### REGISTER 14-11: LATB: PORTB DATA LATCH REGISTER

#### bit 7-0 LATB<7:0>: RB<7:0> Output Latch Value bits<sup>(1)</sup>

u = Bit is unchanged

'1' = Bit is set

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 14-12: ANSELB: PORTB ANALOG SELECT REGISTER

x = Bit is unknown

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSB<7:0>: Analog Select between Analog or Digital Function on pins RB<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| SLRE7     SLRE6     SLRE5     SLRE4     SLRE3     —     SLRE1       bit 7       Legend: | R/W-1/1                            |  |  |  |  |

|-----------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| bit 7 Legend:                                                                           |                                    |  |  |  |  |

| Legend:                                                                                 | SLRE0                              |  |  |  |  |

| -                                                                                       | bit C                              |  |  |  |  |

|                                                                                         |                                    |  |  |  |  |

|                                                                                         |                                    |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                    | U = Unimplemented bit, read as '0' |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all othe   | er Resets                          |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared                                                   |                                    |  |  |  |  |

|                                                                                         |                                    |  |  |  |  |

#### **REGISTER 14-39: SLRCONE: PORTE SLEW RATE CONTROL REGISTER**

| bit 7-3 | SLRE<7:3>: PORTE Slew Rate Enable bits                                                |

|---------|---------------------------------------------------------------------------------------|

|         | For RE<7:0> pins, respectively                                                        |

|         | 1 = Port pin slew rate is limited                                                     |

|         | 0 = Port pin slews at maximum rate                                                    |

| bit 2   | Unimplemented: Read as '0'                                                            |

|         |                                                                                       |

| bit 1-0 | SLRE<1:0>: PORTE Slew Rate Enable bits                                                |

| bit 1-0 | <b>SLRE&lt;1:0&gt;:</b> PORTE Slew Rate Enable bits<br>For RE<1:0> pins, respectively |

0 = Port pin slews at maximum rate

### REGISTER 14-40: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|---------|-----|---------|---------|

| INLVLE7 | INLVLE6 | INLVLE5 | INLVLE4 | INLVLE3 | —   | INLVLE1 | INLVLE0 |

| bit 7   |         |         |         | •       |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | INLVLE<7:3>: PORTE Input Level Select bits                |

|---------|-----------------------------------------------------------|

|         | For RE<7:3> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

| bit 2   | Unimplemented: Read as '0'                                |

| bit 1-0 | INLVLE<1:0>: PORTE Input Level Select bits                |

|         | For RE<1:0> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

#### **REGISTER 19-20:** ADRESH: ADC RESULT REGISTER HIGH, FM = 1

| U-0     | U-0 | U-0 | U-0 | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|-----|-----|-----|-------------|---------|---------|---------|

| —       | —   | —   | —   | ADRES<11:8> |         |         |         |

| bit 7   |     |     | •   |             |         |         | bit 0   |

|         |     |     |     |             |         |         |         |

| Legend: |     |     |     |             |         |         |         |

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 ADRES<11:8>: ADC Sample Result bits. Upper four bits of 12-bit conversion result.

#### **REGISTER 19-21:** ADRESL: ADC RESULT REGISTER LOW, FM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<7:0> |         |         |         |         |         |         |         |

| bit 7 bit  |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits. Lower eight bits of 12-bit conversion result.

| U-0                                                              | R/W-x     | R/W-x | R/W-x                                   | R/W-x     | R/W-x  | R/W-x | R/W-x |  |

|------------------------------------------------------------------|-----------|-------|-----------------------------------------|-----------|--------|-------|-------|--|

| —                                                                | MINH<2:0> |       |                                         | MINL<3:0> |        |       |       |  |

| bit 7                                                            | bit       |       |                                         |           |        |       | bit 0 |  |

|                                                                  |           |       |                                         |           |        |       |       |  |

| Legend:                                                          |           |       |                                         |           |        |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as |           |       |                                         |           | as '0' |       |       |  |

| -n = Value at POR '1' = Bit is set                               |           |       | '0' = Bit is cleared x = Bit is unknown |           |        |       |       |  |

# REGISTER 24-8: MINUTES<sup>(1)</sup>: MINUTE VALUE REGISTER

bit 7 Unimplemented: Read as '0'

| bit 6-4 <b>MINH&lt;2:0&gt;:</b> Binary Coded Decimal value of minutes '10' digit; valid values from 0 to 5 |

|------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------|

bit 3-0 MINL<3:0>: Binary Coded Decimal value of minutes '1' digit; valid values from 0 to 9

**Note 1:** Writes to the MINUTE registers are only allowed when RTCWREN = 1.

# REGISTER 24-9: SECONDS<sup>(1)</sup>: SECOND VALUE REGISTER

| U-0   | R/W-x | R/W-x     | R/W-x | R/W-x | R/W-x     | R/W-x | R/W-x |  |  |

|-------|-------|-----------|-------|-------|-----------|-------|-------|--|--|

| —     |       | SECH<2:0> |       |       | SECL<3:0> |       |       |  |  |

| bit 7 |       |           |       |       |           |       | bit 0 |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 SECH<2:0>: Binary Coded Decimal value of seconds '10' digit; valid values from 0 to 5

bit 3-0 SECL<3:0>: Binary Coded Decimal value of seconds '1' digit; valid values from 0 to 9

**Note 1:** Writes to the SECOND registers are only allowed when RTCWREN = 1.

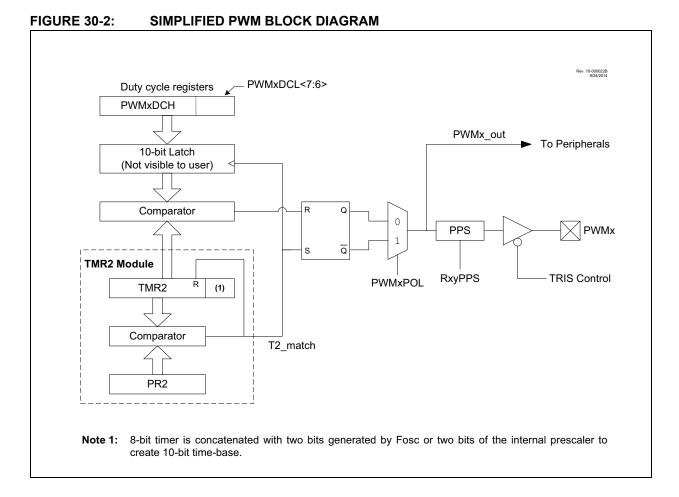

### 30.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 30-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = 0, the output will be the default state.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin.

- 2: Two identical Timer2 modules are implemented on this device. The timers are named Timer2 and Timer4. All references to Timer2 apply as well to Timer4. All references to T2PR apply as well to T4PR.

© 2017 Microchip Technology Inc.

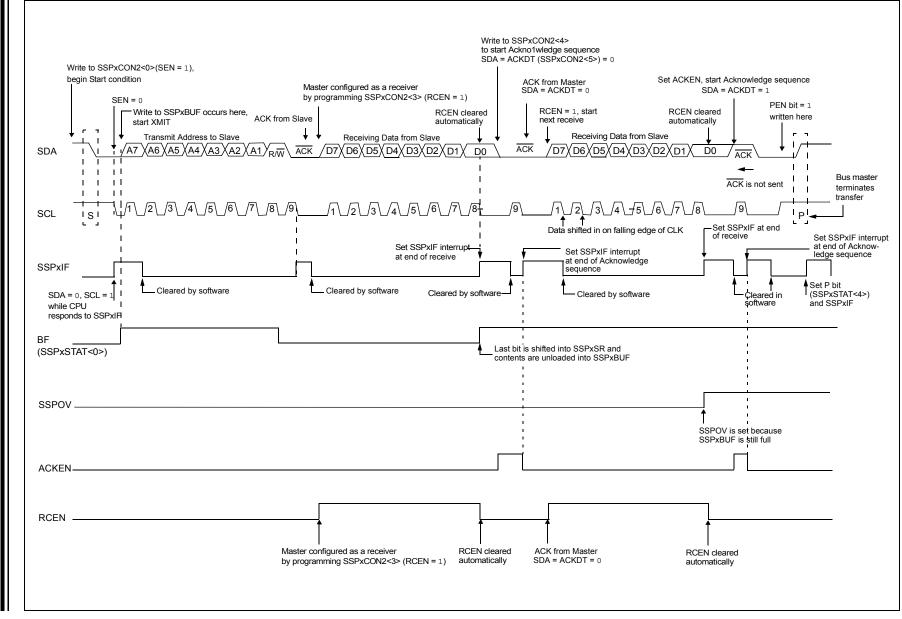

# FIGURE 33-29: I<sup>2</sup>C MASTER MODE WAVEFORM (RECEPTION, 7-BIT ADDRESS)

| Address | Name       | Bit 7         | Bit 6         | Bit 5 | Bit 4                                 | Bit 3   | Bit 2        | Bit 1 | Bit 0 | Register<br>on page |  |

|---------|------------|---------------|---------------|-------|---------------------------------------|---------|--------------|-------|-------|---------------------|--|

| 1E95h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1E96h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1E97h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E98h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E99h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Ah   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Bh   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Ch   | T2AINPPS   | _             | _             | _     |                                       |         | T2INPPS<4:0  | >     |       | 264                 |  |

| 1E9Dh   | T4AINPPS   | —             | _             | _     |                                       |         | T4INPPS<4:0  | >     |       | 264                 |  |

| 1E9Eh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1E9Fh   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA0h   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA1h   | CCP1PPS    | _             | —             | _     |                                       |         | CCP1PPS<4:0  | >     |       | 264                 |  |

| 1EA2h   | CCP2PPS    | _             | —             | _     |                                       |         | CCP2PPS<4:0  | >     |       | 264                 |  |

| 1EA3h   | _          |               |               | •     | Unimpl                                | emented |              |       |       |                     |  |

| 1EA4h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1EA5h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1EA6h   | _          | Unimplemented |               |       |                                       |         |              |       |       |                     |  |

| 1EA7h   | _          | Unimplemented |               |       |                                       |         |              |       |       |                     |  |

| 1EA8h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA9h   | SMT1WINPPS | _             | _             | _     |                                       | S       | MT1WINPPS<4  | 1:0>  |       | 264                 |  |

| 1EAAh   | SMT1SIGPPS | _             | _             | _     |                                       | S       | MT1SIGPPS<4  | :0>   |       | 264                 |  |

| 1EABh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EACh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EADh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EAEh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EAFh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB0h   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB1h   | CWG1PPS    | _             | _             | _     |                                       |         | CWG1PPS<4:0  | )>    |       | 264                 |  |

| 1EB2h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB3h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB4h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB5h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB6h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB7h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB8h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB9h   |            |               |               |       | · · · · · · · · · · · · · · · · · · · | emented |              |       |       |                     |  |

| 1EBAh   | _          |               |               |       | •                                     | emented |              |       |       |                     |  |

| 1EBBh   | CLCIN0PPS  | _             | _             | _     |                                       |         | CLCIN0PPS<4: | 0>    |       | 264                 |  |

| 1EBCh   | CLCIN1PPS  | _             | _             | _     |                                       |         | CLCIN1PPS<4: |       |       | 264                 |  |

| 1EBDh   | CLCIN2PPS  | _             |               | _     |                                       |         | CLCIN2PPS<4: |       |       | 264                 |  |

## TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| Address | Name            | Bit 7         | Bit 6                 | Bit 5        | Bit 4  | Bit 3      | Bit 2        | Bit 1           | Bit 0          | Register<br>on page |  |

|---------|-----------------|---------------|-----------------------|--------------|--------|------------|--------------|-----------------|----------------|---------------------|--|

| 1FD0h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FD1h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FD2h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD3h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD4h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD5h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD6h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD7h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD8h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FD9h   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FDAh   | —               |               |                       |              | Unimpl | emented    |              |                 |                |                     |  |

| 1FDBh   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FDCh   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FDDh   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FDEh   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FDFh   | —               | Unimplemented |                       |              |        |            |              |                 |                |                     |  |

| 1FE0h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FE1h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FE2h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FE3h   | —               |               | Unimplemented         |              |        |            |              |                 |                |                     |  |

| 1FE4h   | STATUS_SHAD     | —             | Z_SHAD DC_SHAD C_SHAD |              |        |            |              |                 |                |                     |  |

| 1FE5h   | WREG_SHAD       |               |                       |              | WREG_S | SHAD<7:0>  |              |                 |                |                     |  |

| 1FE6h   | BSR_SHAD        | _             | BSR SHAD<4:0>         |              |        |            |              |                 |                |                     |  |

| 1FE7h   | PCLATH_SHAD     | _             |                       |              | PC     | LATH_SHAD< | 6:0>         |                 |                |                     |  |

| 1FE8h   | FSR0L_SHAD      |               | FSR0L_SHAD<7:0>       |              |        |            |              |                 |                |                     |  |

| 1FE9h   | -<br>FSR0H SHAD |               | FSR0H SHAD<7:0>       |              |        |            |              |                 |                |                     |  |

| 1FEAh   | FSR1L SHAD      |               | FSR1L SHAD<7:0>       |              |        |            |              |                 |                |                     |  |

| 1FEBh   | <br>FSR1H_SHAD  |               | FSR1H SHAD<7:0>       |              |        |            |              |                 |                |                     |  |

| 1FECh   | _               |               |                       |              |        | emented    |              |                 |                |                     |  |

| 1FEDh   | STKPTR          | _             | _                     | _            |        |            | STKPTR<4:0   | >               |                |                     |  |

| 1FEEh   | TOSL            |               |                       | 1            | TOS    | _<7:0>     |              |                 |                | 1                   |  |

| 1FEFh   | TOSH            | _             |                       |              | 100    | TOSH<6:0>  |              |                 |                |                     |  |

| Legend: |                 |               | I                     | on condition |        |            | = received S | haded locations | unimplemented. | road as '0'         |  |

#### TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

The following sections give the technical details of the packages.

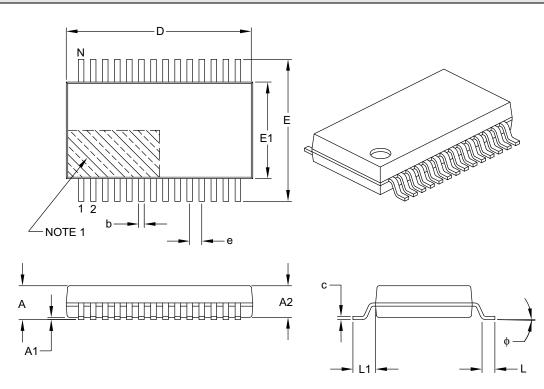

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units                   |          | MILLIMETERS |       |  |  |

|--------------------------|-------------------------|----------|-------------|-------|--|--|

|                          | <b>Dimension Limits</b> | MIN      | NOM         | MAX   |  |  |

| Number of Pins           | N                       |          | 28          |       |  |  |

| Pitch                    | e                       |          | 0.65 BSC    |       |  |  |

| Overall Height           | A                       | _        | -           | 2.00  |  |  |

| Molded Package Thickness | A2                      | 1.65     | 1.75        | 1.85  |  |  |

| Standoff                 | A1                      | 0.05     | -           | -     |  |  |

| Overall Width            | E                       | 7.40     | 7.80        | 8.20  |  |  |

| Molded Package Width     | E1                      | 5.00     | 5.30        | 5.60  |  |  |

| Overall Length           | D                       | 9.90     | 10.20       | 10.50 |  |  |

| Foot Length              | L                       | 0.55     | 0.75        | 0.95  |  |  |

| Footprint                | L1                      | 1.25 REF |             |       |  |  |

| Lead Thickness           | С                       | 0.09     | -           | 0.25  |  |  |

| Foot Angle               | φ                       | 0°       | 4°          | 8°    |  |  |

| Lead Width               | b                       | 0.22     | -           | 0.38  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- 3. Dimensioning and tolerancing per ASME 114.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

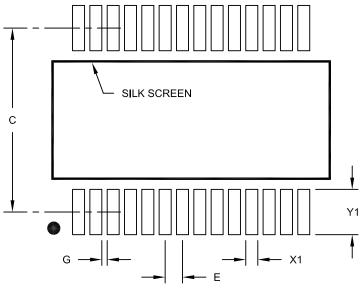

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Ν                | MILLIMETERS |  |      |  |

|--------------------------|------------------|-------------|--|------|--|

| Dimension                | Dimension Limits |             |  |      |  |

| Contact Pitch            | E                | 0.65 BSC    |  |      |  |

| Contact Pad Spacing      | C 7.20           |             |  |      |  |

| Contact Pad Width (X28)  | X1               |             |  | 0.45 |  |

| Contact Pad Length (X28) | Y1               |             |  | 1.75 |  |

| Distance Between Pads    | G                | 0.20        |  |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

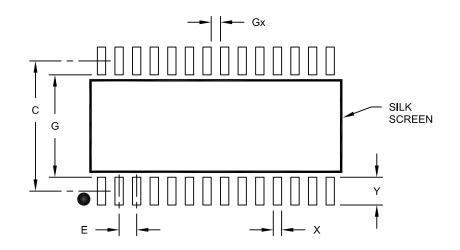

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | N   | MILLIMETERS |          |      |  |

|--------------------------|-----|-------------|----------|------|--|

| Dimension                | MIN | NOM         | MAX      |      |  |

| Contact Pitch            | E   |             | 1.27 BSC |      |  |

| Contact Pad Spacing      | С   |             | 9.40     |      |  |

| Contact Pad Width (X28)  | X   |             |          | 0.60 |  |

| Contact Pad Length (X28) | Y   |             |          | 2.00 |  |

| Distance Between Pads    | Gx  | 0.67        |          |      |  |

| Distance Between Pads    | G   | 7.40        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A