#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19156-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                 | Function              | Input Type | Output<br>Type | Description                                                     |

|--------------------------------------------------------------------------------------|-----------------------|------------|----------------|-----------------------------------------------------------------|

| RB3/C1IN2-/C2IN2-/IOCB3/ANB3/SEG11/COM6/                                             | RB3                   | TTL/ST     | CMOS/OD        | General purpose I/O.                                            |

| SEGCFLY2                                                                             | C1IN2-                | AN         | _              | Comparator negative input.                                      |

|                                                                                      | C2IN2-                | AN         | _              | Comparator negative input.                                      |

|                                                                                      | IOCB3                 | TTL/ST     | _              | Interrupt-on-change input.                                      |

|                                                                                      | ANB3                  | AN         | —              | ADC Channel input.                                              |

|                                                                                      | SEG11                 | _          | AN             | LCD Analog output.                                              |

|                                                                                      | COM6                  | _          | AN             | LCD Driver Common Outputs.                                      |

|                                                                                      | SEGCFLY2              | AN         | _              | LCD Drive Charge Pump Capacitor Inputs                          |

| RB4/ADCACT <sup>(1)</sup> /IOCB4/ANB4/COM0                                           | RB4                   | TTL/ST     | CMOS/OD        | General purpose I/O.                                            |

|                                                                                      | ADCACT <sup>(1)</sup> | TTL/ST     | -              | ADC Auto-Conversion Trigger input                               |

|                                                                                      | IOCB4                 | TTL/ST     | —              | Interrupt-on-change input.                                      |

|                                                                                      | ANB4                  | AN         | —              | ADC Channel input.                                              |

|                                                                                      | COM0                  |            | AN             | LCD Driver Common Outputs.                                      |

| RB5/T1G <sup>(1)</sup> /IOCB5/ANB5/SEG13/COM1                                        | RB5                   | TTL/ST     | CMOS/OD        | General purpose I/O.                                            |

|                                                                                      | T1G <sup>(1)</sup>    | —          | _              | Timer1 Gate input.                                              |

|                                                                                      | IOCB5                 | TTL/ST     | _              | Interrupt-on-change input.                                      |

|                                                                                      | ANB5                  | AN         | _              | ADC Channel input.                                              |

|                                                                                      | SEG13                 | _          | AN             | LCD Analog output.                                              |

|                                                                                      | COM1                  | _          | AN             | LCD Driver Common Outputs.                                      |

| RB6/CK2 <sup>(3)</sup> /TX2 <sup>(1)</sup> /CLCIN2 <sup>(1)</sup> /IOCB6/ANB6/SEG14/ | RB6                   | TTL/ST     | CMOS/OD        | General purpose I/O.                                            |

| ICSPCLK                                                                              | CK2 <sup>(3)</sup>    | _          | —              | EUSART synchronous clock out                                    |

|                                                                                      | TX2 <sup>(1)</sup>    | _          | _              | EUSART asynchronous TX data out                                 |

|                                                                                      | CLCIN2 <sup>(1)</sup> | _          | _              | Configurable Logic Cell source input.                           |

|                                                                                      | IOCB6                 | TTL/ST     | _              | Interrupt-on-change input.                                      |

|                                                                                      | ANB6                  | AN         | _              | ADC Channel input.                                              |

|                                                                                      | SEG14                 | _          | AN             | LCD Analog output.                                              |

|                                                                                      | ICSPCLK               | ST         | _              | In-Circuit Serial Programming™ and debugging<br>clock input.    |

| RB7/DK2 <sup>(3)</sup> /RX2 <sup>(1)</sup> /CLCIN3 <sup>(1)</sup> /IOCB7/ANB7/SEG15/ | RB7                   | TTL/ST     | CMOS/OD        | General purpose I/O.                                            |

| DAC1OUT2/ICSPDAT                                                                     | DK2 <sup>(3)</sup>    | _          | —              | EUSART synchronous data output                                  |

|                                                                                      | RX2 <sup>(1)</sup>    | _          | _              | EUSART receive input.                                           |

|                                                                                      | CLCIN3 <sup>(1)</sup> |            | _              | Configurable Logic Cell source input.                           |

|                                                                                      | IOCB7                 | TTL/ST     | _              | Interrupt-on-change input.                                      |

|                                                                                      | ANB7                  | AN         | _              | ADC Channel input.                                              |

|                                                                                      | SEG15                 | _          | AN             | LCD Analog output.                                              |

|                                                                                      | DAC1OUT2              | _          | AN             | Digital-to-Analog Converter output.                             |

|                                                                                      | ICSPDAT               | TTL/ST     | TTL/ST         | In-Circuit Serial Programming™ and debugging data input/output. |

### TABLE 1-2: PIC16(L)F19155/56 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output TTL = TTL compatible input' HV = High Voltage

ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 14-2 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 14-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

XTAL = Crystal levels

# 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM (GPR)

- Common RAM

- Data EEPROM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device         | Program Flash Memory Size (Words) | Last Program Memory Address |

|----------------|-----------------------------------|-----------------------------|

| PIC16(L)F19155 | 8k                                | 1FFFh                       |

| PIC16(L)F19175 | 8k                                | 1FFFh                       |

| PIC16(L)F19185 | 8k                                | 1FFFh                       |

| PIC16(L)F19156 | 16k                               | 3FFFh                       |

| PIC16(L)F19176 | 16k                               | 3FFFh                       |

| PIC16(L)F19186 | 16k                               | 3FFFh                       |

## 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing  $32K \times 14$  program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

| Address | Name | Bit 7 | Bit 6         | Bit 5 | Bit 4         | Bit 3               | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |  |

|---------|------|-------|---------------|-------|---------------|---------------------|-------------|-------|-------|-----------------------|----------------------------|--|

| Bank 13 |      |       |               |       |               |                     |             |       |       |                       |                            |  |

|         |      |       |               | CPU   | CORE REGISTER | S; see Table 4-3 fo | r specifics |       |       |                       |                            |  |

|         |      |       |               |       |               |                     | •           |       |       |                       |                            |  |

| 68Ch    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 68Dh    | _    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 68Eh    | _    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 68Fh    | _    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 690h    | —    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 691h    | —    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 692h    | _    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 693h    | _    |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 694h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 695h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 696h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 697h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 698h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 699h    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Ah    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Bh    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Ch    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Dh    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Eh    | _    |       |               |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 69Fh    |      |       | Unimplemented |       |               |                     |             |       |       |                       |                            |  |

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name    | Bit 7   | Bit 6                      | Bit 5    | Bit 4          | Bit 3               | Bit 2      | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|---------|---------|----------------------------|----------|----------------|---------------------|------------|---------|---------|-----------------------|----------------------------|

| Bank 16 |         | •       | •                          |          |                | •                   |            |         |         | •                     |                            |

|         |         |         |                            | CPU      | CORE REGISTERS | ; see Table 4-3 for | rspecifics |         |         |                       |                            |

| 80Ch    | WDTCON0 | -       | WDTPS<4:0> SWDTEN          |          |                |                     |            |         |         | dd ddd0               | বর বর্বব                   |

| 80Dh    | WDTCON1 | —       | - WDTCS<2:0> - WINDOW<2:0> |          |                |                     |            |         |         | -বর্বর -বর্বর         | -वेवेवे -वेवेव             |

| 80Eh    | WDTPSL  |         | PSCNT                      |          |                |                     |            |         |         | 0000 0000             | 0000 0000                  |

| 80Fh    | WDTPSH  |         | PSCNT                      |          |                |                     |            |         |         | 0000 0000             | 0000 0000                  |

| 810h    | WDTTMR  | _       |                            | WDTT     | MR<3:0>        |                     | STATE      | PSCNT17 | PSCNT16 | -xxx x000             | -xxx x000                  |

| 811h    | BORCON  | SBOREN  | —                          | _        | _              | _                   | _          | _       | BORRDY  | 1 q                   | u1                         |

| 812h    | VREGCON | —       | —                          | _        | _              | _                   | —          | VREGPM  | _       | x-                    | x                          |

| 813h    | PCON0   | STKOVF  | STKUNF                     | WDTWV    | RWDT           | RMCLR               | RI         | POR     | BOR     | 0011 110q             | qqqq qqu                   |

| 814h    | PCON1   | —       | _                          | _        |                | —                   | —          | MEMV    | VBATBOR | 1x                    | q                          |

| 815h    | —       |         |                            |          | Unimpler       | mented              |            |         |         |                       |                            |

| 816h    | —       |         |                            |          | Unimpler       | mented              |            |         |         |                       |                            |

| 817h    | —       |         |                            |          | Unimpler       | mented              |            |         |         |                       |                            |

| 818h    | —       |         |                            |          | Unimpler       | mented              |            |         |         |                       |                            |

| 819h    | —       |         |                            |          | Unimpler       | mented              |            |         |         |                       |                            |

| 81Ah    | NVMADRL | NVMADR7 | NVMADR6                    | NVMADR5  | NVMADR4        | NVMADR3             | NVMADR2    | NVMADR1 | NVMADR0 | xxxx xxxx             | นนนน นนนเ                  |

| 81Bh    | NVMADRH | —       | NVMADR14                   | NVMADR13 | NVMADR12       | NVMADR11            | NVMADR10   | NVMADR9 | NVMADR8 | 1xxx xxxx             | luuu uuu                   |

| 81Ch    | NVMDATL | NVMDAT7 | NVMDAT6                    | NVMDAT5  | NVMDAT4        | NVMDAT3             | NVMDAT2    | NVMDAT1 | NVMDAT0 | 0000 0000             | 0000 0000                  |

| 81Dh    | NVMDATH | _       | —                          | NVMDAT13 | NVMDAT12       | NVMDAT11            | NVMDAT10   | NVMDAT9 | NVMDAT8 | 0000 0000             | 0000 000                   |

| 81Eh    | NVMCON1 | —       | NVMREGS                    | LWLO     | FREE           | WRERR               | WREN       | WR      | RD      | 0000 0000             | 0000 000                   |

| 81Fh    | NVMCON2 |         |                            |          | NVMCON         | 12<7:0>             |            |         |         |                       |                            |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| Address            | Name                                                                                                                                                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|--|

| Banks 30-5         | anks 30-57                                                                                                                                              |       |       |       |       |       |       |       |       |                       |                            |  |

|                    | CPU CORE REGISTERS; see Table 4-3 for specifics                                                                                                         |       |       |       |       |       |       |       |       |                       |                            |  |

| F0Ch<br>—<br>1C9Fh | Unimplemented                                                                                                                                           |       |       |       |       |       |       |       |       |                       |                            |  |

| Legend:            | egend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. |       |       |       |       |       |       |       |       |                       |                            |  |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| Address    | Name                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|------------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 59    | ank 59                                          |       |       |       |       |       |       |       |       |                       |                            |  |

|            | CPU CORE REGISTERS; see Table 4-3 for specifics |       |       |       |       |       |       |       |       |                       |                            |  |

|            | CPU CORE REGISTERS; see Table 4-3 for specifics |       |       |       |       |       |       |       |       |                       |                            |  |

| 1D8Ch      |                                                 |       |       |       |       |       |       |       |       |                       |                            |  |

| —<br>1D9Fh | PFh Unimplemented                               |       |       |       |       |       |       |       |       |                       |                            |  |

| Legend:    |                                                 |       |       |       |       |       |       |       |       |                       |                            |  |

|                                                                                                                                                   |                                                          |                   |                 |                  |                  | •                |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|-----------------|------------------|------------------|------------------|--------------|

| R/W/HS-0/0                                                                                                                                        | R/W/HS-0/0                                               | U-0               | U-0             | U-0              | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0   |

| LCDIF                                                                                                                                             | RTCCIF                                                   | —                 | _               | _                | SMT1PWAIF        | SMT1PRAIF        | SMT1IF       |

| bit 7                                                                                                                                             |                                                          |                   |                 |                  |                  |                  | bit 0        |

|                                                                                                                                                   |                                                          |                   |                 |                  |                  |                  |              |

| Legend:                                                                                                                                           |                                                          |                   |                 |                  |                  |                  |              |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                |                                                          |                   |                 |                  |                  |                  |              |

| u = Bit is unchanged x = Bit is unknown                                                                                                           |                                                          |                   |                 | -n/n = Value     | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                                                  |                                                          | '0' = Bit is clea | ared            | HS = Hardwa      | are set          |                  |              |

|                                                                                                                                                   |                                                          |                   |                 |                  |                  |                  |              |

| bit 7 LCDIF: LCD Interrupt Flag bit                                                                                                               |                                                          |                   |                 |                  |                  |                  |              |

| <ul> <li>1 = A LCDIF interrupt condition has occurred (must be cleared in software)</li> <li>0 = No LCDIF interrupt event has occurred</li> </ul> |                                                          |                   |                 |                  |                  |                  |              |

| bit 6                                                                                                                                             |                                                          | ) Interrupt Flag  |                 | u                |                  |                  |              |

| DILO                                                                                                                                              |                                                          |                   |                 | urred (must be   | cleared in softv | vare)            |              |

|                                                                                                                                                   |                                                          | IF interrupt eve  |                 |                  |                  | /                |              |

| bit 5-3                                                                                                                                           | Unimplemen                                               | ted: Read as '    | o'              |                  |                  |                  |              |

| bit 2                                                                                                                                             | SMT1PWAIF:                                               | SMT1 Pulse-       | Vidth Acquisit  | ion Interrupt F  | lag bit          |                  |              |

|                                                                                                                                                   | 1 = Interrupt i                                          |                   |                 |                  |                  |                  |              |

|                                                                                                                                                   | 0 = Interrupt i                                          | 1 0               |                 |                  |                  |                  |              |

| bit 1                                                                                                                                             |                                                          | SMT1 Period       | Acquisition Int | terrupt Flag bit |                  |                  |              |

|                                                                                                                                                   | 1 = Interrupt is pending<br>0 = Interrupt is not pending |                   |                 |                  |                  |                  |              |

| bit 0                                                                                                                                             |                                                          | 1 Overflow Int    | errupt Flag bit | ł                |                  |                  |              |

|                                                                                                                                                   |                                                          |                   | 1 0             |                  | ed in software)  |                  |              |

|                                                                                                                                                   | 0 = No overflo                                           | ow event detec    | ted             | -                |                  |                  |              |

|                                                                                                                                                   |                                                          |                   |                 |                  |                  |                  |              |

#### REGISTER 10-19: PIR8: PERIPHERAL INTERRUPT REQUEST REGISTER 8

#### EXAMPLE 13-5: DEVICE ID ACCESS

| ; This write routine as       | ssumes the following:                                                 |

|-------------------------------|-----------------------------------------------------------------------|

| ; 1. A full row of data       | a are loaded, starting at the address in DATA_ADDR                    |

|                               | to be written is made up of two adjacent bytes in DATA_ADDR,          |

| ; stored in little endi       |                                                                       |

|                               | address (the least significant bits = 00000) is loaded in ADDRH:ADDRL |

| -                             | re located in common RAM (locations 0x70 - 0x7F)                      |

|                               | e not taken into account                                              |

| BANKSEL NVMADRH               |                                                                       |

| MOVF ADDRH,W                  |                                                                       |

| MOVWF NVMADRH                 | ; Load initial address                                                |

| MOVF ADDRL,W                  |                                                                       |

| MOVWF NVMADRL                 |                                                                       |

|                               | ; Load initial data address                                           |

| MOVWF FSR0L                   |                                                                       |

| MOVLW HIGH DATA ADDR          |                                                                       |

| MOVWF FSR0H                   |                                                                       |

| BCF NVMCON1,NVMREGS           | ; Set PFM as write location                                           |

| BSF NVMCON1,WREN              | ; Enable writes                                                       |

|                               | ; Load only write latches                                             |

| LOOP                          | / Hoad Only write fatches                                             |

| MOVIW FSR0++                  |                                                                       |

| MOVIW PSROTT<br>MOVWF NVMDATL | ; Load first data byte                                                |

| MOVIW FSR0++                  | / Hoad Tillst data byte                                               |

| MOVIW FSROTT<br>MOVWF NVMDATH | ; Load second data byte                                               |

| CALL UNLOCK_SEQ               |                                                                       |

| INCF NVMADRL, F               | ; Increment address                                                   |

|                               | , increment address                                                   |

| MOVF NVMADRL,W<br>XORLW 0x1F  | ; Check if lower bits of address are 00000                            |

|                               | ; and if on last of 32 addresses                                      |

| ANDLW 0x1F                    | ; Last of 32 words?                                                   |

|                               |                                                                       |

| GOTO START_WRITE              | ; If so, go write latches into memory                                 |

| GOTO LOOP                     |                                                                       |

| START_WRITE                   | · Tatahitaa annulata                                                  |

| BCF NVMCON1,LWLO              | ; Latch writes complete, now write memory                             |

| CALL UNLOCK_SEQ               | ; Perform required unlock sequence                                    |

| BCF NVMCON1,LWLO              | ; Disable writes                                                      |

| UNLOCK_SEQ                    |                                                                       |

| MOVLW 55h                     |                                                                       |

| BCF INTCON, GIE               | ; Disable interrupts                                                  |

| MOVWF NVMCON2                 | ; Begin unlock sequence                                               |

| MOVLW AAh                     |                                                                       |

| MOVWF NVMCON2                 |                                                                       |

| BSF NVMCON1,WR                |                                                                       |

| BSF INTCON,GIE                | ; Unlock sequence complete, re-enable interrupts                      |

|                               |                                                                       |

| R/W-0/0                                 | R/W-0/0                           | R/W-0/0 | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-----------------------------------------|-----------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

| WPUD7                                   | WPUD6                             | WPUD5   | WPUD4                                                 | WPUD3                              | WPUD2   | WPUD1   | WPUD0   |  |  |

| bit 7                                   |                                   |         |                                                       |                                    |         |         | bit 0   |  |  |

|                                         |                                   |         |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |                                   |         |                                                       |                                    |         |         |         |  |  |

| R = Readable                            | R = Readable bit W = Writable bit |         |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                                   |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

# REGISTER 14-29: WPUD: WEAK PULL-UP PORTD REGISTER<sup>(2)</sup>

bit 7-0 **WPUD<7:0>**: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

'1' = Bit is set

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

2: Not available on the PIC16(L)F19155/56 family of devices.

'0' = Bit is cleared

## REGISTER 14-30: ODCOND: PORTD OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ODCD<7:0>: PORTD Open-Drain Enable bits

- For RD<7:0> pins, respectively

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** Not available on the PIC16(L)F19155/56 family of devices.

| SLRE7     SLRE6     SLRE5     SLRE4     SLRE3     —     SLRE1       bit 7       Legend: | R/W-1/1   |

|-----------------------------------------------------------------------------------------|-----------|

| bit 7 Legend:                                                                           |           |

| Legend:                                                                                 | SLRE0     |

| -                                                                                       | bit C     |

|                                                                                         |           |

|                                                                                         |           |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                    |           |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all othe   | er Resets |

| '1' = Bit is set '0' = Bit is cleared                                                   |           |

|                                                                                         |           |

#### **REGISTER 14-39: SLRCONE: PORTE SLEW RATE CONTROL REGISTER**

| bit 7-3 | SLRE<7:3>: PORTE Slew Rate Enable bits                                                |

|---------|---------------------------------------------------------------------------------------|

|         | For RE<7:0> pins, respectively                                                        |

|         | 1 = Port pin slew rate is limited                                                     |

|         | 0 = Port pin slews at maximum rate                                                    |

| bit 2   | Unimplemented: Read as '0'                                                            |

|         |                                                                                       |

| bit 1-0 | SLRE<1:0>: PORTE Slew Rate Enable bits                                                |

| bit 1-0 | <b>SLRE&lt;1:0&gt;:</b> PORTE Slew Rate Enable bits<br>For RE<1:0> pins, respectively |

0 = Port pin slews at maximum rate

### REGISTER 14-40: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|---------|-----|---------|---------|

| INLVLE7 | INLVLE6 | INLVLE5 | INLVLE4 | INLVLE3 | —   | INLVLE1 | INLVLE0 |

| bit 7   |         |         |         | •       |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | INLVLE<7:3>: PORTE Input Level Select bits                |

|---------|-----------------------------------------------------------|

|         | For RE<7:3> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

| bit 2   | Unimplemented: Read as '0'                                |

| bit 1-0 | INLVLE<1:0>: PORTE Input Level Select bits                |

|         | For RE<1:0> pins, respectively                            |

|         | 1 = ST input used for PORT reads and interrupt-on-change  |

|         | 0 = TTL input used for PORT reads and interrupt-on-change |

| R/W/HS-0/0                  | R/W/HS-0/0 | U-0                                   | R/W/HS-0/0                             | R/W/HS-0/0    | R/W/HS-0/0                            | R/W/HS-0/0   | R/W/HS-0/0      |

|-----------------------------|------------|---------------------------------------|----------------------------------------|---------------|---------------------------------------|--------------|-----------------|

| IOCCF7                      | IOCCF6     |                                       | IOCCF4                                 | IOCCF3        | IOCCF2                                | IOCCF1       | IOCCF0          |

| bit 7                       |            |                                       |                                        |               |                                       |              | bit 0           |

|                             |            |                                       |                                        |               |                                       |              |                 |

| Legend:                     |            |                                       |                                        |               |                                       |              |                 |

| R = Readable bit W = Writat |            | W = Writable                          | bit U = Unimplemented bit, read as '0' |               |                                       |              |                 |

| u = Bit is unch             | anged      | x = Bit is unknown -n/n = Value at PC |                                        | at POR and BO | POR and BOR/Value at all other Resets |              |                 |

| '1' = Bit is set            |            | '0' = Bit is clea                     | eared HS - Bit is set in hardware      |               |                                       |              |                 |

|                             |            |                                       |                                        |               |                                       |              |                 |

| bit 7-6                     |            | Interrupt-on-C                        | 0                                      | 0             |                                       |              |                 |

|                             |            | ed change was<br>IOCCPx = 1 a         |                                        |               | pin<br>d on RCx, or wh                | nen IOCCNx = | 1 and a falling |

|         | edge was detected on RCx.                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 0 = No change was detected, or the user cleared the detected change                                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                            |

| bit 4-0 | IOCCF<4:0>: Interrupt-on-Change PORTC Flag bits<br>1 = An enabled change was detected on the associated pin           |

|         | Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx. |

|         |                                                                                                                       |

<sup>0 =</sup> No change was detected, or the user cleared the detected change

#### REGISTER 17-10: IOCEP: INTERRUPT-ON-CHANGE PORTE POSITIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0            | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----------------------|-----|-----|-------|

| —     | —   | —   | —   | IOCEP3 <sup>(1)</sup> | —   | —   | —     |

| bit 7 |     |     |     |                       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 3 IOCEP3: Interrupt-on-Change PORTE Positive Edge Enable bit

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCEFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

bit 2-0 Unimplemented: Read as '0'

**Note 1:** If MCLRE = 1 or LVP = 1, RC port functionality is disabled and IOC is not available on RE3.

### REGISTER 22-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | _   | —   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

## Legend:

| Logonan              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select bits |

|         | 111 = CxVN connects to AVss                             |

|         | 110 = CxVN connects to FVR Buffer 2                     |

|         | 101 = CxVN unconnected                                  |

|         | 100 = CxVN connects to CxIN4- pin                       |

|         | 011 = CxVN connects to CxIN3- pin                       |

|         | 010 = CxVN connects to CxIN2- pin                       |

|         | $0.01 - C_{\rm X}/N$ connects to C_{\rm X}/N1 nin       |

001 = CxVN connects to CxIN1- pin 000 = CxVN connects to CxIN0- pin

#### REGISTER 22-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | —   | —   | —   | —   |         | PCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-2 Unimplemented: Read as '0'

- bit 5-3 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP LCD VREF<sup>(1)</sup>

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

Note 1: Applies to C2 comparator only.

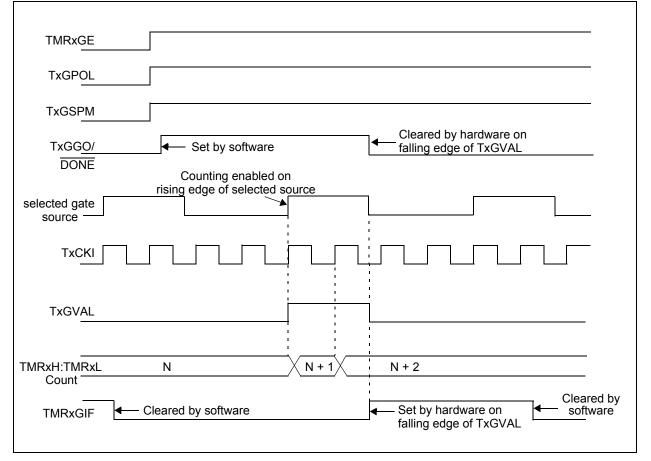

| FIGURE 26-4:           | TIMER1 GATE TOGGLE MODE                                                                                                                                            |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                    |

| TxGPOL                 |                                                                                                                                                                    |

| TxGT <u>M</u>          |                                                                                                                                                                    |

| selected<br>gate input |                                                                                                                                                                    |

| ТхСКІ                  |                                                                                                                                                                    |

| TxGVAL                 |                                                                                                                                                                    |

| TMRxH:TMRxL N<br>Count | $\frac{1}{N+1} \times \frac{1}{N+2} \times \frac{1}{N+3} \times \frac{1}{N+4} \times \frac{1}{N+5} \times \frac{1}{N+6} \times \frac{1}{N+7} \times \frac{1}{N+8}$ |

## FIGURE 26-5: TIMER1 GATE SINGLE-PULSE MODE

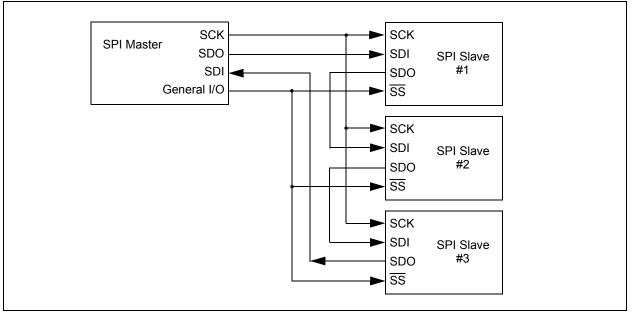

#### FIGURE 33-7: SPI DAISY-CHAIN CONNECTION

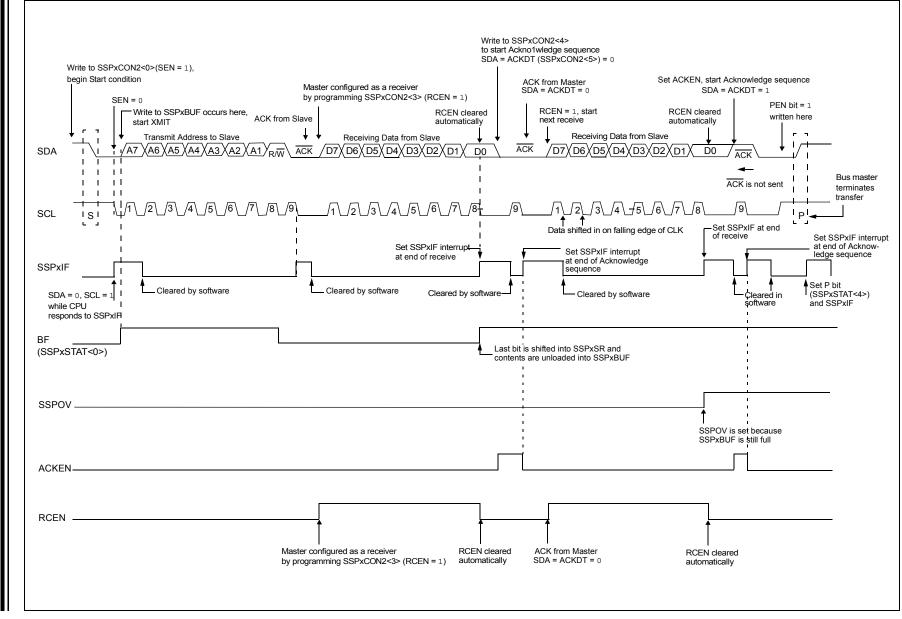

# FIGURE 33-29: I<sup>2</sup>C MASTER MODE WAVEFORM (RECEPTION, 7-BIT ADDRESS)

| Register  | Bit 7       | Bit 6      | Bit 5      | Bit 4       | Bit 3      | Bit 2       | Bit 1     | Bit 0     |

|-----------|-------------|------------|------------|-------------|------------|-------------|-----------|-----------|

| LCDDATA0  | SEG7 COM0   | SEG6 COM0  |            | SEG4 COM0   | SEG3 COM0  | SEG2 COM0   | SEG1 COM0 | SEG0 COM0 |

| LCDDATA1  | SEG15 COM0  | SEG14 COM0 | SEG13 COM0 | _           | SEG11 COM0 | SEG10 COM0  | SEG9 COM0 | SEG8 COM0 |

| LCDDATA2  | SEG23 COM0  | SEG22 COM0 | _          | SEG20 COM0  | SEG19 COM0 | SEG18 COM0  | _         | _         |

| LCDDATA3  | _           | _          |            | _           | _          | _           |           |           |

| LCDDATA4  |             |            |            |             |            |             |           |           |

| LCDDATA5  |             |            |            |             |            |             |           |           |

| LCDDATA6  | SEG7 COM1   | SEG6 COM1  |            | SEG4 COM1   | SEG3 COM1  | SEG2 COM1   | SEG1 COM1 | SEG0 COM1 |

| LCDDATA0  | SEG15 COM1  | SEG14 COM1 | SEG13 COM1 |             | SEG11 COM1 | SEG10 COM1  | SEG9 COM1 | SEG8 COM1 |

| LCDDATA8  | SEG23 COM1  | SEG22 COM1 | -          | SEG20 COM1  | SEG19 COM1 | SEG18 COM1  | -         |           |

| LCDDATA0  | 32023 00111 | 3E022 COM1 |            | 32020 00111 | SECTS COMT | SEC 10 COMT |           |           |

| LCDDATA9  |             |            |            |             |            |             |           |           |

|           |             |            |            |             |            |             |           |           |

| LCDDATA11 |             |            |            |             |            |             |           |           |

| LCDDATA12 | SEG7 COM2   | SEG6 COM2  | -          | SEG4 COM2   | SEG3 COM2  | SEG2 COM2   | SEG1 COM2 | SEG0 COM2 |

| LCDDATA13 | SEG15 COM2  | SEG14 COM2 | SEG13 COM2 | -           | SEG11 COM2 | SEG10 COM2  | SEG9 COM2 | SEG8 COM2 |

| LCDDATA14 | SEG23 COM2  | SEG22 COM2 | _          | SEG20 COM2  | SEG19 COM2 | SEG18 COM2  |           | _         |

| LCDDATA15 | _           | —          |            |             | —          | —           | —         | —         |

| LCDDATA16 | —           | —          |            |             | —          | —           | —         | —         |

| LCDDATA17 | —           | —          |            | —           | —          | —           | —         | —         |

| LCDDATA18 | SEG7 COM3   | SEG6 COM3  | _          | SEG4 COM3   | SEG3 COM3  | SEG2 COM3   | SEG1 COM3 | SEG0 COM3 |

| LCDDATA19 | SEG15 COM3  | SEG14 COM3 | SEG13 COM3 | —           | SEG11 COM3 | SEG10 COM3  | SEG9 COM3 | SEG8 COM3 |

| LCDDATA20 | SEG23 COM3  | SEG22 COM3 | _          | SEG20 COM3  | SEG19 COM3 | SEG18 COM3  | _         | _         |

| LCDDATA21 | —           | —          |            |             | —          | —           | —         | —         |

| LCDDATA22 | —           | —          | —          | —           | —          | —           | —         | —         |

| LCDDATA23 | —           | —          | —          | —           | —          | —           | —         | —         |

| LCDDATA24 | SEG7 COM4   | SEG6 COM4  | _          | SEG4 COM4   | SEG3 COM4  | SEG2 COM4   | SEG1 COM4 | SEG0 COM4 |

| LCDDATA25 | SEG15 COM4  | SEG14 COM4 | SEG13 COM4 |             | SEG11 COM4 | SEG10 COM4  | SEG9 COM4 | SEG8 COM4 |

| LCDDATA26 | SEG23 COM4  | SEG22 COM4 |            | SEG20 COM4  | SEG19 COM4 | SEG18 COM4  |           |           |

| LCDDATA27 | _           | _          | _          | _           | —          | _           | —         | —         |

| LCDDATA28 | _           | _          | _          | _           | —          | _           | —         | —         |

| LCDDATA29 | _           | _          | _          | _           | _          | _           | —         | _         |

| LCDDATA30 | SEG7 COM5   | SEG6 COM5  | _          | SEG4 COM5   | SEG3 COM5  | SEG2 COM5   | SEG1 COM5 | SEG0 COM5 |

| LCDDATA31 | SEG15 COM5  | SEG14 COM5 | SEG13 COM5 | _           | SEG11 COM5 | SEG10 COM5  | SEG9 COM5 | SEG8 COM5 |

| LCDDATA32 | SEG23 COM5  | SEG22 COM5 | —          | SEG20 COM5  | SEG19 COM5 | SEG18 COM5  | —         | —         |

| LCDDATA33 | —           | —          | _          | _           | —          | —           | —         | —         |

| LCDDATA34 | —           | _          |            |             | —          | —           | —         | —         |

| LCDDATA35 | —           | —          | _          | —           | —          | —           | —         | —         |

| LCDDATA36 | SEG7 COM6   | SEG6 COM6  | _          | SEG4 COM6   | SEG3 COM6  | SEG2 COM6   | SEG1 COM6 | SEG0 COM6 |

| LCDDATA37 | SEG15 COM6  | SEG14 COM6 | SEG13 COM6 | _           | SEG11 COM6 | SEG10 COM6  | SEG9 COM6 | SEG8 COM6 |

| LCDDATA38 | SEG23 COM6  | SEG22 COM6 | _          | SEG20 COM6  | SEG19 COM6 | SEG18 COM6  | —         | —         |

| LCDDATA39 | _           | _          | _          | _           | —          | _           | —         | _         |

| LCDDATA40 | _           | _          | _          | _           | _          | _           | _         | _         |

| LCDDATA41 | —           | _          | _          | _           | —          | —           | —         | —         |

| LCDDATA42 | SEG7 COM7   | SEG6 COM7  | —          | SEG4 COM7   | SEG3 COM7  | SEG2 COM7   | SEG1 COM7 | SEG0 COM7 |

| LCDDATA43 | SEG15 COM7  | SEG14 COM7 | SEG13 COM7 | _           | SEG11 COM7 | SEG10 COM7  | SEG9 COM7 | SEG8 COM7 |

| LCDDATA44 | SEG23 COM7  | SEG22 COM7 |            | SEG20 COM7  | SEG19 COM7 | SEG18 COM7  |           | _         |

| LCDDATA45 |             |            |            |             |            |             | _         | _         |

| LCDDATA46 | _           | _          |            |             | _          | _           | _         | _         |

| LCDDATA47 | _           | _          | _          |             | _          | _           | _         | _         |

## TABLE 35-3: LCDDATAX REGISTERS AND BITS FOR SEGMENT AND COM COMBINATIONS (28-PIN)

© 2017 Microchip Technology Inc.

| Address          | Name                | Bit 7                          | Bit 6         | Bit 5                               | Bit 4                       | Bit 3    | Bit 2     | Bit 1       | Bit 0    | Register<br>on page |  |

|------------------|---------------------|--------------------------------|---------------|-------------------------------------|-----------------------------|----------|-----------|-------------|----------|---------------------|--|

| 1D8Ch<br>—       | _                   |                                | Unimplemented |                                     |                             |          |           |             |          |                     |  |

| 1D9Fh            |                     |                                | Unimplemented |                                     |                             |          |           |             |          |                     |  |

| 1E0Ch<br>1E0Dh   |                     |                                |               |                                     |                             |          |           |             |          |                     |  |

| 1E0Eh            |                     | Unimplemented<br>Unimplemented |               |                                     |                             |          |           |             |          |                     |  |

| 1E0Fh            | CLCDATA             | _                              | _             | _                                   |                             | MLC4OUT  | MLC3OUT   | MLC2OUT     | MLC1OUT  | 509                 |  |

| 1E10h            | CLCDATA<br>CLC1CON  | LC1EN                          |               | LC10UT                              | LC1INTP                     | LC1INTN  | IVILC3001 | LC1MODE<2:0 |          | 509                 |  |

|                  | CLC1POL             | LC1POL                         | _             |                                     |                             | LC1G4POL | LC1G3POL  | LC1G2POL    | LC1G1POL |                     |  |

| 1E11h            | CLC190L<br>CLC1SEL0 |                                |               |                                     |                             |          |           | LUIGZPUL    | LUIGIPUL | 502                 |  |

| 1E12h            |                     |                                |               |                                     |                             |          | 1S<5:0>   |             |          | 503                 |  |

| 1E13h            | CLC1SEL1            |                                |               |                                     |                             |          | 2S<5:0>   |             |          | 503                 |  |

| 1E14h            | CLC1SEL2            |                                |               |                                     |                             |          | 3S<5:0>   |             |          | 503                 |  |

| 1E15h            | CLC1SEL3            | _                              |               |                                     |                             |          | 4S<5:0>   |             |          | 503                 |  |

| 1E16h            | CLC1GLS0            | LC1G1D4T                       | LC1G1D4N      | LC1G1D3T                            | LC1G1D3N                    | LC1G1D2T | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | 505                 |  |

| 1E17h            | CLC1GLS1            | LC1G2D4T                       | LC1G2D4N      | LC1G2D3T                            | LC1G2D3N                    | LC1G2D2T | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | 503                 |  |

| 1E18h            | CLC1GLS2            | LC1G3D4T                       | LC1G3D4N      | LC1G3D3T                            | LC1G3D3N                    | LC1G3D2T | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | 507                 |  |

| 1E19h            | CLC1GLS3            | LC1G4D4T                       | LC1G4D4N      | LC1G4D3T                            | LC1G4D3N                    | LC1G4D2T | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | 508                 |  |

| 1E1Ah            | CLC2CON             | LC2EN                          | _             | LC2OUT                              | LC2INTP                     | LC2INTN  |           | LC2MODE<2:0 | >        | 501                 |  |

| 1E1Bh            | CLC2POL             | LC2POL                         | _             | LC2G4POL LC2G3POL LC2G2POL LC2G1POL |                             |          |           |             | 502      |                     |  |

| 1E1Ch            | CLC2SEL0            | —                              | —             |                                     |                             | LC2D     | 1S<5:0>   |             |          | 503                 |  |

| 1E1Dh            | CLC2SEL1            | —                              |               |                                     |                             | LC2D     | 2S<5:0>   |             |          | 503                 |  |

| 1E1Eh            | CLC2SEL2            | —                              | _             |                                     |                             | LC2D     | 3S<5:0>   |             |          | 503                 |  |

| 1E1Fh            | CLC2SEL3            | —                              | _             |                                     |                             | LC2D     | 4S<5:0>   |             |          | 504                 |  |

| 1E20h            | CLC2GLS0            | LC2G1D4T                       | LC1G1D4N      | LC2G1D3T                            | LC2G1D3N                    | LC2G1D2T | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | 505                 |  |

| 1E21h            | CLC2GLS1            | LC2G2D4T                       | LC1G2D4N      | LC2G2D3T                            | LC2G2D3N                    | LC2G2D2T | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | 506                 |  |

| 1E22h            | CLC2GLS2            | LC2G3D4T                       | LC1G3D4N      | LC2G3D3T                            | LC2G3D3N                    | LC2G3D2T | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | 507                 |  |

| 1E23h            | CLC2GLS3            | LC2G4D4T                       | LC1G4D4N      | LC2G4D3T                            | LC2G4D3N                    | LC2G4D2T | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | 508                 |  |

| 1E24h            | CLC3CON             | LC3EN                          | _             | LC3OUT                              | LC3INTP                     | LC3INTN  |           | LC3MODE<2:0 | >        | 501                 |  |

| 1E25h            | CLC3POL             | LC3POL                         | _             | _                                   |                             | LC3G4POL | LC3G3POL  | LC3G2POL    | LC3G1POL | 502                 |  |

| 1E26h            | CLC3SEL0            | _                              | _             |                                     |                             | LC       | 3D1S      |             |          | 503                 |  |

| 1E27h            | CLC3SEL1            | _                              | _             |                                     |                             |          | 3D2S      |             |          | 503                 |  |

| 1E28h            | CLC3SEL2            | _                              | _             |                                     |                             |          | 3D3S      |             |          | 503                 |  |

| 1E29h            | CLC3SEL3            | _                              | _             |                                     |                             |          | 3D4S      |             |          | 503                 |  |

| 1E2Ah            | CLC3GLS0            | LC3G1D4T                       | LC3G1D4N      | LC3G1D3T                            | LC3G1D3N                    | 1        | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | 505                 |  |

| 1E2Bh            | CLC3GLS1            | LC3G2D4T                       | LC3G2D4N      | LC3G2D3T                            | LC3G2D3N                    | LC3G2D2T | LC3G2D2N  | LC3G2D1T    | LC3G2D1N | 506                 |  |

| 1E2Ch            | CLC3GLS2            | LC3G3D4T                       | LC3G3D4N      | LC3G3D3T                            | LC3G3D3N                    | LC3G3D2T | LC3G3D2N  | LC3G3D1T    | LC3G3D1N | 507                 |  |

| 1E2Dh            | CLC3GLS3            | LC3G4D4T                       | LC3G4D4N      | LC3G4D3T                            | LC3G4D3N                    | LC3G4D2T | LC3G4D2N  | LC3G4D1T    | LC3G4D1N | 508                 |  |

| 1E2Eh            | CLC4CON             | LC4EN                          |               | LC4OUT                              | LC304D3N                    | LC4INTN  | 200070211 | LC4MODE<2:0 |          | 503                 |  |

| 1E2Fh            | CLC4POL             | LC4POL                         | _             |                                     |                             | LC4G4POL | LC4G3POL  | LC4G2POL    | LC4G1POL | 502                 |  |

|                  |                     | LUHFUL                         |               |                                     | _                           |          |           | LUHUZFUL    | LUHUIFUL |                     |  |

| 1E30h            | CLC4SEL0            | _                              |               |                                     |                             |          | 1S<5:0>   |             |          | 503                 |  |

| 1E31h            | CLC4SEL1            | _                              | _             |                                     |                             |          | 2S<5:0>   |             |          | 503                 |  |

| 1E32h            | CLC4SEL2            | —                              | _             |                                     |                             |          | 3S<5:0>   |             |          | 503                 |  |

| 1E33h            | CLC4SEL3            | —                              |               |                                     |                             |          | 4S<5:0>   |             |          | 503                 |  |

| 1E34h            | CLC4GLS0            | LC4G1D4T                       | LC4G1D4N      | LC4G1D3T                            | LC4G1D3N                    | LC4G1D2T | LC4G1D2N  | LC4G1D1T    | LC4G1D1N | 505                 |  |

| 1E35h<br>Legend: | CLC4GLS1            | LC4G2D4T                       | LC4G2D4N      | LC4G2D3T                            | LC4G2D3N<br>= unimplemented | LC4G2D2T | LC4G2D2N  | LC4G2D1T    | LC4G2D1N | 506                 |  |

# TABLE 38-1: REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

| Address | Name    | Bit 7   | Bit 6         | Bit 5   | Bit 4           | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on page |

|---------|---------|---------|---------------|---------|-----------------|---------|---------|---------|---------|---------------------|

| 1F33h   | _       |         | Unimplemented |         |                 |         |         |         |         |                     |

| 1F34h   | —       |         |               |         | Unimpl          | emented |         |         |         |                     |

| 1F35h   | _       |         |               |         | Unimpl          | emented |         |         |         |                     |

| 1F36h   | _       |         | Unimplemented |         |                 |         |         |         |         |                     |

| 1F37h   | _       |         |               |         | Unimpl          | emented |         |         |         |                     |

| 1F38h   | ANSELA  | ANSA7   | ANSA6         | —       | ANSA4           | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 223                 |

| 1F39h   | WPUA    | WPUA7   | WPUA6         | WPUA5   | WPUA4           | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 224                 |

| 1F3Ah   | ODCONA  | ODCA7   | ODCA6         | —       | ODCA4           | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 224                 |

| 1F3Bh   | SLRCONA | SLRA7   | SLRA6         | —       | SLRA4           | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 225                 |

| 1F3Ch   | INLVLA  | INLVLA7 | INLVLA6       | INLVLA5 | INLVLA4         | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 225                 |

| 1F3Dh   | IOCAP   | IOCAP7  | IOCAP6        | IOCAP5  | IOCAP4          | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |                     |

| 1F3Eh   | IOCAN   | IOCAN7  | IOCAN6        | IOCAN5  | IOCAN4          | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |                     |

| 1F3Fh   | IOCAF   | IOCAF7  | IOCAF6        | IOCAF5  | IOCAF4          | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  |                     |

| 1F40h   | _       |         | •             |         | Unimpl          | emented |         | •       | •       |                     |

| 1F41h   | _       |         |               |         | Unimpl          | emented |         |         |         |                     |

| 1F42h   | _       |         |               |         | Unimpl          | emented |         |         |         |                     |