Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 20x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19156-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| r                   |      |       |               |       |          | . ,    |       |       |       | ,                     |                            |

|---------------------|------|-------|---------------|-------|----------|--------|-------|-------|-------|-----------------------|----------------------------|

| Address             | Name | Bit 7 | Bit 6         | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 63 (Continued) |      |       |               |       |          |        |       |       |       |                       |                            |

| 1FD0h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD1h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD2h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD3h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD4h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD5h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD6h               | _    |       |               |       | Unimpler | nented |       |       |       |                       |                            |

| 1FD7h               | _    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FD8h               | _    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FD9h               | —    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FDAh               | —    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FDBh               | —    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FDCh               | —    |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1FDDh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FDEh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FDFh               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE0h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE1h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE2h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1FE3h               | —    |       |               |       | Unimpler | mented |       |       |       |                       |                            |

|                     |      |       |               |       |          |        |       |       |       |                       |                            |

Note 1: Unimplemented data memory locations, read as '0'.

Preliminary

# 6.0 DEVICE INFORMATION AREA

The Device Information Area (DIA) is a dedicated region in the program memory space, it is a new feature in the PIC16(L)F19155/56/75/76/85/86 family of devices. The DIA contains the calibration data for the internal temperature indicator module, stores the Microchip Unique Identifier words and the Fixed Voltage Reference voltage readings measured in mV.

The complete DIA table is shown in Table 6-1, followed by a description of each region and its functionality. The data is mapped from 8100h to 811Fh in the PIC16(L)F19155/56/75/76/85/86 family. These locations are read-only and cannot be erased or modified. The data is programmed into the device during manufacturing.

TABLE 6-1: DEVICE INFORMATION AREA

| Address Range | Name of Region        | Standard Device Information                                    |  |  |  |  |

|---------------|-----------------------|----------------------------------------------------------------|--|--|--|--|

|               | MUI0                  |                                                                |  |  |  |  |

|               | MUI1                  |                                                                |  |  |  |  |

|               | MUI2                  |                                                                |  |  |  |  |

|               | MUI3                  |                                                                |  |  |  |  |

| 8100h-8108h   | MUI4                  | Microchip Unique Identifier (9 Words)                          |  |  |  |  |

|               | MUI5                  |                                                                |  |  |  |  |

|               | MUI6                  |                                                                |  |  |  |  |

|               | MUI7                  |                                                                |  |  |  |  |

|               | MUI8                  |                                                                |  |  |  |  |

| 8109h         | MUI9                  | 1 Word Reserved                                                |  |  |  |  |

|               | EUI0                  |                                                                |  |  |  |  |

| 810Ah-8111h   | EUI1                  |                                                                |  |  |  |  |

|               | EUI2                  | 1                                                              |  |  |  |  |

|               | EUI3                  |                                                                |  |  |  |  |

|               | EUI4                  | Unassigned (8 Words)                                           |  |  |  |  |

|               | EUI5                  |                                                                |  |  |  |  |

|               | EUI6                  |                                                                |  |  |  |  |

|               | EUI7                  |                                                                |  |  |  |  |

| 8112h         | TSLR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8113h         | TSLR2                 | Temperature indicator ADC reading at 90°C (low-range setting)  |  |  |  |  |

| 8114h         | TSLR3                 | Unassigned(1 word)                                             |  |  |  |  |

| 8115h         | TSHR1                 | Unassigned (1 word)                                            |  |  |  |  |

| 8116h         | TSHR2                 | Temperature indicator ADC reading at 90°C (high-range setting) |  |  |  |  |

| 8117h         | TSHR3                 | Unassigned (1 Word)                                            |  |  |  |  |

| 8118h         | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)                 |  |  |  |  |

| 8119h         | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)                 |  |  |  |  |

| 811Ah         | FVRA4X <sup>(1)</sup> | ADC FVR1 Output Voltage for 4x setting (in mV)                 |  |  |  |  |

| 811Bh         | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV)          |  |  |  |  |

| 811Ch         | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV)          |  |  |  |  |

| 811Dh         | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV)          |  |  |  |  |

| 811Eh-811Fh   |                       | Unassigned (1 Word)                                            |  |  |  |  |

**Note 1:** Value not present on LF devices.

| U-0                                   | U-0                                     | U-0 | U-0 | U-0                                             | U-0              | R/W/HC-1/u       | R/W/HC-q/u   |  |  |

|---------------------------------------|-----------------------------------------|-----|-----|-------------------------------------------------|------------------|------------------|--------------|--|--|

| —                                     | —                                       | _   | _   | —                                               | —                | MEMV             | VBATBOR      |  |  |

| bit 7                                 |                                         |     |     |                                                 | ·                |                  | bit 0        |  |  |

|                                       |                                         |     |     |                                                 |                  |                  |              |  |  |

| Legend:                               |                                         |     |     |                                                 |                  |                  |              |  |  |

| HC = Bit is cleared by hardware       |                                         |     |     | HS = Bit is set by hardware                     |                  |                  |              |  |  |

| R = Readable bit                      | R = Readable bit W = Writable bit       |     |     | Vritable bit U = Unimplemented bit, read as '0' |                  |                  |              |  |  |

| u = Bit is unchan                     | u = Bit is unchanged x = Bit is unknown |     |     | -m/n = Value                                    | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |     |     | q = Value der                                   | pends on conditi | ion              |              |  |  |

#### REGISTER 8-3: PCON1: POWER CONTROL REGISTER 1

| bit 7-2 | Unimplemented: Read as '0'.                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | <b>MEMV:</b> Memory Violation Flag bit                                                                                                                           |

|         | 1 = No Memory Violation Reset occurred or set to '1' by firmware                                                                                                 |

| bit 0   | <ul> <li>0 = A Memory Violation Reset occurred (set '0' in hardware when a Memory Violation occurs)</li> <li>VBATBOR: VBAT Brown-Out Reset Status Bit</li> </ul> |

| bit o   | 1 = No VBAT Brown-out Reset occurred.                                                                                                                            |

|         | 0 = A VBAT Brown-out Reset occurred.                                                                                                                             |

## 8.17 VBAT System

The VBAT subsystem allows the RTCC and SOSC to run from a battery connected to the VBAT pin in the event of a VDD failure. Typically, the battery is a 3V coin cell, however the system is designed to operate over the entire VDD voltage range. If VDD is greater than VBAT, the RTCC and SOSC will be powered by VDD. If VDD is less than VBAT, the RTCC and SOSC will switch over to VBAT. See Table 4-5 and Table 4-8 for more information on the VBAT registers.

| Note: | It should be noted that in this second<br>scenario, VDD may still be in the valid<br>operating range, but anytime the VDD<br>drops below VBAT, the RTCC and SOSC |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | will switch over to VBAT. This means that<br>in a system with a 3V battery and a 2.8V<br>VDD, the RTCC and SOSC will run off<br>VBAT even when VDD is present.   |

#### 8.17.1 VBAT GPR SEMAPHORE REGISTERS

The VBAT voltage domain offers the user four registers: VB0GPR, VB1GPR, VB3GPR and VB4GPR. These registers can be used by firmware to write any information that needs to survive a VDD failure. As long as either VDD or VBAT is valid, these registers will hold the last value written.

# 12.6 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the OST, if enabled, completes. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

## TABLE 12-2: WWDT CLEARING CONDITIONS

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 4.3.2.1 "STATUS Register" for more information.

| Conditions                                       | WWDT       |

|--------------------------------------------------|------------|

| WDTE<1:0> = 00                                   |            |

| WDTE<1:0> = 01 and SWDTEN = 0                    |            |

| WDTE<1:0> = 10 and enter Sleep                   | Cleared    |

| CLRWDT Command                                   | Cleared    |

| Oscillator Fail Detected                         |            |

| Exit Sleep + System Clock = SOSC, EXTOSC, INTOSC |            |

| Change INTOSC divider (IRCF bits)                | Unaffected |

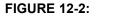

#### WINDOW PERIOD AND DELAY

# 13.2 Data EEPROM Memory

Data EEPROM Memory consists of 256 bytes of user data memory. The EEPROM provides storage locations for 8-bit user defined data. EEPROM can be read and/or written through:

- FSR/INDF indirect access (Section 13.3 "FSR and INDF Access")

- NVMREG access (Section 13.4 "NVMREG Access")

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Unlike PFM, which must be written to by row, EEPROM can be written to word by word.

## 13.3 FSR and INDF Access

The FSR and INDF registers allow indirect access to the PFM.

#### 13.3.1 FSR READ

With the intended address loaded into an FSR register a MOVIW instruction or read of INDF will read data from the PFM.

Reading from NVM requires one instruction cycle. The CPU operation is suspended during the read, and resumes immediately after. Read operations return a single byte of memory.

#### 13.3.2 FSR WRITE

Writing/erasing the NVM through the FSR registers (ex. MOVWI instruction) is not supported in the PIC16(L)F19155/56/75/76/85/86 devices.

## 13.4 NVMREG Access

The NVMREG interface allows read/write access to all the locations accessible by FSRs, and also read/write access to the User ID locations, and read-only access to the device identification, revision, and Configuration data.

Writing, or erasing of NVM via the NVMREG interface is prevented when the device is write-protected.

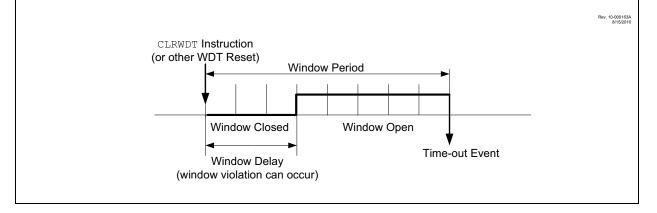

### 13.4.1 NVMREG READ OPERATION

To read a NVM location using the NVMREG interface, the user must:

- Clear the NVMREGS bit of the NVMCON1 register if the user intends to access PFM locations, or set NMVREGS if the user intends to access User ID, or Configuration locations.

- Write the desired address into the NVMADRH:NVMADRL register pair (Table 13-2).

- 3. Set the RD bit of the NVMCON1 register to initiate the read.

Once the read control bit is set, the CPU operation is suspended during the read, and resumes immediately after. The data is available in the very next cycle, in the NVMDATH:NVMDATL register pair; therefore, it can be read as two bytes in the following instructions.

NVMDATH:NVMDATL register pair will hold this value until another read or until it is written to by the user.

Upon completion, the RD bit is cleared by hardware.

# FIGURE 13-1:

#### FLASH PROGRAM MEMORY READ FLOWCHART

# 14.0 I/O PORTS

#### TABLE 14-1: PORT AVAILABILITY PER DEVICE

| Device            | PORTA | PORTB | PORTC | РОКТD | PORTE | PORTF |

|-------------------|-------|-------|-------|-------|-------|-------|

| PIC16(L)F19155/56 | •     | ٠     | ٠     | _     | ٠     | -     |

| PIC16(L)F19175/66 | •     | ٠     | ٠     | ٠     | ٠     | -     |

| PIC16(L)F19185/86 | •     | ٠     | •     | •     | •     | ٠     |

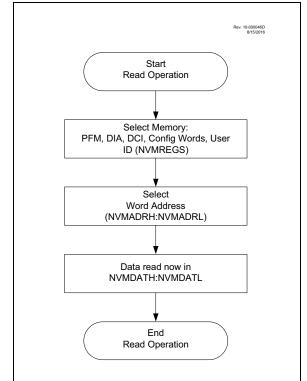

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

#### FIGURE 14-1: GENERIC I/O PORT OPERATION

# 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. The analog functions are always available regardless of ANSEL. The ANSEL bit disables the digital input functions, as shown in Figure 14-1. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

| R/W-0/0              | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0                                            | R/W-0/0          | R/W-0/0 | R/W-0/0      |

|----------------------|---------|----------------------|---------|----------------------------------------------------|------------------|---------|--------------|

| WPUA7                | WPUA6   | WPUA5 <sup>(2)</sup> | WPUA4   | WPUA3                                              | WPUA2            | WPUA1   | WPUA0        |

| bit 7                |         |                      |         |                                                    |                  |         | bit 0        |

|                      |         |                      |         |                                                    |                  |         |              |

| Legend:              |         |                      |         |                                                    |                  |         |              |

| R = Readable bit     |         | W = Writable         | bit     | U = Unimpler                                       | mented bit, read | as '0'  |              |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at POR and BOR/Value at all other Res |                  |         | other Resets |

| '1' = Bit is set     |         | '0' = Bit is clea    | ared    |                                                    |                  |         |              |

#### REGISTER 14-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **2:** Bit not used when  $\overline{VBATEN} = 0$ .

### REGISTER 14-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| ODCA7   | ODCA6   | —   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | ODCA<7:6>: PORTA Open-Drain Enable bits                                     |

|---------|-----------------------------------------------------------------------------|

|         | For RA<7:6> pins, respectively                                              |

|         | 1 = Port pin operates as open-drain drive (sink current only)               |

|         | 0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 5   | Unimplemented: Read as '0'                                                  |

| bit 4-0 | ODCA<4:0>: PORTA Open-Drain Enable bits                                     |

|         | For RA<4:0> pins, respectively                                              |

|         | 1 = Port pin operates as open-drain drive (sink current only)               |

|         | 0 = Port pin operates as standard push-pull drive (source and sink current) |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 222                 |

| TRISA   | TRISA7  | TRISA6  | (1)     | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 222                 |

| LATA    | LATA7   | LATA6   | —       | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 223                 |

| ANSELA  | ANSA7   | ANSA6   | —       | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 223                 |

| WPUA    | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 224                 |

| ODCONA  | ODCA7   | ODCA6   | —       | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 224                 |

| SLRCONA | SLRA7   | SLRA6   | —       | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 225                 |

| INLVLA  | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 225                 |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** Unimplemented, read as '1'.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTD   | RD7     | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     | 241                 |

| TRISD   | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  | 241                 |

| LATD    | LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   | 242                 |

| ANSELD  | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   | 242                 |

| WPUD    | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   | 243                 |

| ODCOND  | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   | 243                 |

| SLRCOND | SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   | 244                 |

| INLVLD  | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 244                 |

## TABLE 14-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

Note 1: Unimplemented, read as '1'.

## 14.10 PORTE Registers

#### 14.10.1 DATA REGISTER

PORTE is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISE (Register 14-2). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTE.

Reading the PORTE register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch.

The PORT data latch LATE (Register 14-3) holds the output port data, and contains the latest value of a LATE or PORTE write.

## EXAMPLE 14-4: INITIALIZING PORTE

| ; initia<br>; other                           | <pre>; This code example illustrates<br/>; initializing the PORTE register. The<br/>; other ports are initialized in the same<br/>; manner.</pre> |                                                                                                                             |  |  |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BANKSEL<br>CLRF<br>BANKSEL<br>CLRF<br>BANKSEL | PORTE<br>LATE<br>LATE<br>ANSELE<br>ANSELE<br>TRISE<br>B'00111000'                                                                                 | ;<br>;Init PORTE<br>;Data Latch<br>;<br>;<br>;digital I/O<br>;<br>;Set RE<5:3> as inputs<br>;and set RE<2:0> as<br>;outputs |  |  |  |  |  |

### 14.10.2 DIRECTION CONTROL

The TRISE register (Register 14-2) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 14.10.3 OPEN-DRAIN CONTROL

The ODCONE register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONE bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONE bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

## 14.10.4 SLEW RATE CONTROL

The SLRCONE register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONE bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONE bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 14.10.5 INPUT THRESHOLD CONTROL

The INLVLE register (Register 14-8) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 39-4 for more information on threshold levels.

| Note: | Changing the input threshold selection      |

|-------|---------------------------------------------|

|       | should be performed while all peripheral    |

|       | modules are disabled. Changing the          |

|       | threshold level during the time a module is |

|       | active may inadvertently generate a         |

|       | transition associated with an input pin,    |

|       | regardless of the actual voltage level on   |

|       | that pin.                                   |

# TABLE 19-2: COMPUTATION MODES

|                    |      | Bit Clear Conditions                         | Value after Trigg                                                            | er completion                                           | TI                                                                                                                                                          | nreshold Opera    | tions             | Value at     | ADTIF Interrupt        |       |

|--------------------|------|----------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|--------------|------------------------|-------|

| Mode               | ADMD | ACC and CNT                                  | ACC                                                                          | CNT                                                     | Retrigger                                                                                                                                                   | Threshold<br>Test | Interrupt         | OV           | FLTR                   | CNT   |

| Basic              | 0    | ADACLR = 1                                   | Unchanged                                                                    | Unchanged                                               | No                                                                                                                                                          | Every<br>Sample   | If threshold=true | N/A          | N/A                    | count |

| Accumulate         | 1    | ADACLR = 1                                   | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT,<br>otherwise: CNT+1                 | No                                                                                                                                                          | Every<br>Sample   | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> | count |

| Average            | 2    | ADACLR = 1 or CNT>=RPT<br>at GO or retrigger | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT,<br>otherwise: CNT+1                 | No                                                                                                                                                          | lf<br>CNT>=RPT    | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> |       |

| Burst<br>Average   | 3    | ADACLR = 1 or GO set or<br>retrigger         | Each repetition: same as<br>Average<br>End with sum of all<br>samples        | Each repetition: same as<br>Average<br>End with CNT=RPT | Repeat while<br>CNT <rpt< td=""><td>lf<br/>CNT&gt;=RPT</td><td>If threshold=true</td><td>ACC Overflow</td><td>ACC/2<sup>ADCRS</sup></td><td>RPT</td></rpt<> | lf<br>CNT>=RPT    | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> | RPT   |

| Low-pass<br>Filter | 4    | ADACLR = 1                                   | S+ACC-ACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ACC-ACC/2 <sup>ADCRS</sup> | Count up, stop counting<br>when CNT = 0xFF              | No                                                                                                                                                          | lf<br>CNT>=RPT    | If threshold=true | ACC Overflow | Filtered Value         | count |

PIC16(L)F19155/56/75/76/85/86

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = PREV and S2 = ADRES.

# PIC16(L)F19155/56/75/76/85/86

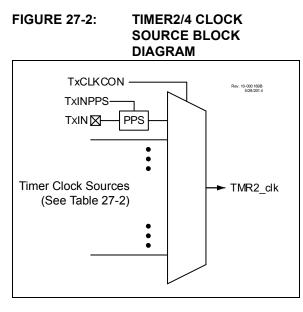

# 27.1 Timer2/4 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset

- · External Reset Source event that resets the timer.

Note: TMR2 is not cleared when T2CON is written.

### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2

to 00h on the next rising TMR2\_clk edge and increments the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

## 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

# 27.2 Timer2/4 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 29.0 "Capture/Compare/PWM Modules"** for more details on setting up Timer2/4 for use with the CCP, as well as the timing diagrams in **Section 27.5 "Operation Examples"** for examples of how the varying Timer2 modes affect CCP PWM output.

## 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, which-ever of the two starts the timer.

| R/W/HC-0/0       | R/W-0/0                                                | U-0                                                    | U-0           | R/W-0/0       | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |

|------------------|--------------------------------------------------------|--------------------------------------------------------|---------------|---------------|------------------|----------------|--------------|--|--|

| SMTxGO           | REPEAT                                                 | —                                                      | —             |               | MODE             | <3:0>          |              |  |  |

| bit 7            |                                                        |                                                        |               |               |                  |                | bit          |  |  |

| Logondu          |                                                        |                                                        |               |               |                  |                |              |  |  |

| Legend:          | anad by bandy                                          |                                                        |               |               |                  |                |              |  |  |

| HC = Bit is cle  | -                                                      |                                                        | L :4          |               | et by hardware   | -l (O)         |              |  |  |

| R = Readable     |                                                        | W = Writable                                           |               | •             | nented bit, read |                |              |  |  |

| u = Bit is unch  | anged                                                  | x = Bit is unkn                                        |               |               |                  | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                                                        | '0' = Bit is clea                                      | ared          | q = Value dep | pends on condi   | tion           |              |  |  |

| bit 7            | 1 = Incremer                                           | MT GO Data Ac<br>nting, acquiring<br>nting, acquiring  | data is enabl |               |                  |                |              |  |  |

| bit 6            | 1 = Repeat D                                           | /IT Repeat Acqu<br>Data Acquisition<br>cquisition mode | mode is ena   |               |                  |                |              |  |  |

| bit 5-4          | Unimpleme                                              | nted: Read as 'o                                       | )'            |               |                  |                |              |  |  |

| · · · ·          |                                                        | SMT Operation<br>erved                                 | Mode Selec    | ot bits       |                  |                |              |  |  |

|                  | •                                                      |                                                        |               |               |                  |                |              |  |  |

|                  | 1011 = Reserved<br>1010 = Windowed counter             |                                                        |               |               |                  |                |              |  |  |

|                  | 1010 = Windowed counter                                |                                                        |               |               |                  |                |              |  |  |

|                  | 1000 = Counter                                         |                                                        |               |               |                  |                |              |  |  |

|                  | 0111 = Capture<br>0110 = Time of flight                |                                                        |               |               |                  |                |              |  |  |

|                  | 0110 = Time of flight<br>0101 = Gated windowed measure |                                                        |               |               |                  |                |              |  |  |

|                  | 0100 = Windowed measure                                |                                                        |               |               |                  |                |              |  |  |

|                  | •                                                      | and low time m<br>od and Duty-Cyc                      |               |               |                  |                |              |  |  |

|                  |                                                        | M = M M + M + M + M + M + M + M + M + M                | JE ACQUISITIC | 11            |                  |                |              |  |  |

|                  | 00010 = r end                                          |                                                        |               |               |                  |                |              |  |  |

#### REGISTER 28-2: SMTxCON1: SMT CONTROL REGISTER 1

|                                       |                                         | -            | _       |                                                       |                  |          |         |

|---------------------------------------|-----------------------------------------|--------------|---------|-------------------------------------------------------|------------------|----------|---------|

| R/W-0/0                               | R/W-0/0                                 | R/W-0/0      | R/W-0/0 | R/W-0/0                                               | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|                                       |                                         |              | SMTxTI  | MR<7:0>                                               |                  |          |         |

| bit 7                                 |                                         |              |         |                                                       |                  |          | bit 0   |

|                                       |                                         |              |         |                                                       |                  |          |         |

| Legend:                               |                                         |              |         |                                                       |                  |          |         |

| R = Readable                          | bit                                     | W = Writable | bit     | U = Unimpler                                          | nented bit, read | d as '0' |         |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |              |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |

| '1' = Bit is set '0' = Bit is cleared |                                         |              | ared    |                                                       |                  |          |         |

bit 7-0 SMTxTMR<7:0>: Significant bits of the SMT Counter – Low Byte

#### **REGISTER 28-8:** SMTxTMRH: SMT TIMER REGISTER – HIGH BYTE

| R/W-0/0      | R/W-0/0                | R/W-0/0      | R/W-0/0 | R/W-0/0                            | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|--------------|------------------------|--------------|---------|------------------------------------|------------------|----------|---------|

| -            |                        |              | SMTxTN  | IR<15:8>                           |                  |          |         |

| bit 7        |                        |              |         |                                    |                  |          | bit 0   |

|              |                        |              |         |                                    |                  |          |         |

| Legend:      |                        |              |         |                                    |                  |          |         |

|              | e bit W = Writable bit |              |         | U = Unimplemented bit, read as '0' |                  |          |         |

| R = Readable | bit                    | W = Writable | bit     | U = Unimplen                       | nented bit, read | d as '0' |         |

bit 7-0 SMTxTMR<15:8>: Significant bits of the SMT Counter – High Byte

'0' = Bit is cleared

#### REGISTER 28-9: SMTxTMRU: SMT TIMER REGISTER – UPPER BYTE

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | SMTxTMF | R<23:16> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxTMR<23:16>: Significant bits of the SMT Counter – Upper Byte

'1' = Bit is set

#### 31.1.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 31-2. This alternation creates the push-pull effect required for driving some transformer-based power supply designs.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWG1A.

The unused outputs CWG1C and CWG1D drive copies of CWG1A and CWG1B, respectively, but with polarity controlled by the POLC and POLD bits of the CWG1CON1 register, respectively.

#### 31.1.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. In Forward Full-Bridge mode, CWG1A is driven to its active state, CWG1B and CWG1C are driven to their inactive state, and CWG1D is modulated by the input signal. In Reverse Full-Bridge mode, CWG1C is driven to its active state, CWG1A and CWG1D are driven to their inactive states, and CWG1B is modulated by the input signal. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or vice-versa. This dead-band control is described in Section 31.5 "Dead-Band Control", with additional details in Section 31.6 "Rising Edge and Reverse Dead Band" and Section 31.7 "Falling Edge and Forward Dead Band".

The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWG1CON0 while keeping MODE<2:1> static, without disabling the CWG module.

## 31.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources (See Register 31-9).

The input sources are selected using the CWG1ISM register.

## 31.4 Output Control

### 31.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

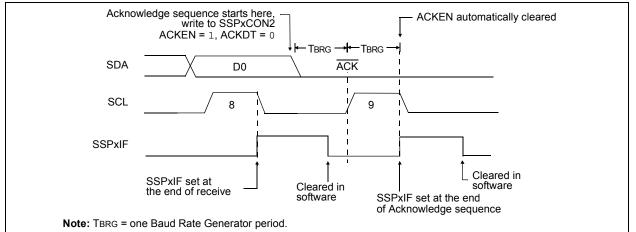

#### 33.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into IDLE mode (Figure 33-30).

### 33.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

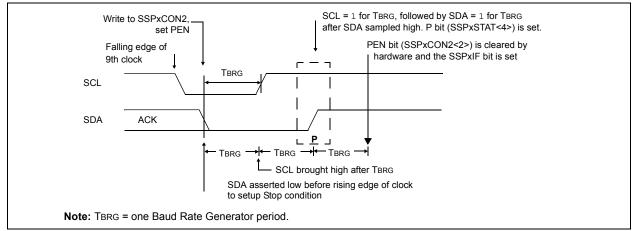

#### 33.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 33-31).

## 33.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## FIGURE 33-30: ACKNOWLEDGE SEQUENCE WAVEFORM

### FIGURE 33-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

# PIC16(L)F19155/56/75/76/85/86

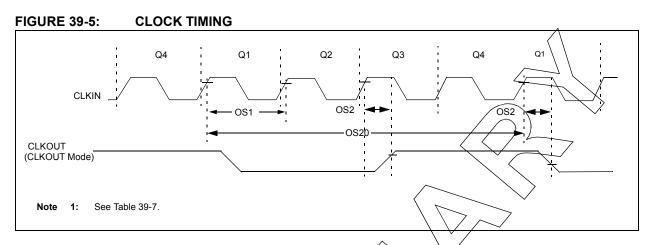

# TABLE 39-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No. | Sym.                | Characteristic         | Min.                | Турт               | Max.       | Units | Conditions       |

|---------------|---------------------|------------------------|---------------------|--------------------|------------|-------|------------------|

| ECL Os        | cillator            |                        |                     |                    | $\searrow$ |       |                  |

| OS1           | F <sub>ECL</sub>    | Clock Frequency        |                     | $\square$          | > 500      | kHz   |                  |

| OS2           | T <sub>ECL_DC</sub> | Clock Duty Cycle       | 40                  |                    | 60         | %     |                  |

| ECM Os        | scillator           |                        | $\sim$              | $\bigtriangledown$ |            |       | •                |

| OS3           | F <sub>ECM</sub>    | Clock Frequency        |                     | $\rangle -$        | 4          | MHz   |                  |

| OS4           | T <sub>ECM_DC</sub> | Clock Duty Cycle       | 40                  | —                  | 60         | %     |                  |

| ECH Os        | cillator            |                        | · · · · ·           |                    |            |       | ·                |

| OS5           | F <sub>ECH</sub>    | Clock Frequency        | $\rangle - \langle$ |                    | 32         | MHz   |                  |

| OS6           | T <sub>ECH_DC</sub> | Clock Duty Sycle       | 40                  | —                  | 60         | %     |                  |

| System        | Oscillator          |                        | •                   |                    |            |       |                  |

| OS20          | F <sub>OSC</sub>    | System Clock Frequency | —                   | —                  | 32         | MHz   | (Note 2, Note 3) |

| OS21          | F <sub>CY</sub>     |                        | -                   | Fosc/4             | —          | MHz   |                  |

| OS22          | T <sub>CY</sub>     | Instruction Period     | 125                 | 1/F <sub>CY</sub>  | —          | ns    |                  |

\* These parameters are characterized but not tested.

† Data in "Jyp" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices. The system clock frequency (Fosc) is selected by the "main clock switch controls" as described in Section 9.0

The system clock frequency (Fosc) is selected by the "main clock switch controls" as described in Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)".

The system clock frequency (Fosc) must meet the voltage requirements defined in the Section 39.2 "Standard Operating Conditions".

3:

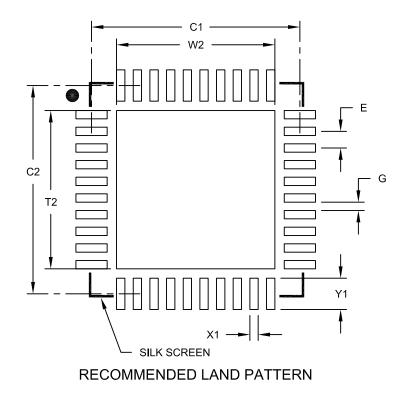

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimensior                  | Limits      | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.40 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 3.80 |

| Optional Center Pad Length | T2          |          |      | 3.80 |

| Contact Pad Spacing        | C1          |          | 5.00 |      |

| Contact Pad Spacing        | C2          |          | 5.00 |      |

| Contact Pad Width (X40)    | X1          |          |      | 0.20 |

| Contact Pad Length (X40)   | Y1          |          |      | 0.75 |

| Distance Between Pads      | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B