Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 31x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

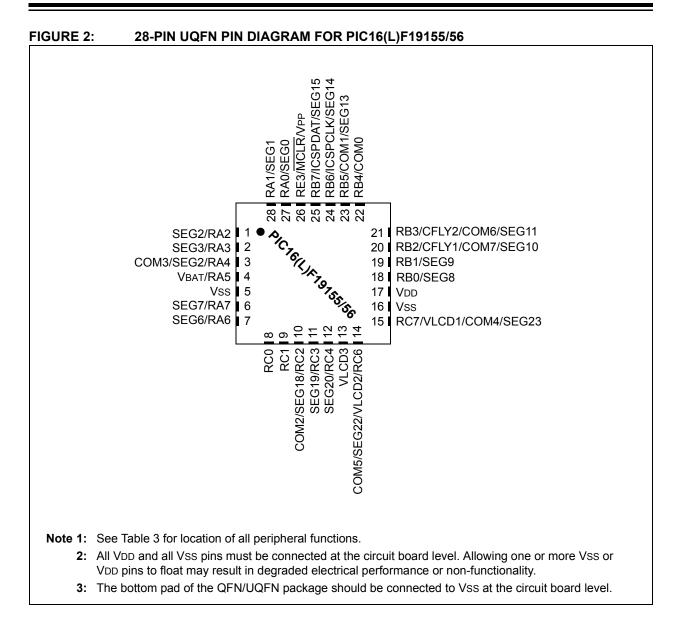

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19175-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F19155/56/75/76/85/86

| Address | Name     | Bit 7  | Bit 6           | Bit 5 | Bit 4          | Bit 3               | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|----------|--------|-----------------|-------|----------------|---------------------|-----------|-----------|-----------|-----------------------|----------------------------|

| Bank 9  |          |        |                 |       |                |                     |           |           |           |                       |                            |

|         |          |        |                 | CPU   | CORE REGISTERS | : see Table 4-3 for | specifics |           |           |                       |                            |

|         | 1        |        |                 |       |                | ,                   |           |           |           | -                     | 1                          |

| 48Ch    | SMT1TMRL |        |                 |       | SMT1           | ſMR                 |           |           |           | 0000 0000             | 0000 0000                  |

| 48Dh    | SMT1TMRH |        | SMT1TMR         |       |                |                     |           |           |           |                       |                            |

| 48Eh    | SMT1TMRU |        | SMT1TMR         |       |                |                     |           |           |           |                       |                            |

| 48Fh    | SMT1CPRL |        |                 |       | CPI            | R                   |           |           |           | xxxx xxxx             | XXXX XXXX                  |

| 490h    | SMT1CPRH |        |                 |       | CPI            | R                   |           |           |           | xxxx xxxx             | XXXX XXXX                  |

| 491h    | SMT1CPRU |        |                 |       | CPI            | R                   |           |           |           | xxxx xxxx             | xxxx xxxx                  |

| 492h    | SMT1CPWL |        | CPW             |       |                |                     |           |           |           |                       |                            |

| 493h    | SMT1CPWH |        | CPW             |       |                |                     |           |           |           |                       |                            |

| 494h    | SMT1CPWU |        |                 |       | CP\            | N                   |           |           |           | xxxx xxxx             | xxxx xxxx                  |

| 495h    | SMT1PRL  |        |                 |       | SMT1           | PR                  |           |           |           | 1111 1111             | 1111 1111                  |

| 496h    | SMT1PRH  |        |                 |       | SMT1           | PR                  |           |           |           | 1111 1111             | 1111 1111                  |

| 497h    | SMT1PRU  |        |                 |       | SMT1           | PR                  |           |           |           | 1111 1111             | 1111 1111                  |

| 498h    | SMT1CON0 | EN     | —               | STP   | WPOL           | SPOL                | CPOL      | SMT1      | PS<1:0>   | 0-00 0000             | 0-00 0000                  |

| 499h    | SMT1CON1 | SMT1GO | REPEAT          | _     | _              |                     | MOD       | E<3:0>    |           | 00 0000               | 00 0000                    |

| 49Ah    | SMT1STAT | CPRUP  | CPWUP           | RST   | _              | _                   | TS        | WS        | AS        | 000000                | 000000                     |

| 49Bh    | SMT1CLK  | —      | —               |       | —              | —                   |           | CSEL<2:0> |           | 0000 0000             | 0000 0000                  |

| 49Ch    | SMT1SIG  |        |                 |       |                |                     |           |           | 0000 0000 | 0000 0000             |                            |

| 49Dh    | SMT1WIN  | —      | — — — WSEL<4:0> |       |                |                     |           |           |           |                       | 0000 0000                  |

| 49Eh    |          |        |                 |       | Unimpler       | nented              |           |           |           |                       |                            |

| 49Fh    | _        |        |                 |       | Unimpler       | nented              |           |           |           |                       |                            |

# TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, g = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

| Address    | Name       | Bit 7    | Bit 6         | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|------------|------------|----------|---------------|----------|----------|----------|----------|----------|----------|-----------------------|----------------------------|

| Bank 60 (0 | Continued) |          |               |          |          |          |          |          |          |                       |                            |

| 1E37h      | CLC4GLS3   | LC4G4D4T | LC4G4D4N      | LC4G4D3T | LC4G4D3N | LC4G4D2T | LC4G4D2N | LC4G4D1T | LC4G4D1N | xxxx xxxx             | uuuu uuuu                  |

| 1E38h      | RF0PPS     | _        | _             | _        | RF0PPS4  | RF0PPS3  | RF0PPS2  | RF0PPS1  | RF0PPS0  | x xxxx                | uu uuuu                    |

| 1E39h      | RF1PPS     |          |               |          |          |          |          |          | xx xxxx  | uu uuuu               |                            |

| 1E3Ah      | RF2PPS     |          | _             | —        | RF2PPS4  | RF2PPS3  | RF2PPS2  | RF2PPS1  | RF2PPS0  | xx xxxx               | uu uuuu                    |

| 1E3Bh      | RF3PPS     | _        | _             | _        | RF3PPS4  | RF3PPS3  | RF3PPS2  | RF3PPS1  | RF3PPS0  | xx xxxx               | uu uuuu                    |

| 1E3Ch      | RF4PPS     |          | _             |          | RF4PPS4  | RF4PPS3  | RF4PPS2  | RF4PPS1  | RF4PPS0  | xx xxxx               | uu uuuu                    |

| 1E3Dh      | RF5PPS     |          | _             |          | RF5PPS4  | RF5PPS3  | RF5PPS2  | RF5PPS1  | RF5PPS0  | xx xxxx               | uu uuuu                    |

| 1E3Eh      | RF6PPS     | _        | _             | _        | RF6PPS4  | RF6PPS3  | RF6PPS2  | RF6PPS1  | RF6PPS0  | xx xxxx               | uu uuuu                    |

| 1E3Fh      | RF7PPS     | _        | —             |          | RF7PPS4  | RF7PPS3  | RF7PPS2  | RF7PPS1  | RF7PPS0  | xx xxxx               | uu uuuu                    |

| 1E40h      | —          |          | Unimplemented |          |          |          |          |          |          |                       |                            |

| 1E41h      | _          |          | Unimplemented |          |          |          |          |          |          |                       |                            |

| 1E42h      | _          |          | Unimplemented |          |          |          |          |          |          |                       |                            |

| 1E43h      | —          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E44h      | —          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E45h      | _          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E46h      | —          |          |               |          | Unimpler | mented   |          |          |          |                       |                            |

| 1E47h      | _          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E48h      | _          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E49h      | _          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

| 1E4Ah      | —          |          |               |          | Unimpler | mented   |          |          |          |                       |                            |

| 1E4Bh      | —          |          | Unimplemented |          |          |          |          |          |          |                       |                            |

| 1E4Ch      | —          |          |               |          | Unimpler | mented   |          |          |          |                       |                            |

| 1E4Dh      | —          |          |               |          | Unimpler | mented   |          |          |          |                       |                            |

| 1E4Eh      | —          |          |               |          | Unimpler | mented   |          |          |          |                       |                            |

| 1E4Fh      | —          |          |               |          | Unimplei | mented   |          |          |          |                       |                            |

PIC16(L)F19155/56/75/76/85/86

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

# 5.2 Register Definitions: Configuration Words

| REGISTER         | <b>CO</b>                                                                                                                                                                                                                                                                                                          | NFIGURATIO                                                                                                                                                                      |                                                                                      |                                                    |                      |                  |             |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|------------------|-------------|--|--|--|

|                  |                                                                                                                                                                                                                                                                                                                    | R/P-1                                                                                                                                                                           | U-1                                                                                  | R/P-1                                              | R/P-1                | R/P-1            | R/P-1       |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | FCMEN                                                                                                                                                                           |                                                                                      | CSWEN                                              | LCDPEN               | VBATEN           | CLKOUTEN    |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | bit 13                                                                                                                                                                          |                                                                                      |                                                    |                      |                  | bit         |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 | D/D 4                                                                                | 11.4                                               |                      |                  |             |  |  |  |

| U-1              | R/P-1                                                                                                                                                                                                                                                                                                              | R/P-1                                                                                                                                                                           | R/P-1                                                                                | U-1                                                | R/P-1                | R/P-1            | R/P-1       |  |  |  |

|                  | RSTOSC2                                                                                                                                                                                                                                                                                                            | RSTOSC2 RSTOSC1 RSTOSC0 — FEXTOSC2 FEXTOSC1 FEXTOSC0                                                                                                                            |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  | bit         |  |  |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                              | P = Programma                                                                                                                                                                   | ble bit                                                                              | x = Bit is unkno                                   | wn U = Un            | mplemented bit,  | read as '1' |  |  |  |

| '0' = Bit is cle |                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                |                                                                                      | W = Writable bi                                    |                      | le when blank or |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 13           | FCMEN: Fail-S<br>1 = FSCM tin<br>0 = FSCM tin                                                                                                                                                                                                                                                                      |                                                                                                                                                                                 | or Enable bit                                                                        |                                                    |                      |                  |             |  |  |  |

| bit 12           | Unimplement                                                                                                                                                                                                                                                                                                        | ed: Read as '1'                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 11           | CSWEN: Cloc                                                                                                                                                                                                                                                                                                        | k Switch Enable I                                                                                                                                                               | oit                                                                                  |                                                    |                      |                  |             |  |  |  |

|                  | 0                                                                                                                                                                                                                                                                                                                  | NOSC and NDI                                                                                                                                                                    |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | C and NDIV bits                                                                                                                                                                 |                                                                                      |                                                    | ware                 |                  |             |  |  |  |

| bit 10           |                                                                                                                                                                                                                                                                                                                    | Charge Pump N<br>nds to enable I C                                                                                                                                              |                                                                                      |                                                    | eration              |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | <ul> <li>L = User intends to enable LCD Charge Pump during LCD operation</li> <li>D = LCD Charge Pump forced off</li> </ul>                                                     |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 9            |                                                                                                                                                                                                                                                                                                                    | AT Pin Enable bit                                                                                                                                                               |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | ctionality is disat                                                                                                                                                             |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | ictionality is enab                                                                                                                                                             | •                                                                                    | as a battery con                                   | nected to it         |                  |             |  |  |  |

| bit 8            |                                                                                                                                                                                                                                                                                                                    | Clock Out Enable                                                                                                                                                                |                                                                                      | ablady                                             |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | EC (high, mid or<br>function is disable                                                                                                                                         |                                                                                      |                                                    | DSC2                 |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | function is enable                                                                                                                                                              | ,                                                                                    |                                                    |                      |                  |             |  |  |  |

|                  | Otherwise:                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 7            | This bit is igno                                                                                                                                                                                                                                                                                                   | red.<br>ed: Read as '1'                                                                                                                                                         |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  | •                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

| bit 6-4          |                                                                                                                                                                                                                                                                                                                    | >: Power-up Defa                                                                                                                                                                |                                                                                      |                                                    | oscillator first use | d by user softwa | re          |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | SC operating per                                                                                                                                                                |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    | OSC with HFFR                                                                                                                                                                   | <b>Q =</b> 4'b0000                                                                   |                                                    |                      |                  |             |  |  |  |

|                  | 101 = LFINT                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  | 100 = SOSC<br>011 = Reser                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 | with EXTOSC o                                                                        | perating per FE                                    | (TOSC bits           |                  |             |  |  |  |

|                  | 010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits<br>001 = HFINTOSC with 2x PLL = 32 MHz, with HFFRQ = '101' and CDIV = '0000'                                                                                                                                                                      |                                                                                                                                                                                 |                                                                                      |                                                    |                      |                  |             |  |  |  |

|                  | 001 = HFINT                                                                                                                                                                                                                                                                                                        | OSC with 2x PLI                                                                                                                                                                 | _ = 32 MHz, wit                                                                      | h HFFRQ = '101                                     | ' and CDIV = '00     | 00'              |             |  |  |  |

|                  | 001 = HFIN<br>000 = HFIN                                                                                                                                                                                                                                                                                           | FOSC with 2x PLI                                                                                                                                                                | _ = 32 MHz, wit                                                                      | h HFFRQ = '101                                     | ' and CDIV = '00)    | 00'              |             |  |  |  |

| bit 3            | 001 = HFIN<br>000 = HFIN<br>Unimplement                                                                                                                                                                                                                                                                            | TOSC with 2x PLI<br>TOSC with OSCF<br>ed: Read as '1'                                                                                                                           | _ = 32 MHz, wit<br>RQ = 32 MHz a                                                     | h HFFRQ = '101<br>and CDIV = 1:1                   |                      | 00'              |             |  |  |  |

| bit 3<br>bit 2-0 | 001 = HFIN <sup>-</sup><br>000 = HFIN <sup>-</sup><br>Unimplement<br>FEXTOSC<2:                                                                                                                                                                                                                                    | TOSC with 2x PLI<br>TOSC with OSCF<br>ed: Read as '1'<br>0>:FEXTOSC Ex                                                                                                          | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>ternal Oscillator                                | h HFFRQ = '101<br>and CDIV = 1:1                   |                      | 00'              |             |  |  |  |

|                  | 001 = HFIN <sup>-</sup><br>000 = HFIN <sup>-</sup><br>Unimplement<br>FEXTOSC<2:<br>111 = EC (E                                                                                                                                                                                                                     | FOSC with 2x PLI<br>FOSC with OSCF<br>ed: Read as '1'<br>0>:FEXTOSC Ext<br>xternal Clock) ab                                                                                    | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>rernal Oscillator<br>ove 8 MHz                   | h HFFRQ = '101<br>and CDIV = 1:1<br>Mode Selection |                      | 00,              |             |  |  |  |

|                  | 001 = HFIN<br>000 = HFIN<br>Unimplement<br>FEXTOSC<2:<br>111 = EC (E<br>110 = EC (E                                                                                                                                                                                                                                | TOSC with 2x PLI<br>TOSC with OSCF<br>ed: Read as '1'<br>0>:FEXTOSC Ex                                                                                                          | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>ternal Oscillator<br>ove 8 MHz<br>100 kHz to 8 M | h HFFRQ = '101<br>and CDIV = 1:1<br>Mode Selection |                      | 00,              |             |  |  |  |

|                  | 001 = HFIN<br>000 = HFIN<br>Unimplement<br>FEXTOSC<2:<br>111 = EC (E<br>110 = EC (E<br>101 = EC (E<br>100 = Oscilla                                                                                                                                                                                                | FOSC with 2x PLI<br>FOSC with OSCF<br>ed: Read as '1'<br>D>:FEXTOSC Ext<br>xternal Clock) ab<br>xternal Clock) for<br>xternal Clock) be<br>ator not enabled                     | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>ternal Oscillator<br>ove 8 MHz<br>100 kHz to 8 M | h HFFRQ = '101<br>and CDIV = 1:1<br>Mode Selection |                      | 00,              |             |  |  |  |

|                  | 001 = HFIN<br>000 = HFIN<br>Unimplement<br>FEXTOSC<2:<br>111 = EC (E<br>110 = EC (E<br>101 = EC (E<br>100 = Oscilla<br>011 = Oscilla                                                                                                                                                                               | FOSC with 2x PLI<br>FOSC with OSCF<br>ed: Read as '1'<br>D>:FEXTOSC Ext<br>xternal Clock) ab<br>xternal Clock) for<br>xternal Clock) be<br>ator not enabled<br>ator not enabled | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>ternal Oscillator<br>ove 8 MHz<br>100 kHz to 8 M | h HFFRQ = '101<br>and CDIV = 1:1<br>Mode Selection |                      | 00,              |             |  |  |  |

|                  | 001 =         HFINT           000 =         HFINT           Unimplement         FEXTOSC<2::           111 =         EC (E           110 =         EC (E           101 =         EC (E           101 =         EC (E           101 =         CO (E)           011 =         Oscilla           010 =         Oscilla | FOSC with 2x PLI<br>FOSC with OSCF<br>ed: Read as '1'<br>D>:FEXTOSC Ext<br>xternal Clock) ab<br>xternal Clock) for<br>xternal Clock) be<br>ator not enabled                     | _ = 32 MHz, wit<br>RQ = 32 MHz a<br>ternal Oscillator<br>ove 8 MHz<br>100 kHz to 8 M | h HFFRQ = '101<br>and CDIV = 1:1<br>Mode Selection |                      | 00 <sup>,</sup>  |             |  |  |  |

# REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

| R/W-0/0          | R/W-0/0                                                                                               | R/W-0/0                        | R/W-0/0         | U-0          | U-0              | R/W-0/0          | R/W-0/0      |  |

|------------------|-------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|--------------|------------------|------------------|--------------|--|

| RC2IE            | TX2IE                                                                                                 | RC1IE                          | TX1IE           | _            | —                | BCL1IE           | SSP1IE       |  |

| bit 7            |                                                                                                       | I                              |                 |              |                  |                  | bit 0        |  |

|                  |                                                                                                       |                                |                 |              |                  |                  |              |  |

| Legend:          |                                                                                                       |                                |                 |              |                  |                  |              |  |

| R = Readable     | e bit                                                                                                 | W = Writable                   | bit             | U = Unimpler | mented bit, read | as '0'           |              |  |

| u = Bit is unc   | hanged                                                                                                | x = Bit is unkr                | nown            | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |  |

| '1' = Bit is set | t                                                                                                     | '0' = Bit is cle               | ared            |              |                  |                  |              |  |

| bit 7            |                                                                                                       | RT Receive Inte                | arrupt Epoble   | h:t          |                  |                  |              |  |

| DIL 7            |                                                                                                       | the USART rec                  | •               |              |                  |                  |              |  |

|                  |                                                                                                       | the USART red                  | •               |              |                  |                  |              |  |

| bit 6            | TX2IE: USAF                                                                                           | RT Transmit Inte               | errupt Enable   | bit          |                  |                  |              |  |

|                  | 1 = Enables the USART transmit interrupt                                                              |                                |                 |              |                  |                  |              |  |

|                  |                                                                                                       | the USART tra                  |                 |              |                  |                  |              |  |

| bit 5            |                                                                                                       | RT Receive Inte                | •               |              |                  |                  |              |  |

|                  |                                                                                                       | the USART rec<br>the USART rec |                 |              |                  |                  |              |  |

| bit 4            |                                                                                                       | RT Transmit Inte               |                 |              |                  |                  |              |  |

|                  |                                                                                                       | the USART tra                  | •               |              |                  |                  |              |  |

|                  | 0 = Disables                                                                                          | the USART tra                  | ansmit interrup | ot           |                  |                  |              |  |

| bit 3-2          | Unimplemen                                                                                            | ted: Read as '                 | 0'              |              |                  |                  |              |  |

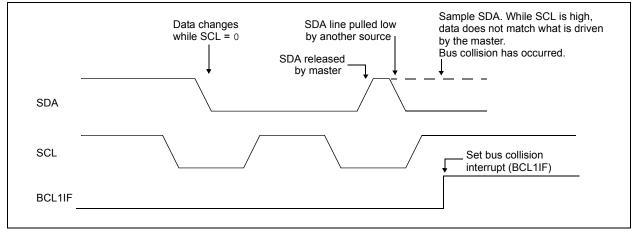

| bit 1            | BCL1IE: MSS                                                                                           | SP1 Bus Collis                 | ion Interrupt E | Enable bit   |                  |                  |              |  |

|                  |                                                                                                       | us collision inte              |                 |              |                  |                  |              |  |

| <b>h</b> # 0     |                                                                                                       | us collision inte              | ·               |              |                  |                  |              |  |

| bit 0            | <b>SSP1IE:</b> Synchronous Serial Port (MSSP1) Interrupt Enable bit<br>1 = Enables the MSSP interrupt |                                |                 |              |                  |                  |              |  |

|                  |                                                                                                       | the MSSP inte                  | •               |              |                  |                  |              |  |

|                  |                                                                                                       |                                |                 |              |                  |                  |              |  |

|                  |                                                                                                       |                                | <b>I</b>        |              |                  |                  |              |  |

|                  | t PEIE of the IN<br>t to enable ar                                                                    |                                |                 |              |                  |                  |              |  |

| 50               |                                                                                                       |                                | on apr          |              |                  |                  |              |  |

#### **REGISTER 10-5: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3**

controlled by PIE1-PIE8.

| TABLE 15-3: | PPS OUTPUT SIGNAL ROUTING OPTIONS |

|-------------|-----------------------------------|

|             |                                   |

|                       | Outrast            |                   |       |       |                   |       | Re    | mappable to | Pins of PO | RTx   |          |           |       |       |       |

|-----------------------|--------------------|-------------------|-------|-------|-------------------|-------|-------|-------------|------------|-------|----------|-----------|-------|-------|-------|

| Output Signal<br>Name | Output<br>Register | PIC16(L)F19155/56 |       |       | PIC16(L)F19175/76 |       |       |             |            |       | PIC16(L) | -19185/86 |       |       |       |

|                       | Value              | PORTA             | PORTB | PORTC | PORTA             | PORTB | PORTC | PORTD       | PORTE      | PORTA | PORTB    | PORTC     | PORTD | PORTE | PORTF |

| RTCC                  | 0x18               | •                 |       | •     | •                 |       | •     |             |            | •     |          | •         |       |       |       |

| ADGRDB                | 0x17               | •                 |       | •     | •                 |       | •     |             |            | •     |          |           |       |       | •     |

| ADGRDA                | 0x16               | •                 |       | •     | •                 |       | •     |             |            | •     |          |           |       |       | •     |

| TMR0                  | 0x15               |                   | •     | •     |                   | •     | •     |             |            |       |          | •         |       |       | •     |

| SDO1/SDA1             | 0x14               |                   | •     | •     |                   | •     | •     |             |            |       | •        | •         |       |       |       |

| SCK1/SCL1             | 0x13               |                   | •     | •     |                   | •     | •     |             |            |       | •        | •         |       |       |       |

| C2OUT                 | 0x12               | •                 |       | •     | •                 |       |       |             | •          | •     |          |           |       | •     |       |

| C1OUT                 | 0x11               | •                 |       | •     | •                 |       |       | •           |            | •     |          |           | •     |       |       |

| DT2                   | 0x10               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| TX2/CK2               | 0x0F               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| DT1                   | 0x0E               |                   | •     | •     |                   | •     | •     |             |            |       |          | •         |       |       | •     |

| TX1/CK1               | 0x0D               |                   | •     | •     |                   | •     | •     |             |            |       |          | •         |       |       | •     |

| PWM4OUT               | 0x0C               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| PWM3OUT               | 0x0B               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CCP2                  | 0x0A               |                   | •     | •     |                   | •     | •     |             |            |       |          | •         |       |       | •     |

| CCP1                  | 0x09               |                   | •     | •     |                   | •     | •     |             |            |       |          | •         |       |       | •     |

| CWG1D                 | 0x08               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CWG1C                 | 0x07               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CWG1B                 | 0x06               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CWG1A                 | 0x05               |                   | •     | •     |                   | •     | •     |             |            |       | •        | •         |       |       |       |

| CLC4OUT               | 0x04               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CLC3OUT               | 0x03               |                   | •     | •     |                   | •     |       | •           |            |       | •        |           | •     |       |       |

| CLC2OUT               | 0x02               | •                 |       | •     | •                 |       | •     |             |            | •     |          |           |       |       | •     |

| CLC1OUT               | 0x01               | •                 |       | •     | •                 |       | •     |             |            | •     |          |           |       |       | •     |

© 2017 Microchip Technology Inc.

| R/W-0/0                 | R/W-0/0                                                   | U-0                                                                   | R/W-0/0 | U-0            | U-0              | U-0              | R/W-0/0      |

|-------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|---------|----------------|------------------|------------------|--------------|

| UART2MD                 | UART1MD                                                   | —                                                                     | MSSP1MD | —              | —                | —                | CWG1MD       |

| bit 7                   |                                                           |                                                                       |         |                |                  |                  | bit 0        |

|                         |                                                           |                                                                       |         |                |                  |                  |              |

| Legend:                 |                                                           |                                                                       |         |                |                  |                  |              |

| R = Readable            | bit                                                       | W = Writable b                                                        | bit     | U = Unimplem   | ented bit, read  | as '0'           |              |

| u = Bit is unch         | nanged                                                    | x = Bit is unkn                                                       | own     | -n/n = Value a | t POR and BOR    | R/Value at all o | other Resets |

| '1' = Bit is set        |                                                           | '0' = Bit is clea                                                     | ired    | q = Value dep  | ends on conditio | on               |              |

| bit 7<br>bit 6<br>bit 5 | 1 = EUSART2 module disabled<br>0 = EUSART2 module enabled |                                                                       |         |                |                  |                  |              |

| bit 4                   | MSSP1MD: D<br>1 = MSSP1 n                                 | ted: Read as '0<br>bisable MSSP1<br>nodule disablec<br>nodule enabled | bit     |                |                  |                  |              |

| bit 3-1<br>bit 0        | -                                                         | ted: Read as '0<br>sable CWG1 bi                                      |         |                |                  |                  |              |

|                         | 1 = CWG1 m                                                | odule disabled<br>odule enabled                                       | -       |                |                  |                  |              |

# REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

# 17.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 17-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER**

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCAP7  | IOCAP6  | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCAP<7:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 17-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCAN7  | IOCAN6  | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

bit 7-0

**IOCAN<7:0>:** Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

# REGISTER 17-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| R/W/HS-0/0  | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------------|------------|------------|------------|------------|------------|------------|------------|

| IOCAF7      | IOCAF6     | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 bit 0 |            |            |            |            |            |            |            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

IOCAF<7:0>: Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

#### 19.5.8 CONTINUOUS SAMPLING MODE

Setting the CONT bit in the ADCON0 register automatically retriggers a new conversion cycle after updating the ADACC register. The GO bit remains set and re-triggering occurs automatically.

If ADSOI = 1, a threshold interrupt condition will clear GO and the conversions will stop.

#### 19.5.9 DOUBLE SAMPLE OR CVD CONVERSION MODE

Double sampling is enabled by setting the ADDSEN bit of the ADCON1 register. When this bit is set, two conversions are required before the module will calculate threshold error (each conversion must still be triggered separately). The first conversion will set the ADMATH bit of the ADSTAT register and update ADACC, but will not calculate ERR or trigger ADTIF. When the second conversion completes, the first value is transferred to PREV (depending on the setting of ADPSIS) and the value of the second conversion is placed into ADRES. Only upon the completion of the second conversion is ERR calculated and ADTIF triggered (depending on the value of ADCALC). The ADACC registers will contain the difference of the two samples taken.

# 26.7 Timer1 Interrupts

The Timer1 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the respective PIR register is set. To enable the interrupt-on-rollover, you must set these bits:

- ON bit of the T1CON register

- TMR1IE bit of the PIE4 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

| Note: | To avoid immediate interrupt vectoring,     |

|-------|---------------------------------------------|

|       | the TMR1H:TMR1L register pair should        |

|       | be preloaded with a value that is not immi- |

|       | nently about to rollover, and the TMR1IF    |

|       | flag should be cleared prior to enabling    |

|       | the timer interrupts.                       |

# 26.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- · ON bit of the T1CON register must be set

- TMR1IE bit of the PIE4 register must be set

- PEIE bit of the INTCON register must be set

- SYNC bit of the T1CON register must be set

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

# 26.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

For more information, see Section 29.0 "Capture/Compare/PWM Modules".

# 26.10 CCP Special Event Trigger

When any of the CCPs are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt. In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1. Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed. In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

# 27.4 Timer2/4 Interrupt

Timer2/4 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

#### FIGURE 27-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10-00205A<br>47/2016                                |

|-----------------|----------------------------------------------------------|

| CKPS            | 0ь010                                                    |

| PRx             | 1                                                        |

| OUTPS           | 0b0001                                                   |

| TMRx_clk        |                                                          |

| TMRx            |                                                          |

| TMRx_postscaled |                                                          |

| TMRxIF          | (1) (2) (1)                                              |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |

#### 27.5.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level -Triggered One-Shot mode the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

#### 28.6.3 GO STATUS

Timer run status is determined by the TS bit of the SMTxSTAT register, and will be delayed in time by synchronizer delays in non-Counter modes.

### 28.7 Modes of Operation

The modes of operation are summarized in Table 28-2. The following sections provide detailed descriptions, examples of how the modes can be used. Note that all waveforms assume WPOL/SPOL/CPOL = 0. When WPOL/SPOL/CPOL = 1, all SMTSIGx, SMTWINx and SMT clock signals will have a polarity opposite to that indicated. For all modes, the REPEAT bit controls whether the acquisition is repeated or single. When REPEAT = 0 (Single Acquisition mode), the timer will stop incrementing and the SMTxGO bit will be reset upon the completion of an acquisition. Otherwise, the timer will continue and allow for continued acquisitions to overwrite the previous ones until the timer is stopped in software.

# 28.7.1 TIMER MODE

Timer mode is the simplest mode of operation where the SMTxTMR is used as a 16/24-bit timer. No data acquisition takes place in this mode. The timer increments as long as the SMTxGO bit has been set by software. No SMT window or SMT signal events affect the SMTxGO bit. Everything is synchronized to the SMT clock source. When the timer experiences a period match (SMTxTMR = SMTxPR), SMTxTMR is reset and the period match interrupt trips. See Figure 28-3.

| MODE      | Mode of Operation                 | Synchronous<br>Operation | Reference                                    |

|-----------|-----------------------------------|--------------------------|----------------------------------------------|

| 0000      | Timer                             | Yes                      | Section 28.7.1 "Timer Mode"                  |

| 0001      | Gated Timer                       | Yes                      | Section 28.7.2 "Gated Timer Mode"            |

| 0010      | Period and Duty Cycle Acquisition | Yes                      | Section 28.7.3 "Period and Duty-Cycle Mode"  |

| 0011      | High and Low Time Measurement     | Yes                      | Section 28.7.4 "High and Low-Measure Mode"   |

| 0100      | Windowed Measurement              | Yes                      | Section 28.7.5 "Windowed Measure Mode"       |

| 0101      | Gated Windowed Measurement        | Yes                      | Section 28.7.6 "Gated Window Measure Mode"   |

| 0110      | Time of Flight                    | Yes                      | Section 28.7.7 "Time of Flight Measure Mode" |

| 0111      | Capture                           | Yes                      | Section 28.7.8 "Capture Mode"                |

| 1000      | Counter                           | No                       | Section 28.7.9 "Counter Mode"                |

| 1001      | Gated Counter                     | No                       | Section 28.7.10 "Gated Counter Mode"         |

| 1010      | Windowed Counter                  | No                       | Section 28.7.11 "Windowed Counter Mode"      |

| 1011-1111 | Reserved                          | —                        | —                                            |

TABLE 28-2: MODES OF OPERATION

# 31.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 31-12.

#### 31.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External input

#### 31.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

#### 31.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT\_sync

- Timer2 TMR2\_postscaled

- CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 31-6).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

# 31.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- · CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

# 32.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR5 register will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · CLCxIE bit of the PIE5 register