#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 31x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19175-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-4**: PIC16(L)F19185/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                       | Function | Input<br>Types | Output<br>Types | Description                    |  |  |

|--------------------------------------------------------------------------------------------|----------|----------------|-----------------|--------------------------------|--|--|

| RF7/ANF7/SEG47                                                                             | RF7      | TTL/ST         | CMOS/OD         | General purpose I/O.           |  |  |

|                                                                                            | ANF7     | AN             | _               | ADC Channel input.             |  |  |

|                                                                                            | SEG47    | _              | AN              | LCD Analog output.             |  |  |

| VLCD3                                                                                      | VLCD3    | AN             | —               | LCD analog input               |  |  |

| Vdd                                                                                        | Vdd      | Power          | Р               | Positive supply voltage input. |  |  |

| Vss                                                                                        | Vdd      | Power          | Р               | Ground reference.              |  |  |

| Legend: AN = Analog input or output CMOS = CMOS compatible input or output QD = Open-Drain |          |                |                 |                                |  |  |

Legend: HV = High Voltage

Note

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. 1: Refer to Table 14-2 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as 2: described in Table 14-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

## 5.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

## 5.7 Register Definitions: Device and Revision

## REGISTER 5-6: DEVID: DEVICE ID REGISTER

|         |      | R      | R   | R     | R      | R | R     |

|---------|------|--------|-----|-------|--------|---|-------|

|         |      |        |     | DEV<  | :13:8> |   |       |

|         |      | bit 13 |     |       |        |   | bit 8 |

|         |      |        |     |       |        |   |       |

| R       | R    | R      | R   | R     | R      | R | R     |

|         |      |        | DEV | <7:0> |        |   |       |

| bit 7   |      |        |     |       |        |   | bit 0 |

|         |      |        |     |       |        |   |       |

| Legend: |      |        |     |       |        |   |       |

|         | 1.11 |        |     |       |        |   |       |

R = Readable bit '1' = Bit is set

et '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device          | DEVID<13:0> Values |      |      |      |         |

|-----------------|--------------------|------|------|------|---------|

| PIC16F19155/56  | 11                 | 0000 | 1001 | 1110 | (309Eh) |

| PIC16LF19155/56 | 11                 | 0000 | 1001 | 1111 | (309Fh) |

| PIC16F19175/76  | 11                 | 0000 | 1010 | 0000 | (30A0h) |

| PIC16LF19175/76 | 11                 | 0000 | 1010 | 0001 | (30A1h) |

| PIC16F19185/86  | 11                 | 0000 | 1010 | 0010 | (30A2h) |

| PIC16LF19185/86 | 11                 | 0000 | 1010 | 0011 | (30A3h) |

# **19.6 Register Definitions: ADC Control**

## REGISTER 19-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0        | R/W-0/0             | U-0                           | R/W-0/0          | U-0               | R/W-0/0                        | U-0           | R/W/HC-0        |

|----------------|---------------------|-------------------------------|------------------|-------------------|--------------------------------|---------------|-----------------|

| ON             | CONT                | -                             | CS               | -                 | FM                             | -             | GO              |

| bit 7          |                     |                               |                  |                   |                                |               | bit (           |

|                |                     |                               |                  |                   |                                |               |                 |

| Legend:        |                     |                               |                  |                   |                                |               |                 |

| R = Reada      | ble bit             | W = Writable                  | bit              | U = Unimple       | mented bit, read               | as '0'        |                 |

| u = Bit is u   | nchanged            | x = Bit is unk                | nown             | -n/n = Value      | at POR and BO                  | R/Value at al | I other Resets  |

| '1' = Bit is s | set                 | '0' = Bit is cle              | eared            | HC = Bit is cl    | leared by hardwa               | are           |                 |

|                |                     |                               |                  |                   |                                |               |                 |

| bit 7          | ON: ADC En          | able bit                      |                  |                   |                                |               |                 |

|                | 1 = ADC is e        |                               |                  |                   |                                |               |                 |

| bit 6          | 0 = ADC is d        | Continuous Or                 | ention Enchl     | ь                 |                                |               |                 |

|                |                     |                               |                  |                   | on triggor until A             |               |                 |

|                |                     |                               |                  | s of the value of | on trigger until A<br>f ADSOI) | DTF IS Set (  | II ADSOLIS SE   |

|                |                     |                               |                  | ach conversion    |                                |               |                 |

| bit 5          | Unimpleme           | nted: Read as                 | '0'              |                   |                                |               |                 |

| bit 4          | CS: ADC Clo         | ock Selection b               | it               |                   |                                |               |                 |

|                |                     | upplied from FF               |                  |                   |                                |               |                 |

|                |                     |                               |                  | ording to ADCL    | K register                     |               |                 |

| bit 3          | •                   | nted: Read as                 |                  |                   |                                |               |                 |

| bit 2          |                     | sults Format/ali              | •                |                   |                                |               |                 |

|                |                     | and PREV dat                  |                  |                   |                                |               |                 |

| bit 1          |                     | and PREV dat<br>nted: Read as | -                | ieu, zero-iilieu  |                                |               |                 |

|                | •                   | nversion Statu                |                  |                   |                                |               |                 |

| bit 0          |                     |                               |                  | Setting this bit  | starts an ADC of               | conversion o  | wole. The bit   |

|                |                     |                               |                  | y the CONT bit    |                                |               |                 |

|                |                     | version comple                |                  |                   |                                |               |                 |

| Note 1:        | This bit requires ( | ON bit to be set              | t.               |                   |                                |               |                 |

| 2:             | If cleared by softv | vare while a co               | nversion is in p | progress, the re  | esults of the conv             | version up to | this point will |

2: If cleared by software while a conversion is in progress, the results of the conversion up to this point will be transfered to ADRES and the state machine will be reset, but the ADIF interrupt flag bit will not be set; filter and threshold operations will not be performed.

## REGISTER 19-33: ADUTHH: ADC UPPER THRESHOLD HIGH BYTE REGISTER

| R/W-0/0                           | R/W-0/0 | R/W-0/0         | R/W-0/0                            | R/W-0/0                                             | R/W-0/0 | R/W-0/0 | R/W-0/0      |

|-----------------------------------|---------|-----------------|------------------------------------|-----------------------------------------------------|---------|---------|--------------|

|                                   |         |                 | UTH<                               | :15:8>                                              |         |         |              |

| bit 7                             |         |                 |                                    |                                                     |         |         | bit 0        |

|                                   |         |                 |                                    |                                                     |         |         |              |

| Legend:                           |         |                 |                                    |                                                     |         |         |              |

| R = Readable bit W = Writable bit |         |                 | U = Unimplemented bit, read as '0' |                                                     |         |         |              |

| u = Bit is unch                   | anged   | x = Bit is unkn | own                                | vn -n/n = Value at POR and BOR/Value at all other I |         |         | other Resets |

bit 7-0 **UTH<15:8>**: ADC Upper Threshold MSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

### REGISTER 19-34: ADUTHL: ADC UPPER THRESHOLD LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|--|

| UTH<7:0> |         |         |         |         |         |         |         |  |  |

| bit 7    |         |         |         |         |         |         | bit 0   |  |  |

|          |         |         |         |         |         |         |         |  |  |

| Leaend:  |         |         |         |         |         |         |         |  |  |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **UTH<7:0>**: ADC Upper Threshold LSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

'1' = Bit is set

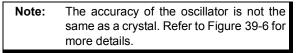

## 24.1.3 CLOCK SOURCES

The RTCC module can be clocked by either an external Real-Time Clock crystal oscillating at 32.768 kHz, MFINTOSC/16 (31.25 kHz) or via the ZCD at 50 Hz or 60 Hz. Each clock selection has a fixed prescaler in order to generate the required half-second clock needed by the RTCC. They are as following:

- SOSC (32.768 kHz) = 1:16384

- MFINTOSC/16 (31.25 kHz) = 1:15625

- ZCD (50 Hz) = 1:25

- ZCD (60 Hz) = 1:30

## FIGURE 24-4: CLOCK SOURCE MULTIPLEXING

### 24.1.4 DIGIT CARRY RULES

This section explains which timer values are affected when there is a rollover.

- Time of Day: From 23:59:59 to 00:00:00 with a carry to the Day and Weekday field

- Month: From 12/31 to 01/01 with a carry to the Year field

- Day of Week: From 6 to 0 with no carry (see Table 24-1)

- Year Carry: From 99 to 00; this also surpasses the use of the RTCC

For the day to month rollover schedule, see Table 24-2.

Because the values are in BCD format, the carry to the upper BCD digit will occur at a count of 10 and not at 16 (SECONDS, MINUTES, HOURS, WEEKDAY, DAYS and MONTHS).

## TABLE 24-1: DAY OF WEEK SCHEDULE

| Day of Week |   |  |  |  |  |  |  |

|-------------|---|--|--|--|--|--|--|

| Sunday      | 0 |  |  |  |  |  |  |

| Monday      | 1 |  |  |  |  |  |  |

| Tuesday     | 2 |  |  |  |  |  |  |

| Wednesday   | 3 |  |  |  |  |  |  |

| Thursday    | 4 |  |  |  |  |  |  |

| Friday      | 5 |  |  |  |  |  |  |

| Saturday    | 6 |  |  |  |  |  |  |

Calibration of the RTCC can be performed to yield an error of three seconds or less per month (see **Section 24.1.7 "Calibration"** for further details).

x = Bit is unknown

| U-0                                                                  | U-0 | R/W-x | R/W-x   | R/W-x        | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|-----|-------|---------|--------------|-------|-------|-------|

| —                                                                    |     | ALRMH | IR<1:0> | ALRMLHR<3:0> |       |       |       |

| bit 7                                                                |     |       |         |              |       |       | bit 0 |

|                                                                      |     |       |         |              |       |       |       |

| Legend:                                                              |     |       |         |              |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |         |              |       |       |       |

'0' = Bit is cleared

## REGISTER 24-15: ALRMHR: ALARM HOUR CONTROL REGISTER

'1' = Bit is set

bit 7-6 Unimplemented: Read as '0'

-n = Value at POR

bit 5-4 ALRMHHR<1:0>: Binary Coded Decimal value of hours '10' digit; valid values from 0 to 2

bit 3-0 ALRMLHR<3:0>: Binary Coded Decimal value of hours '1' digit; valid values from 0 to 9

## REGISTER 24-16: ALRMMIN: ALARM MINUTE CONTROL REGISTER

| U-0   | R/W-x         | R/W-x | R/W-x | R/W-x         | R/W-x | R/W-x | R/W-x |

|-------|---------------|-------|-------|---------------|-------|-------|-------|

| —     | ALRMHMIN<2:0> |       |       | ALRMLMIN<3:0> |       |       |       |

| bit 7 |               |       |       |               |       |       | bit 0 |

|       |               |       |       |               |       |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | Unimplemented: Read as '0'                                                                |

|---------|-------------------------------------------------------------------------------------------|

| bit 6-4 | ALRMHMIN<2:0>: Binary Coded Decimal value of minutes '10' digit; valid values from 0 to 5 |

| bit 3-0 | ALRMLMIN<3:0>: Binary Coded Decimal value of minutes '1' digit; valid values from 0 to 9  |

## REGISTER 24-17: ALRMSEC: ALARM SECONDS CONTROL REGISTER

| U-0   | R/W-x         | R/W-x | R/W-x | R/W-x | R/W-x  | R/W-x   | R/W-x |

|-------|---------------|-------|-------|-------|--------|---------|-------|

| —     | ALRMHSEC<2:0> |       |       |       | ALRMLS | EC<3:0> |       |

| bit 7 |               |       |       |       |        |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7 Unimplemented: Read as '0'

| bit 6-4 | ALRMHSEC<2:0>: Binary Coded Decimal value of seconds '10' digit; valid values from 0 to 5 |

|---------|-------------------------------------------------------------------------------------------|

|---------|-------------------------------------------------------------------------------------------|

bit 3-0 ALRMLSEC<3:0>: Binary Coded Decimal value of seconds '1' digit; valid values from 0 to 9

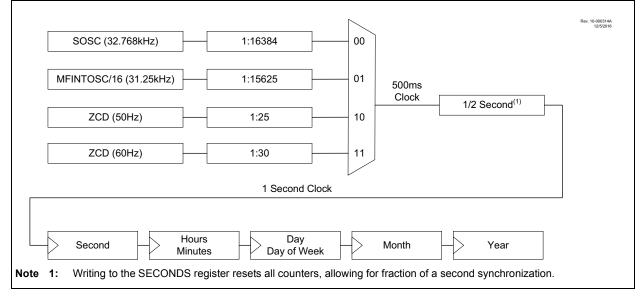

| R/W-0/u                   | R/W-0/u                                                                                                                 | R/W-0/u                                                                                                                                       | R/W-0/u         | R/W/HC-0/u       | R-x/x            | U-0              | U-0          |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|--------------|--|

| GE                        | GPOL                                                                                                                    | GTM                                                                                                                                           | GSPM            | GGO/DONE         | GVAL             | —                | —            |  |

| bit 7                     |                                                                                                                         |                                                                                                                                               |                 |                  |                  |                  | bit 0        |  |

| Louandi                   |                                                                                                                         |                                                                                                                                               |                 |                  |                  |                  |              |  |

| Legend:<br>R = Readable t |                                                                                                                         |                                                                                                                                               | h it            |                  | aantad hit raa   |                  |              |  |

|                           |                                                                                                                         | W = Writable                                                                                                                                  |                 |                  | nented bit, read | R/Value at all o | athor Doooto |  |

| u = Bit is uncha          | ingeu                                                                                                                   | x = Bit is unkr                                                                                                                               |                 |                  |                  |                  | Siner Reseis |  |

| '1' = Bit is set          |                                                                                                                         | '0' = Bit is clea                                                                                                                             | areo            | HC = BILIS CI    | eared by hardv   | vare             |              |  |

| bit 7                     | GE: Timer1 G                                                                                                            | ate Enable bit                                                                                                                                |                 |                  |                  |                  |              |  |

|                           | If ON = 0:                                                                                                              |                                                                                                                                               |                 |                  |                  |                  |              |  |

|                           | This bit is igno                                                                                                        | ored                                                                                                                                          |                 |                  |                  |                  |              |  |

|                           | $\frac{\text{If ON} = 1}{1}$                                                                                            |                                                                                                                                               |                 |                  |                  |                  |              |  |

|                           |                                                                                                                         | ounting is cont<br>always counti                                                                                                              |                 | ïmer1 gate fund  | tion             |                  |              |  |

| bit 6                     |                                                                                                                         | 1 Gate Polarity                                                                                                                               | •               |                  |                  |                  |              |  |

| bit o                     |                                                                                                                         | gate is active-high (Timer1 counts when gate is high)                                                                                         |                 |                  |                  |                  |              |  |

|                           | •                                                                                                                       | her 1 gate is active-light (Timer 1 counts when gate is light)<br>her 1 gate is active-low (Timer 1 counts when gate is low)                  |                 |                  |                  |                  |              |  |

| bit 5                     | GTM: Timer1                                                                                                             | Gate Toggle M                                                                                                                                 | lode bit        |                  |                  |                  |              |  |

|                           | 1 = Timer1 G                                                                                                            | Fimer1 Gate Toggle mode is enabled                                                                                                            |                 |                  |                  |                  |              |  |

|                           |                                                                                                                         | <ul> <li>Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared<br/>mer1 gate flip-flop toggles on every rising edge.</li> </ul> |                 |                  |                  |                  |              |  |

| 1.11.4                    | -                                                                                                                       |                                                                                                                                               | -               |                  |                  |                  |              |  |

| bit 4                     |                                                                                                                         | 1 Gate Single-                                                                                                                                |                 |                  |                  |                  |              |  |

|                           | <ul> <li>1 = Timer1 Gate Single-Pulse mode is enabled</li> <li>0 = Timer1 Gate Single-Pulse mode is disabled</li> </ul> |                                                                                                                                               |                 |                  |                  |                  |              |  |

| bit 3                     |                                                                                                                         | •                                                                                                                                             |                 | cquisition Statu | s bit            |                  |              |  |

|                           |                                                                                                                         |                                                                                                                                               | •               | s ready, waiting |                  |                  |              |  |

|                           | 0 = Timer1 g                                                                                                            | ate single-puls                                                                                                                               | e acquisition h | has completed of | or has not beer  | n started        |              |  |

|                           | This bit is                                                                                                             | automatically                                                                                                                                 | cleared when    | GSPM is clear    | ed               |                  |              |  |

| bit 2                     |                                                                                                                         | 1 Gate Value S                                                                                                                                |                 |                  |                  |                  |              |  |

|                           |                                                                                                                         |                                                                                                                                               | -               | ate that could b | e provided to T  | MR1H:TMR1L       |              |  |

| hit 1 0                   | •                                                                                                                       | Timer1 Gate                                                                                                                                   | . ,             |                  |                  |                  |              |  |

| bit 1-0                   | ommpiemen                                                                                                               | ted: Read as '                                                                                                                                | U               |                  |                  |                  |              |  |

## REGISTER 26-2: T1GCON: TIMER1 GATE CONTROL REGISTER

# 27.7 Register Definitions: Timer2/4 Control

| U-0                                     | U-0                       | U-0              | U-0            | R/W-0/0       | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|-----------------------------------------|---------------------------|------------------|----------------|---------------|------------------|--------------|---------|

| _                                       |                           | _                | _              |               | CS<              | :3:0>        |         |

| bit 7                                   |                           |                  |                |               |                  |              | bit (   |

| Legend:                                 |                           |                  |                |               |                  |              |         |

| R = Reada                               | ble bit                   | W = Writable     | bit            | U = Unimpler  | nented bit, read | d as '0'     |         |

| u = Bit is unchanged x = Bit is unknown |                           | nown             | -n/n = Value a | at POR and BC | R/Value at all   | other Resets |         |

| '1' = Bit is set                        |                           | '0' = Bit is cle | ared           |               |                  |              |         |

|                                         |                           |                  |                |               |                  |              |         |

| bit 7-4                                 | Unimplem                  | ented: Read as ' | 0'             |               |                  |              |         |

| bit 3-0                                 | CS<3:0>:                  | Timer2/4 Clock S | elect bits     |               |                  |              |         |

|                                         | 1111 <b>= Re</b>          | served           |                |               |                  |              |         |

|                                         | 1110 <b>= Re</b>          |                  |                |               |                  |              |         |

|                                         | 1101 <b>= Re</b>          | served           |                |               |                  |              |         |

|                                         | 1100 <b>= LC</b>          | 4_out            |                |               |                  |              |         |

|                                         | 1011 <b>= LC</b>          | 3_out            |                |               |                  |              |         |

|                                         | 1010 <b>= LC</b>          | 2_out            |                |               |                  |              |         |

|                                         | 1001 <b>= LC</b>          | 1_out            |                |               |                  |              |         |

|                                         | 1000 <b>= ZC</b>          | D1_output        |                |               |                  |              |         |

|                                         | 0111 <b>= SC</b>          | DSC              |                |               |                  |              |         |

|                                         |                           | FINTOSC (31.25   |                |               |                  |              |         |

|                                         | 0101 = MFINTOSC (500 kHz) |                  |                |               |                  |              |         |

|                                         | 0100 <b>= LF</b>          |                  |                |               |                  |              |         |

|                                         |                           | INTOSC (32 MH    | z)             |               |                  |              |         |

|                                         | 0010 <b>= F</b> o         |                  |                |               |                  |              |         |

|                                         | 0001 <b>= F</b> o         |                  |                |               |                  |              |         |

|                                         | 0000 <b>= T2</b>          | CKIPPS           |                |               |                  |              |         |

## REGISTER 27-1: TxCLKCON: TIMER2/4 CLOCK SELECTION REGISTER

| Name     | Bit 7   | Bit 6                                        | Bit 5     | Bit 4         | Bit 3   | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------|----------------------------------------------|-----------|---------------|---------|------------|---------|---------|---------------------|

| T2CON    | ON      |                                              | CKPS<2:0> |               |         | OUTPS<3:0> |         |         |                     |

| T2TMR    |         | Holding Register for the 8-bit TMR2 Register |           |               |         |            | 384*    |         |                     |

| T2PR     |         | TMR2 Period Register                         |           |               |         |            | 384*    |         |                     |

| RxyPPS   | —       | —                                            | —         | - RxyPPS<4:0> |         |            | 265     |         |                     |

| CWG1ISM  | —       | _                                            | _         | —             |         | IS<        | 3:0>    |         | 492                 |

| CLCxSELy | —       | _                                            |           | LCxDyS<5:0>   |         |            |         | 503     |                     |

| TRISA    | TRISA7  | TRISA6                                       | TRISA5    | TRISA4        | TRISA3  | TRISA2     | TRISA1  | TRISA0  | 222                 |

| TRISC    | TRISC7  | TRISC6                                       | TRISC5    | TRISC4        | TRISC3  | TRISC2     | TRISC1  | TRISC0  | 235                 |

| PWM3CON  | PWM3EN  | _                                            | PWM3OUT   | PWM3POL       | —       | —          | _       | —       |                     |

| PWM4CON  | PWM4EN  | _                                            | PWM4OUT   | PWM4POL       | —       | —          | _       | —       |                     |

| PWM3DCL  | PWM3DC1 | PWM3DC0                                      | _         | _             | _       | _          | _       | _       |                     |

| PWM3DCH  | PWM3DC9 | PWM3DC8                                      | PWM3DC7   | PWM3DC6       | PWM3DC5 | PWM3DC4    | PWM3DC3 | PWM3DC2 |                     |

| PWM4DCL  | PWM4DC1 | PWM4DC0                                      | —         | —             | —       | —          | —       | —       |                     |

| PWM4DCH  | PWM4DC9 | PWM4DC8                                      | PWM4DC7   | PWM4DC6       | PWM4DC5 | PWM4DC4    | PWM4DC3 | PWM4DC2 |                     |

## TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

\*Page provides register information.

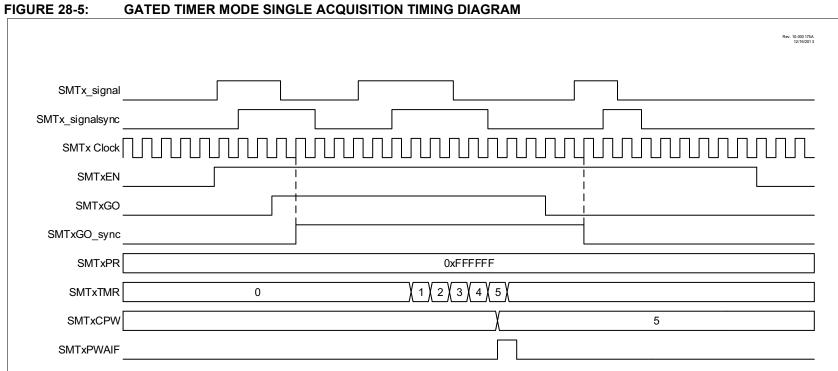

# 31.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWG1x pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWG10CON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWG10CON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWG1CON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 31.10** "**Auto-Shutdown**". An auto-shutdown event will only affect pins that have STRx = 1.

## 31.9.1 STEERING SYNCHRONIZATION

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

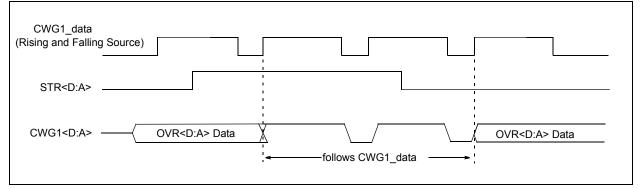

Figure 31-10 and Figure 31-11 illustrate the timing of asynchronous and synchronous steering, respectively.

## FIGURE 31-11: EXAMPLE OF STEERING EVENT (MODE<2:0> = 001)

# 31.13 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripherals are shown in Section 1.1 "Register and Bit Naming Conventions".

## REGISTER 31-1: CWG1CON0: CWG1 CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> |     | —   | _   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <ul> <li>EN: CWG1 Enable bit</li> <li>1 = Module is enabled</li> <li>0 = Module is disabled</li> </ul>                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | LD: CWG1 Load Buffer bits <sup>(1)</sup><br>1 = Buffers to be loaded on the next rising/falling event<br>0 = Buffers not loaded                                                                                                                                                                                                                                                         |

| bit 5-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0 | MODE<2:0>: CWG1 Mode bits<br>111 = Reserved<br>110 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>011 = CWG outputs operate in Reverse Full-Bridge mode<br>010 = CWG outputs operate in Forward Full-Bridge mode<br>001 = CWG outputs operate in Synchronous Steering mode<br>000 = CWG outputs operate in Steering mode |

**Note 1:** This bit can only be set after EN = 1 and cannot be set in the same instruction that EN is set.

# PIC16(L)F19155/56/75/76/85/86

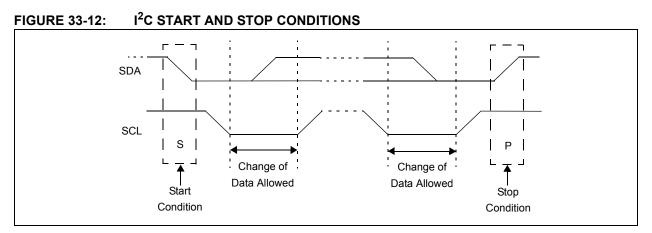

## 33.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, the clock is stretched, allowing the slave time to change the ACK value before it is sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

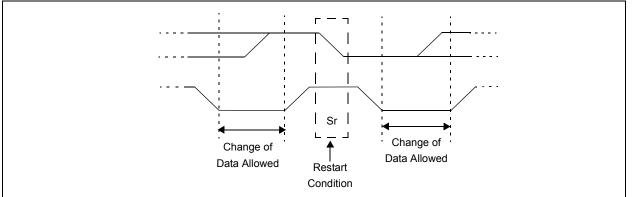

### 33.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow time for the slave software to decide whether it wants to  $\overline{ACK}$  the receive address or data byte.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 33-16 displays a module using both address and data holding. Figure 33-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an  $\overline{ACK}$ , not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSPxSTAT register.

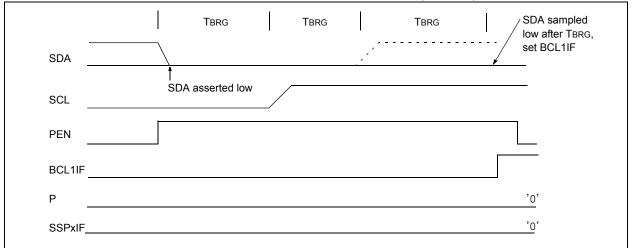

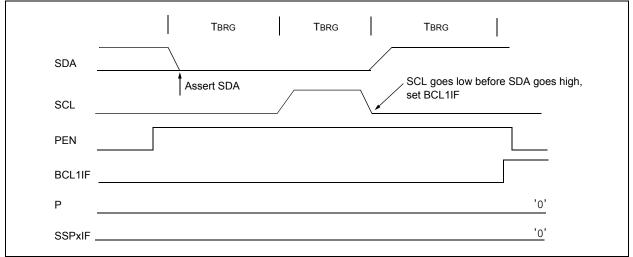

## 33.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 33-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 33-39).

## FIGURE 33-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

## FIGURE 33-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

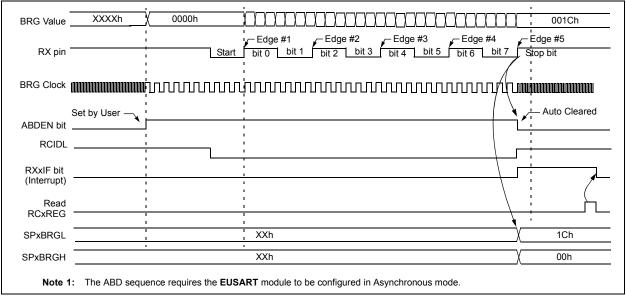

## 34.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDxCON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPxBRG begins counting up using the BRG counter clock as shown in Figure 34-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPxBRGH, SPxBRGL register pair, the ABDEN bit is automatically cleared and the RXxIF interrupt flag is set. The value in the RCxREG needs to be read to clear the RXxIF interrupt. RCxREG content should be discarded. When calibrating for modes that do not use the SPxBRGH register the user can verify that the SPxBRGL register did not overflow by checking for 00h in the SPxBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 34-1. During ABD, both the SPxBRGH and SPxBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPxBRGH and SPxBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 34.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPxBRGH:SPxBRGL register pair.

### TABLE 34-1:BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPxBRGL and SPxBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

## FIGURE 34-6: AUTOMATIC BAUD RATE CALIBRATION

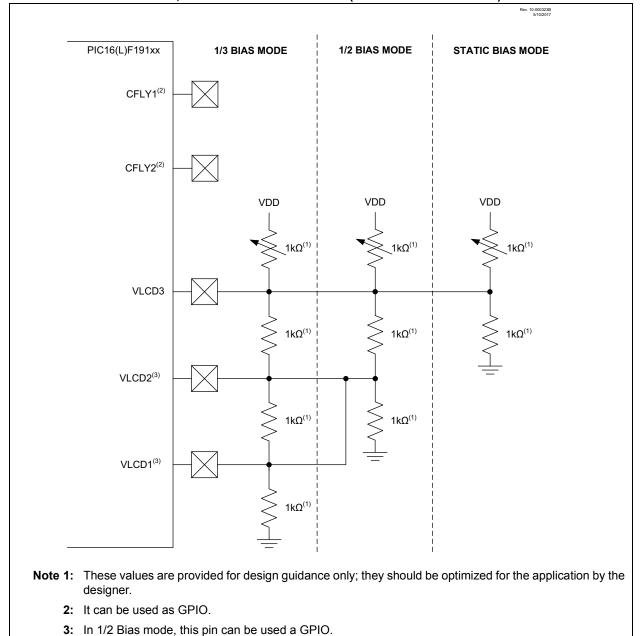

## 35.7.3 LCD VOLTAGE SUPPLIED FROM EXTERNAL RESISTOR LADDER

In this mode, the LCD charge pump is completely disabled. The LCD bias levels are tied to VDD and are generated using an external divider. The difference is that the internal voltage reference is also disabled and the bottom of the ladder is tied to ground (VSS); see Figure 35-6. The value of the resistors, and the difference between VSS and VDD, determine the contrast range; no software adjustment is possible. This configuration is also used where the LCD's current requirements exceed the capacity of the charge pump and the high power (HP) internal resistor ladder and the software contrast control is not needed.

Depending on the bias type required, resistors are connected between some or all of the pins. A potentiometer can also be connected between VLCD3 and VDD to allow for hardware controlled contrast adjustment.

### FIGURE 35-6: CONNECTIONS FOR LCD VOLTAGE SUPPLIED FROM EXTERNAL LADDER, STATIC, 1/2 AND 1/3 BIAS MODES (LCDVSRC<3:0> = 1000)

**4:** In Static mode, this pin can be used a GPIO.

# 42.1 Package Marking Information (Continued)

| Legend: | XXX        | Customer-specific information                                           |

|---------|------------|-------------------------------------------------------------------------|

|         | Y          | Year code (last digit of calendar year)                                 |

|         | ΥY         | Year code (last 2 digits of calendar year)                              |

|         | WW         | Week code (week of January 1 is week '01')                              |

|         | NNN        | Alphanumeric traceability code                                          |

|         |            | Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)                |

|         | *          | This package is Pb-free. The Pb-free JEDEC designator ((e3))            |

|         |            | can be found on the outer packaging for this package.                   |

|         |            |                                                                         |

| Note:   | In the eve | nt the full Microchip part number cannot be marked on one line, it will |

|         |            | d over to the next line, thus limiting the number of available          |

|         |            | s for customer-specific information.                                    |

|         |            |                                                                         |

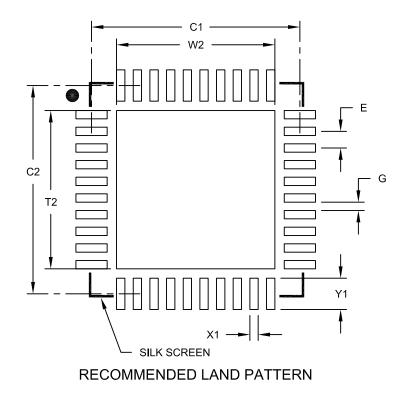

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch              | E  | 0.40 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 3.80 |  |

| Optional Center Pad Length | T2 |             |      | 3.80 |  |

| Contact Pad Spacing        | C1 |             | 5.00 |      |  |

| Contact Pad Spacing        | C2 |             | 5.00 |      |  |

| Contact Pad Width (X40)    | X1 |             |      | 0.20 |  |

| Contact Pad Length (X40)   | Y1 |             |      | 0.75 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B

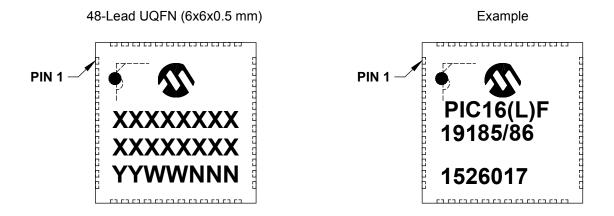

## 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |           | MILLIMETERS |      |  |  |

|------------------------|-------|-----------|-------------|------|--|--|

| Dimension Limits       |       | MIN       | NOM         | MAX  |  |  |

| Number of Pins         | N     | 48        |             |      |  |  |

| Pitch                  | е     | 0.40 BSC  |             |      |  |  |

| Overall Height         | A     | 0.45      | 0.50        | 0.55 |  |  |

| Standoff               | A1    | 0.00      | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3    | 0.127 REF |             |      |  |  |

| Overall Width          | E     | 6.00 BSC  |             |      |  |  |

| Exposed Pad Width      | E2    | 4.45      | 4.60        | 4.75 |  |  |

| Overall Length         | D     | 6.00 BSC  |             |      |  |  |

| Exposed Pad Length     | D2    | 4.45      | 4.60        | 4.75 |  |  |

| Contact Width          | b     | 0.15      | 0.20        | 0.25 |  |  |

| Contact Length         | L     | 0.30      | 0.40        | 0.50 |  |  |

| Contact-to-Exposed Pad | K     | 0.20      | -           | -    |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2