Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 31x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 40-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 40-UQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19175t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bank Offset<br>Bank 0-Bank 63 | Name   | Bit 7 | Bit 6                                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------|--------|-------|-------------------------------------------------------|-------|-------|-------|-------|-------|-----------|-----------------------|----------------------------|

| All Banks                     |        |       |                                                       |       |       |       |       |       |           |                       |                            |

| x00h or x80h                  | INDF0  |       |                                                       |       | IND   | F0    |       |       |           | xxxx xxxx             | XXXX XXXX                  |

| x01h or x81h                  | INDF1  |       |                                                       |       | IND   | F1    |       |       |           | xxxx xxxx             | XXXX XXXX                  |

| x02h or x82h                  | PCL    |       |                                                       |       | PC    | Ľ     |       |       |           | 0000 0000             | 0000 0000                  |

| x03h or x83h                  | STATUS | _     | — — — <u>TO</u> <u>PD</u> <u>Z</u> <u>DC</u> <u>C</u> |       |       |       |       |       | 1 1000    | q quui                |                            |

| x04h or x84h                  | FSR0L  |       |                                                       |       | FSR   | ROL   |       |       |           | 0000 0000             | นนนน นนนเ                  |

| x05h or x85h                  | FSR0H  |       |                                                       |       | FSR   | OH    |       |       |           | 0000 0000             | 0000 0000                  |

| x06h or x86h                  | FSR1L  |       |                                                       |       | FSR   | R1L   |       |       |           | 0000 0000             | uuuu uuuu                  |

| x07h or x87h                  | FSR1H  |       |                                                       |       | FSR   | 1H    |       |       |           | 0000 0000             | 0000 0000                  |

| x08h or x88h                  | BSR    | —     | — — BSR00                                             |       |       |       |       |       | 00 0000   | 00 0000               |                            |

| x09h or x89h                  | WREG   |       | WREG0 0000 0000 uuuu                                  |       |       |       |       |       | uuuu uuuu |                       |                            |

| x0Ah or x8Ah                  | PCLATH | _     |                                                       |       |       |       |       |       |           |                       |                            |

| x0Bh or x8Bh                  | INTCON | GIE   | PEIE                                                  | _     | _     | _     |       |       | INTEDG    | 001                   | 00                         |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** These Registers can be accessed from any bank

© 2017 Microchip Technology Inc.

#### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| Address     | Name               | Bit 7 | Bit 6         | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------|--------------------|-------|---------------|-------|----------|--------|-------|-------|-------|-----------------------|----------------------------|

| Bank 61 (Co | ank 61 (Continued) |       |               |       |          |        |       |       |       |                       |                            |

| 1ECFh       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED0h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED1h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED2h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED3h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED4h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED5h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED6h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1ED7h       | _                  |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1ED8h       | _                  |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1ED9h       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDAh       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDBh       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDCh       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDDh       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDEh       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EDFh       | —                  |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1EE0h       | —                  |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1EE1h       | —                  |       | Unimplemented |       |          |        |       |       |       |                       |                            |

| 1EE2h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EE3h       | —                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

| 1EE4h       | _                  |       |               |       | Unimpler | mented |       |       |       |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

#### 9.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use an internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 9.3 "Clock Switching" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

### 9.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ<2:0> bits of the OSCFRQ register.

The MFINTOSC is an internal clock source within the HFINTOSC that provides two (500 kHz, 32 kHz) constant clock outputs. These constant clock outputs are available for selection to various peripherals, internally.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

#### 9.2.2.2 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 9-7).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WWDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 9.2.2.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Windowed Watchdog Timer (WWDT)

- Timer1

- Timer0

- Timer2

- Fail-Safe Clock Monitor (FSCM)

- CLC

#### 9.2.2.4 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT register (Register 9-4). The oscillators can also be manually enabled through the OSCEN register (Register 9-5). Manual enabling makes it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT register.

| R/W-0/0          | R/W-0/0                                                 | U-0                                                        | U-0                            | U-0             | U-0              | R/W-0/0          | R/W-0/0     |

|------------------|---------------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------|------------------|------------------|-------------|

| OSFIE            | CSWIE                                                   |                                                            | _                              |                 |                  | ADTIE            | ADIE        |

| bit 7            | ·                                                       | ·                                                          |                                |                 |                  | ·                | bit 0       |

| Legend:          |                                                         |                                                            |                                |                 |                  |                  |             |

| R = Readable     | e bit                                                   | W = Writable                                               | oit                            | U = Unimpler    | mented bit, read | as '0'           |             |

| u = Bit is uncl  | hanged                                                  | x = Bit is unkn                                            | own                            | -n/n = Value    | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                         | '0' = Bit is clea                                          | ared                           |                 |                  |                  |             |

| bit 7            | 1 = Enables t<br>0 = Disables                           | lator Fail Interru<br>he Oscillator Fa<br>the Oscillator F | ail Interrupt<br>ail Interrupt |                 |                  |                  |             |

| bit 6            | 1 = The clock                                           | k Switch Comp<br>switch module<br>switch module            | interrupt is e                 | nabled          |                  |                  |             |

| bit 5-2          | Unimplemen                                              | ted: Read as '                                             | )'                             |                 |                  |                  |             |

| bit 1            | 1 = Enables t                                           | og-to-Digital Co<br>he ADC thresh<br>the ADC thresh        | old compare i                  | nterrupt        | mpare Interrupt  | Enable bit       |             |

| bit 0            | 1 = Enables t                                           | to-Digital Con<br>he ADC interru<br>the ADC interru        | ot                             | Interrupt Enabl | e bit            |                  |             |

| se               | t PEIE of the IN<br>t to enable ar<br>ntrolled by regis | ny peripheral                                              | interrupt                      |                 |                  |                  |             |

| REGISTER 10-12: | PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1 |

|-----------------|-----------------------------------------------|

|-----------------|-----------------------------------------------|

| R/W/HS-0/         | 0 R/W/HS-0/0                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                | U-0                      | U-0              | U-0              | R/W/HS-0/0                     | R/W/HS-0/0  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|------------------|--------------------------------|-------------|--|

| OSFIF             | CSWIF                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                  |                          | _                | _                | ADTIF                          | ADIF        |  |

| bit 7             |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                    |                          |                  |                  |                                | bit 0       |  |

|                   |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                    |                          |                  |                  |                                |             |  |

| Legend:           |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                    |                          |                  |                  |                                |             |  |

| R = Readab        | le bit                                                                                                                                                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                                       | bit                      | U = Unimpler     | nented bit, read | d as '0'                       |             |  |

| u = Bit is une    | changed                                                                                                                                                                                                                                                                                                    | x = Bit is unkr                                                                                                                                                                                                                                                                                    | nown                     | -n/n = Value a   | at POR and BC    | R/Value at all o               | ther Resets |  |

| '1' = Bit is se   | et                                                                                                                                                                                                                                                                                                         | '0' = Bit is clea                                                                                                                                                                                                                                                                                  | ared                     | HS = Hardwa      | ire set          |                                |             |  |

| bit 7<br>bit 6    | 1 = Oscillator<br>0 = No oscilla                                                                                                                                                                                                                                                                           | ator Fail-Safe I<br>fail-safe interru<br>ator fail-safe inter<br>k Switch Comp                                                                                                                                                                                                                     | upt has occuri<br>errupt | red (must be cl  | eared in softwa  | re)                            |             |  |

| bit o             | 1 = The clock<br>operation                                                                                                                                                                                                                                                                                 | <ul> <li>CSWIF: Clock Switch Complete Interrupt Flag bit</li> <li>1 = The clock switch module indicates an interrupt condition and is ready to complete the clock switch operation (must be cleared in software)</li> <li>0 = The clock switch does not indicate an interrupt condition</li> </ul> |                          |                  |                  |                                |             |  |

| bit 5-2           | Unimplemen                                                                                                                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                                                                     | 0'                       |                  |                  |                                |             |  |

| bit 1             | 1 = An A/D m                                                                                                                                                                                                                                                                                               | og-to-Digital Co<br>leasurement wa<br>surements have                                                                                                                                                                                                                                               | as beyond the            | e configured thr | eshold (must b   | t Flag bit<br>e cleared in sof | tware)      |  |

| bit 0             | 1 = An A/D co                                                                                                                                                                                                                                                                                              | <ul> <li>ADIF: Analog-to-Digital Converter (ADC) Interrupt Flag bit</li> <li>1 = An A/D conversion or complex operation has completed (must be cleared in software)</li> <li>0 = An A/D conversion or complex operation is not complete</li> </ul>                                                 |                          |                  |                  |                                |             |  |

| c<br>it<br>E<br>u | Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit or the Global<br>Enable bit, GIE, of the INTCON register.<br>User software should ensure the<br>appropriate interrupt flag bits are clear<br>prior to enabling an interrupt. |                                                                                                                                                                                                                                                                                                    |                          |                  |                  |                                |             |  |

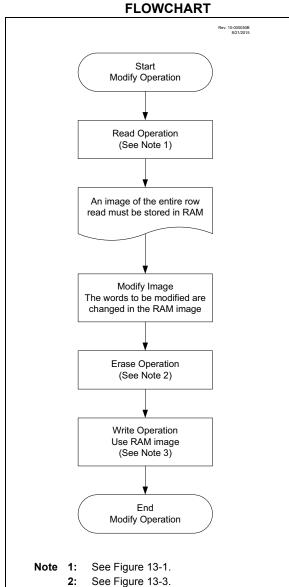

**FIGURE 13-6:**

#### 13.4.6 MODIFYING FLASH PROGRAM MEMORY

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

**FLASH PROGRAM**

MEMORY MODIFY

**3:** See Figure 13-5.

#### 14.4.7 ANALOG CONTROL

The ANSELB register (Register 14-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 14.4.8 WEAK PULL-UP CONTROL

The WPUB register (Register 14-5) controls the individual weak pull-ups for each PORT pin.

#### 14.4.9 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| R/W-0/0                 | R/W-0/0                                                                        | U-0                                                                                                                            | R/W-0/0                          | U-0            | U-0              | U-0              | R/W-0/0      |

|-------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|------------------|------------------|--------------|

| UART2MD                 | UART1MD                                                                        | —                                                                                                                              | MSSP1MD                          | —              | _                | —                | CWG1MD       |

| bit 7                   |                                                                                |                                                                                                                                |                                  |                |                  |                  | bit 0        |

|                         |                                                                                |                                                                                                                                |                                  |                |                  |                  |              |

| Legend:                 |                                                                                |                                                                                                                                |                                  |                |                  |                  |              |

| R = Readable            | bit                                                                            | W = Writable b                                                                                                                 | bit                              | U = Unimplem   | ented bit, read  | as '0'           |              |

| u = Bit is unch         | nanged                                                                         | x = Bit is unkn                                                                                                                | own                              | -n/n = Value a | t POR and BOR    | R/Value at all o | other Resets |

| '1' = Bit is set        |                                                                                | '0' = Bit is clea                                                                                                              | ired                             | q = Value dep  | ends on conditio | on               |              |

| bit 7<br>bit 6<br>bit 5 | 1 = EUSART2<br>0 = EUSART2<br><b>UART1MD</b> : D<br>1 = EUSART2<br>0 = EUSART2 | isable EUSAR <sup>-</sup><br>2 module disab<br>2 module enabl<br>isable EUSAR <sup>-</sup><br>1 module disab<br>1 module enabl | led<br>ed<br>F1 bit<br>led<br>ed |                |                  |                  |              |

| bit 4                   | MSSP1MD: D<br>1 = MSSP1 n                                                      | ted: Read as '0<br>bisable MSSP1<br>nodule disablec<br>nodule enabled                                                          | bit                              |                |                  |                  |              |

| bit 3-1<br>bit 0        | -                                                                              | ted: Read as '0<br>sable CWG1 bi                                                                                               |                                  |                |                  |                  |              |

|                         | 1 = CWG1 m                                                                     | odule disabled<br>odule enabled                                                                                                | -                                |                |                  |                  |              |

#### REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

#### REGISTER 19-11: ADACQL: ADC ACQUISITION TIME CONTROL REGISTER (LOW BYTE)

|                  |         |                   |         |                |                  | •              | ,            |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|                  |         |                   | ACQ     | <7:0>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable b   | bit     | W = Writable b    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | inged   | x = Bit is unkne  | own     | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | red     |                |                  |                |              |

bit 7-0 ACQ<7:0>: Acquisition (charge share time) Select bits See Table 19-6.

#### REGISTER 19-12: ADACQH: ADC ACQUISITION TIME CONTROL REGISTER (HIGH BYTE)

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     | —   |     |         |         | ACQ<12:8> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 ACQ<12:8>: Acquisition (charge share time) Select bits See Table 19-6.

#### TABLE 19-5: ACQUISITION TIME

| ADACQ            | Acquisition time                                         |

|------------------|----------------------------------------------------------|

| 1 1111 1111 1111 | 8191 clocks of the selected ADC clock                    |

| 1 1111 1111 1110 | 8190 clocks of the selected ADC clock                    |

| 1 1111 1111 1101 | 8189 clocks of the selected ADC clock                    |

|                  |                                                          |

| 0 0000 0000 0010 | 2 clocks of the selected ADC clock                       |

| 0 0000 0000 0001 | 1 clock of the selected ADC clock                        |

| 0 0000 0000 0000 | Not included in the data conversion cycle <sup>(1)</sup> |

**Note 1:** If ADPRE is not equal to '0', then ADACQ = b' 0\_0000\_0000 means Acquisition time is 8192 clocks of the selected ADC clock.

© 2017 Microchip Technology Inc.

| R/W-x/u          | R/W-x/u     | R/W-x/u                              | R/W-x/u         | R/W-x/u                            | R/W-x/u       | R/W-x/u          | R/W-x/u     |  |  |  |

|------------------|-------------|--------------------------------------|-----------------|------------------------------------|---------------|------------------|-------------|--|--|--|

| LCxG4D4T         | LCxG4D4N    | LCxG4D3T                             | LCxG4D3N        | LCxG4D2T                           | LCxG4D2N      | LCxG4D1T         | LCxG4D1N    |  |  |  |

| bit 7            |             |                                      |                 |                                    |               |                  | bit         |  |  |  |

|                  |             |                                      |                 |                                    |               |                  |             |  |  |  |

| Legend:          |             |                                      |                 |                                    |               |                  |             |  |  |  |

| R = Readable     |             | W = Writable                         |                 | U = Unimplemented bit, read as '0' |               |                  |             |  |  |  |

| u = Bit is unch  | anged       | x = Bit is unkr                      |                 | -n/n = Value a                     | at POR and BO | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is set |             | '0' = Bit is clea                    | ared            |                                    |               |                  |             |  |  |  |

| bit 7            | LCxG4D4T: ( | Gate 3 Data 4 1                      | rue (non-inve   | rted) bit                          |               |                  |             |  |  |  |

|                  |             | (true) is gated i                    |                 |                                    |               |                  |             |  |  |  |

|                  |             | (true) is not gat                    |                 |                                    |               |                  |             |  |  |  |

| bit 6            | LCxG4D4N:   | Gate 3 Data 4                        | Negated (inver  | rted) bit                          |               |                  |             |  |  |  |

|                  |             | (inverted) is ga                     |                 |                                    |               |                  |             |  |  |  |

|                  | 0 = CLCIN3  | (inverted) is no                     | t gated into Cl | _Cx Gate 3                         |               |                  |             |  |  |  |

| bit 5            |             | Gate 3 Data 3 1                      | · ·             | ,                                  |               |                  |             |  |  |  |

|                  |             | (true) is gated i                    |                 |                                    |               |                  |             |  |  |  |

| 1.11.4           |             | (true) is not gat                    |                 |                                    |               |                  |             |  |  |  |

| bit 4            |             | Gate 3 Data 3 I                      |                 |                                    |               |                  |             |  |  |  |

|                  |             | (inverted) is ga<br>(inverted) is no |                 |                                    |               |                  |             |  |  |  |

| bit 3            |             | Sate 3 Data 2 1                      | •               |                                    |               |                  |             |  |  |  |

|                  |             | (true) is gated i                    |                 | ,                                  |               |                  |             |  |  |  |

|                  |             | (true) is not gat                    |                 |                                    |               |                  |             |  |  |  |

| bit 2            | LCxG4D2N:   | Gate 3 Data 2 I                      | Negated (inver  | rted) bit                          |               |                  |             |  |  |  |

|                  |             | (inverted) is ga                     |                 |                                    |               |                  |             |  |  |  |

|                  | 0 = CLCIN1  | (inverted) is no                     | t gated into Cl | _Cx Gate 3                         |               |                  |             |  |  |  |

| bit 1            | LCxG4D1T: ( | Gate 4 Data 1 1                      | rue (non-inve   | rted) bit                          |               |                  |             |  |  |  |

|                  |             | (true) is gated i                    |                 |                                    |               |                  |             |  |  |  |

|                  |             | (true) is not gat                    |                 |                                    |               |                  |             |  |  |  |

| bit 0            |             | Gate 3 Data 1                        | •               | ,                                  |               |                  |             |  |  |  |

|                  |             | (inverted) is ga                     |                 |                                    |               |                  |             |  |  |  |

|                  | 0 = CLCINO  | (inverted) is no                     | i gated into Cl | Lox Gate 3                         |               |                  |             |  |  |  |

#### REGISTER 32-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

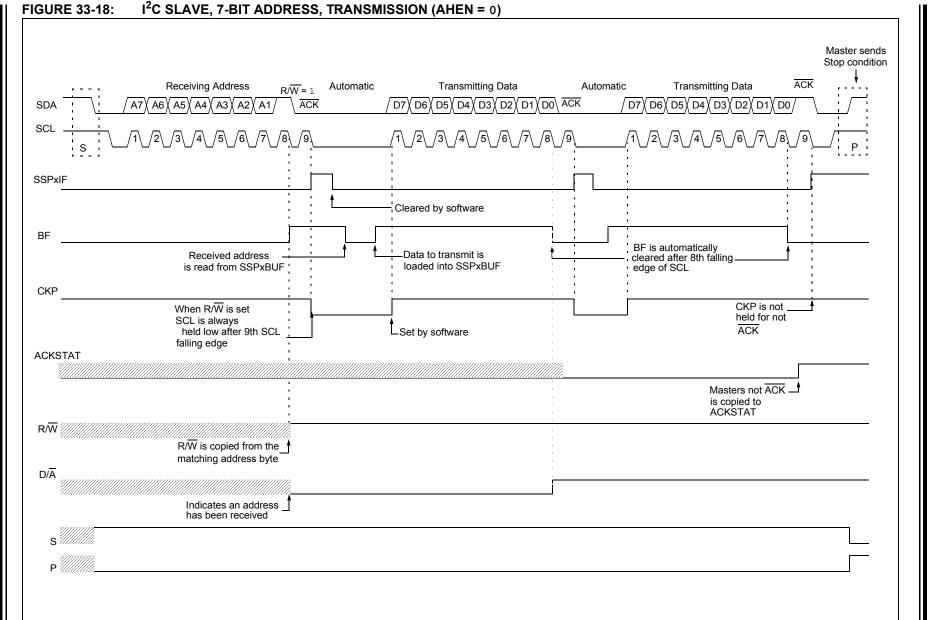

### 33.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 33-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSP module must be in an Idle      |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|

|       | state before the RCEN bit is set or the |  |  |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.           |  |  |  |  |  |  |  |  |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 33.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 33.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 33.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

- 33.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 6. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- User sets the RCEN bit of the SSPxCON2 register and the master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxBUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Master's ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

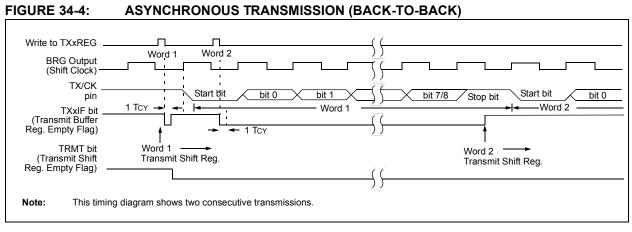

#### 34.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 34-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

#### 34.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

### 34.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 34.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RXxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 34.1.2.5 "Receive Overrun Error" for more information on overrun errors.

#### 34.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 9.2.2.2 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 34.3.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| R/W-0        | R/W-0                      | HS/C-0                                                                   | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0              |  |  |  |  |

|--------------|----------------------------|--------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|--------------------|--|--|--|--|

| LCDEN        | SLPEN                      | WERR                                                                     | CS              | LMUX3            | LMUX2           | LMUX1           | LMUX0              |  |  |  |  |

| bit 7        |                            |                                                                          |                 |                  |                 |                 | bit 0              |  |  |  |  |

| Legend:      |                            | C = Clearable                                                            | e bit           | HS = Bit is se   | t by hardware   |                 |                    |  |  |  |  |

| R = Readab   | le bit                     | W = Writable                                                             | bit             | U = Unimplen     | nented bit, rea | id as '0'       |                    |  |  |  |  |

| -n = Value a | t POR                      | '1' = Bit is set                                                         |                 | '0' = Bit is cle | ared            | x = Bit is unkr | x = Bit is unknown |  |  |  |  |

| bit 7        | LCDEN: LCD                 | Enable bit                                                               |                 |                  |                 |                 |                    |  |  |  |  |

|              |                            | lule is enabled<br>lule is disabled                                      |                 |                  |                 |                 |                    |  |  |  |  |

| bit 6        | SLPEN: LCD                 | Display Sleep-                                                           | Enabled bit     |                  |                 |                 |                    |  |  |  |  |

|              |                            | vill stop driving                                                        |                 |                  |                 |                 |                    |  |  |  |  |

|              |                            | vill continue driv                                                       |                 |                  |                 |                 |                    |  |  |  |  |

| bit 5        |                            | Write Failed Er                                                          |                 |                  |                 |                 |                    |  |  |  |  |

|              |                            | = Write failure to LCDDATA register occurred (must be reset in software) |                 |                  |                 |                 |                    |  |  |  |  |

|              | 0 = No LCD                 |                                                                          |                 |                  |                 |                 |                    |  |  |  |  |

| bit 4        |                            | Clock Source Select bit                                                  |                 |                  |                 |                 |                    |  |  |  |  |

|              | 1 = SOSC Se<br>0 = LFINTOS |                                                                          |                 |                  |                 |                 |                    |  |  |  |  |

| bit 3-0      |                            |                                                                          | tion hita Cna   | oifice the numb  | or of common    | _(2)            |                    |  |  |  |  |

| DIT 3-0      |                            | Common Selec                                                             | ction bits. Spe | cifies the numbe | er of commons   | 5(-)            |                    |  |  |  |  |

|              | LMUX<3                     | :0>                                                                      |                 | Multiplex        |                 |                 | Bias               |  |  |  |  |

|              | 0000                       |                                                                          |                 | All COMs off     |                 |                 | _                  |  |  |  |  |

|              | 0001                       |                                                                          |                 | Static (COM0)    |                 |                 | Static             |  |  |  |  |

|              | 0010                       |                                                                          | 1/2             | MUX (COM<1:      | 0>)             |                 | 1/2                |  |  |  |  |

|              | 0011                       |                                                                          | 1/3             | MUX (COM<2:      | 0>)             |                 | 1/3                |  |  |  |  |

|              | 0100                       |                                                                          | 1/4             | MUX (COM<3:      | 0>)             |                 | 1/3                |  |  |  |  |

|              | 0101                       |                                                                          | 1/5             | MUX (COM<4:      | 0>)             |                 | 1/3                |  |  |  |  |

|              | 0110                       |                                                                          | 1/6             | MUX (COM<5:      | 0>)             |                 | 1/3                |  |  |  |  |

|              | 0111                       |                                                                          | 1/7             | MUX (COM<6:      | 0>)             |                 | 1/3                |  |  |  |  |

|              | 1000                       |                                                                          | 1/8             | MUX (COM<7:      | 0>)             |                 | 1/3                |  |  |  |  |

#### REGISTER 35-1: LCDCON: LCD CONTROL REGISTER

Note 1: Bit can only be set by hardware and only cleared in software by writing to zero.

**2:** Cannot be changed when LCDEN = 1.

| Address         | Name     | Bit 7  | Bit 6         | Bit 5 | Bit 4           | Bit 3   | Bit 2     | Bit 1     | Bit 0   | Register<br>on page |  |  |

|-----------------|----------|--------|---------------|-------|-----------------|---------|-----------|-----------|---------|---------------------|--|--|

| 40Ch            | _        |        |               | •     | Unimpl          | emented |           | •         |         |                     |  |  |

| 40Dh            | HIDRVB   | _      | _             | —     | _               | _       | —         | HIDB1     | _       | 232                 |  |  |

| 40Eh            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 40Fh            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 410h            | —        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 411h            | —        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 412h            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 413h            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 414h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 415h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 416h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 417h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 418h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 419h            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 41Ah            | _        |        |               |       | Unimpl          | emented |           |           |         |                     |  |  |

| 41Bh            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 41Ch            |          |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 41Dh            |          |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 41Eh            | _        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

| 41Fh            | —        |        | Unimplemented |       |                 |         |           |           |         |                     |  |  |

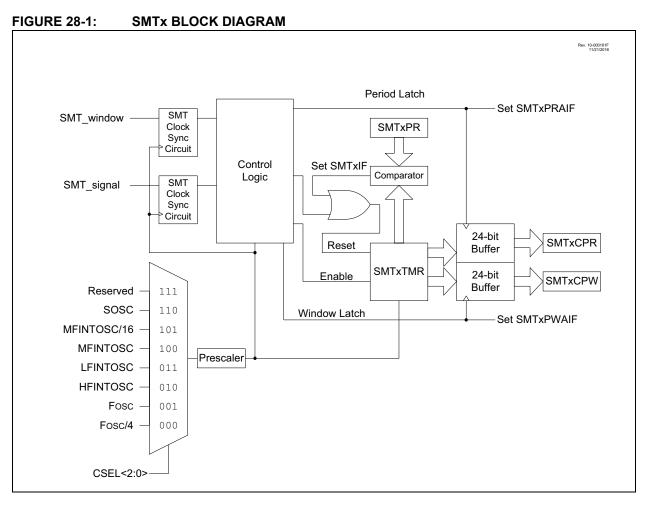

| 48Ch            | SMT1TMRL |        |               |       | SMT             | 1TMR    |           |           |         | 416                 |  |  |

| 48Dh            | SMT1TMRH |        | SMT1TMR       |       |                 |         |           |           |         |                     |  |  |

| 48Eh            | SMT1TMRU |        |               |       | SMT             | 1TMR    |           |           |         | 416                 |  |  |

| 48Fh            | SMT1CPRL |        | CPR           |       |                 |         |           |           |         |                     |  |  |

| 490h            | SMT1CPRH |        |               |       | С               | PR      |           |           |         | 417                 |  |  |

| 491h            | SMT1CPRU |        |               |       | С               | PR      |           |           |         | 417                 |  |  |

| 492h            | SMT1CPWL |        |               |       | С               | PW      |           |           |         | 418                 |  |  |

| 493h            | SMT1CPWH |        |               |       | С               | PW      |           |           |         | 418                 |  |  |

| 494h            | SMT1CPWU |        | CPW 2         |       |                 |         |           |           |         |                     |  |  |

| 495h            | SMT1PRL  |        |               |       |                 | T1PR    |           |           |         | 419                 |  |  |

| 496h            | SMT1PRH  |        |               |       |                 | Г1PR    |           |           |         | 419                 |  |  |

| 497h            | SMT1PRU  |        |               |       |                 | Г1PR    |           |           |         | 419                 |  |  |

| 497h<br>498h    | SMT1CON0 | EN     |               | STP   | WPOL            | SPOL    | CPOL      | CMT4      | PS<1.0> | 419                 |  |  |

| 49011<br>499h   | SMT1CON0 | SMT1GO | REPEAT        |       |                 |         |           |           |         |                     |  |  |

|                 |          |        |               | DOT   | — MODE<3:0>     |         |           |           |         | 411                 |  |  |

| 49Ah            | SMT1STAT | CPRUP  | CPWUP         | RST   |                 | _       | TS        | WS        | AS      | 412                 |  |  |

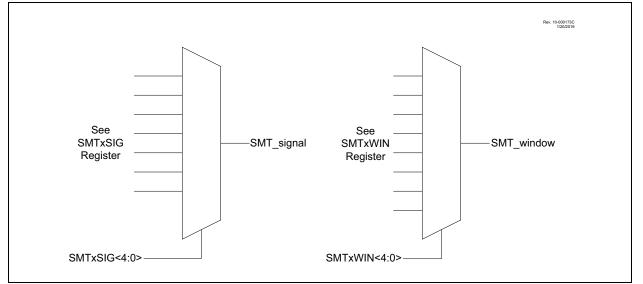

| 49Bh            | SMT1CLK  |        |               |       |                 |         |           | CSEL<2:0> |         | 413<br>415          |  |  |

| 49Ch            | SMT1SIG  | _      |               | _     | SSEL<4:0>       |         |           |           |         |                     |  |  |

| 49Dh<br>Legend: | SMT1WIN  |        |               |       | = unimplemented |         | WSEL<4:0> |           |         | 414                 |  |  |

### TABLE 38-1: REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

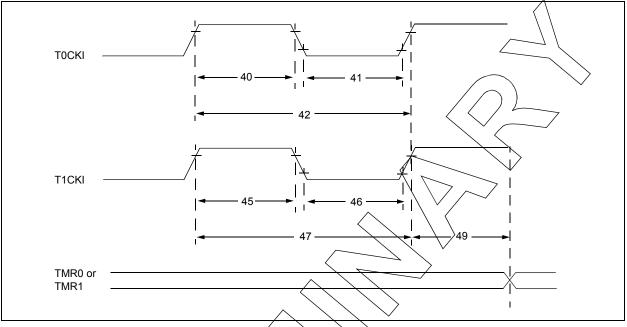

### TABLE 39-19: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param.<br>No.     | Sym.                                   | Characteristic            |                     |                | Min.                                      | Тур†   | Max. | Units                  | Conditions        |

|-------------------|----------------------------------------|---------------------------|---------------------|----------------|-------------------------------------------|--------|------|------------------------|-------------------|

| 40*               | T⊤0H                                   | T0CKI High F              | Pulse Width         | No Prescaler   | 0.5 Tcy + 20                              | —      |      | ns                     |                   |

|                   |                                        |                           |                     | With Prescaler | 10                                        | _      |      | ns                     |                   |

| 41*               | T⊤0L                                   | TOCKI LOW P               | ulse Width //       | No Prescaler   | 0.5 Tcy + 20                              | _      | _    | ns                     |                   |

|                   |                                        | $  \rangle \rangle$       | $\smallsetminus$    | With Prescaler | 10                                        | _      | _    | ns                     |                   |

| 42*               | Ттор                                   | 70CKI Period              |                     |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _    | ns                     | N = prescale valu |

| 45*               | TT1H                                   | TICKI High                | Synchronous, N      | lo Prescaler   | 0.5 Tcy + 20                              | —      | _    | ns                     |                   |

|                   |                                        | Time                      | Śynchronous, w      | vith Prescaler | 15                                        | _      |      | ns                     |                   |

|                   |                                        |                           | Asynchronous        |                | 30                                        | _      |      | ns                     |                   |

| 46*               | Tų 1L                                  | T1CKI Low                 | Synchronous, N      | lo Prescaler   | 0.5 Tcy + 20                              |        |      | ns                     |                   |

|                   | $\backslash \setminus \langle \rangle$ | Time                      | Synchronous, w      | vith Prescaler | 15                                        |        |      | ns                     |                   |

| $\left( -\right)$ |                                        | 5                         | Asynchronous        |                | 30                                        | _      |      | ns                     |                   |

| 47*               | Ттір                                   | T1CKI Input<br>Period     | Synchronous         |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _      | _    | ns                     | N = prescale valu |

| $\sim$            | $\searrow$                             |                           | Asynchronous        |                | 60                                        | _      | _    | ns                     |                   |

| 48                | ET7                                    |                           | scillator Input Fre |                | 32.4                                      | 32.768 | 33.1 | kHz                    |                   |

| 49*               | TCKEZTMR1                              | Delay from E<br>Increment | xternal Clock Ed    | 2 Tosc         | —                                         | 7 Tosc | —    | Timers in Sync<br>mode |                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

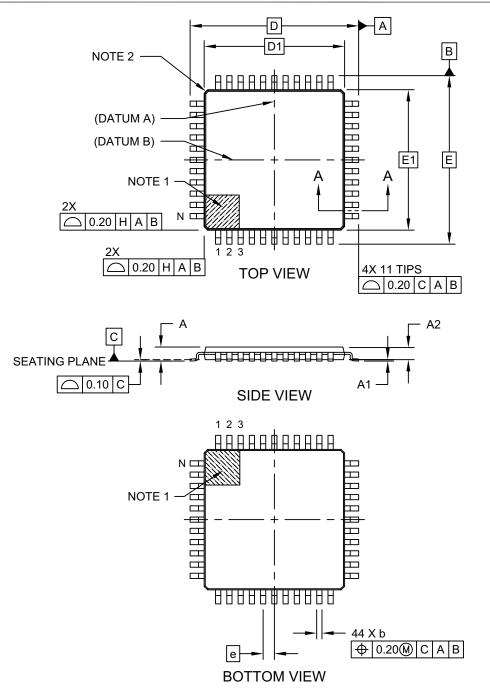

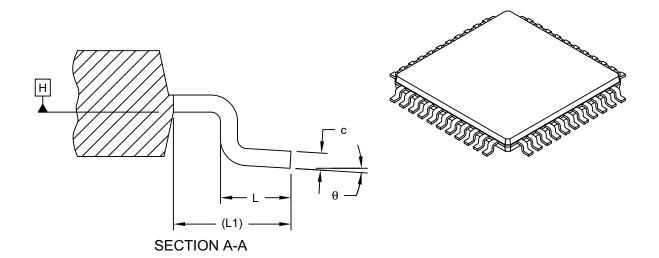

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

Microchip Technology Drawing C04-076C Sheet 1 of 2

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |  |

|--------------------------|-------------|-----------|------|------|--|--|

| Dimension                | MIN         | NOM       | MAX  |      |  |  |

| Number of Leads          | N           | 44        |      |      |  |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |  |

| Overall Height           | A           | -         | -    | 1.20 |  |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |  |

| Lead Length              | L           | 0.45      | 0.60 | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF  |      |      |  |  |

| Foot Angle               | θ           | 0°        | 3.5° | 7°   |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2