Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 43                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-TQFP                                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19185-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE              | - 3:                   | 2           | 8-PIN AL         | LOCA      | ATION          | ABL               | .E (PIC16    | (L)F19155                                      | /56) (C             | ONTIN        | UED)                             |                                                             |                                          |                       |             |                        |                     |              |         |                    |

|--------------------|------------------------|-------------|------------------|-----------|----------------|-------------------|--------------|------------------------------------------------|---------------------|--------------|----------------------------------|-------------------------------------------------------------|------------------------------------------|-----------------------|-------------|------------------------|---------------------|--------------|---------|--------------------|

| (2)O/I             | 28-Pin SPDIP/SSOP/SOIC | 28-Pin UQFN | ADC              | Reference | Comparator     | Zero-Cross Detect | DAC          | Timers/SMT                                     | CCP                 | WMd          | CWG                              | dssm                                                        | EUSART                                   | CLC                   | RTCC        | ГСD                    | Interrupt-on-Change | High Current | dn-IInd | Basic              |

| RB6                | 27                     | 24          | ANB6             | I         | _              |                   | _            | -                                              |                     | _            |                                  | _                                                           | TX2 <sup>(1)</sup><br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> | _           | SEG14                  | IOCB6               | _            | Y       | ICDCLK/<br>ICSPCLK |

| RB7                | 28                     | 25          | ANB7             | I         | _              |                   | DAC1OUT2     |                                                |                     | _            |                                  | _                                                           | RX2 <sup>(1)</sup><br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | _           | SEG15                  | IOCB7               | —            | Y       | ICDDAT/<br>ICSPDAT |

| RC0                | 11                     | 8           | _                |           | _              |                   | _            | T1CKI <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> |                     | _            | _                                | —                                                           |                                          | —                     | _           |                        | IOCC0               | —            | Y       | SOSCO              |

| RC1                | 12                     | 9           | _                | _         | _              | _                 | _            | SMTSIG1 <sup>(1)</sup><br>T4IN <sup>(1)</sup>  | CCP2 <sup>(1)</sup> | _            | _                                | —                                                           | -                                        | _                     | _           | -                      | IOCC1               | _            | Y       | SOSCI              |

| RC2                | 13                     | 10          | ANC2             | -         | _              | _                 | -            | -                                              | CCP1 <sup>(1)</sup> | _            | _                                | —                                                           | -                                        | -                     |             | COM2<br>SEG18          | IOCC2               | _            | Y       | _                  |

| RC3                | 14                     | 11          | ANC3             | -         | —              | _                 | -            | T2IN <sup>(1)</sup>                            | -                   | _            | _                                | SCK <sup>(1)</sup><br>SCL <sup>(1,3,4)</sup>                |                                          | -                     | -           | SEG19                  | IOCC3               | _            | Y       | _                  |

| RC4                | 15                     | 12          | ANC4             | _         | _              | _                 | _            | —                                              | _                   | _            | _                                | SDI <sup>(1)</sup><br>SDA <sup>(1,3,4)</sup>                | _                                        | -                     | _           | SEG20                  | IOCC4               | _            | Y       | _                  |

| RC6                | 17                     | 14          | ANC6             | Ι         | _              |                   | _            | _                                              | _                   |              | _                                | _                                                           | TX1 <sup>(1)</sup><br>CK1 <sup>(1)</sup> | _                     | Ι           | COM5<br>SEG22<br>VLCD2 | IOCC6               | _            | Y       | _                  |

| RC7                | 18                     | 15          | ANC7             | Ι         | _              | _                 | -            | _                                              | _                   | -            | _                                | —                                                           | RX1 <sup>(1)</sup><br>DT1 <sup>(1)</sup> | —                     | Ι           | SEG23<br>COM4<br>VLCD1 | IOCC7               | _            | Y       | _                  |

| RE3                | 1                      | 26          |                  | —         | —              |                   | _            |                                                | -                   | —            |                                  | _                                                           | -                                        | —                     | _           | -                      | IOCE3               | _            | Υ       | MCLR               |

| VLCD3              | 16                     | 13          | _                | _         | —              |                   | _            | _                                              | _                   | —            | _                                | _                                                           | _                                        | —                     | _           | VLCD3                  | —                   | _            | —       | _                  |

| Vdd                | 20                     | 17          | _                | —         | —              | _                 | _            | _                                              | _                   | —            | _                                | —                                                           | —                                        | —                     | _           | _                      | —                   | _            | —       | Vdd                |

| Vss                | 8<br>19                | 5<br>16     | _                | _         | —              | —                 | _            | _                                              | _                   | _            | _                                | _                                                           | _                                        | —                     | _           | _                      | —                   | —            | —       | Vss                |

| OUT <sup>(2)</sup> |                        | _           | ADGRDA<br>ADGRDB | _         | C1OUT<br>C2OUT |                   | _            | TMR0                                           | CCP1<br>CCP2        | PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | SDO<br>SCK<br>SCL<br>SDA                                    | TX1<br>DT1<br>CK1<br>TX2<br>DT2<br>CK2   | CLC1OUT               | RTCC        | _                      | —                   | _            | _       | _                  |

|                    | 2: /                   | All digit   | al output sign   | als show  | /n in this ro  | w are I           | PPS remappat | le. These sign                                 | als may be          | e mapped     | to output ont                    | one of several ot<br>o one or more Po<br>oin in both the PF | ORTx pin (                               | options.              | ıt register | rs.                    |                     |              |         |                    |

### TABLE 3 28-PIN ALLOCATION TABLE (PIC16(L)E19155/56) (CONTINUED)

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by INLCVL register, instead of the I<sup>2</sup>C specific or 4: SMBUS input buffer thresholds.

These are alternative I<sup>2</sup>C logic levels pins. 5:

In I<sup>2</sup>C logic levels configuration, these pins can operate as either SCL and SDA pins. 6:

© 2017 Microchip Technology Inc.

Preliminary

| Address | Name | Bit 7 | Bit 6 | Bit 5 | Bit 4         | Bit 3               | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |

|---------|------|-------|-------|-------|---------------|---------------------|-------------|-------|-------|-----------------------|----------------------------|

| Bank 10 |      |       |       |       |               |                     |             |       |       |                       |                            |

|         |      |       |       | CPU   | CORE REGISTER | S; see Table 4-3 fo | r specifics |       |       |                       |                            |

| 50Ch    | _    |       |       |       | Unimple       | mented              |             |       |       |                       |                            |

| 50Dh    |      |       |       |       | Unimple       |                     |             |       |       |                       |                            |

| 50Eh    | _    |       |       |       | Unimple       |                     |             |       |       |                       |                            |

| 50Fh    |      |       |       |       | Unimple       |                     |             |       |       |                       |                            |

| 510h    | _    |       |       |       | · · ·         | emented             |             |       |       |                       |                            |

| 511h    | _    |       |       |       | Unimple       |                     |             |       |       |                       |                            |

| 512h    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 513h    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 514h    |      |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 515h    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 516h    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 517h    | —    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 518h    | —    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 519h    | —    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Ah    | —    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Bh    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Ch    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Dh    |      |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Eh    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

| 51Fh    | _    |       |       |       | Unimple       | emented             |             |       |       |                       |                            |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Preliminary

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

# 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing.

Refer to Table 7-1 for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

# TABLE 7-1: DEVICE CONFIGURATION INFORMATION FOR PIC16(L)F19155/56/75/76/85/86 FAMILY OF DEVICES

| ADDRESS | Name  | DESCRIPTION             | VALUE         | UNITS |

|---------|-------|-------------------------|---------------|-------|

| 8200h   | ERSIZ | Erase Row Size          | 32            | Words |

| 8201h   | WLSIZ | Number of write latches | 32            |       |

| 8202h   | URSIZ | Number of User Rows     | See Table 7-2 | Rows  |

| 8203h   | EESIZ | EE Data memory size     | 256           | Bytes |

| 8204h   | PCNT  | Pin Count               | 28/40/44/48   | Pins  |

### TABLE 7-2: MEMORY SIZE AND NUMBER OF USER ROWS

| Part Name      | Memory size | Number of User rows |

|----------------|-------------|---------------------|

| PIC16(L)F19155 | 8k          | 256                 |

| PIC16(L)F19175 | 8k          | 256                 |

| PIC16(L)F19185 | 8k          | 256                 |

| PIC16(L)F19156 | 16k         | 512                 |

| PIC16(L)F19176 | 16k         | 512                 |

| PIC16(L)F19186 | 16k         | 512                 |

### 7.1 DIA and DCI Access

The DIA and DCI addresses are read-only and cannot be erased or modified. See Section 13.4.7 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

| Name    | Bit 7   | Bit 6   | Bit 5     | Bit 4 | Bit 3   | Bit 2      | Bit 1  | Bit 0 | Register<br>on Page |

|---------|---------|---------|-----------|-------|---------|------------|--------|-------|---------------------|

| OSCCON1 | —       |         | NOSC<2:0> |       |         | NDIV<      | 3:0>   |       | 152                 |

| OSCCON2 | —       |         | COSC<2:0> |       |         | CDIV<3:0>  |        |       |                     |

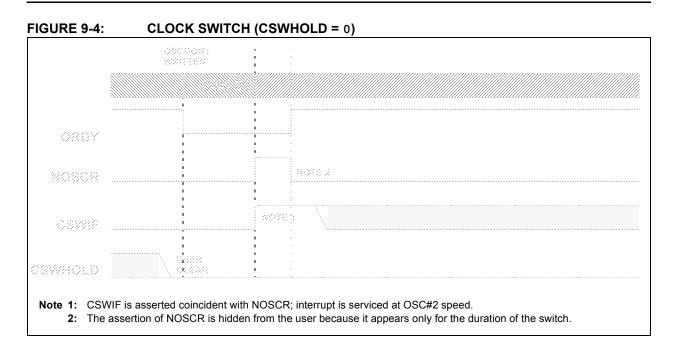

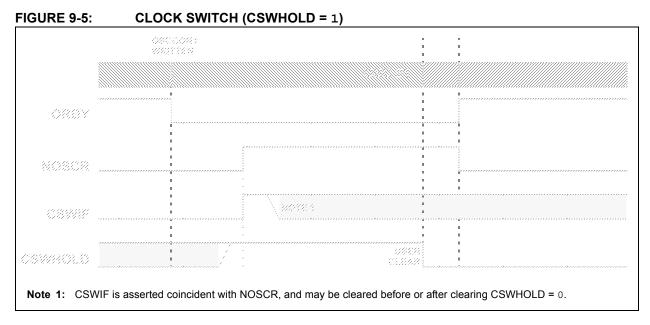

| OSCCON3 | CWSHOLD | SOSCPWR | _         | ORDY  | NOSCR   | _          | _      | -     | 154                 |

| OSCFRQ  | _       | _       | _         | _     | _       | HFFRQ<2:0> |        |       | 157                 |

| OSCSTAT | EXTOR   | HFOR    | MFOR      | LFOR  | SOR     | ADOR       | —      | PLLR  | 155                 |

| OSCTUNE | —       | _       |           |       | HFTUN   | HFTUN<5:0> |        |       |                     |

| OSCEN   | EXTOEN  | HFOEN   | MFOEN     | LFOEN | SOSCEN  | ADOEN      | _      | _     | 156                 |

| ACTCON  | ACTEN   | ACTUD   | _         | _     | ACTLOCK | _          | ACTORS |       | 158                 |

### TABLE 9-3:SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 9-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|----------|------------|----------|---------------------|

| CONFIG1 | 13:8 | —       | _       | FCMEN      | _        | CSWEN    | LCDPEN   | VBATEN     | CLKOUTEN | 100                 |

| CONFIGT | 7:0  | —       | F       | RSTOSC<2:0 | >        | _        | I        | EXTOSC<2:0 | >        | 120                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### REGISTER 10-13: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|------------|-----|-----|-----|-----|------------|------------|

| _     | ZCDIF      |     |     | _   | _   | C2IF       | C1IF       |

| bit 7 |            |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ZCDIF: Zero-Cross Detect (ZCD1) Interrupt Flag bit                                                                                                             |

|         | <ul> <li>1 = An enabled rising and/or falling ZCD1 event has been detected (must be cleared in software)</li> <li>0 = No ZCD1 event has occurred</li> </ul>    |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1   | <b>C2IF</b> : Comparator C2 Interrupt Flag bit<br>1 = Comparator 2 interrupt asserted (must be cleared in software)<br>0 = Comparator 2 interrupt not asserted |

| bit 0   | <b>C1IF:</b> Comparator C1 Interrupt Flag bit<br>1 = Comparator 1 interrupt asserted (must be cleared in software)<br>0 = Comparator 1 interrupt not asserted  |

| Note:   | Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of                                                                     |

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |

### 13.2 Data EEPROM Memory

Data EEPROM Memory consists of 256 bytes of user data memory. The EEPROM provides storage locations for 8-bit user defined data. EEPROM can be read and/or written through:

- FSR/INDF indirect access (Section 13.3 "FSR and INDF Access")

- NVMREG access (Section 13.4 "NVMREG Access")

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Unlike PFM, which must be written to by row, EEPROM can be written to word by word.

### 13.3 FSR and INDF Access

The FSR and INDF registers allow indirect access to the PFM.

### 13.3.1 FSR READ

With the intended address loaded into an FSR register a MOVIW instruction or read of INDF will read data from the PFM.

Reading from NVM requires one instruction cycle. The CPU operation is suspended during the read, and resumes immediately after. Read operations return a single byte of memory.

### 13.3.2 FSR WRITE

Writing/erasing the NVM through the FSR registers (ex. MOVWI instruction) is not supported in the PIC16(L)F19155/56/75/76/85/86 devices.

### 13.4 NVMREG Access

The NVMREG interface allows read/write access to all the locations accessible by FSRs, and also read/write access to the User ID locations, and read-only access to the device identification, revision, and Configuration data.

Writing, or erasing of NVM via the NVMREG interface is prevented when the device is write-protected.

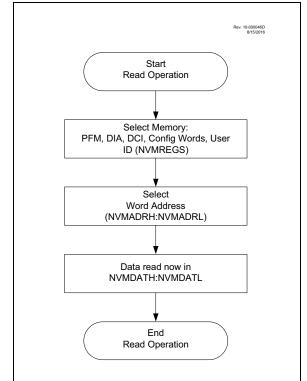

### 13.4.1 NVMREG READ OPERATION

To read a NVM location using the NVMREG interface, the user must:

- Clear the NVMREGS bit of the NVMCON1 register if the user intends to access PFM locations, or set NMVREGS if the user intends to access User ID, or Configuration locations.

- Write the desired address into the NVMADRH:NVMADRL register pair (Table 13-2).

- 3. Set the RD bit of the NVMCON1 register to initiate the read.

Once the read control bit is set, the CPU operation is suspended during the read, and resumes immediately after. The data is available in the very next cycle, in the NVMDATH:NVMDATL register pair; therefore, it can be read as two bytes in the following instructions.

NVMDATH:NVMDATL register pair will hold this value until another read or until it is written to by the user.

Upon completion, the RD bit is cleared by hardware.

# FIGURE 13-1:

### FLASH PROGRAM MEMORY READ FLOWCHART

# 21.6 Register Definitions: DAC Control

### REGISTER 21-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0        | U-0                                                                                                                                                                                                                                                        | R/W-0/0                                                                 | R/W-0/0                         | R/W-0/0        | R/W-0/0          | U-0              | U-0         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------|----------------|------------------|------------------|-------------|

| DAC1EN         | I                                                                                                                                                                                                                                                          | DAC10E1                                                                 | DAC10E2                         | DAC1P          | SS<1:0>          | —                | —           |

| bit 7          |                                                                                                                                                                                                                                                            |                                                                         |                                 |                |                  |                  | bit 0       |

| Lonordi        |                                                                                                                                                                                                                                                            |                                                                         |                                 |                |                  |                  |             |

| Legend:        | 1.1.1                                                                                                                                                                                                                                                      |                                                                         |                                 |                |                  | (0)              |             |

| R = Readab     | ble bit                                                                                                                                                                                                                                                    | W = Writable                                                            | bit                             |                | nented bit, read |                  |             |

| u = Bit is un  | changed                                                                                                                                                                                                                                                    | x = Bit is unkr                                                         | nown                            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is s | et                                                                                                                                                                                                                                                         | '0' = Bit is clea                                                       | ared                            |                |                  |                  |             |

| bit 6<br>bit 5 | <b>DAC10E1:</b> D<br>1 = DAC volt                                                                                                                                                                                                                          | ited: Read as '<br>AC1 Voltage C<br>age level is an<br>age level is dis | output 1 Enabl<br>output on the | DAC1OUT1 pi    |                  |                  |             |

| bit 4          | 1 = DAC volt                                                                                                                                                                                                                                               | AC1 Voltage C<br>age level is an<br>age level is dis                    | output on the                   | DAC1OUT2 pi    |                  |                  |             |

| bit 3-2        | <ul> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> <li>it 3-2 DAC1PSS&lt;1:0&gt;: DAC1 Positive Source Select bits</li> <li>11 = Reserved, do not use</li> <li>10 = FVR output</li> <li>01 = VREF+ pin</li> <li>00 = VDD</li> </ul> |                                                                         |                                 |                |                  |                  |             |

bit 1-0 Unimplemented: Read as '0'

### REGISTER 21-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 4-0 DAC1R<4:0>: DAC1 Voltage Output Select bits VOUT = (VSRC+ - VSRC-)\*(DAC1R<4:0>/32) + VSRC

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x     | R/W-x |

|---------|-----|-----|-----|-----|-------|-----------|-------|

| —       | —   | —   | —   | —   |       | WDAY<2:0> |       |

| bit 7   |     |     |     |     |       |           | bit 0 |

|         |     |     |     |     |       |           |       |

| Legend: |     |     |     |     |       |           |       |

### **REGISTER 24-5:** WEEKDAY<sup>(1)</sup>: WEEKDAY VALUE REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY<2:0>: Binary Coded Decimal value of weekdays '1' digit; valid values from 0 to 6

**Note 1:** Writes to the WDAY registers are only allowed when RTCWREN = 1.

### REGISTER 24-6: DAY<sup>(1)</sup>: DAY VALUE REGISTER

| U-0   | U-0 | R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----------|-------|-------|-------|-------|-------|

| —     | —   | DAYH<1:0> |       |       | DAYL  | <3:0> |       |

| bit 7 |     |           |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 5-4 DAYH<1:0>: Binary Coded Decimal value of days '10' digit; valid values from 0 to 3

bit 3-0 DAYL<3:0>: Binary Coded Decimal value of days '1' digit; valid values from 0 to 9

**Note 1:** Writes to the DAY registers are only allowed when RTCWREN = 1.

## REGISTER 24-7: HOURS<sup>(1)</sup>: HOUR VALUE REGISTER

| U-0   | U-0 | R/W-x    | R/W-x | R/W-x    | R/W-x | R/W-x | R/W-x |

|-------|-----|----------|-------|----------|-------|-------|-------|

| —     | —   | HRH<1:0> |       | HRL<3:0> |       |       |       |

| bit 7 |     |          |       |          |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 5-4 HRH<1:0>: Binary Coded Decimal value of hours '10' digit; valid values from 0 to 2

bit 3-0 HRL<3:0>: Binary Coded Decimal value of hours '1' digit; valid values from 0 to 9

**Note 1:** Writes to the HOURS registers are only allowed when RTCWREN = 1.

### 27.5 Operation Examples

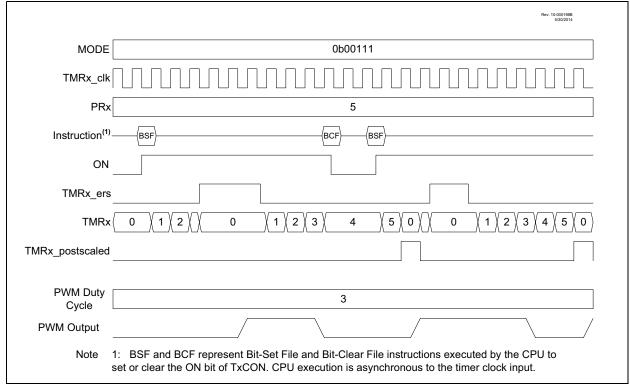

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2/4\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2/4\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in **Section 29.0 "Capture/Compare/PWM Modules"**. The signals are not a part of the Timer2/4 module.

### 27.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2/4 operation. The timer increments with each clock input when ON = 1 and does not increment when ON = 0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 27-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

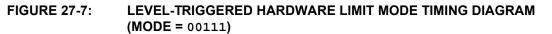

### 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

### 34.4.1.6 Slave Clock

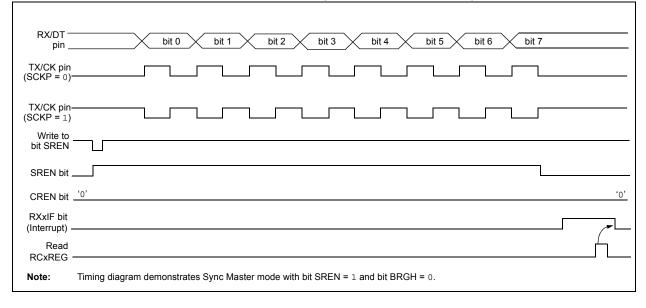

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and  |

|-------|---------------------------------------------|

|       | the TX/CK function is on an analog pin, the |

|       | corresponding ANSEL bit must be cleared.    |

### 34.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

### 34.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

# 34.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPxBRGH, SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RXxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RXxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

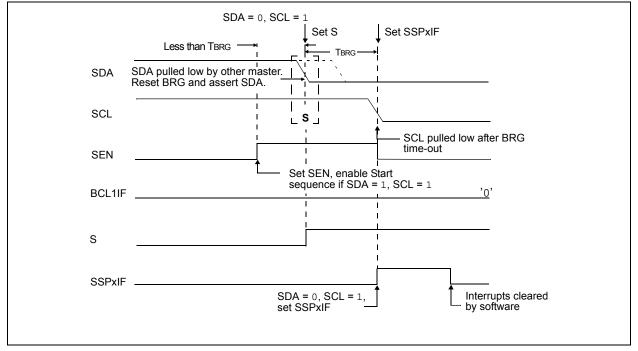

### FIGURE 34-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 35.8 LCD Multiplex Types

The LCD driver module can be configured into four multiplex types:

- Static (only COM0 used)

- 1/2 multiplex (COM0 and COM1 are used)

- 1/3 multiplex (COM0, COM1 and COM2 are used)1/4 multiplex (COM0, COM1, COM2 and COM3

- are used)1/5 multiplex (COM0, COM1, COM2, COM3 and COM4 are used)

- 1/6 multiplex (COM0, COM1, COM2, COM3, COM4 and COM5 are used)

- 1/7 multiplex (COM0, COM1, COM2, COM3, COM4, COM5 and COM6 are used)

- 1/8 multiplex (COM0, COM1, COM2, COM3, COM4, COM5, COM6 and COM7 are used)

The LMUX<3:0> setting (LCDCON<3:0>) decides the function of the COM pins. (For details, see Table 35-8).

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. If the pin is a COM drive, the TRIS setting of that pin is overridden.

Note: On a Power-on Reset, the LMUX<3:0> bits are '0000'.

| LMUX<3:0> | COM7 Pin | COM6 Pin | COM5 Pin | COM4 Pin | COM3 Pin | COM2 Pin | COM1 Pin | COM0 Pin |

|-----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 1000      | COM7     | COM6     | COM5     | COM4     | COM3     | COM2     | COM1     | COM0     |

| 0111      | I/O Pin  | COM6     | COM5     | COM4     | COM3     | COM2     | COM1     | COM0     |

| 0110      | I/O Pin  | I/O Pin  | COM5     | COM4     | COM3     | COM2     | COM1     | COM0     |

| 0101      | I/O Pin  | I/O Pin  | I/O Pin  | COM4     | COM3     | COM2     | COM1     | COM0     |

| 0100      | I/O Pin  | I/O Pin  | I/O Pin  | I/O Pin  | COM3     | COM2     | COM1     | COM0     |

| 0011      | I/O Pin  | COM2     | COM1     | COM0     |

| 0010      | I/O Pin  | COM1     | COM0     |

| 0001      | I/O Pin  | COM0     |

| 0000      | I/O Pin  |

### TABLE 35-8: COM<7:0> PIN FUNCTIONS

|           |       | -     |       |         |       | i     | (     |       | <u>, '</u>          |

|-----------|-------|-------|-------|---------|-------|-------|-------|-------|---------------------|

| Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

| LCDDATA34 | S47C5 | S46C5 | S45C5 | S44C5   | S43C5 | S42C5 | S41C5 | S40C5 | 624                 |

| LCDDATA35 | S07C6 | S06C6 | —     | S04C6   | S03C6 | S02C6 | S01C6 | S00C6 | 624                 |

| LCDDATA36 | S15C6 | S14C6 | S13C6 | _       | S11C6 | S10C6 | S09C6 | S08C6 | 624                 |

| LCDDATA37 | S23C6 | S22C6 | —     | S20C6   | S19C6 | S18C6 | —     | _     | 624                 |

| LCDDATA38 | S31C6 | S30C6 | S29C6 | S28C6   | S27C6 | S26C6 | S25C6 | S24C6 | 624                 |

| LCDDATA39 | _     | _     | _     | _       | _     | S34C6 | S33C6 | S32C6 | 624                 |

| LCDDATA40 | S47C6 | S46C6 | S45C6 | S44C6   | S43C6 | S42C6 | S41C6 | S40C6 | 624                 |

| LCDDATA41 | S07C7 | S06C7 | _     | S04C7   | S03C7 | S02C7 | S01C7 | S00C7 | 624                 |

| LCDDATA42 | S15C7 | S14C7 | S13C7 | _       | S11C7 | S10C7 | S09C7 | S08C7 | 624                 |

| LCDDATA43 | S23C7 | S22C7 | _     | S20C7   | S19C7 | S18C7 | —     | _     | 624                 |

| LCDDATA44 | S31C7 | S30C7 | S29C7 | S28C7   | S27C7 | S26C7 | S25C7 | S24C7 | 624                 |

| LCDDATA45 | —     | —     | —     | —       | _     | S34C7 | S33C7 | S32C7 | 624                 |

| LCDDATA46 | S47C7 | S46C7 | S45C7 | S44C7   | S43C7 | S42C7 | S41C7 | S40C7 | 624                 |

| LCDDATA47 | S07C0 | S06C0 | _     | S04COM0 | S03C0 | S02C0 | S01C0 | S00C0 | 624                 |

### TABLE 35-10: SUMMARY OF REGISTERS ASSOCIATED WITH LCD MODULE (CONTINUED)

| Address | Name       | Bit 7         | Bit 6         | Bit 5 | Bit 4                                 | Bit 3   | Bit 2        | Bit 1 | Bit 0 | Register<br>on page |  |

|---------|------------|---------------|---------------|-------|---------------------------------------|---------|--------------|-------|-------|---------------------|--|

| 1E95h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1E96h   | _          | Unimplemented |               |       |                                       |         |              |       |       |                     |  |

| 1E97h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E98h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E99h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Ah   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Bh   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1E9Ch   | T2AINPPS   | _             | _             | _     |                                       |         | T2INPPS<4:0  | >     |       | 264                 |  |

| 1E9Dh   | T4AINPPS   | —             | _             | _     |                                       |         | T4INPPS<4:0  | >     |       | 264                 |  |

| 1E9Eh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1E9Fh   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA0h   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA1h   | CCP1PPS    | _             | —             | _     |                                       |         | CCP1PPS<4:0  | >     |       | 264                 |  |

| 1EA2h   | CCP2PPS    | _             | —             | _     |                                       |         | CCP2PPS<4:0  | >     |       | 264                 |  |

| 1EA3h   | _          |               |               | •     | Unimpl                                | emented |              |       |       |                     |  |

| 1EA4h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA5h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA6h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1EA7h   | _          |               | Unimplemented |       |                                       |         |              |       |       |                     |  |

| 1EA8h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EA9h   | SMT1WINPPS | _             | _             | _     |                                       | S       | MT1WINPPS<4  | 1:0>  |       | 264                 |  |

| 1EAAh   | SMT1SIGPPS | _             | _             | _     |                                       | S       | MT1SIGPPS<4  | :0>   |       | 264                 |  |

| 1EABh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EACh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EADh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EAEh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EAFh   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB0h   | -          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB1h   | CWG1PPS    | _             | _             | _     |                                       |         | CWG1PPS<4:0  | )>    |       | 264                 |  |

| 1EB2h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB3h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB4h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB5h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB6h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB7h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB8h   | _          |               |               |       | Unimpl                                | emented |              |       |       |                     |  |

| 1EB9h   |            |               |               |       | · · · · · · · · · · · · · · · · · · · | emented |              |       |       |                     |  |

| 1EBAh   | _          |               |               |       | •                                     | emented |              |       |       |                     |  |

| 1EBBh   | CLCIN0PPS  | _             | _             | _     |                                       |         | CLCIN0PPS<4: | 0>    |       | 264                 |  |

| 1EBCh   | CLCIN1PPS  | _             | _             | _     |                                       |         | CLCIN1PPS<4: |       |       | 264                 |  |

| 1EBDh   | CLCIN2PPS  | _             |               | _     |                                       |         | CLCIN2PPS<4: |       |       | 264                 |  |

### TABLE 38-1:REGISTER FILE SUMMARY FOR PIC16(L)F19155/56/75/76/85/86 DEVICES

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| Standar       | d Operati          | ng Conditions (unless otherwise stated                 | )             |              |                   |                   | $\sim$                                        |

|---------------|--------------------|--------------------------------------------------------|---------------|--------------|-------------------|-------------------|-----------------------------------------------|

| Param.<br>No. | Sym.               | Characteristic                                         | Min.          | Тур†         | Max.              | Units             | Conditions                                    |

| High Vo       | ltage Entr         | y Programming Mode Specifications                      |               |              |                   | /                 | $\frown$                                      |

| MEM01         | V <sub>IHH</sub>   | Voltage on MCLR/VPP pin to enter pro-<br>gramming mode | 8             | —            | 9                 |                   | (Note 2 Note 3)                               |

| MEM02         | I <sub>PPGM</sub>  | Current on MCLR/VPP pin during pro-<br>gramming mode   | —             | 1            | —                 | mA                | (Note 2)                                      |

| Program       | nming Mo           | de Specifications                                      |               |              |                   |                   | $\sim$                                        |

| MEM10         | $V_{BE}$           | VDD for Bulk Erase                                     | —             | 2.7          | $7 \neq 7$        | ∖-y `             |                                               |

| MEM11         | I <sub>DDPGM</sub> | Supply Current during Programming operation            | _             | -            | 10                | /mA               |                                               |

| Data EE       | PROM Me            | mory Specifications                                    |               |              |                   | $\langle \rangle$ |                                               |

| MEM20         | ED                 | DataEE Byte Endurance                                  | 100k          | $\sim$       | $\langle \rangle$ | ₩.W               | $-40^\circ C \leq T A \leq +85^\circ C$       |

| MEM21         | TD-RET             | Characteristic Retention                               |               | 40           |                   | Year              | Provided no other specifications are violated |

| MEM22         | ND_REF             | Total Erase/Write Cycles before<br>Refresh             |               |              | 700k              | E/W               |                                               |

| MEM23         | VD_RW              | Vdd for Read or Erase/Write operation                  | VORMIN        | $\sim$       | VDDMAX            | V                 |                                               |

| MEM24         | TD_BEW             | Byte Erase and Write Cycle Time                        |               | 4.0          | 5.0               | ms                |                                               |

| Program       | n Flash M          | emory Specifications                                   | $\mathcal{I}$ | $\checkmark$ |                   |                   |                                               |

| MEM30         | E <sub>P</sub>     | Flash Memory Cell Endurance                            | hak /         | —            | —                 | E/W               | -40°C ≤ TA ≤ +85°C<br>(Note 1)                |

| MEM32         | T <sub>P_RET</sub> | Characteristic Retention                               | $\geq$        | 40           | _                 | Year              | Provided no other specifications are violated |

| MEM33         | $V_{P_{RD}}$       | VDD for Read operation                                 | VDDMIN        | —            | VDDMAX            | V                 |                                               |

| MEM34         | $V_{P_{REW}}$      | VDD for Row Erase or Write operation                   | VDDMIN        | —            | VDDMAX            | V                 |                                               |

| MEM35         | T <sub>P_REW</sub> | Self-Timed Row Erase of Self-Timed                     | —             | 2.0          | 2.5               | ms                |                                               |

Data in "Typ" column is at 3.0/, 28°C unless otherwise stated. These parameters are for design guidance only and are † not tested.

Note 1: Flash/Memory Cell Endurance for the Flash memory is defined as: One Row Erase operation and one Self-Timed Write.

Required only if CONFIG4, bit LVP is disabled. 2:

The MPLAB® TCD2 does not support variable VPP output. Circuitry to limit the ICD2 VPP voltage must be placed 3: between the CD2 and target system when programming or debugging with the ICD2.

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |          |      |  |  |  |

|------------------------|-------------|-----------|----------|------|--|--|--|

| Dimension              | MIN         | NOM       | MAX      |      |  |  |  |

| Number of Pins         | N           |           | 40       |      |  |  |  |

| Pitch                  | е           |           | 0.40 BSC |      |  |  |  |

| Overall Height         | Α           | 0.45      | 0.50     | 0.55 |  |  |  |

| Standoff               | A1          | 0.00      | 0.02     | 0.05 |  |  |  |

| Contact Thickness      | A3          | 0.127 REF |          |      |  |  |  |

| Overall Width          | E           | 5.00 BSC  |          |      |  |  |  |

| Exposed Pad Width      | E2          | 3.60      | 3.70     | 3.80 |  |  |  |

| Overall Length         | D           | 5.00 BSC  |          |      |  |  |  |

| Exposed Pad Length     | D2          | 3.60      | 3.70     | 3.80 |  |  |  |

| Contact Width          | b           | 0.15      | 0.20     | 0.25 |  |  |  |

| Contact Length         | L           | 0.30      | 0.40     | 0.50 |  |  |  |

| Contact-to-Exposed Pad | K           | 0.20      | -        | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2