Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 43                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19185-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name     | Bit 7         | Bit 6         | Bit 5 | Bit 4          | Bit 3                | Bit 2      | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|---------------|---------------|-------|----------------|----------------------|------------|-----------|-----------|-----------------------|----------------------------|

| Bank 20 |          |               |               |       |                |                      |            |           |           |                       |                            |

|         |          |               |               | CPU   | CORE REGISTERS | 6; see Table 4-3 for | rspecifics |           |           |                       |                            |

| A0Ch    | _        |               |               |       | Unimple        | mented               |            |           |           |                       |                            |

| A0Dh    | _        |               |               |       | Unimple        | mented               |            |           |           |                       |                            |

| A0Eh    | _        |               |               |       | Unimple        | mented               |            |           |           |                       |                            |

| A0Fh    | _        |               |               |       | Unimple        | mented               |            |           |           |                       |                            |

| A10h    | _        | Unimplemented |               |       |                |                      |            |           |           |                       |                            |

| A11h    | _        | Unimplemented |               |       |                |                      |            |           |           |                       |                            |

| A12h    | _        |               | Unimplemented |       |                |                      |            |           |           |                       |                            |

| A13h    | _        |               | Unimplemented |       |                |                      |            |           |           |                       |                            |

| A14h    | —        |               | Unimplemented |       |                |                      |            |           |           |                       |                            |

| A15h    | —        |               | Unimplemented |       |                |                      |            |           |           |                       |                            |

| A16h    | —        |               | Unimplemented |       |                |                      |            |           |           |                       |                            |

| A17h    | —        | Unimplemented |               |       |                |                      |            |           |           |                       |                            |

| A18h    | —        |               |               |       | Unimple        | mented               |            |           |           |                       |                            |

| A19h    | RC2REG   | RC2REG        |               |       |                |                      |            |           | 0000 0000 | 0000 0000             |                            |

| A1Ah    | TX2REG   | TX2REG        |               |       |                |                      |            | 0000 0000 | 0000 000  |                       |                            |

| A1Bh    | SP2BRGL  | SP2BRGL       |               |       |                |                      |            |           | 0000 0000 | 0000 0000             |                            |

| A1Ch    | SP2BRGH  |               |               |       | SP2B           | RGH                  |            |           |           | 0000 0000             | 0000 000                   |

| A1Dh    | RC2STA   | SPEN          | RX9           | SREN  | CREN           | ADDEN                | FERR       | OERR      | RX9D      | 0000 0000             | 0000 000                   |

| A1Eh    | TX2STA   | CSRC          | TX9           | TXEN  | SYNC           | SENDB                | BRGH       | TRMT      | TX9D      | 0000 0010             | 0000 001                   |

| A1Fh    | BAUD2CON | ABDOVF        | RCIDL         | _     | SCKP           | BRG16                | _          | WUE       | ABDEN     | 01-0 0-00             | 01-0 0-0                   |

PIC16(L)F19155/56/75/76/85/86

# TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

### 8.2 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 8.3 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

#### TABLE 8-1: BOR OPERATING MODES

#### 8.3.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 8.3.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | х      | Х           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |

| 1.0        |        | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |

| 10         | X      | Sleep       | Disabled | Waits for BOR Reset release                                         |

| 0.1        | 1      | х           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |

| 01         | 0      | х           | Disabled | Paging immediately (POPDDY =)                                       |

| 00         | Х      | х           | Disabled | Begins immediately (BORRDY = $x$ )                                  |

**Note 1:** In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O

- pinsCurrent draw from pins with internal weak

- pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Any module with a clock source that is not Fosc can be enabled. Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module", Section 18.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 11.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.14 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WWDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

# 12.1 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC, or 31.25 kHz MFINTOSC internal oscillators or 32.768 kHz SOSC, depending on the value of either the WDTCCS<2:0> Configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 39.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

# 12.2 WWDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 12-1.

#### 12.2.1 WWDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WWDT is always on.

WWDT protection is active during Sleep.

#### 12.2.2 WWDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WWDT is on, except in Sleep.

WWDT protection is not active during Sleep.

#### 12.2.3 WWDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WWDT is controlled by the SWDTEN bit of the WDTCON0 register.

#### 12.2.4 WWDT IS OFF

When the WDTE bits of the Configuration Word are set to '00', the WWDT is always OFF.

WWDT protection is unchanged by Sleep. See Table 12-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WWDT<br>Mode |

|-----------|--------|----------------|--------------|

| 11        | Х      | Х              | Active       |

| 10        |        | Awake          | Active       |

| 10        | х      | Sleep          | Disabled     |

| 0.1       | 1      | Х              | Active       |

| 01        | 0      | Х              | Disabled     |

| 00        | х      | Х              | Disabled     |

| <b>TABLE 12-1:</b> | WWDT OPERATING MODES |

|--------------------|----------------------|

|--------------------|----------------------|

# 12.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 12.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WWDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 12-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

# 12.5 Clearing the WWDT

The WWDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- WWDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

#### 12.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 12-2 for more information.

# 14.11 Register Definitions: PORTE

| R/W-x/u                                                                                                              | R/W-x/u                           | R/W-x/u           | R/W-x/u | R/W-x/u                            | U-0            | R/W-x/u          | R/W-x/u     |  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|---------|------------------------------------|----------------|------------------|-------------|--|

| RE7                                                                                                                  | RE6                               | RE5               | RE4     | RE3                                | —              | RE1              | RE0         |  |

| bit 7                                                                                                                | -                                 |                   |         |                                    |                |                  | bit 0       |  |

|                                                                                                                      |                                   |                   |         |                                    |                |                  |             |  |

| Legend:                                                                                                              |                                   |                   |         |                                    |                |                  |             |  |

| R = Readable                                                                                                         | R = Readable bit W = Writable bit |                   | bit     | U = Unimplemented bit, read as '0' |                |                  |             |  |

| u = Bit is unch                                                                                                      | anged                             | x = Bit is unkr   | nown    | -n/n = Value a                     | at POR and BOF | R/Value at all o | ther Resets |  |

| '1' = Bit is set                                                                                                     |                                   | '0' = Bit is clea | ared    |                                    |                |                  |             |  |

|                                                                                                                      |                                   |                   |         |                                    |                |                  |             |  |

| bit 7-3 <b>RE&lt;7:3&gt;</b> : PORTE I/O Value bits <sup>(1)</sup><br>1 = Port pin is ≥ VIH<br>0 = Port pin is ≤ VIL |                                   |                   |         |                                    |                |                  |             |  |

#### REGISTER 14-33: PORTE: PORTE REGISTER

#### bit 2 Unimplemented: Read as '0' bit 1-0 RE<1:0>: PORTE I/O Value bits<sup>(1)</sup>

- $1 = Port pin is \geq VIH$

- 0 = Port pin is <u><</u> VIL

- **Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

# REGISTER 14-34: TRISE: PORTE TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|---------|-----|---------|---------|

| TRISE7  | TRISE6  | TRISE5  | TRISE4  | TRISE3  | —   | TRISE1  | TRISE0  |

| bit 7   |         |         |         |         |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | <b>TRISE&lt;7:3&gt;:</b> PORTE Tri-State Control bit<br>1 = PORTE pin configured as an input (tri-stated)<br>0 = PORTE pin configured as an output |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | Unimplemented: Read as '0'                                                                                                                         |

| bit 1-0 | <b>TRISE&lt;1:0&gt;:</b> PORTE Tri-State Control bit<br>1 = PORTE pin configured as an input (tri-stated)                                          |

0 = PORTE pin configured as an output

| U-0                                                                       | U-0          | U-0                               | R/W-0/0 | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|---------------------------------------------------------------------------|--------------|-----------------------------------|---------|----------------|------------------|------------------|--------------|

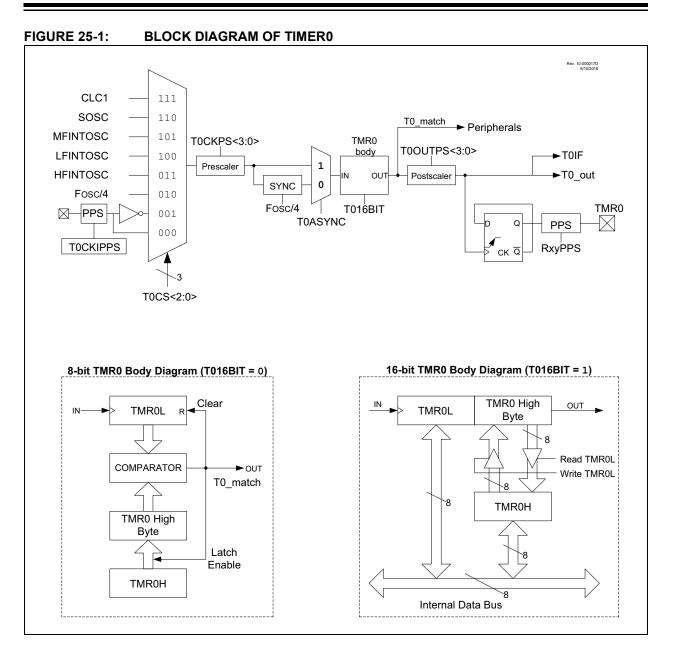

| _                                                                         | —            | —                                 | TMR4MD  | —              | TMR2MD           | TMR1MD           | TMR0MD       |

| bit 7                                                                     |              |                                   |         |                |                  |                  | bit 0        |

|                                                                           |              |                                   |         |                |                  |                  |              |

| Legend:                                                                   |              |                                   |         |                |                  |                  |              |

| R = Readab                                                                | ole bit      | W = Writable                      | bit     | U = Unimplem   | nented bit, read | as '0'           |              |

| u = Bit is un                                                             | ichanged     | x = Bit is unkr                   | nown    | -n/n = Value a | t POR and BO     | R/Value at all c | other Resets |

| '1' = Bit is s                                                            | et           | '0' = Bit is clea                 | ared    | q = Value dep  | ends on condit   | ion              |              |

|                                                                           |              |                                   |         |                |                  |                  |              |

| bit 7-5                                                                   | Unimpleme    | nted: Read as '                   | כ'      |                |                  |                  |              |

| bit 4                                                                     | TMR4MD: D    | isable Timer TM                   | IR4 bit |                |                  |                  |              |

|                                                                           |              | module disabled                   |         |                |                  |                  |              |

|                                                                           |              | module enabled                    |         |                |                  |                  |              |

| bit 3                                                                     | Unimpleme    | nted: Read as '                   | כ'      |                |                  |                  |              |

| bit 2                                                                     |              | isable Timer TM                   |         |                |                  |                  |              |

|                                                                           |              | module disabled<br>module enabled |         |                |                  |                  |              |

| L:1 4                                                                     |              |                                   |         |                |                  |                  |              |

| bit 1 <b>TMR1MD:</b> Disable Timer TMR1 bit<br>1 = Timer1 module disabled |              |                                   |         |                |                  |                  |              |

|                                                                           |              | module enabled                    |         |                |                  |                  |              |

| bit 0                                                                     | TMR0MD: D    | isable Timer TM                   | IR0 bit |                |                  |                  |              |

|                                                                           | 1 = Timer0 ı | module disabled                   | l       |                |                  |                  |              |

|                                                                           | 0 = Timer0 I | module enabled                    |         |                |                  |                  |              |

# REGISTER 16-2: PMD1: PMD CONTROL REGISTER 1

# 19.4 Capacitive Voltage Divider (CVD) Features

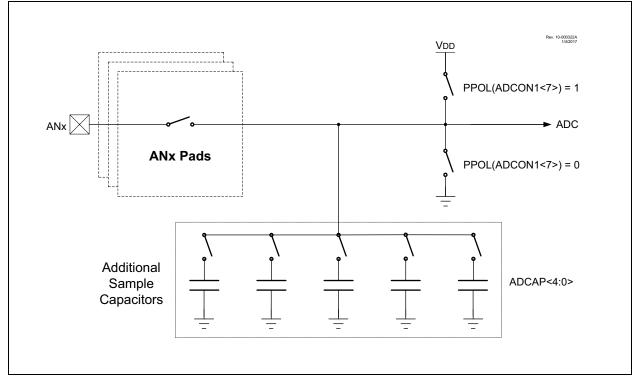

The ADC module contains several features that allow the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications. Figure 19-6 shows the basic block diagram of the CVD portion of the ADC module.

#### FIGURE 19-6: HARDWARE CAPACITIVE VOLTAGE DIVIDER BLOCK DIAGRAM

#### 19.5.1 DIGITAL FILTER/AVERAGE

The digital filter/average module consists of an accumulator with data feedback options, and control logic to determine when threshold tests need to be applied. The accumulator is a 24-bit wide register with sign extension which can be accessed through the ADACCU:H:L register triple.

Upon each trigger event (the GO bit set or external event trigger), the ADC conversion result is added to the accumulator. If the accumulated result exceeds  $2^{(accumulator_width)}-1 = 18 = 262143$ , the overflow bit OV in the ADSTAT register is set.

The number of samples to be accumulated is determined by the RPT (A/D Repeat Setting) register. Each time a sample is added to the accumulator, the ADCNT register is incremented. Once RPT samples are accumulated (CNT = RPT), an accumulator clear command can be issued by the software by setting the ADACLR bit in the ADCON2 register. Setting the ADACLR bit will also clear the OV (Accumulator overflow) bit in the ADSTAT register, as well as the

ADCNT register. The ADACLR bit is cleared by the hardware when accumulator clearing action is complete.

# Note: When ADC is operating from FRC, five FRC clock cycles are required to execute the ACC clearing operation.

The ADCRS <2:0> bits in the ADCON2 register control the data shift on the accumulator result, which effectively divides the value in accumulator (ADACCU:ADACCH:ADACCL) register triple For the Accumulate mode of the digital filter, the shift provides a simple scaling operation. For the Average/Burst Average modes, the shift bits are used to determine the number of arithmetic right shifts to be performed on the accumulated result. For the Low-Pass Filter mode, the shift is an integral part of the filter, and determines the cut-off frequency of the filter. Table 19-3 shows the -3 dB cut-off frequency in  $\omega$ T (radians) and the highest signal attenuation obtained by this filter at nyquist frequency ( $\omega$ T =  $\pi$ ).

| TADIE 40.2. | LOW DASS EILTED |                         |

|-------------|-----------------|-------------------------|

| IADLE 19-3. | LUW-PASS FILLER | -3 dB CUT-OFF FREQUENCY |

| ADCRS | ωT (radians) @ -3 dB Frequency | dB @ F <sub>nyquist</sub> =1/(2T) |

|-------|--------------------------------|-----------------------------------|

| 1     | 0.72                           | -9.5                              |

| 2     | 0.284                          | -16.9                             |

| 3     | 0.134                          | -23.5                             |

| 4     | 0.065                          | -29.8                             |

| 5     | 0.032                          | -36.0                             |

| 6     | 0.016                          | -42.0                             |

| 7     | 0.0078                         | -48.1                             |

# 19.5.2 BASIC MODE

Basic mode (ADMD = 000) disables all additional computation features. In this mode, no accumulation occurs but threshold error comparison is performed. Double sampling, Continuous mode, and all CVD features are still available, but no features involving the digital filter/average features are used.

#### 19.5.3 ACCUMULATE MODE

In Accumulate mode (ADMD = 001), after every conversion, the ADC result is added to the ADACC register. The ADACC register is right-shifted by the value of the ADCRS bits in the ADCON2 register. This right-shifted value is copied in to the ADFLT register. The Formatting mode does not affect the right-justification of the ACC value. Upon each sample, CNT is also incremented, incrementing the number of samples accumulated. After each sample and accumulation, the ACC value has a threshold comparison performed on it (see **Section 19.5.7 "Threshold Comparison**") and the ADTIF interrupt may trigger.

#### 19.5.4 AVERAGE MODE

In Average mode (ADMD = 010), the ADACC registers accumulate with each ADC sample, much as in Accumulate mode, and the ADCNT register increments with each sample. The ADFLT register is also updated with the right-shifted value of the ADACC register. The value of the ADCRS bits governs the number of right shifts. However, in Average mode, the threshold comparison is performed upon CNT being greater than or equal to a user-defined RPT value. In this mode when RPT =  $2^A$ ADCRS-the shift distance, then the final accumulated value will be divided by number of samples, allowing for a threshold comparison operation on the average of all gathered samples.

### 19.5.5 BURST AVERAGE MODE

The Burst Average mode (ADMD = 011) acts the same as the Average mode in most respects. The one way it differs is that it continuously retriggers ADC sampling until the CNT value is greater than or equal to RPT, even if Continuous Sampling mode (see **Section 19.5.8 "Continuous Sampling mode"**) is not enabled. This allows for a threshold comparison on the average of a short burst of ADC samples.

# 19.5.6 LOW-PASS FILTER MODE

The Low-Pass Filter mode (ADMD = 100) acts similarly to the Average mode in how it handles samples (accumulates samples until CNT value is greater than or equal to RPT, then triggers threshold comparison. CNT does not reset once it is greater or equal to RPT. Thus CNT will be greater than RPT for all subsequent samples until CNT is reset by the user), but instead of a simple average, it performs a low-pass filter operation on all of the samples, reducing the effect of high-frequency noise on the average, then performs a threshold comparison on the results. (see Table 19-2 for a more detailed description of the mathematical operation). In this mode, the ADCRS bits determine the cut-off frequency of the low-pass filter (as demonstrated by Table 19-3).

#### 19.5.7 THRESHOLD COMPARISON

At the end of each computation:

- The conversion results are latched and held stable at the end-of-conversion.

- The error is calculated based on a difference calculation which is selected by the ADCALC<2:0> bits in the ADCON3 register. The value can be one of the following calculations (see Register 19-4 for more details):

- The first derivative of single measurements

- The CVD result in CVD mode

- The current result vs. a setpoint

- The current result vs. the filtered/average result

- The first derivative of the filtered/average value

- Filtered/average value vs. a setpoint

- The result of the calculation (ERR) is compared to the upper and lower thresholds, UTH<ADUTHH:ADUTHL> and

LTH<ADLTHH:ADLTHL> registers, to set the ADUTHR and ADLTHR flag bits. The threshold logic is selected by ADTMD<2:0> bits in the ADCON3 register. The threshold trigger option can be one of the following:

- Never interrupt

- Error is less than lower threshold

- Error is greater than or equal to lower threshold

- Error is between thresholds (inclusive)

- Error is outside of thresholds

- Error is less than or equal to upper threshold

- Error is greater than upper threshold

- Always interrupt regardless of threshold test results

- If the threshold condition is met, the threshold interrupt flag ADTIF is set.

Note 1: The threshold tests are signed operations.

**2:** If OV is set, a threshold interrupt is signaled.

#### REGISTER 19-24: ADACCU: ADC ACCUMULATOR REGISTER UPPER

| U-0                               | U-0 | U-0 | U-0          | U-0              | U-0      | R/W-x/x | R/W-x/x |

|-----------------------------------|-----|-----|--------------|------------------|----------|---------|---------|

| —                                 | —   | —   | —            | —                | —        | ACC<    | 17:16>  |

| bit 7                             |     |     | •            |                  |          |         | bit 0   |

|                                   |     |     |              |                  |          |         |         |

| Legend:                           |     |     |              |                  |          |         |         |

| R = Readable bit W = Writable bit |     |     | U = Unimpler | nented bit, read | l as '0' |         |         |

| R – Reauable bil     |                      | 0 – Onimplemented bit, read as 0                      |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ACC<17:16>: ADC Accumulator MSB. Upper two bits of accumulator value. See Table 19-2 for more details.

#### REGISTER 19-25: ADACCH: ADC ACCUMULATOR REGISTER HIGH

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ACC<    | 15:8>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: ADC Accumulator middle bits. Middle eight bits of accumulator value. See Table 19-2 for more details.

#### REGISTER 19-26: ADACCL: ADC ACCUMULATOR REGISTER LOW

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ACC<    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Logond  |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 ACC<7:0>: ADC Accumulator LSB. Lower eight bits of accumulator value. See Table 19-2 for more details.

© 2017 Microchip Technology Inc.

# PIC16(L)F19155/56/75/76/85/86

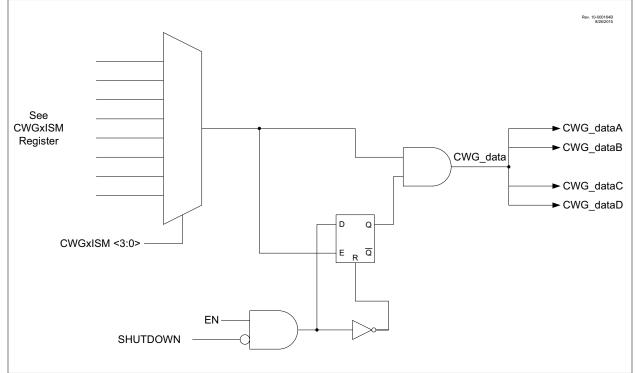

#### 31.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 31.9 "CWG Steering Mode"**.

# 31.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWG1CLKCON register.

| U-0              | U-0                                | U-0               | U-0  | R-0                                                   | R-0              | R-0     | R-0     |  |

|------------------|------------------------------------|-------------------|------|-------------------------------------------------------|------------------|---------|---------|--|

| —                | —                                  | —                 |      | MLC4OUT                                               | MLC3OUT          | MLC2OUT | MLC1OUT |  |

| bit 7            |                                    |                   |      |                                                       |                  |         | bit 0   |  |

|                  |                                    |                   |      |                                                       |                  |         |         |  |

| Legend:          |                                    |                   |      |                                                       |                  |         |         |  |

| R = Readable     | bit                                | W = Writable I    | bit  | U = Unimpler                                          | nented bit, read | as '0'  |         |  |

| u = Bit is uncha | anged                              | x = Bit is unkn   | iown | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |

| '1' = Bit is set |                                    | '0' = Bit is clea | ared |                                                       |                  |         |         |  |

|                  |                                    |                   |      |                                                       |                  |         |         |  |

| bit 7-4          | Unimplemen                         | ted: Read as '    | )'   |                                                       |                  |         |         |  |

| bit 3            | MLC4OUT: Mirror copy of LC4OUT bit |                   |      |                                                       |                  |         |         |  |

| bit 2            | MLC3OUT: Mirror copy of LC3OUT bit |                   |      |                                                       |                  |         |         |  |

| bit 1            | MLC2OUT: Mirror copy of LC2OUT bit |                   |      |                                                       |                  |         |         |  |

| bit 0            | MLC10UT: Mirror copy of LC10UT bit |                   |      |                                                       |                  |         |         |  |

# REGISTER 32-11: CLCDATA: CLC DATA OUTPUT

| Name      | Bit 7    | Bit 6    | Bit 5    | Bit 4          | Bit 3          | Bit 2        | Bit 1    | Bit 0    |     |

|-----------|----------|----------|----------|----------------|----------------|--------------|----------|----------|-----|

| CLC4GLS1  | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N       | LC4G2D2T       | LC4G2D2N     | LC4G2D1T | LC4G2D1N | 506 |

| CLC4GLS2  | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N       | LC4G3D2T       | LC4G3D2N     | LC4G3D1T | LC4G3D1N | 507 |

| CLC4GLS3  | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N       | LC4G4D2T       | LC4G4D2N     | LC4G4D1T | LC4G4D1N | 508 |

| CLCIN0PPS | —        | -        | _        |                | CLCIN0PPS<4:0> |              |          | 264      |     |

| CLCIN1PPS | -        | _        | _        |                | CLCIN1PPS<4:0> |              |          |          | 264 |

| CLCIN2PPS | _        | _        | _        | CLCIN2PPS<4:0> |                |              | 264      |          |     |

| CLCIN3PPS | _        | _        | _        |                | (              | CLCIN3PPS<4: | 0>       |          | 264 |

# TABLE 32-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued)

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

#### **Register Definitions: MSSPx Control** 33.8

# REGISTER 33-1: SSPxSTAT: SSPx STATUS REGISTER

| REGISTI<br>R/W-0 |                                                                                                          | R/HS/HC-0                                                                                                                                                                                                                                                                                           | R/HS/HC-0                                                  | R/HS/HC-0                      | R/HS/HC-0                                | R/HS/HC-0           | R/HS/HC-0         |

|------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------|---------------------|-------------------|

| SMP              | (4)                                                                                                      | D/A                                                                                                                                                                                                                                                                                                 | P <sup>(2)</sup>                                           | S <sup>(2)</sup>               | R/W                                      | UA                  | BF                |

| bit 7            |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            | _                              |                                          |                     | bit 0             |

|                  |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            |                                |                                          |                     |                   |

| Legend:          |                                                                                                          |                                                                                                                                                                                                                                                                                                     |                                                            |                                |                                          |                     |                   |

| R = Reada        | ble bit                                                                                                  | W = Writable bit                                                                                                                                                                                                                                                                                    |                                                            | U = Unimpleme                  | nted bit, read as '0                     | 2                   |                   |

| u = Bit is u     | nchanged                                                                                                 | x = Bit is unknow                                                                                                                                                                                                                                                                                   | vn                                                         | -n/n = Value at                | POR and BOR/Val                          | ue at all other Res | sets              |

| '1' = Bit is s   | set                                                                                                      | '0' = Bit is cleare                                                                                                                                                                                                                                                                                 | ed                                                         | HS/HC = Hardv                  | vare set/clear                           |                     |                   |

| bit 7            | SPI Master mod                                                                                           | Input Sample bit<br><u>te:</u><br>ampled at end of o                                                                                                                                                                                                                                                | data output time                                           |                                |                                          |                     |                   |

|                  | SPI Slave mode<br>SMP must be c<br>In I <sup>2</sup> C Master of<br>1 = Slew rate c                      | control disabled for                                                                                                                                                                                                                                                                                | s used in Slave r<br>Standard Speed                        | node<br>d mode (100 kHz        | and 1 MHz)                               |                     |                   |

| bit 6            |                                                                                                          | control enabled for<br>Edge Select bit (                                                                                                                                                                                                                                                            | •                                                          | . , ,                          |                                          |                     |                   |

| bit o            | In SPI Master o<br>1 = Transmit oc<br>0 = Transmit oc<br>In I <sup>2</sup> C mode onl<br>1 = Enable inpu | r Slave mode:<br>curs on transition<br>curs on transition                                                                                                                                                                                                                                           | from active to Id<br>from Idle to activ<br>sholds are comp | e clock state<br>e clock state | specification                            |                     |                   |

| bit 5            | 1 = Indicates th                                                                                         | D/A: Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                                                     |                                                            |                                |                                          |                     |                   |

| bit 4            | 1 = Indicates th                                                                                         | <ul> <li>P: Stop bit<sup>(2)</sup></li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Stop bit was not detected last</li> </ul>     |                                                            |                                |                                          |                     |                   |

| bit 3            | 1 = Indicates th                                                                                         | <ul> <li>S: Start bit <sup>(2)</sup></li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)</li> <li>0 = Start bit was not detected last</li> </ul> |                                                            |                                |                                          |                     |                   |

| bit 2            | This bit holds th<br>next Start bit, Sl<br>In I <sup>2</sup> C Slave mo<br>1 = Read<br>0 = Write         | top bit, or not ACK<br>i <u>de:</u>                                                                                                                                                                                                                                                                 | ion following the                                          | last address mat               | ch. This bit is only v                   | valid from the add  | ress match to the |

|                  | 0 = Transmit is                                                                                          | s in progress<br>s not in progress                                                                                                                                                                                                                                                                  | SEN, PEN, RCE                                              | N or ACKEN will i              | ndicate if the MSS                       | P is in IDLE mode   |                   |

| bit 1            | 1 = Indicates th                                                                                         | dress bit (10-bit I <sup>2</sup><br>at the user needs<br>es not need to be                                                                                                                                                                                                                          | to update the ad                                           | dress in the SSP               | kADD register                            |                     |                   |

| bit 0            | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C m</u><br>1 = Data transm                                  | nd I <sup>2</sup> C modes):<br>mplete, SSPxBUF<br>t complete, SSPxE<br>lode only):<br>nit in progress (doe                                                                                                                                                                                          | UF is empty<br>es not include the                          |                                | its), SSPxBUF is fi<br>s), SSPxBUF is em |                     |                   |

| Note 1:<br>2:    | Polarity of clock state<br>This bit is cleared on                                                        | •                                                                                                                                                                                                                                                                                                   |                                                            | •                              |                                          |                     |                   |

# PIC16(L)F19155/56/75/76/85/86

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                                                                                                                                       |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

#### **TABLE 39-6**: **THERMAL CHARACTERISTICS**

|               |           | Conditions (unless otherwise stated) ure -40°C $\leq$ TA $\leq$ +125°C |                                 |                  | $\land$                                                  |  |  |

|---------------|-----------|------------------------------------------------------------------------|---------------------------------|------------------|----------------------------------------------------------|--|--|

| Param.<br>No. | Sym.      | Characteristic                                                         | Тур.                            | Units            | Conditions                                               |  |  |

| TH01          | θја       | Thermal Resistance Junction to Ambient                                 | 60                              | °C/W             | 28-pin SPDIP package                                     |  |  |

|               |           |                                                                        | 80                              | °C/W             | 28-pin SOIC package                                      |  |  |

|               |           |                                                                        | 90                              | °C/W             | 28-pin SSOP package                                      |  |  |

|               |           |                                                                        | 48                              | °C/W             | 28-pin UQFN 4x4 mm package                               |  |  |

|               |           |                                                                        | 47.2                            | °C/W             | 40-pin PDIP package                                      |  |  |

|               |           |                                                                        | 41.0                            | °C/W             | 40-pin UQFN 5x5 package                                  |  |  |

|               |           |                                                                        | 46.0                            | °C/W             | 44-pin TQFP package                                      |  |  |

|               |           |                                                                        | 24.4                            | °C/W 〈           | 44-pin QFN 8x8 mm package                                |  |  |

|               |           |                                                                        | 27.6                            | °C/W             | 48-pin DQFN 6x6 package                                  |  |  |

|               |           |                                                                        | _                               | °C/W             | 48-pin/TQFP 7x7 package                                  |  |  |

| TH02          | θις       | Thermal Resistance Junction to Case                                    | 31.4                            | ∕°C⁄₩            | 28-pin SPDIP package                                     |  |  |

|               |           |                                                                        | 24                              | °€∕W∕            | 28-pin SOIC package                                      |  |  |

|               |           |                                                                        | 24 /~                           | °C/W             | 28-pin SSOP package                                      |  |  |

|               |           |                                                                        | 12                              | <u>°C/W</u>      | 28-pin UQFN 4x4 mm package                               |  |  |

|               |           |                                                                        | 24,70                           | ~°C∕W            | 40-pin PDIP package                                      |  |  |

|               |           |                                                                        | 5.5                             | ~C/W             | 40-pin UQFN 5x5 package                                  |  |  |

|               |           |                                                                        | 14.5                            | _°C/₩∕           | 44-pin TQFP package                                      |  |  |

|               |           |                                                                        | 20.0                            | w/کور            | 44-pin QFN 8x8 mm package                                |  |  |

|               |           | $\sim$                                                                 | 6.7                             | <sup>∼</sup> C/W | 48-pin UQFN 6x6 package                                  |  |  |

|               |           |                                                                        | $\overline{\langle /  \rangle}$ | °C/W             | 48-pin TQFP 7x7 package                                  |  |  |

| TH03          | TJMAX     | Maximum Junction Temperature                                           | 150                             | °C               |                                                          |  |  |

| TH04          | PD        | Power Dissipation                                                      | $\searrow$                      | W                | PD = PINTERNAL + PI/O                                    |  |  |

| TH05          | PINTERNAL | Internal Power Dissipation                                             | $\rangle -$                     | W                | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06          | Pı/o      | I/O Power Dissipation                                                  | × _                             | W                | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07          | Pder      | Derated Power                                                          | _                               | W                | Pder = PDmax (Τj - Τα)/θja <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

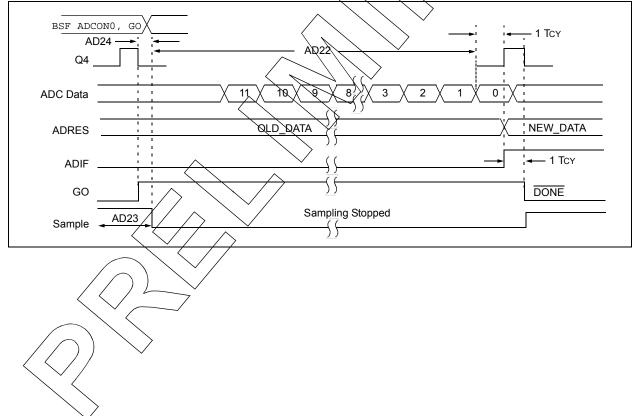

#### TABLE 39-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |       |                                              |      |                |      |       |                                                           |

|---------------------------------------------------------|-------|----------------------------------------------|------|----------------|------|-------|-----------------------------------------------------------|

| Param.<br>No.                                           | Sym.  | Characteristic                               | Min. | Тур†           | Max. | Units | Conditions                                                |

| AD20                                                    | - Tad | ADC Clock Period                             | 1    | _              | 9    | μS    | Using Fosc as the ADC clock<br>source ADCS = 1            |

| AD21                                                    |       |                                              |      | 2              |      | μS    | Using FRC as the ADC clock<br>source ADS <del>C =</del> 0 |

| AD22 T                                                  | TCNV  | Conversion Time                              | _    | 14 TAD + 2 TCY | _    | —     | Using Fosc as the ADC clock<br>source ADCS = 1            |

|                                                         | ICINV |                                              |      | 16 TAD + 2 TCY |      | —     | Using FRC as the ADC clock<br>source ADSC = 0             |

| AD24                                                    | THCD  | Sample and Hold Capacitor<br>Disconnect Time | _    | 2 TAD + 1 TCY  | _    |       | Using Fosc as the ADC clock<br>source ADCS = 1            |

|                                                         |       |                                              |      | 3 TAD + 2 TCY  |      | £     | Using Frc as the ADC clock<br>source ADSC = 0             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: A TAD of 8  $\mu$ s is recommended measuring the 1/3 tap point on the VBAT.

# FIGURE 39-10: ADC CONVERSION TIMING (ADC CLOCK Fosc-BASED)

# PIC16(L)F19155/56/75/76/85/86

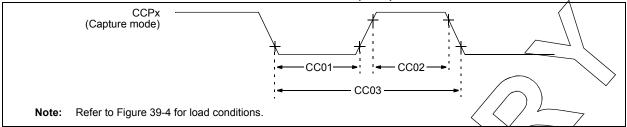

#### FIGURE 39-13: CAPTURE/COMPARE/PWM TIMINGS (CCP)

### TABLE 39-20: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)         Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |        |                     |       |                    |

|-------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|--------|---------------------|-------|--------------------|

| Param.<br>No.                                                                                                                 | Sym. | Characteristic       |                | Min.                  | Тур†   | Max.                | Units | Conditions         |

| CC01*                                                                                                                         | TccL | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —      | $\langle - \rangle$ | ns    | $\rangle$          |

|                                                                                                                               |      |                      | With Prescaler | 20                    | $\sim$ | A                   | ns    |                    |

| CC02*                                                                                                                         | TccH | CCPx Input High Time | No Prescaler   | 0.5Tcy + 20           | /-/    | 1                   | ns    |                    |

|                                                                                                                               |      |                      | With Prescaler | 20                    |        |                     | ns    |                    |

| CC03*                                                                                                                         | TccP | CCPx Input Period    |                | <u>3Tcy + 40</u><br>N |        | $\triangleright$    | ns    | N = prescale value |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

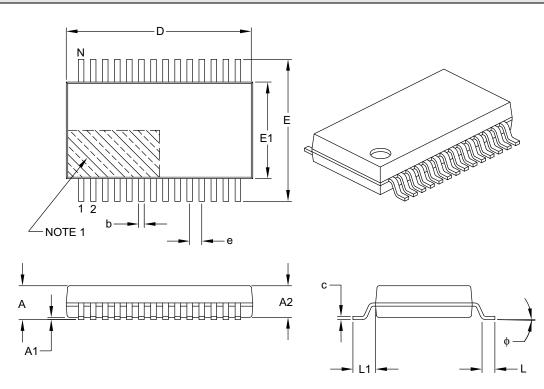

The following sections give the technical details of the packages.

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |       |       |  |  |  |

|--------------------------|------------------|----------|-------|-------|--|--|--|

|                          | Dimension Limits |          |       | MAX   |  |  |  |

| Number of Pins           | N                | 28       |       |       |  |  |  |

| Pitch                    | е                | 0.65 BSC |       |       |  |  |  |

| Overall Height           | А                | _        | -     | 2.00  |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75  | 1.85  |  |  |  |

| Standoff                 | A1               | 0.05     | -     | -     |  |  |  |

| Overall Width            | E                | 7.40     | 7.80  | 8.20  |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30  | 5.60  |  |  |  |

| Overall Length           | D                | 9.90     | 10.20 | 10.50 |  |  |  |

| Foot Length              | L                | 0.55     | 0.75  | 0.95  |  |  |  |

| Footprint                | L1               | 1.25 REF |       |       |  |  |  |

| Lead Thickness           | С                | 0.09     | -     | 0.25  |  |  |  |

| Foot Angle               | φ                | 0°       | 4°    | 8°    |  |  |  |

| Lead Width               | b                | 0.22     | -     | 0.38  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- 3. Dimensioning and tolerancing per ASME 114.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B