Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 43                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

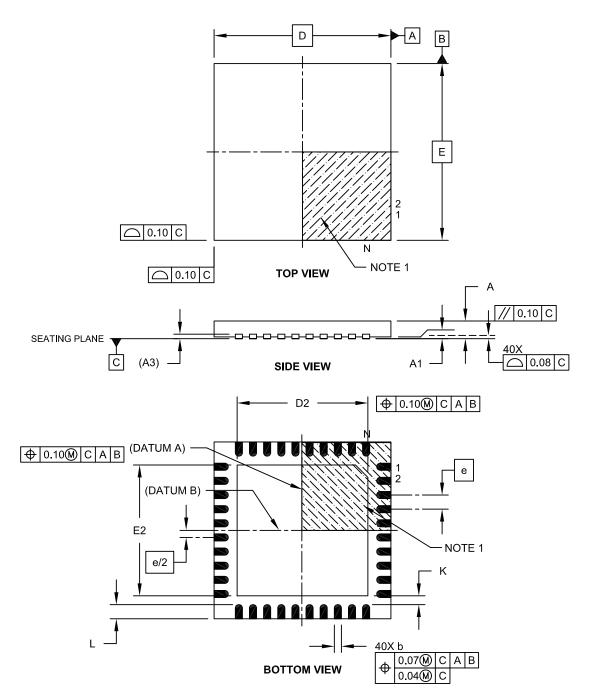

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19185t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

# 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack"** for more details.

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers, program memory, and data EEPROM, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6 "Indirect Addressing"** for more details.

# 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 37.0 "Instruction Set Summary"** for more details.

| Address | Name | Bit 7 | Bit 6                                   | Bit 5 | Bit 4         | Bit 3               | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |  |

|---------|------|-------|-----------------------------------------|-------|---------------|---------------------|-------------|-------|-------|-----------------------|----------------------------|--|

| Bank 10 |      |       |                                         |       |               |                     |             |       |       |                       |                            |  |

|         |      |       |                                         | CPU   | CORE REGISTER | S; see Table 4-3 fo | r specifics |       |       |                       |                            |  |

| 50Ch    | _    |       |                                         |       | Unimple       | mented              |             |       |       |                       |                            |  |

| 50Dh    |      |       | Unimplemented             Unimplemented |       |               |                     |             |       |       |                       |                            |  |

| 50Eh    | _    |       |                                         |       | Unimple       |                     |             |       |       |                       |                            |  |

| 50Fh    |      |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 510h    | _    |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 511h    | _    |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 512h    | _    |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 513h    | _    |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 514h    |      |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 515h    | _    |       | Unimplemented                           |       |               |                     |             |       |       |                       |                            |  |

| 516h    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 517h    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 518h    | —    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 519h    | —    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Ah    | —    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Bh    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Ch    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Dh    |      |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Eh    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

| 51Fh    | _    |       |                                         |       | Unimple       | emented             |             |       |       |                       |                            |  |

# TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Preliminary

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

# TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

| Address                                         | Name                                                                                                                                                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|

| Banks 30-57                                     |                                                                                                                                                         |       |       |       |       |       |       |       |       |                       |                            |

| CPU CORE REGISTERS; see Table 4-3 for specifics |                                                                                                                                                         |       |       |       |       |       |       |       |       |                       |                            |

| F0Ch<br>—<br>1C9Fh                              | — Unimplemented                                                                                                                                         |       |       |       |       |       |       |       |       |                       |                            |

| Legend:                                         | egend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. |       |       |       |       |       |       |       |       |                       |                            |

**Note 1:** Unimplemented data memory locations, read as '0'.

| VDD                                                                                                                                                                                                                                       | VBAT                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| >VBOR                                                                                                                                                                                                                                     | >VBOR                                                                                                                                                                                                   | <ul> <li>If VDD &gt; VBAT, then all active modules operate on VDD. If VBAT &gt; VDD, then<br/>RTCC and SOSC operate on Vbat and all other active modules operate on<br/>VDD.</li> <li>VBATBOR bit in PCON1 unchanged</li> <li>BOR bit in PCON0 unchanged</li> </ul> |

| >VBOR                                                                                                                                                                                                                                     | <vbor< td=""><td><ul> <li>All active modules operate on VDD</li> <li>VBATBOR bit in PCON1 unchanged</li> <li>BOR bit in PCON0 unchanged</li> </ul></td></vbor<>                                         | <ul> <li>All active modules operate on VDD</li> <li>VBATBOR bit in PCON1 unchanged</li> <li>BOR bit in PCON0 unchanged</li> </ul>                                                                                                                                   |

| <vbor< td=""><td>&gt;VBOR</td><td><ul> <li>The RTCC, SOSC operate on VBAT</li> <li>All other modules are held in Reset</li> <li>VBATBOR bit in PCON1 unchanged</li> <li>Clear BOR bit in PCON0 to indicate VDDBOR</li> </ul></td></vbor<> | >VBOR                                                                                                                                                                                                   | <ul> <li>The RTCC, SOSC operate on VBAT</li> <li>All other modules are held in Reset</li> <li>VBATBOR bit in PCON1 unchanged</li> <li>Clear BOR bit in PCON0 to indicate VDDBOR</li> </ul>                                                                          |

| <vbor< td=""><td><vbor< td=""><td><ul> <li>All modules are held in Reset.</li> <li>The VBATBOR bit in PCON1 cleared to indicate VBATBOR</li> <li>The BOR bit in PCON0 cleared to indicate VDDBOR</li> </ul></td></vbor<></td></vbor<>     | <vbor< td=""><td><ul> <li>All modules are held in Reset.</li> <li>The VBATBOR bit in PCON1 cleared to indicate VBATBOR</li> <li>The BOR bit in PCON0 cleared to indicate VDDBOR</li> </ul></td></vbor<> | <ul> <li>All modules are held in Reset.</li> <li>The VBATBOR bit in PCON1 cleared to indicate VBATBOR</li> <li>The BOR bit in PCON0 cleared to indicate VDDBOR</li> </ul>                                                                                           |

#### TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0   | Register<br>on Page |  |

|---------|--------|--------|-------|-------|-----------|-------|-------|---------|---------------------|--|

| BORCON  | SBOREN | —      | —     | _     | —         | _     | _     | BORRDY  | 135                 |  |

| PCON0   | STKOVF | STKUNF | WDTWV | RWDT  | RMCLR     | RI    | POR   | BOR     | 140                 |  |

| PCON1   | _      | _      | _     | _     | _         | _     | MEMV  | VBATBOR | 141                 |  |

| STATUS  | _      | _      | _     | TO    | PD        | Z     | DC    | С       | 50                  |  |

| WDTCON0 | _      | _      |       | V     | VDTPS<4:0 | >     |       | SWDTEN  | 196                 |  |

| VB0GPR  |        |        |       |       | VB0GPR    |       |       |         |                     |  |

| VB1GPR  |        | VB1GPR |       |       |           |       |       |         |                     |  |

| VP2GPR  |        | VP2GPR |       |       |           |       |       |         |                     |  |

| VP3GPR  |        |        |       |       | VP3GPR    |       |       |         |                     |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# PIC16(L)F19155/56/75/76/85/86

#### EXAMPLE 13-5: DEVICE ID ACCESS

| ; This write routine as       | ssumes the following:                                                 |

|-------------------------------|-----------------------------------------------------------------------|

| ; 1. A full row of data       | a are loaded, starting at the address in DATA_ADDR                    |

|                               | to be written is made up of two adjacent bytes in DATA_ADDR,          |

| ; stored in little endi       |                                                                       |

|                               | address (the least significant bits = 00000) is loaded in ADDRH:ADDRL |

| -                             | re located in common RAM (locations 0x70 - 0x7F)                      |

|                               | e not taken into account                                              |

| BANKSEL NVMADRH               |                                                                       |

| MOVF ADDRH,W                  |                                                                       |

| MOVWF NVMADRH                 | ; Load initial address                                                |

| MOVF ADDRL,W                  |                                                                       |

| MOVWF NVMADRL                 |                                                                       |

|                               | ; Load initial data address                                           |

| MOVWF FSR0L                   |                                                                       |

| MOVLW HIGH DATA ADDR          |                                                                       |

| MOVWF FSR0H                   |                                                                       |

| BCF NVMCON1,NVMREGS           | ; Set PFM as write location                                           |

| BSF NVMCON1,WREN              | ; Enable writes                                                       |

|                               | ; Load only write latches                                             |

| LOOP                          | / Hoad Only write fatches                                             |

| MOVIW FSR0++                  |                                                                       |

| MOVIW PSROTT<br>MOVWF NVMDATL | ; Load first data byte                                                |

| MOVIW FSR0++                  | / Hoad Tillst data byte                                               |

| MOVIW FSROTT<br>MOVWF NVMDATH | ; Load second data byte                                               |

| CALL UNLOCK_SEQ               |                                                                       |

| INCF NVMADRL, F               | ; Increment address                                                   |

|                               | , increment address                                                   |

| MOVF NVMADRL,W<br>XORLW 0x1F  | ; Check if lower bits of address are 00000                            |

|                               | ; and if on last of 32 addresses                                      |

| ANDLW 0x1F                    | ; Last of 32 words?                                                   |

|                               |                                                                       |

| GOTO START_WRITE              | ; If so, go write latches into memory                                 |

| GOTO LOOP                     |                                                                       |

| START_WRITE                   | · Tatahitaa annulata                                                  |

| BCF NVMCON1,LWLO              | ; Latch writes complete, now write memory                             |

| CALL UNLOCK_SEQ               | ; Perform required unlock sequence                                    |

| BCF NVMCON1,LWLO              | ; Disable writes                                                      |

| UNLOCK_SEQ                    |                                                                       |

| MOVLW 55h                     |                                                                       |

| BCF INTCON, GIE               | ; Disable interrupts                                                  |

| MOVWF NVMCON2                 | ; Begin unlock sequence                                               |

| MOVLW AAh                     |                                                                       |

| MOVWF NVMCON2                 |                                                                       |

| BSF NVMCON1,WR                |                                                                       |

| BSF INTCON,GIE                | ; Unlock sequence complete, re-enable interrupts                      |

|                               |                                                                       |

| U-0          | R/W-0/0                                        | R/W-0/0                                | R/W/HC-0/0        | R/W/HC-x/q               | R/W-0/0            | R/S/HC-0/0            | R/S/HC-0/0        |

|--------------|------------------------------------------------|----------------------------------------|-------------------|--------------------------|--------------------|-----------------------|-------------------|

| _            | NVMREGS                                        | LWLO                                   | FREE              | WRERR <sup>(1,2,3)</sup> | WREN               | WR <sup>(4,5,6)</sup> | RD                |

| oit 7        |                                                |                                        | 1                 |                          |                    |                       | bit               |

|              |                                                |                                        |                   |                          |                    |                       |                   |

| Legend:      |                                                |                                        |                   |                          |                    |                       |                   |

| R = Read     | able bit                                       | W = Writable b                         | it                | •                        | ented bit, read as |                       |                   |

| S = Bit ca   | n only be set                                  | x = Bit is unkno                       | own               | -n/n = Value at          | POR and BOR/       | /alue at all other    | Resets            |

| '1' = Bit is | set                                            | '0' = Bit is clea                      | red               | HC = Bit is clea         | ared by hardware   | 9                     |                   |

|              |                                                |                                        |                   |                          |                    |                       |                   |

| bit 7        | •                                              | ed: Read as '0'                        |                   |                          |                    |                       |                   |

| bit 6        |                                                | onfiguration Sele                      |                   | - Llear ID and D         | ovice ID Deciste   | <b>r</b> 0            |                   |

|              | 1 = Access E<br>0 = Access P                   |                                        | ci, coniguration  | n, User ID and De        | evice ID Registe   | 15                    |                   |

| bit 5        |                                                | Vrite Latches On                       | lv bit            |                          |                    |                       |                   |

|              | When FREE =                                    |                                        | <b>,</b>          |                          |                    |                       |                   |

|              |                                                |                                        |                   |                          | d within the row;  | no memory oper        | ation is initiate |

|              | 0 = The next<br>Otherwise: The                 | WR command w                           | rites data or era | ses                      |                    |                       |                   |

| bit 4        |                                                | rase Enable bit                        |                   |                          |                    |                       |                   |

| UIL 4        |                                                | GS:NVMADR pc                           | oints to a PFM lo | cation:                  |                    |                       |                   |

|              |                                                |                                        |                   |                          | the 32-word pse    | udo-row containi      | ng the indicate   |

|              |                                                | s erased (to all 1                     | <i>,</i>          | -                        |                    |                       |                   |

|              |                                                | operations have                        |                   | nally                    |                    |                       |                   |

| bit 3        |                                                | ram/Erase Error                        |                   |                          |                    |                       |                   |

|              |                                                | hally set by hard                      |                   | set interrupted u        | inlock sequence    | , or WR was writ      | ten to one whi    |

|              |                                                | points to a write                      |                   |                          |                    |                       |                   |

|              | 0 = The progr                                  | ram or erase ope                       | ration complete   | d normally               |                    |                       |                   |

| bit 2        | •                                              | m/Erase Enable                         |                   |                          |                    |                       |                   |

|              |                                                | ogram/erase cyc                        |                   |                          |                    |                       |                   |

|              |                                                | ogramming/eras                         | ing of program    | lasn                     |                    |                       |                   |

| bit 1        | WR: Write Cor                                  | G:NVMADR poir                          | nts to a PEM loc  | ation.                   |                    |                       |                   |

|              |                                                | ne operation indi                      |                   |                          |                    |                       |                   |

|              |                                                | gram/erase opera                       | •                 |                          |                    |                       |                   |

| bit 0        | RD: Read Con                                   | trol bit <sup>(7)</sup>                |                   |                          |                    |                       |                   |

|              |                                                |                                        | -                 |                          |                    | akes one instructi    |                   |

|              |                                                | red when the ope<br>d operation is cor | •                 |                          | only be set (not c | leared) in softwa     | re.               |

|              |                                                |                                        |                   | uvG                      |                    |                       |                   |

| Note 1:      | Bit is undefined while                         |                                        |                   |                          |                    |                       |                   |

| 2:<br>3:     | Bit must be cleared I<br>Bit may be written to |                                        |                   |                          | 200                |                       |                   |

| 3.<br>4:     | This bit can only be                           |                                        | •                 | •                        |                    | lock Seauence"        |                   |

| 5:           | Operations are self-                           | , 0                                    |                   |                          |                    |                       |                   |

| 6:           | Once a write operati                           |                                        |                   |                          | effect.            |                       |                   |

| 7.           | Deading from CCDD                              |                                        |                   | (Decister 10 1)          |                    |                       |                   |

#### REGISTER 13-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

7: Reading from EEPROM loads only NVMDATL<7:0> (Register 13-1).

| R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|-----|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | —   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         | •   |         | •       |         |         | bit 0   |

|         |         |     |         |         |         |         |         |

| Legend: |         |     |         |         |         |         |         |

#### REGISTER 14-3: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 LATA<7:6>: RA<7:6> Output Latch Value bit | s <sup>(1)</sup> |

|---------------------------------------------------|------------------|

|---------------------------------------------------|------------------|

bit 5 **Unimplemented:** Read as '0'

bit 4-0 LATA<4:0>: RA<4:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 14-4: ANSELA: PORTA ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| ANSA7   | ANSA6   | —   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ANSA<7:6>**: Analog Select between Analog or Digital Function on pins RA<7:6>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

bit 5 Unimplemented: Read as '0'

bit 4-0 **ANSA<4:0>**: Analog Select between Analog or Digital Function on pins RA<4:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

# **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# TABLE 15-1: PPS INPUT SIGNAL ROUTING OPTIONS

| INPUT     |                        | Default            |       |             |       |       |           | Remappa   | ble to Pins | of PORTx |       |          |           |       |      |

|-----------|------------------------|--------------------|-------|-------------|-------|-------|-----------|-----------|-------------|----------|-------|----------|-----------|-------|------|

| SIGNAL    | Input Register<br>Name | Location at<br>POR | PIC   | :16(L)F1915 | 5/56  |       | PIC16(L)I | F19175/76 |             |          |       | PIC16(L) | -19185/86 |       |      |

|           |                        | . OK               | PORTA | PORTB       | PORTC | PORTA | PORTB     | PORTC     | PORTD       | PORTA    | PORTB | PORTC    | PORTD     | PORTE | PORT |

| INT       | INTPPS                 | RB0                | •     | •           |       | ٠     | ٠         |           |             | •        | ٠     |          |           |       |      |

| TOCKI     | TOCKIPPS               | RA4                | •     | •           |       | •     | •         |           |             | •        |       |          |           |       | •    |

| T1CKI     | T1CKIPSS               | RC0                | •     |             | •     | •     |           | •         |             |          |       | •        |           | •     |      |

| T1G       | T1GPPS                 | RB5                |       | •           | •     |       | •         | •         |             |          | •     | •        |           |       |      |

| T2IN      | T2INPPS                | RC3                | •     |             | •     | •     |           | •         |             | •        |       | •        |           |       |      |

| T4IN      | T4INPPS                | RC1                |       | •           | •     |       | •         | •         |             |          | •     | •        |           |       |      |

| CCP1      | CCP1PPS                | RC2                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| CCP2      | CCP2PPS                | RC1                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| SMT1WIN   | SMT1WINPPS             | RC0                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| SMT1SIG   | SMT1SIGPPS             | RC1                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| CWG1IN    | CWG1INPPS              | RB0                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       |      |

| CLCIN0    | CLCIN0PPS              | RA0                | •     |             | •     | •     |           | •         |             | •        |       | •        |           |       |      |

| CLCIN1    | CLCIN1PPS              | RA1                | •     |             | •     | •     |           | •         |             | •        |       | •        |           |       |      |

| CLCIN2    | CLCIN2PPS              | RB6                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       |      |

| CLCIN3    | CLCIN3PPS              | RB7                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       |      |

| ADCACT    | ADACTPPS               | RB4                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       |      |

| SCK1/SCL1 | SSP1CLKPPS             | RC3                |       | •           | •     |       | •         | •         |             |          | •     | •        |           |       |      |

| SDI1/SDA1 | SSP1DATPPS             | RC4                |       | •           | •     |       | •         | •         |             |          | •     | •        |           |       |      |

| SS1       | SSP1SS1PPS             | RA5                | •     |             | •     | •     |           |           | •           | •        |       |          | •         |       |      |

| RX1/DT1   | RX1PPS                 | RC7                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| CK1       | TX1PPS                 | RC6                |       | •           | •     |       | •         | •         |             |          |       | •        |           |       | •    |

| RX2/DT2   | RX2PPS                 | RB7                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       |      |

| CK2       | TX2PPS                 | RB6                |       | •           | •     |       | •         |           | •           |          | •     |          | •         |       | 1    |

# **19.6 Register Definitions: ADC Control**

#### REGISTER 19-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0        | R/W-0/0             | U-0                                                                                                                                                   | R/W-0/0          | U-0               | R/W-0/0                        | U-0           | R/W/HC-0        |  |

|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|--------------------------------|---------------|-----------------|--|

| ON             | CONT                | -                                                                                                                                                     | CS               | -                 | FM                             | -             | GO              |  |

| bit 7          |                     |                                                                                                                                                       |                  |                   |                                |               | bit (           |  |

|                |                     |                                                                                                                                                       |                  |                   |                                |               |                 |  |

| Legend:        |                     |                                                                                                                                                       |                  |                   |                                |               |                 |  |

| R = Reada      | ble bit             | W = Writable                                                                                                                                          | bit              | U = Unimple       | mented bit, read               | as '0'        |                 |  |

| u = Bit is u   | nchanged            | x = Bit is unk                                                                                                                                        | nown             | -n/n = Value      | at POR and BO                  | R/Value at al | I other Resets  |  |

| '1' = Bit is s | set                 | '0' = Bit is cle                                                                                                                                      | eared            | HC = Bit is cl    | leared by hardwa               | are           |                 |  |

|                |                     |                                                                                                                                                       |                  |                   |                                |               |                 |  |

| bit 7          | ON: ADC En          | able bit                                                                                                                                              |                  |                   |                                |               |                 |  |

|                | 1 = ADC is e        |                                                                                                                                                       |                  |                   |                                |               |                 |  |

| bit 6          | 0 = ADC is d        | Continuous Or                                                                                                                                         | ention Enchl     | ь                 |                                |               |                 |  |

|                |                     |                                                                                                                                                       |                  |                   | on triggor until A             |               |                 |  |

|                |                     |                                                                                                                                                       |                  | s of the value of | on trigger until A<br>f ADSOI) | DTF IS Set (  | II ADSOLIS SE   |  |

|                |                     |                                                                                                                                                       |                  | ach conversion    |                                |               |                 |  |

| bit 5          | Unimpleme           | nted: Read as                                                                                                                                         | '0'              |                   |                                |               |                 |  |

| bit 4          | CS: ADC Clo         | ock Selection b                                                                                                                                       | it               |                   |                                |               |                 |  |

|                |                     | upplied from FF                                                                                                                                       |                  |                   |                                |               |                 |  |

|                |                     |                                                                                                                                                       |                  | ording to ADCL    | K register                     |               |                 |  |

| bit 3          | •                   | nted: Read as                                                                                                                                         |                  |                   |                                |               |                 |  |

| bit 2          |                     | sults Format/ali                                                                                                                                      | •                |                   |                                |               |                 |  |

|                |                     | and PREV dat                                                                                                                                          |                  |                   |                                |               |                 |  |

| bit 1          |                     | and PREV dat<br>nted: Read as                                                                                                                         | -                | ieu, zero-iilieu  |                                |               |                 |  |

|                | •                   |                                                                                                                                                       |                  |                   |                                |               |                 |  |

| bit 0          |                     | <b>GO:</b> ADC Conversion Status bit <sup>(1)</sup><br>1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. The bit |                  |                   |                                |               |                 |  |

|                |                     |                                                                                                                                                       |                  | y the CONT bit    |                                |               |                 |  |

|                |                     | version comple                                                                                                                                        |                  |                   |                                |               |                 |  |

| Note 1:        | This bit requires ( | ON bit to be set                                                                                                                                      | t.               |                   |                                |               |                 |  |

| 2:             | If cleared by softv | vare while a co                                                                                                                                       | nversion is in p | progress, the re  | esults of the conv             | version up to | this point will |  |

2: If cleared by software while a conversion is in progress, the results of the conversion up to this point will be transfered to ADRES and the state machine will be reset, but the ADIF interrupt flag bit will not be set; filter and threshold operations will not be performed.

| REGISTER        | 19-13: ADC                              | AP: ADC ADD      | DITIONAL SA   | AMPLE CAPA         | CITOR SELE       | CTION REG      | ISTER        |

|-----------------|-----------------------------------------|------------------|---------------|--------------------|------------------|----------------|--------------|

| U-0             | U-0                                     | U-0              | R/W-0/0       | R/W-0/0            | R/W-0/0          | R/W-0/0        | R/W-0/0      |

| _               |                                         |                  |               |                    | ADCAP<4:0>       |                |              |

| bit 7           |                                         |                  |               |                    |                  |                | bit (        |

|                 |                                         |                  |               |                    |                  |                |              |

| Legend:         |                                         |                  |               |                    |                  |                |              |

| R = Readab      | le bit                                  | W = Writable     | bit           | U = Unimpler       | nented bit, read | d as '0'       |              |

| u = Bit is un   | u = Bit is unchanged x = Bit is unknown |                  | nown          | -n/n = Value a     | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is se | et                                      | '0' = Bit is cle | ared          |                    |                  |                |              |

|                 |                                         |                  |               |                    |                  |                |              |

| bit 7-5         | Unimpleme                               | nted: Read as '  | 0'            |                    |                  |                |              |

| bit 4-0         | ADCAP<4:0                               | >: ADC Addition  | nal Sample Ca | apacitor Selection | on bits          |                |              |

|                 | 11111 <b>= 31</b>                       | •                |               |                    |                  |                |              |

|                 | 11110 <b>= 30</b>                       | pF               |               |                    |                  |                |              |

|                 | 11101 <b>= 29</b>                       | pF               |               |                    |                  |                |              |

|                 | •                                       |                  |               |                    |                  |                |              |

|                 | •                                       |                  |               |                    |                  |                |              |

|                 | •                                       |                  |               |                    |                  |                |              |

|                 | 00011 <b>= 3 p</b>                      | F                |               |                    |                  |                |              |

|                 | 00010 <b>= 2 p</b>                      | F                |               |                    |                  |                |              |

|                 | 00001 = 1 p                             | F                |               |                    |                  |                |              |

|                 | 00000 <b>= No</b>                       | additional capa  | citance       |                    |                  |                |              |

#### REGISTER 19-14: ADRPT: ADC REPEAT SETTING REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | RPT     | <7:0>          |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable b   | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

#### bit 7-0 **RPT<7:0>**: ADC Repeat Threshold bits

Determines the number of times that the ADC is triggered before the threshold is checked when the computation is Low-pass Filter, Burst Average, or Average modes. See Table 19-2 for more details.

# PIC16(L)F19155/56/75/76/85/86

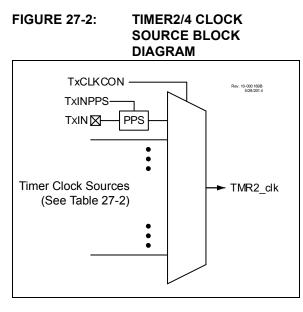

# 27.1 Timer2/4 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset

- · External Reset Source event that resets the timer.

Note: TMR2 is not cleared when T2CON is written.

#### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2

to 00h on the next rising TMR2\_clk edge and increments the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

# 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

# 27.2 Timer2/4 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 29.0 "Capture/Compare/PWM Modules"** for more details on setting up Timer2/4 for use with the CCP, as well as the timing diagrams in **Section 27.5 "Operation Examples"** for examples of how the varying Timer2 modes affect CCP PWM output.

# 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

# 31.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources (See Register 31-9).

The input sources are selected using the CWG1ISM register.

# 31.4 Output Control

#### 31.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

| KEGISTER 51-3                                                                                                                                          |                              |                  |                 |                                  |                 |                 |              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-----------------|----------------------------------|-----------------|-----------------|--------------|--|

| R/W/HS-0/0                                                                                                                                             | R/W-0/0                      | R/W-0/0          | R/W-1/1         | R/W-0/0                          | R/W-1/1         | U-0             | U-0          |  |

| SHUTDOWN <sup>(1, 2)</sup>                                                                                                                             | REN                          | REN LSBD<1:0>    |                 | LSAC                             | <1:0>           |                 | _            |  |

| bit 7                                                                                                                                                  |                              |                  |                 |                                  |                 |                 | bit (        |  |

|                                                                                                                                                        |                              |                  |                 |                                  |                 |                 |              |  |

| Legend:                                                                                                                                                |                              |                  |                 |                                  |                 |                 |              |  |

| HC = Bit is cleare                                                                                                                                     | d by hardware                |                  |                 | HS = Bit is se                   | et by hardware  | 9               |              |  |

| R = Readable bit                                                                                                                                       |                              | W = Writable     | e bit           | U = Unimplei                     | mented bit, rea | ad as 'O'       |              |  |

| u = Bit is unchang                                                                                                                                     | ged                          | x = Bit is unk   | nown            | -n/n = Value a                   | at POR and BO   | OR/Value at all | other Resets |  |

| '1' = Bit is set                                                                                                                                       |                              | '0' = Bit is cle | eared           | q = Value depends on condition   |                 |                 |              |  |

| L:1 7                                                                                                                                                  |                              |                  |                 | hua hit(1, 2)                    |                 |                 |              |  |

| bit 7                                                                                                                                                  |                              | Shutdown sta     | own Event Stat  | tus bit <sup>(1, -)</sup>        |                 |                 |              |  |

|                                                                                                                                                        |                              |                  | ent has occurre | ed                               |                 |                 |              |  |

| bit 6                                                                                                                                                  | REN: Auto-R                  | estart Enable    | bit             |                                  |                 |                 |              |  |

|                                                                                                                                                        | 1 = Auto-res                 | tart enabled     |                 |                                  |                 |                 |              |  |

|                                                                                                                                                        | 0 = Auto-res                 | tart disabled    |                 |                                  |                 |                 |              |  |

| bit 5-4                                                                                                                                                | LSBD<1:0>:                   | CWG1B and        | CWG1D Auto      | -Shutdown Sta                    | te Control bits |                 |              |  |

|                                                                                                                                                        |                              |                  |                 | hen an auto-sh                   |                 |                 |              |  |

|                                                                                                                                                        | •                            | •                |                 | hen an auto-sh<br>an auto-shutdo |                 | •               |              |  |

|                                                                                                                                                        |                              |                  |                 | g polarity, is pla               |                 |                 | equired dead |  |

|                                                                                                                                                        | band in                      | terval           |                 |                                  |                 |                 | ·            |  |

| bit 3-2                                                                                                                                                | LSAC<1:0>:                   | CWG1A and        | CWG1C Auto      | -Shutdown Sta                    | te Control bits |                 |              |  |

|                                                                                                                                                        |                              |                  |                 | hen an auto-sh                   |                 |                 |              |  |

| 10 =A logic '0' is placed on CWG1A/C when an auto-shutdown event is present<br>01 =Pin is tri-stated on CWG1A/C when an auto-shutdown event is present |                              |                  |                 |                                  |                 |                 |              |  |

|                                                                                                                                                        |                              |                  |                 | g polarity, is pla               |                 |                 | equired dead |  |

|                                                                                                                                                        | band in                      |                  |                 |                                  |                 |                 | •            |  |

| bit 1-0                                                                                                                                                | Unimplemer                   | nted: Read as    | · '0'           |                                  |                 |                 |              |  |

| Note 1: This I                                                                                                                                         | bit may be writ<br>juration. | tten while EN    | = 0 (CWG10      | CON0 register                    | ) to place the  | outputs into    | the shutdow  |  |

#### REGISTER 31-5: CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

# 32.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 32.1.1 DATA SELECTION

There are 40 signals available as inputs to the configurable logic. Four 40-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 32-2. Data inputs in the figure are identified by a generic numbered input name.

Table 32-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<5:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation to identify specific multiplexers: LCxD1S<5:0> through LCxD4S<5:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 32-3 through Register 32-6).

| TABLE 32-2: CLC> | DATA INPUT | SELECTION |

|------------------|------------|-----------|

|------------------|------------|-----------|

| LCxDyS<5:0><br>Value | CLCx Input Source      |

|----------------------|------------------------|

| 100101 to 111111     | Reserved               |

| 100100               | EUSART2 (TX/CK) output |

| 100011               | EUSART2 (DT) output    |

| 100010               | CWG1B output           |

| 100001               | CWG1A output           |

| 100000               | RTCC seconds           |

| 011111               | MSSP1 SCK output       |

| 011110               | MSSP1 SDO output       |

| 011101               | EUSART1 (TX/CK) output |

| 011100               | EUSART1 (DT) output    |

| 011011               | CLC4 output            |

| 011010               | CLC3 output            |

| 011001               | CLC2 output            |

| 011000               | CLC1 output            |

| 010111               | IOCIF                  |

| 010110               | ZCD output             |

| 010101               | C2OUT                  |

| 010100               | C10UT                  |

| 010011               | PWM4 output            |

| 010010               | PWM3 output            |

| 010001               | CCP2 output            |

| 010000               | CCP1 output            |

| 001111               | SMT overflow           |

| 001110               | Timer4 overflow        |

| 001101               | Timer2 overflow        |

| 001100               | Timer1 overflow        |

| 001011               | Timer0 overflow        |

| 001010               | ADCRC                  |

| 001001               | SOSC                   |

| 001000               | MFINTOSC (32 kHz)      |

| 000111               | MFINTOSC (500 kHz)     |

| 000110               | LFINTOSC               |

| 000101               | HFINTOSC               |

| 000100               | FOSC                   |

| 000011               | CLCIN3PPS              |

| 000010               | CLCIN2PPS              |

| 000001               | CLCIN1PPS              |

| 000000               | CLCIN0PPS              |

#### 34.1.2.3 Receive Interrupts

The RXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RXxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RXxIF interrupts are enabled by setting all of the following bits:

- RXxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RXxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 34.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCxREG will not clear the FERR bit.

#### 34.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

#### 34.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 34.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RXxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

# PIC16(L)F19155/56/75/76/85/86

# REGISTER 34-4: RCxREG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | RCxRE | G<7:0> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 RCxREG<7:0>: Lower eight bits of the received data; read-only; see also RX9D (Register 34-2)

**Note 1:** RCxREG (including the 9<sup>th</sup> bit) is double buffered, and data is available while new data is being received.

# REGISTER 34-5: TXxREG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------------|-------|-------|--------|-------|-------|-------|

|       |             |       | TXxRE | G<7:0> |       |       |       |

| bit 7 | bit 7 bit C |       |       |        |       |       |       |

| Legend:              |                      |                                                       |