Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 43                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 39x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

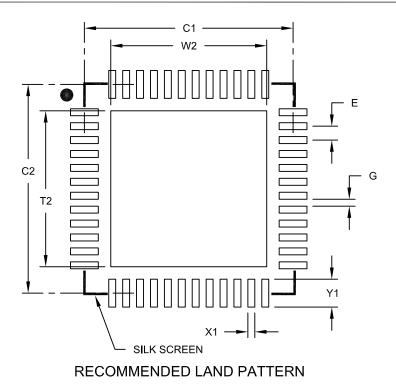

| Package / Case             | 48-TQFP                                                                      |

| Supplier Device Package    | 48-TQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf19185t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 2: PACKAGES

| Device         | 28-Pin<br>SPDIP | 28-Pin<br>SOIC | 28-Pin<br>SSOP | 28-Pin<br>UQFN<br>(4x4) | 40-Pin<br>PDIP | 40-Pin<br>UQFN<br>(5x5) | 44-Pin<br>TQFP | 48-Pin<br>UQFN<br>(6x6) | 48-Pin<br>TQFP<br>(7x7) |

|----------------|-----------------|----------------|----------------|-------------------------|----------------|-------------------------|----------------|-------------------------|-------------------------|

| PIC16(L)F19155 | Х               | Х              | Х              | Х                       |                |                         |                |                         |                         |

| PIC16(L)F19156 | Х               | Х              | Х              | Х                       |                |                         |                |                         |                         |

| PIC16(L)F19175 |                 |                |                |                         | Х              | Х                       | Х              |                         |                         |

| PIC16(L)F19176 |                 |                |                |                         | Х              | Х                       | Х              |                         |                         |

| PIC16(L)F19185 |                 |                |                |                         |                |                         |                | Х                       | Х                       |

| PIC16(L)F19186 |                 |                |                |                         |                |                         |                | Х                       | Х                       |

**Note:** Pin details are subject to change.

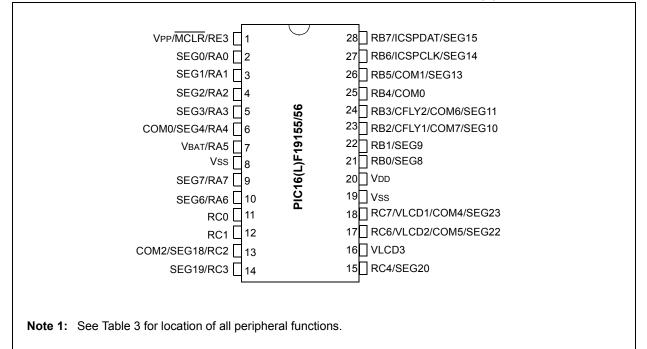

### FIGURE 1: 28-PIN SSOP, SPDIP AND SOIC PIN DIAGRAM FOR PIC16(L)F19155/56

| Core Registers<br>(Table 4-3)                       | C80h         | Core Registers<br>(Table 4-3)    | D00h         | Core Registers<br>(Table 4-3)  | D80h         | Core Registers<br>(Table 4-3)  | E00h         | Core Registers<br>(Table 4-3)  | E80h         | Core Registers<br>(Table 4-3)  |

|-----------------------------------------------------|--------------|----------------------------------|--------------|--------------------------------|--------------|--------------------------------|--------------|--------------------------------|--------------|--------------------------------|

| RTCCON                                              | C8Ch         | _                                | D0Ch         | _                              | D8Ch         | _                              | E0Ch         | _                              | E8Ch         | VB0GPR                         |

| RTCCAL                                              | C8Dh         | _                                | D0Dh         | —                              | D8Dh         | —                              | E0Dh         | _                              | E8Dh         | VB1GPR                         |

| ALRMCON                                             | C8Eh         | -                                | D0Eh         | —                              | D8Eh         | —                              | E0Eh         | —                              | E8Eh         | VB2GPR                         |

| ALRMRPT                                             | C8Fh         | -                                | D0Fh         | —                              | D8Fh         | —                              | E0Fh         | —                              | E8Fh         | VB3GPR                         |

| YEAR                                                | C90h         | -                                | D10h         | —                              | D90h         | —                              | E10h         | —                              | E90h         | —                              |

| MONTH                                               | C91h         | —                                | D11h         | —                              | D91h         | —                              | E11h         | —                              | E91h         | —                              |

| WEEKDAY                                             | C92h         | —                                | D12h         | —                              | D92h         | —                              | E12h         | —                              | E92h         | —                              |

| DAY                                                 | C93h         | _                                | D13h         | _                              | D93h         | _                              | E13h         | _                              | E93h         | _                              |

| HOURS                                               | C94h         | _                                | D14h         | _                              | D94h         | _                              | E14h         | _                              | E94h         | _                              |

| MINUTES                                             | C95h         | _                                | D15h         | —                              | D95h         | _                              | E15h         | _                              | E95h         | _                              |

| SECONDS                                             | C96h         | _                                | D16h         | —                              | D96h         | _                              | E16h         | _                              | E96h         | _                              |

| ALRMMTH                                             | C97h         | _                                | D17h         | _                              | D97h         | _                              | E17h         | _                              | E97h         | _                              |

| ALRMWD                                              | C98h         | _                                | D18h         | —                              | D98h         | _                              | E18h         | _                              | E98h         | _                              |

| ALRMDAY                                             | C99h         | _                                | D19h         | _                              | D99h         | _                              | E19h         | _                              | E99h         | _                              |

| ALRMHR                                              | C9Ah         | _                                | D1Ah         | _                              | D9Ah         | _                              | E1Ah         | _                              | E9Ah         | _                              |

| ALRMMIN                                             | C9Bh         | _                                | D1Bh         | _                              | D9Bh         | _                              | E1Bh         | _                              | E9Bh         | _                              |

| ALRMSEC                                             | C9Ch         | _                                | D1Ch         | —                              | D9Ch         | _                              | E1Ch         | _                              | E9Ch         | _                              |

| _                                                   | C9Dh         | _                                | D1Dh         | —                              | D9Dh         | _                              | E1Dh         | _                              | E9Dh         | _                              |

| _                                                   | C9Eh         | _                                | D1Eh         | —                              | D9Eh         | _                              | E1Eh         | _                              | E9Eh         | _                              |

| —                                                   | C9Fh         | —                                | D1Fh         | —                              | D9Fh         | —                              | E1Fh         | —                              | E9Fh         | —                              |

|                                                     | CA0h         | General Purpose                  | D20h         |                                | DA0h         |                                | E20h         |                                | EA0h         |                                |

| General Purpose<br>Register 80 Bytes <sup>(2)</sup> | CBFh         | Register 32 Bytes <sup>(2)</sup> |              | _                              |              | _                              |              | _                              |              | _                              |

| Register of Bytes                                   | CC0h<br>CEFh | _                                | D6Fh         |                                | DEFh         |                                | E6Fh         |                                | EEFh         |                                |

|                                                     | CEFn<br>CF0h |                                  | D6Fn<br>D70h |                                | DEFN<br>DF0h |                                | E6Fh<br>E70h |                                | EEFN<br>EF0h |                                |

| Common RAM<br>Accesses 70h-7Fh                      | CFFh         | Common RAM<br>Accesses 70h-7Fh   | D76h         | Common RAM<br>Accesses 70h-7Fh | DFFh         | Common RAM<br>Accesses 70h-7Fh | E70h         | Common RAM<br>Accesses 70h-7Fh | EFFh         | Common RAM<br>Accesses 70h-7Fh |

Bank 27

Bank 28

Bank 29

Bank 26

**TABLE 4-9**: PIC16(L)F19155/56/75/76/85/86 MEMORY MAP, BANKS 24-29 BANK 25

Note 1: Unimplemented locations read as '0'.

2: Present only on PIC16(L)F19156/76/86.

Present only on PIC16(L)F19185/86. 3:

BANK 24

4: Banks 30-57 have been omitted from the tables in the data sheet since they have unimplemented registers.

5: See Table 4-4 for general purpose RAM size and bank location.

C00h

C0Ch C0Dh C0Eh C0Fh C10h C11h C12h

C13h C14h C15h C16h C17h

C18h C19h C1Ah C1Bh C1Ch C1Dh C1Eh C1Fh C20h

C6Fh C70h

C7Fh

| Address | Name | Bit 7 | Bit 6         | Bit 5 | Bit 4               | Bit 3               | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue on</u> :<br>MCLR |  |  |  |

|---------|------|-------|---------------|-------|---------------------|---------------------|-------------|-------|-------|-----------------------|----------------------------|--|--|--|

| Bank 10 |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

|         |      |       |               | CPU   | CORE REGISTER       | S; see Table 4-3 fo | r specifics |       |       |                       |                            |  |  |  |

| 50Ch    | _    |       |               |       | Unimple             | mented              |             |       |       |                       |                            |  |  |  |

| 50Dh    |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 50Eh    |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 50Fh    |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 510h    |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 511h    |      |       |               |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 512h    | _    |       | Unimplemented |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 513h    | _    |       | Unimplemented |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 514h    |      |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 515h    | _    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 516h    | _    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 517h    | _    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 518h    | —    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 519h    | —    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 51Ah    | —    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 51Bh    | _    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 51Ch    | _    |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 51Dh    |      |       |               |       | Unimple             | emented             |             |       |       |                       |                            |  |  |  |

| 51Eh    | _    |       | Unimplemented |       |                     |                     |             |       |       |                       |                            |  |  |  |

| 51Fh    | _    |       |               |       | 1Fh — Unimplemented |                     |             |       |       |                       |                            |  |  |  |

### TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED)

Preliminary

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Unimplemented data memory locations, read as '0'.

| 1 | TABLE 4-12: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 PIC16(L)F19155/56/75/76/85/86 (CONTINUED) |      |       |       |       |       |       |       |       |       |           |  |

|---|----------------------------------------------------------------------------------------------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|--|

|   | Addroop                                                                                            | Nomo | Dit 7 | Dit 6 | Dit E | Dit 4 | Dit 2 | Dit 2 | Dit 1 | Rit 0 | Value on: |  |

| Address    | Name      | Bit 7   | Bit 6         | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|------------|-----------|---------|---------------|-------|----------|--------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 61 (C | ontinued) | tinued) |               |       |          |        |       |       |       |                       |                            |  |

| 1EE5h      | —         |         |               |       |          |        |       |       |       |                       |                            |  |

| 1EE6h      | —         |         |               |       |          |        |       |       |       |                       |                            |  |

| 1EE7h      | —         |         |               |       |          |        |       |       |       |                       |                            |  |

| 1EE8h      | _         |         |               |       |          |        |       |       |       |                       |                            |  |

| 1EE9h      | —         |         | Unimplemented |       |          |        |       |       |       |                       |                            |  |

| 1EEAh      | —         |         |               |       | Unimpler | nented |       |       |       |                       |                            |  |

| 1EEBh      | —         |         |               |       | Unimpler | nented |       |       |       |                       |                            |  |

| 1EECh      | —         |         |               |       | Unimpler | nented |       |       |       |                       |                            |  |

| 1EEDh      | —         |         |               |       | Unimpler | nented |       |       |       |                       |                            |  |

| 1EEEh      | _         |         |               |       |          |        |       |       |       |                       |                            |  |

| 1EEFh      | _         |         | Unimplemented |       |          |        |       |       |       |                       |                            |  |

| 1          |           |         |               |       |          |        |       |       |       |                       |                            |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Unimplemented data memory locations, read as '0'.

| Name    | Bit 7   | Bit 6   | Bit 5     | Bit 4 | Bit 3     | Bit 2      | Bit 1  | Bit 0 | Register<br>on Page |

|---------|---------|---------|-----------|-------|-----------|------------|--------|-------|---------------------|

| OSCCON1 | —       |         | NOSC<2:0> |       |           | NDIV<      | 3:0>   |       | 152                 |

| OSCCON2 | —       |         | COSC<2:0> |       | CDIV<3:0> |            |        |       | 152                 |

| OSCCON3 | CWSHOLD | SOSCPWR | _         | ORDY  | NOSCR     | -          | _      | -     | 154                 |

| OSCFRQ  | _       | _       | _         | _     | _         | HFFRQ<2:0> |        |       | 157                 |

| OSCSTAT | EXTOR   | HFOR    | MFOR      | LFOR  | SOR       | ADOR       | —      | PLLR  | 155                 |

| OSCTUNE | —       | _       |           |       | HFTUN     | HFTUN<5:0> |        |       |                     |

| OSCEN   | EXTOEN  | HFOEN   | MFOEN     | LFOEN | SOSCEN    | ADOEN      | _      | _     | 156                 |

| ACTCON  | ACTEN   | ACTUD   | _         | _     | ACTLOCK   | _          | ACTORS |       | 158                 |

### TABLE 9-3:SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 9-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2     | Bit 9/1 | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|--------------|---------|----------|---------------------|

| CONFIG1 | 13:8 | —       | _       | FCMEN      | _        | CSWEN    | LCDPEN       | VBATEN  | CLKOUTEN | 100                 |

| CONFIGT | 7:0  | —       | F       | RSTOSC<2:0 | >        | _        | FEXTOSC<2:0> |         |          | 120                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| U-0            | U-0                                                                                   | U-0                                 | U-0          | R/W-0/0      | U-0              | R/W-0/0  | R/W-0/0 |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------|-------------------------------------|--------------|--------------|------------------|----------|---------|--|--|--|--|

| _              | —                                                                                     | —                                   | —            | TMR4IE       | —                | TMR2IE   | TMR1IE  |  |  |  |  |

| bit 7          |                                                                                       |                                     |              |              |                  |          | bit 0   |  |  |  |  |

|                |                                                                                       |                                     |              |              |                  |          |         |  |  |  |  |

| Legend:        |                                                                                       |                                     |              |              |                  |          |         |  |  |  |  |

| R = Reada      | ble bit                                                                               | W = Writable                        | bit          | U = Unimpler | mented bit, read | d as '0' |         |  |  |  |  |

| u = Bit is u   | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all othe |                                     |              |              |                  |          |         |  |  |  |  |

| '1' = Bit is s | Bit is set '0' = Bit is cleared HS = Hardware set                                     |                                     |              |              |                  |          |         |  |  |  |  |

|                |                                                                                       |                                     |              |              |                  |          |         |  |  |  |  |

| bit 7-4        | Unimpleme                                                                             | nted: Read as '                     | 0'           |              |                  |          |         |  |  |  |  |

| bit 3          | TMR4IE: TMR4 to PR4 Match Interrupt Enable bit                                        |                                     |              |              |                  |          |         |  |  |  |  |

|                |                                                                                       | the Timer4 to P                     |              | •            |                  |          |         |  |  |  |  |

|                | 0 = Disables                                                                          | the Timer4 to P                     | PR4 match in | terrupt      |                  |          |         |  |  |  |  |

| bit 2          | Unimpleme                                                                             | nted: Read as '                     | 0'           |              |                  |          |         |  |  |  |  |

| bit 1          |                                                                                       | IR2 to PR2 Mate                     |              |              |                  |          |         |  |  |  |  |

|                |                                                                                       | s the Timer2 to                     |              |              |                  |          |         |  |  |  |  |

| L:1 0          |                                                                                       | s the Timer2 to                     |              | •            |                  |          |         |  |  |  |  |

| bit 0          |                                                                                       | ner1 Overflow Ir<br>s the Timer1 ov | •            |              |                  |          |         |  |  |  |  |

|                |                                                                                       | s the Timer1 ov                     |              | •            |                  |          |         |  |  |  |  |

|                |                                                                                       |                                     |              | - F          |                  |          |         |  |  |  |  |

| Note:          | Bit PEIE of the IN                                                                    | ITCON register                      | must be      |              |                  |          |         |  |  |  |  |

|                | set to enable a                                                                       |                                     |              |              |                  |          |         |  |  |  |  |

|                | controlled by regi                                                                    | sters PIE1-PIE8                     |              |              |                  |          |         |  |  |  |  |

# REGISTER 10-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

|         |         |         | -       |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| R/W-1/1 |

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

### REGISTER 14-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRB<7:0>: PORTB Slew Rate Enable bits For RB<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 14-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

# Legend:

| Legena.              |                      |                                                       |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |  |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits

For RB<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### REGISTER 14-17: HIDRVB: PORTB HIGH DRIVE CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|-----|-----|-----|-----|---------|-------|

| —     | —   | —   | —   | —   | —   | HIDB1   | —     |

| bit 7 |     |     |     |     |     |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'.              |

|---------|------------------------------------------|

| bit 1   | HIDB1: PORTB High Drive Enable bit       |

|         | For RB1 pin                              |

|         | 1 = High current source and sink enabled |

|         | 0 = Standard current source and sink     |

| bit 0   | Unimplemented: Read as '0'.              |

| IOCCP7 IOCCP6 — IOCCP4 IOCCP3 IOCCP2 IOCCP1 IOCCP                                                                                                                                                                                                                                  |                      |            |                   |            |                                    |               |                  |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|-------------------|------------|------------------------------------|---------------|------------------|-------------|

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared | R/W-0/0              | R/W-0/0    | U-0               | R/W-0/0    | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0     |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared               | IOCCP7               | IOCCP6     | —                 | IOCCP4     | IOCCP3                             | IOCCP2        | IOCCP1           | IOCCP0      |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Rese'1' = Bit is set'0' = Bit is cleared                                                                                    | bit 7                |            |                   |            |                                    |               |                  | bit 0       |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Rese'1' = Bit is set'0' = Bit is cleared                                                                                    |                      |            |                   |            |                                    |               |                  |             |

| u = Bit is unchangedx = Bit is unknown<br>'0' = Bit is cleared-n/n = Value at POR and BOR/Value at all other Rese'1' = Bit is set'0' = Bit is cleared                                                                                                                              | Legend:              |            |                   |            |                                    |               |                  |             |

| '1' = Bit is set '0' = Bit is cleared                                                                                                                                                                                                                                              | R = Readable I       | bit        | W = Writable      | bit        | U = Unimplemented bit, read as '0' |               |                  |             |

|                                                                                                                                                                                                                                                                                    | u = Bit is unchanged |            | x = Bit is unkr   | nown       | -n/n = Value a                     | at POR and BO | R/Value at all o | ther Resets |

| bit 7-6 <b>IOCCP&lt;7:6&gt;:</b> Interrupt-on-Change PORTC Positive Edge Enable bits                                                                                                                                                                                               | '1' = Bit is set     |            | '0' = Bit is clea | ared       |                                    |               |                  |             |

| bit 7-6 <b>IOCCP&lt;7:6&gt;:</b> Interrupt-on-Change PORTC Positive Edge Enable bits                                                                                                                                                                                               |                      |            |                   |            |                                    |               |                  |             |

|                                                                                                                                                                                                                                                                                    | bit 7-6              | IOCCP<7:6> | : Interrupt-on-C  | hange PORT | C Positive Edg                     | e Enable bits |                  |             |

|         | <ul> <li>1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will<br/>be set upon detecting an edge.</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = Interrupt-on-Change disabled for the associated pin                                                                                                     |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 4-0 | IOCCP<4:0>: Interrupt-on-Change PORTC Positive Edge Enable bits                                                                                             |

|         | <ul> <li>1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will<br/>be set upon detecting an edge.</li> </ul> |

0 = Interrupt-on-Change disabled for the associated pin

### REGISTER 17-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | —   | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         | •   |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | <ul> <li>IOCCN&lt;7:6&gt;: Interrupt-on-Change PORTC Negative Edge Enable bits</li> <li>1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.</li> <li>0 = Interrupt-on-Change disabled for the associated pin</li> </ul> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                              |

| bit 4-0 | <ul> <li>IOCCN&lt;4:0&gt;: Interrupt-on-Change PORTC Negative Edge Enable bits</li> <li>1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.</li> <li>0 = Interrupt-on-Change disabled for the associated pin</li> </ul> |

# 20.4 Minimum Operating VDD

When the temperature circuit is operated in Low range, the device may be operated at any operating voltage that is within specifications. When the temperature circuit is operated in High range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 20-1 shows the recommended minimum  $V \mbox{\scriptsize DD}$  vs. Range setting.

TABLE 20-1: RECOMMENDED VDD vs. RANGE

| Min.VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |  |  |  |

|--------------------|---------------------|--|--|--|

| (High Range)       | (Low Range)         |  |  |  |

| ≥ 2.5              | ≥ 1.8               |  |  |  |

### 20.5 Temperature Indicator Range

The temperature indicator circuit operates in either High or Low range. The High range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range. High range requires a higher-bias voltage to operate and thus, a higher VDD is needed. The Low range is selected by clearing the TSRNG bit of the FVRCON register. The Low range generates a lower sensor voltage and thus, a lower VDD voltage is needed to operate the circuit. The output voltage of the sensor is the highest value at  $-40^{\circ}$ C and the lowest value at  $+125^{\circ}$ C.

- **High Range:** The High range is used in applications with the reference for the ADC, VREF = 2.048V. This range may not be suitable for battery-powered applications.

- Low Range: This mode is useful in applications in which the VDD is too low for high-range operation. The VDD in this mode can be as low as 1.8V. VDD must, however, be at least 0.5V higher than the maximum sensor voltage depending on the expected low operating temperature.

# 20.6 DIA Information

DIA data provide ADC readings at one operating temperature. DIA data is taken during factory testing and stored within the device. The 90°C reading alone allows single-point calibration as described in Section 20.2.1, Calibration, by solving Equation 20-1 for TOFFSET.

Refer to **Section 6.0 "Device Information Area"** for more information on the data stored in the DIA and how to access them.

**Note:** The lower temperature range (e.g., - 40°C) will suffer in accuracy because temperature conversion must extrapolate below the reference points, amplifying any measurement errors.

### TABLE 20-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFV  | R<1:0> | ADFVF | R<1:0> | 285                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are unused by the temperature indicator module.

# PIC16(L)F19155/56/75/76/85/86

EQUATION 23-2: R-C CALCULATIONS V<sub>peak</sub> = external voltage source peak voltage = external voltage source frequency f С = series capacitor R = series resistor V<sub>c</sub> = Peak capacitor voltage = Capacitor induced zero crossing phase φ advance in radians Τ<sub>φ</sub> = Time ZC event occurs before actual zero crossing  $Z = \frac{V_{PEAK}}{3x10^{-4}}$  $X_C = \frac{1}{(2\pi fC)}$  $R = \sqrt{Z^2 - X_C}$  $V_c = X_c (3x10^{-4})$  $\phi = Tan^{-1}\left(\frac{X_c}{R}\right)$  $T_{\phi} = \frac{\phi}{(2\pi f)}$

V<sub>rms</sub> = 120

# EXAMPLE 23-1: R-C CALCULATIONS EXAMPLE

$$V_{peak} = V_{rms} \cdot \sqrt{2} = 169.7$$

f = 60 Hz

C = 0.1 µf

$$Z = \frac{V_{peak}}{3 \times 10^{-4}} = \frac{169.7}{3 \times 10^{-4}} = 565.7 \ kOhms$$

$$X_{c} = \frac{1}{(2\pi fC)} = \frac{1}{(2\pi \cdot 60 \cdot 1 \cdot 10^{-7})} = 26.53 \ kOhms$$

R = 560 kOhms

$$Z_{R} = \sqrt{(R^{2} + X_{c}^{-2})} = 560.6 \ kOhm \ (using actual resistor)$$

$$I_{peak} = \frac{V_{peak}}{Z_{R}} = 302.7 \cdot 10^{-6}$$

$$V_{c} = X_{c} \cdot I_{peak} = 8.0 \ V$$

$$\phi = Tan^{-1} \left(\frac{X_{c}}{R}\right) = 0.047 \ radians$$

$$T_{\phi} = \frac{\phi}{(2\pi f)} = 125.6 \ \mu s$$

© 2017 Microchip Technology Inc.

#### 27.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- · Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

**FIGURE 27-6:** EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM

| (N                         | <b>IODE =</b> 00100)                                                                                                                                                                             |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                            | Rev. 10.000 1970<br>500/2014                                                                                                                                                                     |  |

| MODE                       | 0b00100                                                                                                                                                                                          |  |

| TMRx_dk                    |                                                                                                                                                                                                  |  |

| PRx                        | 5                                                                                                                                                                                                |  |

| Instruction <sup>(1)</sup> | (BSF)                                                                                                                                                                                            |  |

| ON                         |                                                                                                                                                                                                  |  |

| TMRx_ers                   |                                                                                                                                                                                                  |  |

| TMRx                       | 0 1 2 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1                                                                                                                                                    |  |

| TMRx_postscaled            |                                                                                                                                                                                                  |  |

| PWM Duty<br>Cycle          | 3                                                                                                                                                                                                |  |

| PWM Output                 |                                                                                                                                                                                                  |  |

|                            | <ol> <li>BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the<br/>set or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock in</li> </ol> |  |

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 27-6.

### **REGISTER 28-16: SMTxPRL: SMT PERIOD REGISTER – LOW BYTE**

| R/W-x/1          | R/W-x/1 | R/W-x/1           | R/W-x/1 | R/W-x/1        | R/W-x/1         | R/W-x/1        | R/W-x/1      |

|------------------|---------|-------------------|---------|----------------|-----------------|----------------|--------------|

|                  |         |                   | SMTxF   | PR<7:0>        |                 |                |              |

| bit 7            |         |                   |         |                |                 |                | bit 0        |

|                  |         |                   |         |                |                 |                |              |

| Legend:          |         |                   |         |                |                 |                |              |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, rea | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                 |                |              |

bit 7-0 SMTxPR<7:0>: Significant bits of the SMT Timer Value for Period Match – Low Byte

### REGISTER 28-17: SMTxPRH: SMT PERIOD REGISTER – HIGH BYTE

| R/W-x/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMTxPF  | R<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<15:8>: Significant bits of the SMT Timer Value for Period Match – High Byte

### REGISTER 28-18: SMTxPRU: SMT PERIOD REGISTER – UPPER BYTE

| R/W-x/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMTxPR  | <23:16> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<23:16>: Significant bits of the SMT Timer Value for Period Match – Upper Byte

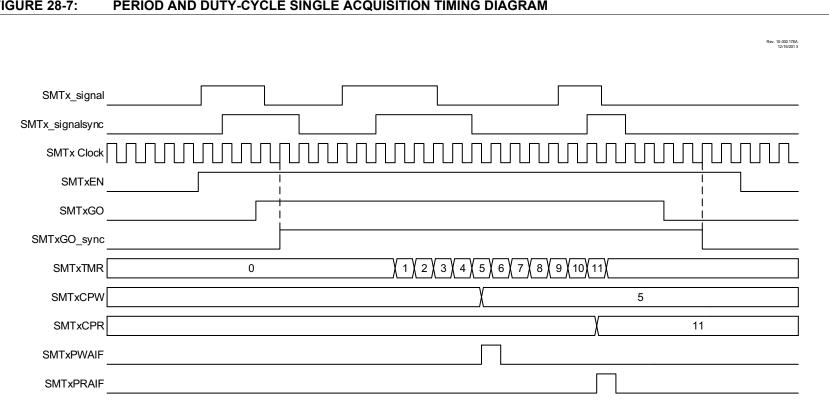

### 28.7.3 PERIOD AND DUTY-CYCLE MODE

In Duty-Cycle mode, either the duty cycle or period (depending on polarity) of the SMTx\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMTxTMR resetting to  $0 \times 0001$ . In addition, the SMTxGO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 28-6 and Figure 28-7.

PIC16(L)F19155/56/75/76/85/86

FIGURE 28-7:

| Name      | Bit 7    | Bit 6    | Bit 5    | Bit 4          | Bit 3          | Bit 2        | Bit 1    | Bit 0    |     |

|-----------|----------|----------|----------|----------------|----------------|--------------|----------|----------|-----|

| CLC4GLS1  | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N       | LC4G2D2T       | LC4G2D2N     | LC4G2D1T | LC4G2D1N | 506 |

| CLC4GLS2  | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N       | LC4G3D2T       | LC4G3D2N     | LC4G3D1T | LC4G3D1N | 507 |

| CLC4GLS3  | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N       | LC4G4D2T       | LC4G4D2N     | LC4G4D1T | LC4G4D1N | 508 |

| CLCIN0PPS | —        | -        | —        |                | (              | CLCIN0PPS<4: | 0>       |          | 264 |

| CLCIN1PPS | _        | _        | _        |                | CLCIN1PPS<4:0> |              | 264      |          |     |

| CLCIN2PPS | _        | _        | _        | CLCIN2PPS<4:0> |                |              | 264      |          |     |

| CLCIN3PPS | _        | _        | _        |                | (              | CLCIN3PPS<4: | 0>       |          | 264 |

# TABLE 32-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued)

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

| R-0/0                | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                                                                                                                                                                            | R/W-0/0                                                                                                                                 | R/W-0/0                                                      | R/W-0/0                                                        | R/W-0/0           | R/W-0/0          |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|-------------------|------------------|

| ACKTIM <sup>(3</sup> | <sup>3)</sup> PCIE                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SCIE                                                                                                                                                                               | BOEN                                                                                                                                    | SDAHT                                                        | SBCDE                                                          | AHEN              | DHEN             |

| bit 7                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                  | -                                                                                                                                       | •                                                            |                                                                |                   | bit              |

| Legend:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |                                                                                                                                         |                                                              |                                                                |                   |                  |

| R = Readabl          | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                               | W = Writable b                                                                                                                                                                     | it                                                                                                                                      | U = Unimplem                                                 | ented bit, read as                                             | ʻ0'               |                  |

| u = Bit is und       | changed                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x = Bit is unkno                                                                                                                                                                   | own                                                                                                                                     | -n/n = Value at                                              | t POR and BOR/V                                                | alue at all other | Resets           |

| '1' = Bit is se      | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '0' = Bit is clear                                                                                                                                                                 | red                                                                                                                                     |                                                              |                                                                |                   |                  |

| bit 7                | 1 = Indicates t                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nowledge Time S<br>he I <sup>2</sup> C bus is in a<br>knowledge seque                                                                                                              | n Acknowledge                                                                                                                           | sequence, set o                                              | on 8 <sup>th</sup> falling edge<br>of SCL clock                | of SCL clock      |                  |

| bit 6                | 1 = Enable inte                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ndition Interrupt l<br>errupt on detection<br>tion interrupts are                                                                                                                  | n of Stop condi                                                                                                                         |                                                              |                                                                |                   |                  |

| bit 5                | 1 = Enable inte                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ndition Interrupt<br>errupt on detectio<br>tion interrupts ar                                                                                                                      | n of Start or Re                                                                                                                        | • /                                                          |                                                                |                   |                  |

| bit 4                | $\frac{\text{In SPI Slave m}}{1 = SSPx}$ $0 = \text{If new}$ $regist$ $\frac{\text{In I}^2C \text{ Master r}}{\text{This bit is}}$ $\frac{\text{In I}^2C \text{ Slave m}}{1 = SSPx}$ $SSP(0)$ $0 = SSPx$                                                                                                                                                                                                                                                            | BUF updates even<br>v byte is received<br>ter is set, and the<br><u>mode and SPI Ma</u><br>ignored.<br><u>ode:</u><br>(BUF is updated<br>DV bit only if the<br>BUF is only updated | ery time that a r<br>d with BF bit of<br>buffer is not up<br>aster mode:<br>and $\overline{ACK}$ is get<br>BF bit = 0.<br>ated when SSP | the SSPxSTAT r<br>odated<br>nerated for a rec<br>OV is clear | shifted in ignoring<br>egister already se<br>ceived address/da | et, SSPOV bit of  |                  |

| bit 3                | 1 = Minimum c                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Hold Time Select<br>of 300 ns hold tim<br>of 100 ns hold tim                                                                                                                       | e on SDA after                                                                                                                          | the falling edge                                             |                                                                |                   |                  |

| bit 2                | <ul> <li>0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL</li> <li>SBCDE: Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)</li> <li>If, on the rising edge of SCL, SDA is sampled low when the module is outputting a high state, the BCL1IF</li> <li>PIR3 register is set, and bus goes idle</li> <li>1 = Enable slave bus collision interrupts</li> <li>0 = Slave bus collision interrupts are disabled</li> </ul> |                                                                                                                                                                                    |                                                                                                                                         |                                                              |                                                                |                   | 3CL1IF bit of th |

| bit 1                | AHEN: Addres<br>1 = Following<br>register w                                                                                                                                                                                                                                                                                                                                                                                                                         | s Hold Enable bi                                                                                                                                                                   | t (I <sup>2</sup> C Slave mo<br>edge of SCL t<br>the SCL will b                                                                         | for a matching re                                            | eceived address                                                | byte; CKP bit of  | the SSPxCON      |

| bit 0                | 1 = Following                                                                                                                                                                                                                                                                                                                                                                                                                                                       | N1 register and S                                                                                                                                                                  | edge of SCL f                                                                                                                           | or a received da                                             | ita byte; slave ha                                             | rdware clears the | e CKP bit of th  |

| l                    | For daisy-chained Sl<br>byte is received and<br>This bit has no effec                                                                                                                                                                                                                                                                                                                                                                                               | BF = 1, but hard                                                                                                                                                                   | ware continues                                                                                                                          | to write the mos                                             | t recent byte to SS                                            | SPxBUF.           |                  |

### REGISTER 33-4: SSPxCON3: SSPx CONTROL REGISTER 3

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

**3:** The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

# PIC16(L)F19155/56/75/76/85/86

# REGISTER 34-4: RCxREG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | RCxRE | G<7:0> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 RCxREG<7:0>: Lower eight bits of the received data; read-only; see also RX9D (Register 34-2)

**Note 1:** RCxREG (including the 9<sup>th</sup> bit) is double buffered, and data is available while new data is being received.

# REGISTER 34-5: TXxREG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------------|-------|-------|--------|-------|-------|-------|

|       |             |       | TXxRE | G<7:0> |       |       |       |

| bit 7 | bit 7 bit C |       |       |        |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TXxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 34-1)

**Note 1:** TXxREG (including the 9th bit) is double buffered, and can be written when previous data has started shifting.

# **REGISTER 34-6:** SPxBRGL<sup>(1)</sup>: BAUD RATE GENERATOR REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| SPxBRG<7:0> |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SPxBRG<7:0>: Lower eight bits of the Baud Rate Generator

**Note 1:** Writing to SP1BRG resets the BRG counter.

# 35.0 LIQUID CRYSTAL DISPLAY (LCD) CONTROLLER

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. The module drives panels with up to eight commons and up to 38 segments pins. It also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- Two LCD clock sources with selectable prescaler

- Up to eight commons: See Table 35-1 for multiplexing options.

- Static (One common)

- 1/2 Multiplex (two commons)

- 1/3 Multiplex (three commons)

- 1/4 Multiplex (four commons)

- 1/5 Multiplex (five commons)

- 1/6 Multiplex (six commons)

- 1/7 Multiplex (seven commons)

- 1/8 Multiplex (eight commons)

- Static, 1/2 (1/2 Multiplex only) or 1/3 LCD bias (1/3 Multiplex and higher)

- On-chip bias generator with dedicated charge pump to support a range of fixed and variable bias options

- · Internal resistors for bias voltage generation

- · Software contrast control through internal biasing

A simplified block diagram of the module is shown in Figure 35-1.

| Device I III Count | Number of Cold Osed |    | Number of 1 ossible beginents |

|--------------------|---------------------|----|-------------------------------|

| 28-Pin             | 1                   | 19 | 19                            |

|                    | 2                   | 18 | 36                            |

|                    | 3                   | 17 | 51                            |

|                    | 4                   | 16 | 64                            |

|                    | 5                   | 15 | 75                            |

|                    | 6                   | 14 | 84                            |

|                    | 7                   | 13 | 91                            |

|                    | 8                   | 12 | 96                            |

| 40-Pin, 44-Pin     | 1                   | 30 | 30                            |

|                    | 2                   | 29 | 58                            |

|                    | 3                   | 28 | 84                            |

|                    | 4                   | 27 | 108                           |

|                    | 5                   | 26 | 130                           |

|                    | 6                   | 25 | 150                           |

|                    | 7                   | 24 | 168                           |

|                    | 8                   | 23 | 184                           |

| 48-Pin             | 1                   | 38 | 38                            |

|                    | 2                   | 37 | 74                            |

|                    | 3                   | 36 | 108                           |

|                    | 4                   | 35 | 140                           |

|                    | 5                   | 34 | 170                           |

|                    | 6                   | 33 | 198                           |

|                    | 7                   | 32 | 198                           |

|                    | 8                   | 31 | 248                           |