#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 16                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 20-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl020-e-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. This data sheet contains device-specific information for the PIC32MM0064GPL036 family devices.

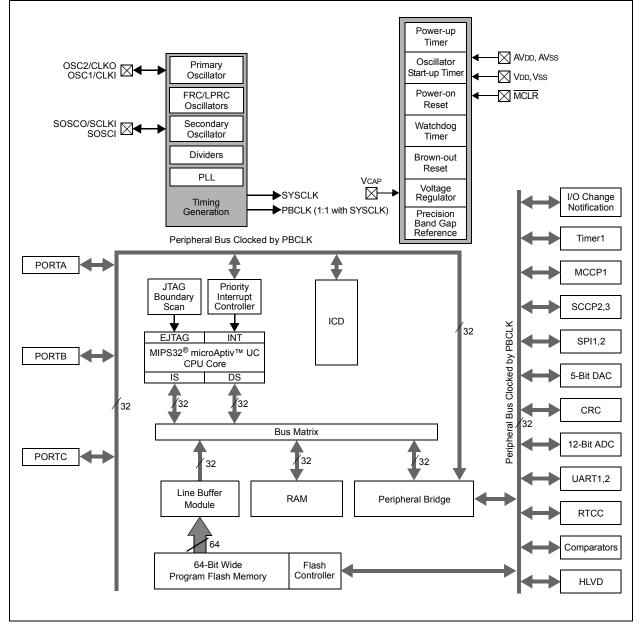

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0064GPL036 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

## FIGURE 1-1: PIC32MM0064GPL036 FAMILY BLOCK DIAGRAM

NOTES:

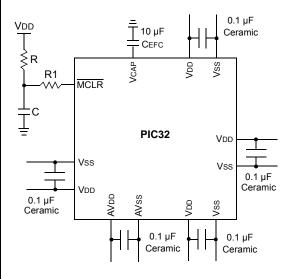

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

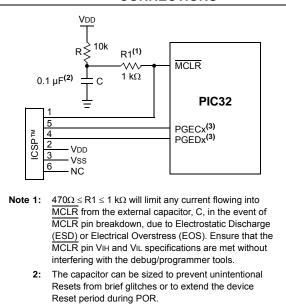

# 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS<sup>(1,2,3)</sup>

**<sup>3:</sup>** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

# 2.4 Capacitor on Internal Voltage Regulator (VCAP)

A low-ESR (<1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. The recommended value of the CEFC capacitor is 10  $\mu$ F. On the printed circuit board, it should be placed as close to the VCAP pin as possible. If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to this capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F.

# 4.0 MEMORY ORGANIZATION

PIC32MM microcontrollers provide 4 Gbytes of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The data memory can be made executable, allowing the CPU to execute code from data memory.

Key features include:

- 32-Bit Native Data Width

- Separate Boot Flash Memory (BFM) for Protected Code

- Robust Bus Exception Handling to Intercept Runaway Code

- Simple Memory Mapping with Fixed Mapping Translation (FMT) Unit

The PIC32MM0064GPL036 family devices implement two address spaces: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions. Physical addresses are used by peripherals, such as Flash controllers, that access memory independently of the CPU.

The virtual address space is divided into two segments of 512 Mbytes each, labeled kseg0 and kseg1. The Program Flash Memory (PFM) and Data RAM Memory (DRM) are accessible from either kseg0 or kseg1, while the Boot Flash Memory (BFM) and peripheral SFRs are accessible only from kseg1. The Fixed Mapping Translation (FMT) unit translates the memory segments into corresponding physical address regions. Figure 4-1 through Figure 4-3 illustrate the fixed mapping scheme, implemented by the PIC32MM0064GPL036 family core, between the virtual and physical address space.

The mapping of the memory segments depends on the CPU error level, set by the ERL bit in the CPU STATUS Register (SR). Error level is set (ERL = 1) by the CPU on a Reset, Soft Reset or NMI. In this mode, the CPU can access memory by the physical address. This mode is provided for compatibility with other MIPS<sup>®</sup> processor cores that use a TLB-based MMU. The C start-up code clears the ERL bit to zero, so that when application software starts up, it sees the proper virtual to physical memory mapping.

# 4.1 Alternate Configuration Bits Space

Every Configuration Word has an associated Alternate Word (designated by the letter A as the first letter in the name of the word). During device start-up, Primary Words are read, and if uncorrectable ECC errors are found, the BCFGERR (RCON<27>) flag is set and Alternate Words are used. If uncorrectable ECC errors are found in Primary and Alternate Words, the BCFGFAIL (RCON<26>) flag is set, and the default configuration is used. The Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. The Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6   | Bit<br>29/21/13/5      | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|---------------------|---------------------|------------------------|-------------------------|-------------------|-------------------|----------------------|------------------|

| 24.24        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 31:24        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 00.40        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 23:16        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 45-0         | R/W-0, HC           | R/W-0               | R-0, HS, HC            | R-0, HS, HC             | r-0               | U-0               | U-0                  | U-0              |

| 15:8         | WR <sup>(1,4)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1,2)</sup> | LVDERR <sup>(1,2)</sup> | —                 | _                 | _                    | —                |

| 7.0          | U-0                 | U-0                 | U-0                    | U-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 7:0          |                     | -                   |                        | —                       |                   | NVMOP             | <3:0> <sup>(3)</sup> |                  |

#### REGISTER 5-1: NVMCON: NVM PROGRAMMING CONTROL REGISTER

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit           |

|-------------------|----------------------------|---------------------------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'    |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared r = Reserved bit |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 WR: Write Control bit<sup>(1,4)</sup>

- This bit cannot be cleared and can be set only when WREN = 1, and the unlock sequence has been performed. 1 = Initiates a Flash operation

- 0 = Flash operation is complete or inactive

#### bit 14 WREN: Write Enable bit<sup>(1)</sup>

- 1 = Enables writes to the WR bit and disables writes to the NVMOP<3:0> bits

- 0 = Disables writes to the WR bit and enables writes to the NVMOP<3:0> bits

#### bit 13 WRERR: Write Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

- 1 = Program or erase sequence did not complete successfully

- 0 = Program or erase sequence completed normally

#### bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation. 1 = Low voltage is detected (possible data corruption if WRERR is set)

- 0 = Voltage level is acceptable for programming

- bit 11 Reserved: Maintain as '0'

- bit 10-4 Unimplemented: Read as '0'

- **Note 1:** These bits are only reset by a Power-on Reset (POR) and are not affected by other Reset sources.

- 2: These bits are cleared by setting NVMOP<3:0> = 0000 and initiating a Flash operation (i.e., WR).

- 3: NVMOP<3:0> bits are write-protected if the WREN bit is set.

- 4: Writes to the WR bit require an unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

# REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup> (CONTINUED)

- bit 12-10 IP1<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 9-8 IS1<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Unimplemented: Read as '0' bit 7-5 bit 4-2 IP0<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 1-0 ISO<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

# PIC32MM0064GPL036 FAMILY

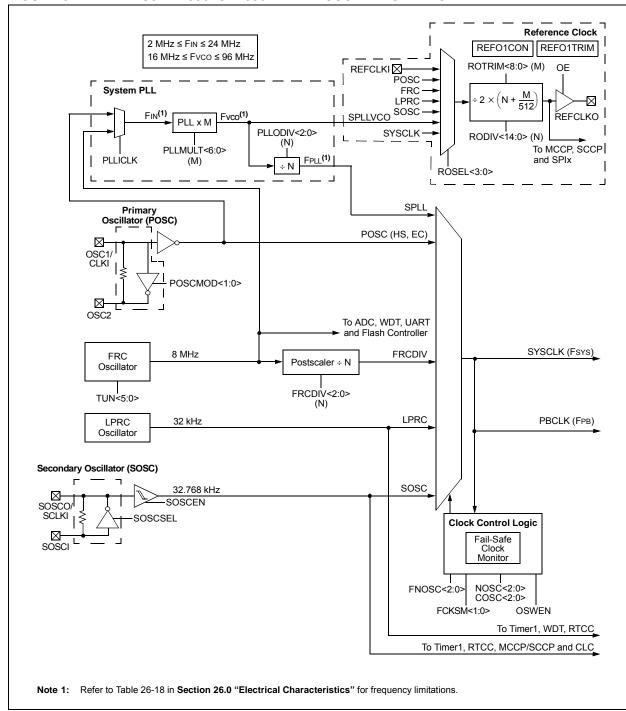

#### FIGURE 8-1: PIC32MM0064GPL036 FAMILY OSCILLATOR DIAGRAM

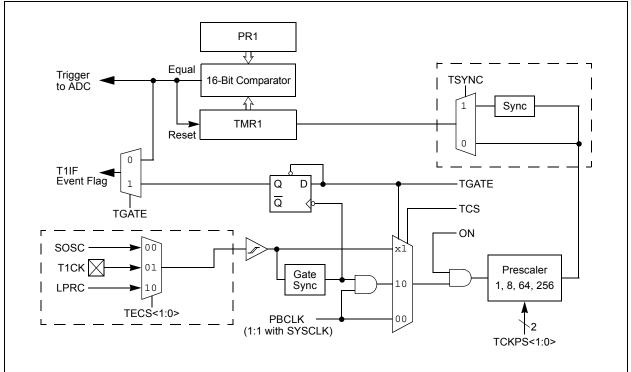

## 10.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0064GPL036 family devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can be clocked from different sources, such as the Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK), Secondary Oscillator (SOSC), T1CK pin or LPRC oscillator.

The following modes are supported by Timer1:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

The timer has a selectable clock prescaler and can operate in Sleep and Idle modes.

#### FIGURE 10-1: TIMER1 BLOCK DIAGRAM

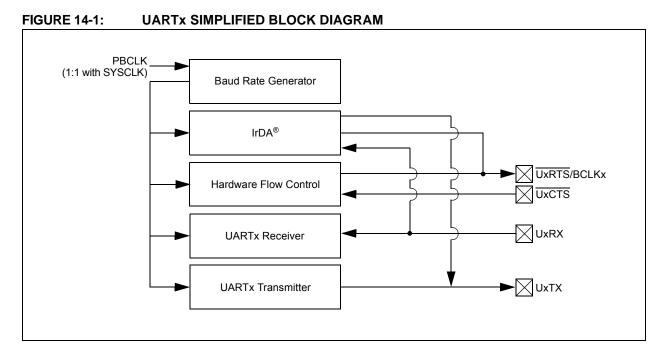

# 14.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21. "UART"** (DS61107) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

The UART module is one of the serial I/O modules available in the PIC32MM0064GPL036 family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN/J2602 and IrDA<sup>®</sup>. The module also supports the hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Auto-Baud Feature

- · Hardware Flow Control Option

- Fully Integrated Baud Rate Generator (BRG) with 16-Bit Prescaler

- Baud Rates Ranging from 47.7 bps to 6.26 Mbps at 25 MHz

- 8-Level Deep First-In-First-Out (FIFO) Transmit Data Buffer

- 8-Level Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for Interrupt Only on Address Detect (9th bit = 1)

- Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- LIN/J2602 Protocol Support

- IrDA Encoder and Decoder with 16x Baud Clock Output for External IrDA Encoder/Decoder Support

- · Supports Separate UART Baud Clock Input

- Ability to Continue to Run when a Receive Overflow (ROV) Condition Exists

- Ability to Run and Receive Data during Sleep mode

Figure 14-1 illustrates a simplified block diagram of the UART module.

© 2015-2016 Microchip Technology Inc.

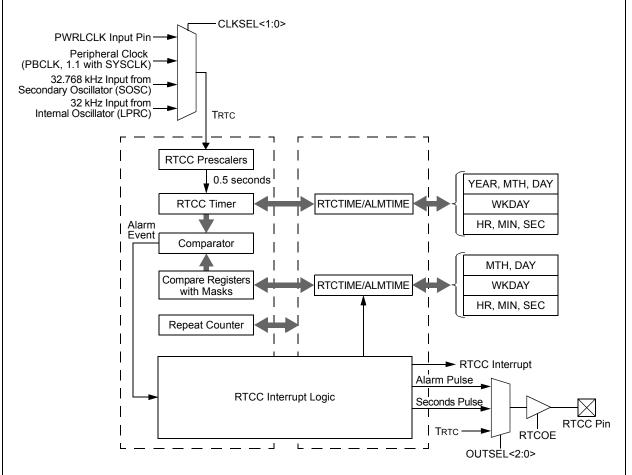

# 15.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 28. "RTCC with Timestamp" (DS60001362) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Lowpower optimization provides extended battery lifetime while keeping track of time. Key features of the RTCC module are:

- Time: Hours, Minutes and Seconds

- 24-Hour Format (military time)

- · Visibility of One-Half Second Period

- · Provides Calendar: Weekday, Date, Month and Year

- Alarm Intervals are Configurable for Half of a second, One Second, 10 Seconds, One Minute, 10 Minutes, One Hour, One Day, One Week, One Month and One Year

- Alarm Repeat with Decrementing Counter

- · Alarm with Indefinite Repeat: Chime

- Year Range: 2000 to 2099

- Leap Year Correction

- · BCD Format for Smaller Firmware Overhead

- Optimized for Long-Term Battery Operation

- · Fractional Second Synchronization

- User Calibration of the Clock Crystal Frequency with Auto-Adjust

- Uses External 32.768 kHz Crystal, 32 kHz Internal Oscillator, PWRLCLK Input Pin or Peripheral Clock

- Alarm Pulse, Seconds Clock or Internal Clock

Output on RTCC Pin

FIGURE 15-1: RTCC BLOCK DIAGRAM

|  | REGISTER 16-7: | AD1CHIT: ADC COMPARE HIT REGISTER |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| Bit Range                           | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24                               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                               | —                 | _                 |                   | _                 | -                 | -                 | _                | —                |

| 00.10                               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16                               | —                 | _                 |                   | -                 | _                 |                   | -                | —                |

| 45.0                                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8 — — CHH<13:8> <sup>(1,2)</sup> |                   |                   |                   |                   |                   |                   |                  |                  |

| 7:0                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0                                 |                   |                   |                   | CHH<7             | /:0>              |                   |                  |                  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13-0 CHH<13:0>: ADC Compare Hit bits<sup>(1,2)</sup>

If CM<1:0> = 11:

1 = ADC Result Buffer x has been written with data or a match has occurred

0 = ADC Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on ADC Result Channel n

0 = No match has occurred on ADC Result Channel n

Note 1: The CHH<13:11> bits are not implemented in 20-pin devices.

2: The CHH<13:12> bits are not implemented in 28-pin devices.

#### TABLE 18-1: CLC1 AND CLC2 REGISTER MAP

|                             | 1                               |           |       |       |          |       |       |       |          |       |       |       |          |       |       |       |          |       | 1          |

|-----------------------------|---------------------------------|-----------|-------|-------|----------|-------|-------|-------|----------|-------|-------|-------|----------|-------|-------|-------|----------|-------|------------|

| ess                         |                                 | 0         |       |       |          |       |       |       |          | E     | Bits  |       |          |       |       |       |          |       | 6          |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13    | 28/12 | 27/11 | 26/10 | 25/9     | 24/8  | 23/7  | 22/6  | 21/5     | 20/4  | 19/3  | 18/2  | 17/1     | 16/0  | All Resets |

| 0A80                        | CLC1CON                         | 32:16     | _     |       |          |       | —     |       | _        |       |       | —     |          | _     | G4POL | G3POL | G2POL    | G1POL | 0000       |

| 0A00                        | CLUTCON                         | 15:0      | ON    |       | _        |       | INTP  | INTN  |          | —     | LCOE  | LCOUT | LCPOL    |       |       | I     | MODE<2:0 | >     | 0000       |

| 0A90                        | CLC1SEL                         | 32:16     | _     | _     | _        | _     | _     | _     | _        | _     | _     | _     | _        | _     | _     | _     | _        | _     | 0000       |

| UA9U                        | GLUISEL                         | 15:0      | _     |       | DS4<2:0> |       | —     |       | DS3<2:0> |       |       |       | DS2<2:0> |       |       |       | DS1<2:0> |       | 0000       |

| 0AA0                        | CLC1GLS                         | 32:16     | G4D4T | G4D4N | G4D3T    | G4D3N | G4D2T | G4D2N | G4D1T    | G4D1N | G3D4T | G3D4N | G3D3T    | G3D3N | G3D2T | G3D2N | G3D1T    | G3D1N | 0000       |

| UAAU                        | CLUIGLS                         | 15:0      | G2D4T | G2D4N | G2D3T    | G2D3N | G2D2T | G2D2N | G2D1T    | G2D1N | G1D4T | G1D4N | G1D3T    | G1D3N | G1D2T | G1D2N | G1D1T    | G1D1N | 0000       |

| 0B00                        | CLC2CON                         | 32:16     | _     |       | _        |       | —     |       |          | —     |       | —     |          |       | G4POL | G3POL | G2POL    | G1POL | 0000       |

| 0600                        | CLC2CON                         | 15:0      | ON    |       | _        |       | INTP  | INTN  |          | —     | LCOE  | LCOUT | LCPOL    |       |       | I     | MODE<2:0 | >     | 0000       |

| 0B10                        | CLC2SEL                         | 32:16     | _     |       | _        |       | —     | _     | _        | —     |       | —     | -        | -     |       | —     | —        |       | 0000       |

| UBIU                        | CLC2SEL                         | 15:0      | _     |       | DS4<2:0> |       | —     |       | DS3<2:0> |       | _     |       | DS2<2:0> |       |       |       | DS1<2:0> |       | 0000       |

| 0B20                        | CLC2GLS                         | 32:16     | G4D4T | G4D4N | G4D3T    | G4D3N | G4D2T | G4D2N | G4D1T    | G4D1N | G3D4T | G3D4N | G3D3T    | G3D3N | G3D2T | G3D2N | G3D1T    | G3D1N | 0000       |

| 0620                        | ULUZGLS                         | 15:0      | G2D4T | G2D4N | G2D3T    | G2D3N | G2D2T | G2D2N | G2D1T    | G2D1N | G1D4T | G1D4N | G1D3T    | G1D3N | G1D2T | G1D2N | G1D1T    | G1D1N | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# 20.1 CDAC Control Registers

### TABLE 20-1: CDAC REGISTER MAP

| ess                       |                                 | a.        | Bits  |       |       |       |       |       |      |       |      |      |      | 6    |      |          |       |        |           |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|------|----------|-------|--------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2     | 17/1  | 16/0   | All Reset |

| 0000                      | DACICON                         | 31:16     | _     | —     | —     | _     | _     | —     | _    | -     | —    | —    | —    |      | D    | ACDAT<4: | 0>    |        | 0000      |

| 0980                      | DAC1CON                         | 15:0      | ON    |       | —     |       |       | _     |      | DACOE |      | _    | —    | _    | —    | _        | REFSE | L<1:0> | 0000      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | -                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 |                   |                   |                   |                   |                  |                  |

| 15.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 15:8         | ON                | _                 |                   |                   | _                 |                   | _                | DACOE            |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | REFSE            | EL<1:0>          |

#### REGISTER 20-1: DAC1CON: CDAC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

bit 20-16 **DACDAT<4:0>:** CDAC Voltage Reference Selection bits

11111 = (DACDAT<4:0> \* VREF+/32) or (DACDAT<4:0> \* AVDD/32) volts depending on the REFSEL<1:0> bits •

•

• 00000 = 0.0 volts

bit 15 **ON:** Voltage Reference Enable bit

- 1 = Voltage reference is enabled

- 0 = Voltage reference is disabled

#### bit 14-9 **Unimplemented:** Read as '0'

bit 8 DACOE: CDAC Voltage Reference Output Enable bit

- 1 = Voltage level is output on the CDAC1 pin

- 0 = Voltage level is disconnected from the CDAC1 pin

#### bit 7-2 Unimplemented: Read as '0'

- bit 1-0 REFSEL<1:0>: CDAC Voltage Reference Source Select bits

- 11 = Reference voltage is AVDD

- 10 = No reference is selected output is AVss

- 01 = Reference voltage is the VREF+ input pin voltage

- 00 = No reference is selected output is AVss

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (CONTINUED)

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin and is compared with 1.2V band gap) 1110 = VDD trip point is  $2.11V^{(1)}$

- 1101 = VDD trip point is  $2.21V^{(1)}$

- 1100 = VDD trip point is 2.30V<sup>(1)</sup>

- 1011 = VDD trip point is 2.40V<sup>(1)</sup>

- 1010 = VDD trip point is  $2.52V^{(1)}$

- 1001 = VDD trip point is 2.63V<sup>(1)</sup>

- $1000 = \text{VDD trip point is } 2.82\text{V}^{(1)}$

- 0111 = VDD trip point is  $2.92V^{(1)}$

- 0110 = VDD trip point is  $3.13V^{(1)}$

- 0101 = VDD trip point is  $3.44V^{(1)}$

- 0100-0000 = Reserved; do not use

- Note 1: The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in Section 26.0 "Electrical Characteristics" for minimum and maximum values.

| Parameter<br>No. | Typical <sup>(1)</sup> | Max  | Units                     | Operating<br>Temperature | Vdd  | Conditions                                       |  |  |  |  |

|------------------|------------------------|------|---------------------------|--------------------------|------|--------------------------------------------------|--|--|--|--|

| DC60             | 134                    | 198  | μA                        | -40°C                    |      |                                                  |  |  |  |  |

|                  | 136                    | 208  | μA                        | +25°C                    | 2.0V |                                                  |  |  |  |  |

|                  | 141                    | 217  | μA                        | +85°C                    |      | Sleep with active main voltage regulator         |  |  |  |  |

|                  | 139                    | 209  | μA                        | -40°C                    |      | (VREGS (PWRCON<0>) = 1,<br>RETEN (PWRCON<1>) =0) |  |  |  |  |

|                  | 141                    | 217  | μA                        | +25°C                    | 3.3V |                                                  |  |  |  |  |

|                  | 143                    | 231  | μA                        | +85°C                    |      |                                                  |  |  |  |  |

| DC61             | 4.3                    | 11.7 | μA                        | -40°C                    |      |                                                  |  |  |  |  |

|                  | 5.1                    | 15.6 | μA                        | +25°C                    | 2.0V | Sleep with main voltage regulator in             |  |  |  |  |

|                  | 11.4                   | 34.3 | μA                        | +85°C                    |      | Standby mode                                     |  |  |  |  |

|                  | 6.1                    | 16.8 | μA                        | -40°C                    |      | (VREGS (PWRCON<0>) = 0,                          |  |  |  |  |

|                  | 6.9 20.1 μA +25°C 3.3  | 3.3V | RETEN (PWRCON<1>) = $0$ ) |                          |      |                                                  |  |  |  |  |

|                  | 12.7                   | 36.0 | μA                        | +85°C                    |      |                                                  |  |  |  |  |

| DC62             | 2.3                    | _    | μA                        | -40°C                    |      | Sleep with enabled retention voltage             |  |  |  |  |

|                  | 2.7                    | _    | μA                        | +25°C                    | 2.0V |                                                  |  |  |  |  |

|                  | 5.2                    |      | μA                        | +85°C                    |      | regulator (VREGS (PWRCON<0>) = 1,                |  |  |  |  |

|                  | 2.3                    | -    | μA                        | -40°C                    |      | RETEN (PWRCON<1>) = 1,                           |  |  |  |  |

|                  | 2.7                    |      | μA                        | +25°C                    | 3.3V | RETVR(FPOR<2>)=0)                                |  |  |  |  |

|                  | 5.4                    | _    | μA                        | +85°C                    |      |                                                  |  |  |  |  |

| DC63             | 0.28                   | -    | μA                        | -40°C                    |      |                                                  |  |  |  |  |

|                  | 0.44                   |      | μA                        | +25°C                    | 2.0V | Sleep with enabled retention voltage             |  |  |  |  |

|                  | 2.52                   | _    | μA                        | +85°C                    |      | regulator (VREGS (PWRCON<0>) = 0,                |  |  |  |  |

|                  | 0.29                   | _    | μA                        | -40°C                    |      | <b>RETEN</b> (PWRCON<1>) = 1,                    |  |  |  |  |

|                  | 0.44                   | _    | μA                        | +25°C                    | 3.3V | RETVR(FPOR<2>)=0)                                |  |  |  |  |

|                  | 2.62                   | _    | μA                        | +85°C                    |      |                                                  |  |  |  |  |

## TABLE 26-6: POWER-DOWN CURRENT (IPD)<sup>(2)</sup>

**Note 1:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with:

- Oscillator is configured in FRC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 000)

- OSC2 is configured as I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- All I/O pins are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

## TABLE 26-8: I/O PIN INPUT SPECIFICATIONS

| Operati      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                       |                    |                    |            |        |                                                   |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|--------------------|------------|--------|---------------------------------------------------|--|--|--|--|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                                        | Min                | Typ <sup>(1)</sup> | Мах        | Units  | Conditions                                        |  |  |  |  |  |

|              | VIL                                                                                                                     | Input Low Voltage <sup>(2)</sup>                                      |                    |                    |            |        |                                                   |  |  |  |  |  |

| DI10         |                                                                                                                         | I/O Pins with ST Buffer                                               | Vss                | _                  | 0.2 Vdd    | V      |                                                   |  |  |  |  |  |

| DI15         |                                                                                                                         | MCLR                                                                  | Vss                |                    | 0.2 VDD    | V      |                                                   |  |  |  |  |  |

| DI16         |                                                                                                                         | OSC1/CLKI (XT mode)                                                   | Vss                | _                  | 0.2 Vdd    | V      |                                                   |  |  |  |  |  |

| DI17         |                                                                                                                         | OSC1/CLKI (HS mode)                                                   | Vss                | _                  | 0.2 Vdd    | V      |                                                   |  |  |  |  |  |

| DIOO         | Viн                                                                                                                     | Input High Voltage <sup>(2)</sup>                                     |                    |                    |            |        |                                                   |  |  |  |  |  |

| DI20         |                                                                                                                         | I/O Pins with ST Buffer:<br>without 5V Tolerance<br>with 5V Tolerance | 0.8 Vdd<br>0.8 Vdd |                    | VDD<br>5.5 | V<br>V |                                                   |  |  |  |  |  |

| DI25         |                                                                                                                         | MCLR                                                                  | 0.8 Vdd            | _                  | Vdd        | V      |                                                   |  |  |  |  |  |

| DI26         |                                                                                                                         | OSCI/CLKI (XT mode)                                                   | 0.7 Vdd            |                    | Vdd        | V      |                                                   |  |  |  |  |  |

| DI27         |                                                                                                                         | OSC1/CLKI (HS mode)                                                   | 0.7 Vdd            | _                  | Vdd        | V      |                                                   |  |  |  |  |  |

| DI30         | ICNPU                                                                                                                   | CNPUx Pull-up Current                                                 | _                  | 350                | _          | μA     | VPIN = 0V, VDD = 3.3V                             |  |  |  |  |  |

| DI30A        | ICNPD                                                                                                                   | CNPDx Pull-Down Current                                               | —                  | 300                | —          | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |  |  |

|              | lı∟                                                                                                                     | Input Leakage Current                                                 |                    |                    |            |        |                                                   |  |  |  |  |  |

| DI50         |                                                                                                                         | I/O Pins – 5V Tolerant                                                | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V,<br>pin at high-impedance |  |  |  |  |  |

| DI51         |                                                                                                                         | I/O Pins – Not 5V Tolerant                                            | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V,<br>pin at high-impedance |  |  |  |  |  |

| DI55         |                                                                                                                         | MCLR                                                                  | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |  |  |

| DI56         |                                                                                                                         | OSC1/CLKI                                                             | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Refer to Table 1-1 for I/O pin buffer types.

## TABLE 26-14: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                      |                           |             |                    |             |       |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------|--------------------|-------------|-------|

| Param<br>No.                                                                                 | Symbol               | Characteristic            | Min         | Тур <sup>(2)</sup> | Мах         | Units |

| D300                                                                                         | VIOFF                | Input Offset Voltage      | -20         |                    | 20          | mV    |

| D301                                                                                         | VICM                 | Input Common-Mode Voltage | AVss - 0.3V | —                  | AVDD + 0.3V | V     |

| D307                                                                                         | TRESP <sup>(1)</sup> | Response Time             |             | 150                | —           | ns    |

Note 1: Measured with one input at VDD/2 and the other transitioning from Vss to VDD.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-15: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> $2.0V < VDD < 3.6V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |        |                              |     |                    |     |       |

|-----------------------------------------------------------------------------------------------------------------|--------|------------------------------|-----|--------------------|-----|-------|

| Param<br>No.                                                                                                    | Symbol | Characteristic               | Min | Тур <sup>(2)</sup> | Max | Units |

| VRD310                                                                                                          | TSET   | Settling Time <sup>(1)</sup> | _   |                    | 10  | μs    |

| VRD311                                                                                                          | VRA    | Accuracy                     | -1  | _                  | 1   | LSb   |

| VRD312                                                                                                          | VRur   | Unit Resistor Value (R)      |     | 4.5                |     | kΩ    |

Note 1: Measures the interval while VRDAT<4:0> transitions from '11111' to '00000'.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | MILLIMETERS |          |      |  |  |

|------------------------|--------|-------------|----------|------|--|--|

| Dimension              | Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins         | N      |             | 40       |      |  |  |

| Pitch                  | е      |             | 0.40 BSC |      |  |  |

| Overall Height         | Α      | 0.45        | 0.50     | 0.55 |  |  |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3     | 0.127 REF   |          |      |  |  |

| Overall Width          | E      | 5.00 BSC    |          |      |  |  |

| Exposed Pad Width      | E2     | 3.60        | 3.70     | 3.80 |  |  |

| Overall Length         | D      | 5.00 BSC    |          |      |  |  |

| Exposed Pad Length     | D2     | 3.60        | 3.70     | 3.80 |  |  |

| Contact Width          | b      | 0.15        | 0.20     | 0.25 |  |  |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | K      | 0.20        | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2

## F

| Fail-Safe Clock Monitor (FSCM) | 65 |

|--------------------------------|----|

| Flash Program Memory           |    |

| Write Protection               |    |

## G

| 19 |

|----|

| 19 |

| 19 |

| 21 |

| 21 |

|    |

| 21 |

|    |

| 21 |

|    |

# н

| High/Low-Voltage Detect (HLVD)1    | 73 |

|------------------------------------|----|

| High/Low-Voltage Detect. See HLVD. |    |

## L

| I/O Ports                              | 77  |

|----------------------------------------|-----|

| Analog/Digital Port Pins Configuration | 78  |

| Open-Drain Configuration               | 78  |

| Parallel I/O (PIO)                     | 78  |

| Pull-up/Pull-Down Pins                 |     |

| Write/Read Timing                      | 78  |

| Input Change Notification (ICN)        | 78  |

| Instruction Set                        | 203 |

| Inter-IC Sound. See I <sup>2</sup> S.  |     |

| Internet Address                       |     |

## Μ

| MCCP/SCCP                                       |     |

|-------------------------------------------------|-----|

| Registers                                       |     |

| Memory Maps                                     |     |

| Devices with 16 Kbytes Program Memory           |     |

| Devices with 32 Kbytes Program Memory           |     |

| Devices with 64 Kbytes Program Memory           |     |

| Memory Organization                             |     |

| Alternate Configuration Bits Space              |     |

| Microchip Internet Web Site                     |     |

| MIPS32® microAptiv™ UC Core Configuration       |     |

| MPLAB Assembler, Linker, Librarian              |     |

| MPLAB ICD 3 In-Circuit Debugger                 | 201 |

| MPLAB PM3 Device Programmer                     | 201 |

| MPLAB REAL ICE In-Circuit Emulator System       | 201 |

| MPLAB X Integrated Development                  |     |

| Environment Software                            |     |

| MPLAB X SIM Software Simulator                  | 201 |

| MPLIB Object Librarian                          | 200 |

| MPLINK Object Linker                            | 200 |

| Multiply/Divide Unit Latencies and Repeat Rates |     |

| 0                                               |     |

| Oscillator Configuration                        | 65  |

| Р                                               |     |

| Package Thermal Resistance                      | 206 |

| Packaging                                       |     |

| Details                                         |     |

| Marking                                         |     |

| Peripheral Pin Select (PPS)                     |     |

| PICkit 3 In-Circuit Debugger/Programmer         |     |

Pinout Description ......14

| Power-Saving Features                     | 177 |

|-------------------------------------------|-----|

| Idle Mode                                 | 177 |

| Low-Power Brown-out Reset                 | 179 |

| On-Chip Voltage Regulator Low-Power Modes | 179 |

| Regulator Retention                       | 179 |

| Regulator Standby                         | 179 |

| Peripheral Module Disable                 |     |

| Sleep Mode                                |     |

| PPS                                       |     |

| Available Peripherals                     | 79  |

| Available Pins                            |     |

| Controlling                               |     |

| Controlling Configuration Changes         |     |

| Input Mapping                             |     |

| Input Pin Selection                       |     |

| Output Mapping                            |     |

| Output Pin Selection                      |     |

| Programming and Diagnostics               |     |

|                                           |     |

## R

| Real-Time Clock and Calendar (RTCC)          | 123 |

|----------------------------------------------|-----|

| Real-Time Clock and Calendar. See RTCC.      |     |

| Register Map                                 |     |

| ADC                                          | 135 |

| Alternate Configuration Words Summary        | 184 |

| Band Gap                                     | 195 |

| CDAC                                         |     |

| CLC1 and CLC2                                | 155 |

| Comparator 1 and 2                           | 164 |

| Configurations Words Summary                 |     |

| CRC                                          | 148 |

| Flash Controller                             | 38  |

| High/Low Voltage Detect                      | 174 |

| Interrupts                                   |     |

| MCCP/SCCP                                    |     |

| Oscillator Configuration                     | 67  |

| Peripheral Module Disable                    |     |

| Peripheral Pin Select                        |     |

| PORTA                                        | 82  |

| PORTB                                        |     |

| PORTC                                        | 84  |

| RAM Configuration, Device ID and System Lock | 192 |

| Reserved Registers                           |     |

| Resets                                       |     |

| RTCC                                         | 124 |

| SPI1 and SPI2                                |     |

| Timer1                                       |     |

| UART1 and UART2                              | 118 |

| UDID                                         | 197 |

| Watchdog Timer                               |     |

| Registers                                    |     |

| AD1CHIT (ADC Compare Hit)                    | 145 |

| AD1CHS (ADC Input Select)                    |     |

| AD1CON1 (ADC Control 1)                      |     |

| AD1CON2 (ADC Control 2)                      |     |

| AD1CON3 (ADC Control 3)                      |     |

| AD1CON5 (ADC Control 5)                      |     |

| AD1CSS (ADC Input Scan Select)               |     |

| ALMDATE (Alarm Date)                         |     |

| ANCFG (Band Gap Control)                     |     |

| CCPxCON1 (Capture/Compare/PWMx               |     |

| Control 1)                                   |     |

| CCPxCON2 (Capture/Compare/PWMx               |     |

| Control 2)                                   | 102 |

|                                              |     |