#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 16                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 4K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 20-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl020t-i-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MIPS<sup>®</sup> architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS architecture also defines a Multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. These configuration options and other system information is available by accessing the CP0 registers listed in Table 3-2.

## **REGISTER 6-1:** RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | SLEEP: Wake from Sleep Flag bit                                                          |

|-------|------------------------------------------------------------------------------------------|

|       | 1 = Device was in Sleep mode                                                             |

|       | 0 = Device was not in Sleep mode                                                         |

| bit 2 | IDLE: Wake from Idle Flag bit <sup>(2)</sup>                                             |

|       | <ol> <li>1 = Device was in Idle mode</li> <li>0 = Device was not in Idle mode</li> </ol> |

| bit 1 | BOR: Brown-out Reset Flag bit                                                            |

|       | 1 = Brown-out Reset has occurred                                                         |

|       | 0 = Brown-out Reset has not occurred                                                     |

| bit 0 | POR: Power-on Reset Flag bit                                                             |

|       | 1 = Power-on Reset has occurred                                                          |

|       | 0 = Power-on Reset has not occurred                                                      |

|       |                                                                                          |

- Note 1: User software must clear bits in this register to view the next detection.

- 2: The IDLE bit will also be set when the device wakes from Sleep mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | -                | —                      |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 23.10        | —                 | _                 | —                 | -                 | _                 | _                 | -                | —                      |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                      |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC                |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | _                | SWRST <sup>(1,2)</sup> |

REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:         HC = Hardware Clearable bit |                  |                                    |                    |  |  |  |  |

|---------------------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit                            | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR                           | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1,2)</sup>

- 1 = Enables Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: Once this bit is set, any read of the RSWRST register will cause a Reset to occur.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | _                 | —                 |                   | IP3<2:0>          |                   | IS3<1:0>         |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 | _                 | _                 |                   | IP2<2:0>          | IS2<1:0>          |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |  |

### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup>

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 =Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

### bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

### bit 23-21 Unimplemented: Read as '0'

- bit 20-18 **IP2<2:0>:** Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

## REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup> (CONTINUED)

- bit 12-10 IP1<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 9-8 IS1<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Unimplemented: Read as '0' bit 7-5 bit 4-2 IP0<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 1-0 ISO<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

## 9.9 I/O Ports Control Registers

## TABLE 9-4: PORTA REGISTER MAP

| ess                         |                                 | æ         |       |       |       |       |         |       |                          |      | Bits |      |      |      |      |             |       |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|-------|--------------------------|------|------|------|------|------|------|-------------|-------|------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10 | 25/9                     | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2        | 17/1  | 16/0 | All<br>Resets |

| 2600                        | ANSELA                          | 31:16     | _     | _     | _     | _     | —       | _     | —                        | —    | _    | —    | _    | —    | —    | —           | _     | —    | 0000          |

| 2000                        | / NOLL/                         | 15:0      | _     | —     | —     | —     | —       |       |                          | _    | _    | _    | _    | _    |      | ANSA        | <3:0> |      | 000F          |

| 2610                        | TRISA                           | 31:16     | _     | _     | —     | —     | —       |       | —                        | _    | _    | _    | _    | —    | —    | —           | _     | _    | 0000          |

| 2010                        | INIOA                           | 15:0      | _     | —     | —     | —     | —       | _     | TRISA9 <sup>(1,2)</sup>  | _    | —    | —    | _    |      |      | TRISA<4:0>  |       |      | 021F          |

| 2620                        | PORTA                           | 31:16     | _     | _     | —     | —     | —       |       | —                        | _    | _    | _    | _    | —    | —    | —           | _     | _    | 0000          |

| 2020                        | 1 OKIA                          | 15:0      | _     | —     | —     | —     | —       |       | RA9 <sup>(1,2)</sup>     | _    | _    | _    | _    |      |      | RA<4:0>     |       |      | xxxx          |

| 2630                        | LATA                            | 31:16     | _     | —     | —     | —     | —       |       |                          | _    | _    | _    | _    | —    | —    | —           | _     | _    | 0000          |

| 2000                        | DAIX                            | 15:0      | _     | —     | —     | —     | —       |       | LATA9 <sup>(1,2)</sup>   | _    | _    | _    | _    |      |      | LATA<4:0>   |       |      | 0000          |

| 2640                        | ODCA                            | 31:16     | _     | —     | —     | —     | —       |       |                          | _    | _    | _    | _    | —    | —    | _           | _     | _    | 0000          |

| 2040                        | 000/1                           | 15:0      | _     | —     | —     | —     | —       |       | ODCA9 <sup>(1,2)</sup>   | _    | _    | _    | _    |      | 1    | ODCA<4:0>   |       |      | 0000          |

| 2650                        | CNPUA                           | 31:16     | _     | —     | —     | —     | —       |       |                          | _    | _    | _    | _    | —    | —    | _           | _     | _    | 0000          |

| 2000                        |                                 | 15:0      | _     | —     | —     | —     | —       |       | CNPUA9 <sup>(1,2)</sup>  | _    | _    | _    | _    |      | (    | CNPUA<4:0>  |       |      | 0000          |

| 2660                        | CNPDA                           | 31:16     | —     | —     | —     | —     | —       | _     | —                        | —    | —    | —    | —    | —    | —    | —           | —     | —    | 0000          |

| 2000                        |                                 | 15:0      | —     | —     | —     | —     | —       | _     | CNPDA9 <sup>(1,2)</sup>  | —    | —    | —    | —    |      | 0    | CNPDA<4:0>  |       |      | 0000          |

| 2670                        | CNCONA                          | 31:16     | —     | —     | —     | —     | —       | _     | —                        | —    | —    | —    | —    | —    | —    | —           | —     | —    | 0000          |

| 2010                        |                                 | 15:0      | ON    | —     | —     | —     | CNSTYLE |       |                          | _    | _    | _    | _    | _    | —    | _           | _     | _    | 0000          |

| 2680                        | CNEN0A                          | 31:16     | —     | —     | —     | —     | —       | _     | —                        | —    | —    | —    | —    | —    | —    | —           | —     | —    | 0000          |

| 2000                        |                                 | 15:0      | —     | —     | —     | —     | —       | _     | CNIEA9 <sup>(1,2)</sup>  | —    | —    | —    | —    |      |      | CNIEA<4:0>  |       |      | 0000          |

| 2690                        | CNSTATA                         | 31:16     | —     | —     | —     | —     | —       | _     | —                        | —    | —    | —    | —    | —    | —    | —           | —     | —    | 0000          |

| 2000                        | 01101/11/1                      | 15:0      | —     | —     | —     | —     | —       | _     | CNSTATA9(1,2)            | —    | —    | —    | —    |      | С    | NSTATA<4:0  | >     |      | 0000          |

| 26A0                        | CNEN1A                          | 31:16     | —     | —     | —     | —     | —       | _     | —                        | —    | —    | —    | —    | —    | —    | —           | —     | —    | 0000          |

| 20/10                       | SNENIA                          | 15:0      | _     | —     | —     | —     | —       | _     | CNIE1A9 <sup>(1,2)</sup> | —    | _    | —    | _    |      | C    | CNIE1A<4:0> |       |      | 0000          |

| 26B0                        | CNFA                            | 31:16     | _     | —     | —     | —     | —       | _     |                          | —    | _    | —    | _    | —    | —    | —           | _     | —    | 0000          |

| 2000                        |                                 | 15:0      | _     | —     | —     | —     | —       | _     | CNFA9 <sup>(1,2)</sup>   |      | _    | —    | -    |      |      | CNFA<4:0>   |       |      | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## 12.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 12.1 Introduction

PIC32MM0064GPL036 family devices include three Capture/Compare/PWM/Timer (CCP) modules. These modules are similar to the multipurpose timer modules found on many other 32-bit microcontrollers. They also provide the functionality of the comparable input capture, output compare and general purpose timer peripherals found in all earlier PIC32 devices.

CCP modules can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

There are two different forms of the module, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM/Timer (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM/Timer (MCCPs) output modules can provide up to six outputs and an extended range of output control features, depending on the pin count of the particular device.

All modules (SCCP and MCCP) include these features:

- User-Selectable Clock Inputs, including System Clock and External Clock Input Pins

- Input Clock Prescaler for Time Base

- Output Postscaler for module Interrupt Events or Triggers

- Synchronization Output Signal for Coordinating other MCCP/SCCP modules with User-Configurable Alternate and Auxiliary Source Options

- Fully Asynchronous Operation in all modes and in Low-Power Operation

- Special Output Trigger for ADC Conversions

- 16-Bit and 32-Bit General Purpose Timer modes with Optional Gated Operation for Simple Time Measurements

- · Capture modes:

- Backward compatible with previous input capture peripherals of the PIC32 family

- 16-bit or 32-bit capture of time base on external event

- Up to four-level deep FIFO capture buffer

- Capture source input multiplexer

- Gated capture operation to reduce noise-induced false captures

- · Output Compare/PWM modes:

- Backward compatible with previous output compare peripherals of the PIC32 family

- Single Edge and Dual Edge Compare modes

- Center-Aligned Compare mode

- Variable Frequency Pulse mode

- External Input mode

MCCP modules also include these extended PWM features:

- Single Output Steerable mode

- Brush DC Motor (Forward and Reverse) modes

- Half-Bridge with Dead-Time Delay mode

- Push-Pull PWM mode

- Output Scan mode

- Auto-Shutdown with Programmable Source and Shutdown State

- Programmable Output Polarity

The SCCP and MCCP modules can be operated in only one of the three major modes (Capture, Compare or Timer) at any time. The other modes are not available unless the module is reconfigured.

A conceptual block diagram for the module is shown in Figure 12-1. All three modes use the time base generator and the common Timer register pair (CCPxTMR). Other shared hardware components, such as comparators and buffer registers, are activated and used as a particular mode requires. NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | -                 | _                 |                   | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |  |  |

| 15:8         | _                 | _                 |                   | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |  |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |  |  |  |  |

### **REGISTER 13-3:** SPIxSTAT: SPIx STATUS REGISTER

| Legend:           | C = Clearable bit                                   | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 FRMERR: SPIx Frame Error status bit 1 = Frame error is detected 0 = No frame error is detected This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPIx Activity Status bit

- 1 = SPIx peripheral is currently busy with some transactions

- 0 = SPIx peripheral is currently Idle

- bit 10-9 **Unimplemented:** Read as '0'

- bit 8 SPITUR: SPIx Transmit Underrun (TUR) bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When the SPIx Shift register is empty

- 0 = When the SPIx Shift register is not empty

- bit 6 SPIROV: SPIx Receive Overflow (ROV) Flag bit

- 1 = New data is completely received and discarded; the user software has not read the previous data in the SPIxBUF register

- 0 = No overflow has occurred

- This bit is set in hardware; it can only be cleared (= 0) in software.

- bit 5 SPIRBE: SPIx RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CPU Read Pointer (CRPTR) = SPI Write Pointer (SWPTR))

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

## TABLE 23-4: ALTERNATE CONFIGURATION WORDS SUMMARY

| sse                         |                  |           |        |        |         |         |       |            |       | E       | Bits    |         |          |        |         |          |          |        |

|-----------------------------|------------------|-----------|--------|--------|---------|---------|-------|------------|-------|---------|---------|---------|----------|--------|---------|----------|----------|--------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31\15  | 30/14  | 29/13   | 28/12   | 27/11 | 26/10      | 25/9  | 24/8    | 23/7    | 22/6    | 21/5     | 20/4   | 19/3    | 18/2     | 17/1     | 16/0   |

| 1740                        |                  | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1740                        | RESERVED         | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 4744                        |                  | 31:16     |        |        | •       |         |       |            |       | USERI   | D<15:0> |         |          | •      | •       |          |          |        |

| 1744                        | AFDEVOPT         | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | SOSCHP  | r-1      | r-1      | r-1    |

| 1748                        | AFICD            | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1748                        | AFICD            | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | ICS    | <1:0>   | JTAGEN   | r-1      | r-1    |

| 174C                        | AFPOR            | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1740                        | AFFUR            | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | LPBOREN | RETVR    | BOREN    | √<1:0> |

| 1750                        | AFWDT            | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        | AFWDI            | 15:0      | FWDTEN | RCLKSE | EL<1:0> |         | R     | WDTPS<4:0> |       |         | WINDIS  | FWDTWIN | ISZ<1:0> |        | SW      | DTPS<4:0 | >        |        |

| 1754                        | AFOSCSEL         | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 17.54                       | AI USUSEE        | 15:0      | FCKSM  | <1:0>  | r-1     | SOSCSEL | r-1   | OSCIOFNC   | POSCM | OD<1:0> | IESO    | SOSCEN  | r-1      | PLLSRC | r-1     | F        | NOSC<2:0 | >      |

| 1758                        | AFSEC            | 31:16     | CP     | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        |                  | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 175C                        | RESERVED         | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        | RESERVED         | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1760                        | RESERVED         | 31:16     | r-0    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1700                        | NEGERVED         | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1764                        | RESERVED         | 31:16     | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1704                        | NEGENVED         | 15:0      | r-1    | r-1    | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1     | r-1     | r-1      | r-1    | r-1     | r-1      | r-1      | r-1    |

**Legend:** r-0 = Reserved bit, must be programmed as '0'; r-1 = Reserved bit, must be programmed as '1'.

## 25.0 INSTRUCTION SET

The PIC32MM0064GPL036 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0064GPL036 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for |

|-------|--------------------------------------|

|       | Programmers Volume II-B: The         |

|       | microMIPS32™ Instruction Set" at     |

|       | www.imgtec.com for more information. |

## TABLE 26-10: I/O PIN OUTPUT SPECIFICATIONS

| Operatir     | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                  |      |      |       |                           |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|------|-------|---------------------------|--|--|--|--|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                   | Min  | Max  | Units | Conditions                |  |  |  |  |  |

|              | Vol                                                                                                                     | Output Low Voltage               |      |      |       |                           |  |  |  |  |  |

| DO10         |                                                                                                                         | I/O Ports                        | _    | 0.36 | V     | IOL = 6.0 mA, VDD = 3.6V  |  |  |  |  |  |

|              |                                                                                                                         |                                  | _    | 0.21 | V     | IOL = 3.0 mA, VDD = 2V    |  |  |  |  |  |

| DO16         |                                                                                                                         | RA3, RB8, RB9 and RB15 I/O Ports | —    | 0.16 | V     | IOL = 6.0 mA, VDD = 3.6V  |  |  |  |  |  |

|              |                                                                                                                         |                                  | _    | 0.12 | V     | IOL = 3.0 mA, VDD = 2V    |  |  |  |  |  |

|              | Voн                                                                                                                     | Output High Voltage              |      |      |       |                           |  |  |  |  |  |

| DO20         |                                                                                                                         | I/O Ports                        | 3.25 | —    | V     | IOH = -6.0 mA, VDD = 3.6V |  |  |  |  |  |

|              |                                                                                                                         |                                  | 1.4  | —    | V     | IOH = -3.0 mA, VDD = 2V   |  |  |  |  |  |

| DO26         |                                                                                                                         | RA3, RB8, RB9 and RB15 I/O Ports | 3.3  | —    | V     | IOH = -6.0 mA, VDD = 3.6V |  |  |  |  |  |

|              |                                                                                                                         |                                  | 1.55 | —    | V     | IOH = -3.0 mA, VDD = 2V   |  |  |  |  |  |

### TABLE 26-11: PROGRAM FLASH MEMORY SPECIFICATIONS

| Operat       | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                   |       |                    |      |       |                                                    |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|--------------------|------|-------|----------------------------------------------------|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                    | Min   | Typ <sup>(1)</sup> | Max  | Units | Conditions                                         |  |

| D130         | Eр                                                                                                                      | Cell Endurance                                    | 10000 | 20000              | _    | E/W   |                                                    |  |

| D131         | VICSP                                                                                                                   | VDD for In-Circuit Serial<br>Programming™ (ICSP™) | VBOR  | _                  | 3.6  | V     |                                                    |  |

| D132         | VRTSP                                                                                                                   | VDD for Run-Time<br>Self-Programming (RTSP)       | 2.0   | _                  | 3.6  | V     |                                                    |  |

| D133         | Tiw                                                                                                                     | Self-Timed Double-Word<br>Write Cycle Time        | 19.7  | 21.0               | 22.3 | μs    | 8 bytes, data is not all '1's                      |  |

|              |                                                                                                                         | Self-Timed Row Write<br>Cycle Time                | 1.3   | 1.4                | 1.5  | ms    | 256 bytes, data is not all '1's,<br>SYSCLK > 2 MHz |  |

| D133         | TIE                                                                                                                     | Self-Timed Page Erase<br>Time                     | 15.0  | 16.0               | 17.0 | ms    | 2048 bytes                                         |  |

| D134         | TRETD                                                                                                                   | Characteristic Retention                          | 20    | —                  | _    | Year  | If no other specifications are violated            |  |

| D136         | TCE                                                                                                                     | Self-Timed Chip Erase<br>Time                     | 16.0  | 17.0               | 18.0 | ms    |                                                    |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-14: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                      |                           |             |                    |             |       |  |  |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------|--------------------|-------------|-------|--|--|

| Param<br>No.                                                                                 | Symbol               | Characteristic            | Min         | Тур <sup>(2)</sup> | Мах         | Units |  |  |

| D300                                                                                         | VIOFF                | Input Offset Voltage      | -20         |                    | 20          | mV    |  |  |

| D301                                                                                         | VICM                 | Input Common-Mode Voltage | AVss - 0.3V | —                  | AVDD + 0.3V | V     |  |  |

| D307                                                                                         | TRESP <sup>(1)</sup> | Response Time             |             | 150                | —           | ns    |  |  |

Note 1: Measured with one input at VDD/2 and the other transitioning from Vss to VDD.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-15: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |        |                              |     |                    |     |       |  |

|----------------------------------------------------------------------------------------------|--------|------------------------------|-----|--------------------|-----|-------|--|

| Param<br>No.                                                                                 | Symbol | Characteristic               | Min | Тур <sup>(2)</sup> | Max | Units |  |

| VRD310                                                                                       | TSET   | Settling Time <sup>(1)</sup> | _   |                    | 10  | μs    |  |

| VRD311                                                                                       | VRA    | Accuracy                     | -1  | _                  | 1   | LSb   |  |

| VRD312                                                                                       | VRur   | Unit Resistor Value (R)      |     | 4.5                |     | kΩ    |  |

Note 1: Measures the interval while VRDAT<4:0> transitions from '11111' to '00000'.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## PIC32MM0064GPL036 FAMILY

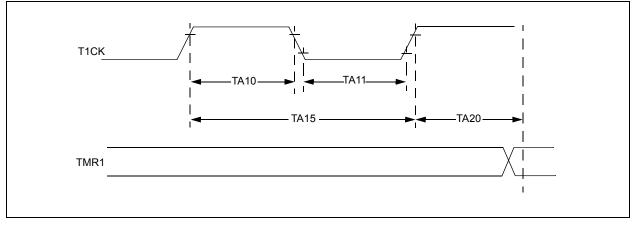

### FIGURE 26-5: TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

### TABLE 26-23: MCCP/SCCP TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |           |                                        |                        |     |     |        |                               |

|-------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------------------------|-----|-----|--------|-------------------------------|

| Param.<br>No.                                                                                                           | Symbol    | Characte                               | ristics <sup>(1)</sup> | Min | Max | Units  | Conditions                    |

| TA10                                                                                                                    | Тскн      | T1CK High Time                         | Synchronous            | 1   | _   | TPBCLK | Must also meet Parameter TA15 |

|                                                                                                                         |           |                                        | Asynchronous           | 10  | _   | ns     |                               |

| TA11                                                                                                                    | TCKL      | T1CK Low Time                          | Synchronous            | 1   | _   | TPBCLK | Must also meet Parameter TA15 |

|                                                                                                                         |           |                                        | Asynchronous           | 10  | _   | ns     |                               |

| TA15                                                                                                                    | Тскр      | T1CK Input                             | Synchronous            | 2   | _   | TPBCLK |                               |

|                                                                                                                         |           | Period                                 | Asynchronous           | 20  | _   | ns     |                               |

| TA20                                                                                                                    | TCKEXTMRL | Delay from Exterr<br>Edge to Timer Inc |                        |     | 3   | TPBCLK | Synchronous mode              |

**Note 1:** These parameters are characterized but not tested in manufacturing.

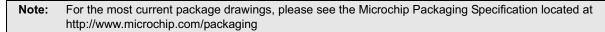

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

|                            | MILLIMETERS     |      |          |      |  |  |

|----------------------------|-----------------|------|----------|------|--|--|

| Dimension Limits           |                 | MIN  | NOM      | MAX  |  |  |

| Contact Pitch              | Contact Pitch E |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2              |      |          | 4.25 |  |  |

| Optional Center Pad Length | T2              |      |          | 4.25 |  |  |

| Contact Pad Spacing        |                 |      | 5.70     |      |  |  |

| Contact Pad Spacing        | C2              |      | 5.70     |      |  |  |

| Contact Pad Width (X28)    | X1              |      |          | 0.37 |  |  |

| Contact Pad Length (X28)   | Y1              |      |          | 1.00 |  |  |

| Distance Between Pads      |                 | 0.20 |          |      |  |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

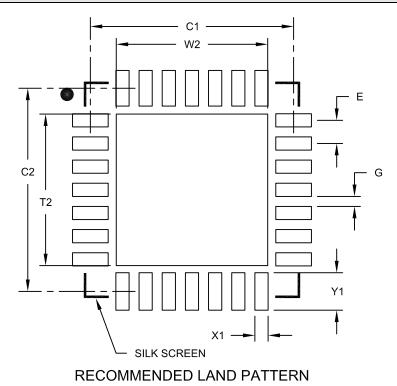

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### **RECOMMENDED LAND PATTERN**

|                                 | MILLIMETERS      |      |          |      |

|---------------------------------|------------------|------|----------|------|

| Dimension                       | Dimension Limits |      |          | MAX  |

| Contact Pitch                   | E                |      | 0.40 BSC |      |

| Center Pad Width                | X2               |      |          | 2.00 |

| Center Pad Length               | Y2               |      |          | 2.00 |

| Contact Pad Spacing             | C1               |      | 3.90     |      |

| Contact Pad Spacing             | C2               |      | 3.90     |      |

| Contact Pad Width (X28)         | X1               |      |          | 0.20 |

| Contact Pad Length (X28)        | Y1               |      |          | 0.85 |

| Contact Pad to Center Pad (X28) | G1               |      | 0.52     |      |

| Contact Pad to Pad (X24)        | G2               | 0.20 |          |      |

| Contact Pad to Corner Pad (X8)  | G3               | 0.20 |          |      |

| Corner Anchor Width (X4)        | X3               |      |          | 0.78 |

| Corner Anchor Length (X4)       | Y3               |      |          | 0.78 |

| Thermal Via Diameter            | V                |      | 0.30     |      |

| Thermal Via Pitch               | EV               |      | 1.00     |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2333-M6 Rev B

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

| To order or obtain info                                        | rmation, e.g., on pricing or delivery, refer to the factory or the listed sales o                | office.                                                                                                                                                             |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family<br>Key Feature Set _<br>Pin Count<br>Tape and Reel Flag |                                                                                                  | Example:<br>PIC32MM0064GPL036-I/M2:<br>PIC32 General Purpose Device<br>with MIPS32 <sup>®</sup> microAptiv™ UC<br>Core, 64-Kbyte Program Memory,<br>36-Pin Package. |

| Architecture                                                   | MM = MIPS32 <sup>®</sup> microAptiv™ UC CPU Core                                                 |                                                                                                                                                                     |

| Flash Memory Size                                              | 0016 = 16 Kbytes<br>0032 = 32 Kbytes<br>0064 = 64 Kbytes                                         |                                                                                                                                                                     |

| Family                                                         | GP = General Purpose Family                                                                      |                                                                                                                                                                     |

| Key Feature                                                    | L = Up to 25 MHz operating frequency with basic peripheral set of 2 UART<br>and 2 SPI modules    |                                                                                                                                                                     |

| Pin Count                                                      | 020 = 20-pin<br>028 = 28-pin<br>036 = 36/40-pin                                                  |                                                                                                                                                                     |

| Pattern                                                        | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample |                                                                                                                                                                     |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0653-2

## **Worldwide Sales and Service**

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15