#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (4x4)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028-e-m6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC microprocessor core in the PIC32MM0064GPL036 family devices contains several logic blocks, working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Power Management

- microMIPS Instructions Decoder

- Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous Multiply/ Divide Unit (MDU). The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port, and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid Stalls when executing instruction streams where data producing instructions are followed closely by consumers for their results

- Leading zero/one detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The microAptiv UC core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows the longrunning MDU operations to be partially masked by system Stalls and/or other Integer Unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, Result/Accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the rs operand. The second number ('16' of 32x16) represents the rt operand. The microAptiv UC core only checks the value of the rt operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back, 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU. Divide operations are implemented with a simple 1-bit-per-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (rs) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16-bit wide rs, 15 iterations are skipped, and for a 24-bit wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline Stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be re-issued), and latency (number of cycles until a result is available) for the microAptiv UC core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL (GPR destination)   | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

### TABLE 3-1: MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

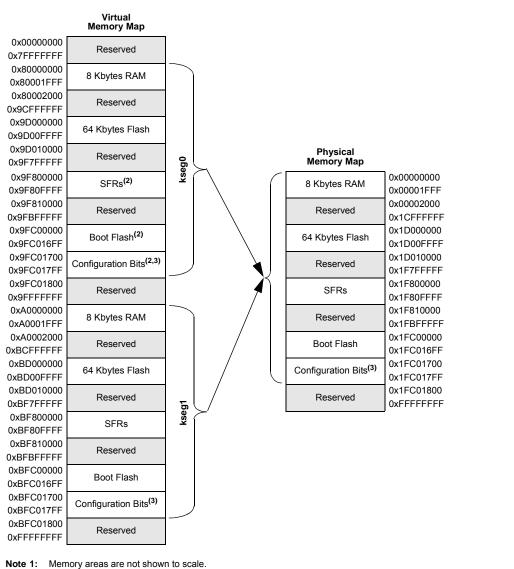

### FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 64 Kbytes OF PROGRAM MEMORY<sup>(1)</sup>

2: This region should be accessed from kseg1 space only.

3: Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768. Refer to Section 4.1 "Alternate Configuration Bits Space" for more information.

## 5.2 Flash Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |          |               |       |        |       |       |          | Bi      | ts        |      |      |      |        |      |        |      | 6          |

|-----------------------------|------------------------|-----------|----------|---------------|-------|--------|-------|-------|----------|---------|-----------|------|------|------|--------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15    | 30/14         | 29/13 | 28/12  | 27/11 | 26/10 | 25/9     | 24/8    | 23/7      | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1   | 16/0 | All Resets |

| 2380                        | NVMCON <sup>(1)</sup>  | 31:16     | _        |               |       |        |       |       |          | _       |           |      |      |      |        |      |        |      | 0000       |

| 2300                        | INVINCOIN.             | 15:0      | WR       | WREN          | WRERR | LVDERR | _     |       | _        | _       | —         |      | —    |      |        | NVMO | P<3:0> |      | 0000       |

| 2390                        | NVMKEY                 | 31:16     |          |               |       |        |       |       |          |         | /~31.0>   |      |      |      |        |      |        |      | 0000       |

| 2390                        |                        | 15:0      |          | NVMKEY<31:0>  |       |        |       |       |          |         |           |      |      |      |        |      |        |      |            |

| 23A0                        | NVMADDR <sup>(1)</sup> | 31:16     |          | NVMADDR<31:0> |       |        |       |       |          |         |           |      |      | 0000 |        |      |        |      |            |

| 2370                        | NUMADOR                | 15:0      |          |               |       |        |       |       |          | NVINADD | 1(51.02   |      |      |      |        |      |        |      | 0000       |

| 23B0                        | NVMDATA0               | 31:16     |          |               |       |        |       |       |          | NVMDAT  | A0<31·0>  |      |      |      |        |      |        |      | 0000       |

| 2020                        |                        | 15:0      |          |               |       |        |       |       |          |         | 10 10 1.0 |      |      |      |        |      |        |      | 0000       |

| 23C0                        | NVMDATA1               | 31:16     |          |               |       |        |       |       |          | NVMDAT  | A1<31·0>  |      |      |      |        |      |        |      | 0000       |

| 2000                        |                        | 15:0      |          |               |       |        |       |       |          |         | 11.01.0   |      |      |      |        |      |        |      | 0000       |

| 23D0                        | NVMSRCADDR             | 31:16     |          |               |       |        |       |       | N        | VMSRCA  | DDR<31:0  | >    |      |      |        |      |        |      | 0000       |

| 2020                        |                        | 15:0      |          |               |       |        |       |       |          |         |           |      |      |      |        |      |        |      | 0000       |

| 23E0                        | NVMPWP <sup>(1)</sup>  | 31:16     | PWPULOCK | —             | —     | —      | _     | —     | —        | —       |           |      |      | PWP< | 23:16> |      |        |      | 8000       |

| -0-0                        |                        | 15:0      |          |               |       |        |       |       |          | PWP<    | 15:0>     |      |      |      |        |      |        |      | 0000       |

| 23F0                        | NVMBWP <sup>(1)</sup>  | 31:16     | —        | —             | —     | —      | _     | _     |          | _       | _         | _    | —    | _    | _      | _    | _      | —    | 0000       |

| 2010                        |                        | 15:0      | BWPULOCK | _             | _     | —      | —     |       | BWP<2:0> |         | _         | _    | —    | _    | _      | _    | _      | —    | 8700       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

### REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|-------------------|-------------------|----------------------|------------------|

| 04-04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI6SS            | <3:0> <sup>(1)</sup> |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI4SS            | <3:0> <sup>(1)</sup> |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 15:8         |                   | PRI3SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI2SS            | <3:0>(1)             |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0               | U-0               | U-0                  | R/W-0            |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> |                   | —                 | —                 | —                    | SS0              |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

0001 = Interrupt with a priority level of 6 uses Shadow Set 1

0000 = Interrupt with a priority level of 6 uses Shadow Set 0

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(3)</sup>

- 111 and 110 = Reserved (selects internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV))

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (SOSC)

- 011 = Reserved

- 010 = Primary Oscillator (POSC) (XT, HS or EC)

- 001 = System PLL (SPLL)

- 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (FOSCSEL<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

- bit 6-5 Unimplemented: Read as '0'

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 CF: Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- bit 2 Unimplemented: Read as '0'

- bit 1 SOSCEN: Secondary Oscillator (SOSC) Enable bit<sup>(4)</sup>

- 1 = Enables Secondary Oscillator

- 0 = Disables Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit<sup>(2)</sup>

- 1 = Initiates an oscillator switch to a selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: The Reset value for this bit depends on the setting of the IESO (FOSCSEL<7>) Configuration bit. When IESO = 1, the Reset value is '1'. When IESO = 0, the Reset value is '0'.

- **3:** The Reset value for these bits matches the setting of the FNOSC<2:0> (FOSCSEL<2:0>) Configuration bits.

- 4: The Reset value for this bit matches the setting of the SOSCEN (FOSCSEL<6>) Configuration bit.

### TABLE 9-6: PORTC REGISTER MAP

| DS60001324B-pa |

|----------------|

| age            |

| 84             |

| ess                         |                                 | <b>n</b>  | Bits              |       |       |       |                        |       |        |                      |      |      |      |      |      |         |                       |                       |               |

|-----------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|------------------------|-------|--------|----------------------|------|------|------|------|------|---------|-----------------------|-----------------------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2    | 17/1                  | 16/0                  | All<br>Resets |

| 2800                        | ANSELC                          | 31:16     | _                 | _     | _     | _     | _                      | _     |        | _                    |      | _    | _    | -    | —    | —       |                       | _                     | 0000          |

|                             |                                 | 15:0      | —                 | _     | _     | _     |                        |       | _      | _                    | —    |      |      | _    | —    | _       | ANSC<                 | 1:0> <sup>(1,2)</sup> | 0003          |

| 2810                        | TRISC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| -0.0                        |                                 | 15:0      | _                 | —     | —     | _     | _                      | _     | TRISC  | :9:8> <b>(1,2)</b>   | —    | _    | —    | _    |      | TRISC<  | 3:0> <b>(1,2)</b>     |                       | 030F          |

| 2820                        | PORTC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2020                        | TORTO                           | 15:0      | —                 |       |       |       | _                      | _     | RC<9   | :8> <sup>(1,2)</sup> | —    | _    |      | _    |      | RC<3:   | 0> <b>(1,2)</b>       |                       | 0000          |

| 2830                        | LATC                            | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | —    | —    | —    | —    | —       | —                     | —                     | 0000          |

| 2000                        | EATO                            | 15:0      | —                 |       |       |       | _                      | _     | LATC<  | 9:8> <b>(1,2)</b>    | —    | _    |      | _    |      | LATC<   | 3:0> <b>(1,2)</b>     |                       | 0000          |

| 2840                        | ODCC                            | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                     | —                     | 0000          |

| 2040                        | 0000                            | 15:0      | —                 |       |       |       | _                      | _     | ODCC<  | :9:8> <b>(1,2)</b>   | —    | _    |      | _    |      | ODCC<   | 3:0> <b>(1,2)</b>     |                       | 0000          |

| 2850                        | CNPUC                           | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                     | —                     | 0000          |

| 2000                        |                                 | 15:0      | —                 | —     | —     | —     | _                      | _     | CNPUC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPUC   | <3:0>(1,2)            |                       | 0000          |

| 2860                        | CNPDC                           | 31:16     | —                 | —     | —     | _     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | -                     | —                     | 0000          |

| 2000                        | CINFDC                          | 15:0      | —                 | —     | —     | —     | —                      | —     | CNPDC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPDC<  | <3:0> <b>(1,2)</b>    |                       | 0000          |

| 2870                        | CNCONC                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2070                        | CINCOINC                        | 15:0      | ON <sup>(1)</sup> | —     | —     | —     | CNSTYLE <sup>(1)</sup> | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2880                        | CNEN0C                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2000                        | CINEINUC                        | 15:0      | _                 | —     | —     | —     | _                      | _     | CNIE0C | <9:8>(1,2)           | —    |      | _    |      |      | CNIE0C4 | <3:0>(1,2)            |                       | 0000          |

| 2890                        | CNSTATC -                       | 31:16     | _                 | —     | —     | —     | _                      | _     | _      | —                    | —    |      | _    |      | —    | _       |                       | _                     | 0000          |

| 2090                        | CINGTATE                        | 15:0      | —                 | —     | —     | —     | _                      | _     | CNSTAT | C<9:8>(1,2)          | —    | —    | —    |      |      | CNSTATO | <3:0>(1,2)            |                       | 0000          |

| 28A0                        | CNEN1C                          | 31:16     | _                 | -     | _     | -     | -                      | _     | _      | —                    | —    | _    | _    | I    | _    | -       |                       | _                     | 0000          |

| 2040                        | CINENTO                         | 15:0      | _                 | -     | -     | -     | —                      | _     | CNIE1C | <9:8>(1,2)           | _    |      |      |      |      | CNIE1C  | <3:0>(1,2)            |                       | 0000          |

| 28B0                        | CNFC                            | 31:16     | _                 | -     | —     | -     | —                      | _     | —      | —                    | —    |      |      |      | _    | —       | _                     | —                     | 0000          |

| 20BU                        | CINFC                           | 15:0      | _                 | —     | —     | —     | _                      | _     | CNFC<  | :9:8> <b>(1,2)</b>   | _    |      |      |      |      | CNFC<   | 3:0> <sup>(1,2)</sup> |                       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **Note 1:** Bits<15,11,9:8,3:0> are not implemented in 20-pin devices.

**2:** Bits<8,3:0> are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## TABLE 9-7: PERIPHERAL PIN SELECT REGISTER MAP

| ess                         |                                 |               | Bits  |       |       |              |              |                        |             |      |       |        |      |      |      |                        |         |      |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|--------------|--------------|------------------------|-------------|------|-------|--------|------|------|------|------------------------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12        | 27/11        | 26/10                  | 25/9        | 24/8 | 23/7  | 22/6   | 21/5 | 20/4 | 19/3 | 18/2                   | 17/1    | 16/0 | All Resets |

| 2480                        | RPCON                           | 31:16<br>15:0 | _     |       | _     |              | —<br>IOLOCK  |                        |             | _    |       | _      | _    |      |      |                        | _       | _    | 0000       |

| 24A0                        | RPINR1                          | 31:16<br>15:0 | _     |       |       | _            |              |                        |             |      |       |        |      |      | _    | —<br>INT4R<4:0>        |         | _    | 0000       |

| 24B0                        | RPINR2                          | 31:16<br>15:0 | _     | _     |       |              | ICM2R<4:0>   |                        |             |      | _     | _      | _    |      |      | ICM1R<4:0              | >       |      | 0000       |

| 24C0                        | RPINR3                          | 31:16         | _     | _     | _     |              | —            | _                      | _           |      | _     | _      | _    | _    |      |                        | _       | -    | 0000       |

| 24E0                        | RPINR5                          | 15:0<br>31:16 | _     | _     |       | —            | (            | —<br>DCFBR<4:0>        | >           | —    |       |        | _    |      |      | ICM3R<4:0<br>DCFAR<4:0 |         |      | 0000       |

| 24F0                        | RPINR6                          | 15:0<br>31:16 | _     |       |       |              |              |                        |             |      |       |        |      |      |      |                        |         |      | 0000       |

|                             |                                 | 15:0<br>31:16 |       |       |       |              |              | CKIBR<4:0<br>2CTSR<4:0 |             |      |       |        | _    |      |      | CKIAR<4:0<br>J2RXR<4:0 |         |      | 0000       |

| 2520                        | RPINR9                          | 15:0<br>31:16 | _     |       |       | _            | _            | _                      | _           | _    |       |        |      |      | —    | —<br>SS2INR<4:0        | -       | _    | 0000       |

| 2540                        | RPINR11                         | 15:0          | _     |       | —     |              | S            | CK2INR<4:0             | )>          |      | _     | _      | —    |      |      | SDI2R<4:0>             | >       |      | 0000       |

| 2550                        | RPINR12                         | 31:16<br>15:0 | _     |       |       | _            | - C          | LCINBR<4:0             | )><br>      | _    |       |        |      | —    | - C  | LCINAR<4:              | 0><br>— | _    | 0000       |

| 2590                        | RPOR0                           | 31:16<br>15:0 | _     |       |       | _            |              |                        | <3:0><<3:0> |      |       |        |      |      |      | RP3R<br>RP1R           |         |      | 0000       |

| 25A0                        | RPOR1                           | 31:16<br>15:0 | _     | _     |       | _            | - RP8R<3:0>  |                        |             |      |       |        | _    |      |      | RP7R<br>RP5R           |         |      | 0000       |

| 25B0                        | RPOR2                           | 31:16<br>15:0 | _     |       |       | _            | - RP12R<3:0> |                        |             |      |       |        |      |      |      | RP11F<br>RP9R          | R<3:0>  |      | 0000       |

| 25C0                        | RPOR3                           | 31:16         | _     | _     | _     | _            |              | RP16F                  | २<3:0>      |      | _     | _      | _    | _    |      | RP15F                  | R<3:0>  |      | 0000       |

| 25D0                        | RPOR4                           | 15:0<br>31:16 | _     |       |       |              |              |                        |             |      |       | 0000   |      |      |      |                        |         |      |            |

| 2020                        |                                 | 15:0          | _     | —     | —     | - RP18R<3:0> |              |                        |             |      | RP17F | R<3:0> |      | 0000 |      |                        |         |      |            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

### REGISTER 12-1: CCPxCON1: CAPTURE/COMPARE/PWMx CONTROL 1 REGISTER (CONTINUED)

- bit 7-6 **TMRPS<1:0>:** CCPx Time Base Prescale Select bits

- 11 = 1:64 prescaler

- 10 = 1:16 prescaler

- 01 = 1:4 prescaler

- 00 = 1:1 prescaler

- bit 5 **T32:** 32-Bit Time Base Select bit

- 1 = 32-bit time base for timer, single edge output compare or input capture function

- 0 = 16-bit time base for timer, single edge output compare or input capture function

- bit 4 CCSEL: Capture/Compare Mode Select bit

- 1 = Input Capture mode

- 0 = Output Compare/PWM or Timer mode (exact function is selected by the MOD<3:0> bits)

- bit 3-0 MOD<3:0>: CCPx Mode Select bits

- CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

- CCSEL = 0 (Output Compare modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Variable Frequency Pulse mode

- 0110 = Center-Aligned Pulse Compare mode, buffered

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode: Toggles output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode: Drives output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode: Drives output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode: Output functions are disabled

- **Note 1:** This control bit has no function in Input Capture modes.

- 2: This control bit has no function when TRIGEN = 0.

- 3: Values greater than '0011' will cause a FIFO buffer overflow in Input Capture mode.

### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 23    | MCLKSEL: Master Clock Enable bit <sup>(1)</sup>                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = REFCLKO is used by the Baud Rate Generator</li> <li>0 = PBCLK is used by the Baud Rate Generator (1:1 with SYSCLK)</li> </ul>                                                                                                         |

| bit 22-18 | Unimplemented: Read as '0'                                                                                                                                                                                                                         |

| bit 17    | SPIFE: SPIx Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                                                                |

|           | <ul> <li>1 = Frame synchronization pulse coincides with the first bit clock</li> <li>0 = Frame synchronization pulse precedes the first bit clock</li> </ul>                                                                                       |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(1)</sup>                                                                                                                                                                                                  |

|           | <ul><li>1 = Enhanced Buffer mode is enabled</li><li>0 = Enhanced Buffer mode is disabled</li></ul>                                                                                                                                                 |

| bit 15    | ON: SPIx Module On bit                                                                                                                                                                                                                             |

|           | <ul><li>1 = SPIx module is enabled</li><li>0 = SPIx module is disabled</li></ul>                                                                                                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                         |

| bit 13    | SIDL: SPIx Stop in Idle Mode bit                                                                                                                                                                                                                   |

|           | <ul> <li>1 = Discontinues operation when CPU enters Idle mode</li> <li>0 = Continues operation in Idle mode</li> </ul>                                                                                                                             |

| bit 12    | DISSDO: Disable SDOx Pin bit <sup>(4)</sup>                                                                                                                                                                                                        |

|           | <ul> <li>1 = SDOx pin is not used by the module; the pin is controlled by the associated PORTx register</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                                               |

| bit 11-10 | MODE<32,16>: 32/16/8-Bit Communication Select bits                                                                                                                                                                                                 |

|           | When AUDEN = 1:                                                                                                                                                                                                                                    |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |

|           | 1124-bit data, 32-bit FIFO, 32-bit channel/64-bit frame1032-bit data, 32-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                     |

|           | 0 1 16-bit data, 16-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                                                                          |

|           | 0 0 16-bit data, 16-bit FIFO, 16-bit channel/32-bit frame                                                                                                                                                                                          |

|           | When AUDEN = 0:                                                                                                                                                                                                                                    |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                                                                           |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                                                                   |

| bit 9     | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                                              |

|           | Master mode (MSTEN = 1):                                                                                                                                                                                                                           |

|           | <ul> <li>1 = Input data is sampled at the end of data output time</li> <li>0 = Input data is sampled at the middle of data output time</li> </ul>                                                                                                  |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                                                                            |

|           | SMP value is ignored when SPIx is used in Slave mode. The module always uses SMP = 0.                                                                                                                                                              |

| bit 8     | <b>CKE:</b> SPIx Clock Edge Select bit <sup>(2)</sup>                                                                                                                                                                                              |

|           | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)</li> </ul> |

| Note 1:   | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                            |

| 2:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                          |

| 3:        | When AUDEN = 1, the SPI/I <sup>2</sup> S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.                                                                                                        |

| 4:        | These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see <b>Section 9.8</b> " <b>Peripheral Pin Select (PPS)</b> " for more information).                                                     |

## 14.1 UART Control Registers

## TABLE 14-1: UART1 AND UART2 REGISTER MAP

| ess                         |                         |           |                                         |                                |        |         |          |       |                            | E          | lits        |         |       |            |             |       |        |        |            |

|-----------------------------|-------------------------|-----------|-----------------------------------------|--------------------------------|--------|---------|----------|-------|----------------------------|------------|-------------|---------|-------|------------|-------------|-------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name        | Bit Range | 31/15                                   | 30/14                          | 29/13  | 28/12   | 27/11    | 26/10 | 25/9                       | 24/8       | 23/7        | 22/6    | 21/5  | 20/4       | 19/3        | 18/2  | 17/1   | 16/0   | All Resets |

| 0600                        | U1MODE <sup>(1)</sup>   | 31:16     |                                         | _                              | —      | _       | _        | _     |                            | —          | SLPEN       | ACTIVE  | _     | _          | -           | CLKSE | L<1:0> | OVFDIS | 0000       |

| 0000                        | ONNODE                  | 15:0      | ON                                      |                                | SIDL   | IREN    | RTSMD    | —     | UEN≤                       | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV      | BRGH        | PDSE  | L<1:0> | STSEL  | 0000       |

| 0610                        | U1STA <sup>(1)</sup>    | 31:16     |                                         |                                |        | UART1 M | ASK<7:0> |       |                            |            |             |         |       | UART1 AD   | DR<7:0>     |       |        |        | 0000       |

| 0010                        | UISIA                   | 15:0      | UTXISE                                  | L<1:0>                         | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF                      | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE      | PERR        | FERR  | OERR   | URXDA  | 0110       |

| 0620                        | U1TXREG                 | 31:16     | —                                       |                                |        |         |          |       |                            |            | 0000        |         |       |            |             |       |        |        |            |

| 0020                        | UTIAREG                 | 15:0      | —                                       | TX8 UART1 Transmit Register 00 |        |         |          |       |                            |            | 0000        |         |       |            |             |       |        |        |            |

| 0630                        | U1RXREG                 | 31:16     | —                                       |                                | —      |         |          |       |                            | _          |             | —       | _     | _          |             | —     | _      | _      | 0000       |

| 0030                        | UIRAREG                 | 15:0      | —                                       |                                | —      |         |          |       |                            | RX8        |             |         | U.    | ART1 Rece  | ive Registe | er    |        |        | 0000       |

| 0640                        | U1BRG <sup>(1)</sup>    | 31:16     | —                                       |                                | _      |         |          |       |                            | _          |             | _       | _     | _          |             | _     | —      | _      | 0000       |

| 0040                        | UIBKG.                  | 15:0      |                                         |                                |        |         |          |       | Bau                        | d Rate Ger | nerator Pre | scaler  |       |            |             |       |        |        | 0000       |

| 0680                        | U2MODE <sup>(1)</sup>   | 31:16     | —                                       | -                              | —      | —       | —        | —     | _                          | —          | SLPEN       | ACTIVE  | —     | —          | _           | CLKSE | L<1:0> | OVFDIS | 0000       |

| 0000                        | UZIVIODE <sup>(</sup> ) | 15:0      | ON                                      |                                | SIDL   | IREN    | RTSMD    |       | UEN∙                       | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV      | BRGH        | PDSE  | L<1:0> | STSEL  | 0000       |

| 0690                        | U2STA <sup>(1)</sup>    | 31:16     |                                         |                                |        | UART2 M | ASK<7:0> |       |                            |            |             |         |       | UART2 AD   | DR<7:0>     |       |        |        | 0000       |

| 0090                        | 0231A.7                 | 15:0      | UTXISE                                  | EL<1:0>                        | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF                      | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE      | PERR        | FERR  | OERR   | URXDA  | 0110       |

| 06A0                        | U2TXREG                 | 31:16     | —                                       |                                | —      |         |          |       |                            | _          |             | —       | _     | _          |             | —     | _      | _      | 0000       |

| UOAU                        | UZIAREG                 | 15:0      | —                                       |                                | —      |         |          |       |                            | TX8        |             |         | U     | ART2 Trans | mit Registe | er    |        |        | 0000       |

| 06B0                        | U2RXREG                 | 31:16     |                                         |                                | —      |         |          | _     |                            |            |             |         |       |            |             | 0000  |        |        |            |

| 0080                        | UZKAREG                 | 15:0      |                                         |                                | —      |         |          | _     | RX8 UART2 Receive Register |            |             |         |       |            | 0000        |       |        |        |            |

| 06C0                        | U2BRG <sup>(1)</sup>    | 31:16     |                                         |                                | —      |         |          | _     |                            |            |             | —       | _     | _          |             | —     | _      |        | 0000       |

| 0000                        | UZBRG''                 | 15:0      | 15:0 Baud Rate Generator Prescaler 0000 |                                |        |         |          |       |                            |            | 0000        |         |       |            |             |       |        |        |            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## 15.1 RTCC Control Registers

## TABLE 15-1: RTCC REGISTER MAP

| ess                         |                                 | 6         |        |       |          |         |        |       |        |      | Bits    |      |            |        |        |      |          |         | ú          |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|---------|--------|-------|--------|------|---------|------|------------|--------|--------|------|----------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12   | 27/11  | 26/10 | 25/9   | 24/8 | 23/7    | 22/6 | 21/5       | 20/4   | 19/3   | 18/2 | 17/1     | 16/0    | All Resets |

| 0000                        | RTCCON1                         | 31:16     | ALRMEN | CHIME | -        |         |        | AMASK | <3:0>  |      |         |      |            | ALMRP  | T<7:0> |      |          |         | 0000       |

| 0000                        | RICCONT                         | 15:0      | ON     | _     | _        |         | WRLOCK | _     | —      |      | RTCOE   |      | OUTSEL<2:0 | >      | —      | —    | _        | —       | 0000       |

| 0010                        | RTCCON2                         | 31:16     |        |       |          |         |        |       |        | DI   | V<15:0> |      |            |        |        |      |          |         | 0000       |

| 0010                        | RICCONZ                         | 15:0      |        |       | FDIV<4:0 | )>      |        | —     | —      | _    | —       | —    | —          | —      | —      | —    | CLKSE    | L<1:0>  | 0000       |

| 0030                        | RTCSTAT                         | 31:16     | —      | —     | —        | _       | —      | _     | —      | _    | —       | _    | —          | —      | —      | —    | —        | —       | 0000       |

| 0000                        | RIGOLAI                         | 15:0      | —      | —     | —        | —       | —      | _     | —      | —    | —       | _    | ALMEVT     | —      | —      | SYNC | ALMSYNC  | HALFSEC | 0000       |

| 0040                        | RTCTIME                         | 31:16     | —      | F     | IRTEN<2  | :0>     |        | HRONE | =<3:0> |      | —       |      | MINTEN<2:0 | >      |        | MINC | NE<3:0>  | -       | xxxx       |

| 0040                        | RIGHME                          | 15:0      |        | SECTE | N<3:0>   |         |        | SECON | E<3:0> |      | —       | _    | _          |        | _      | —    | —        | —       | xx00       |

| 0050                        | RTCDATE                         | 31:16     |        | YRTE  | N<3:0>   |         |        | YRONE | <3:0>  |      | —       | _    | _          | MTHTEN |        | MTHC | DNE<3:0> |         | 0000       |

| 0000                        | RIODAIL                         | 15:0      | —      | —     | DAYT     | EN<1:0> |        | DAYON | E<3:0> |      | —       | _    | _          | —      | —      |      | WDAY<2:0 | >       | 0000       |

| 0060                        | ALMTIME                         | 31:16     | —      | F     | IRTEN<2  | :0>     |        | HRONE | =<3:0> |      | —       |      | MINTEN<2:0 | >      |        | MINC | NE<3:0>  | -       | xxxx       |

| 0000                        |                                 | 15:0      |        | SECTE | N<3:0>   |         |        | SECON | E<3:0> |      | —       | _    | —          | —      | —      | _    | _        | —       | xx00       |

| 0070                        | ALMDATE                         | 31:16     | _      | —     | _        | —       | —      | _     | —      | —    | —       | _    | —          | MTHTEN |        | MTHC | )NE<3:0> |         | 0000       |

| 0070                        |                                 | 15:0      | _      | —     | DAYTI    | EN<1:0> |        | DAYON | E<3:0> |      | —       | _    | _          | —      | —      |      | WDAY<2:0 | >       | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 24.24        | U-0                 | U-0                 |

| 31:24        | _                 | _                 | _                 |                   |                   | —                 | —                   | —                   |

| 23:16        | U-0                 | U-0                 |

| 23.10        | —                 | _                 | -                 | —                 | —                 | —                 | —                   | —                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON                | _                 | SIDL              |                   |                   |                   | FORM<2:0>           |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HSC          | R/W-0, HSC          |

| 7:0          |                   | SSRO              | C<3:0>            |                   | MODE12            | ASAM              | SAMP <sup>(1)</sup> | DONE <sup>(2)</sup> |

### REGISTER 16-1: AD1CON1: ADC CONTROL REGISTER 1

| Legend:           | HSC = Hardware Settable | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

|-------------------|-------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0'    |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit

- 1 = ADC module is operating

- 0 = ADC is off

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** ADC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- For 12-Bit Operation (MODE12 bit = 1):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dddd 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dddd 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 dddd dddd)

### For 10-Bit Operation (MODE12 bit = 0):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd ddd0 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- **Note 1:** The SAMP bit is cleared and cannot be written if the ADC is disabled (ON bit = 0).

- 2: The DONE bit is not persistent in Automatic modes; it is cleared by hardware at the beginning of the next sample.

## PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0                   | U-0              | U-0              |

| 31:24        | _                 |                   | CSS<30:28>        |                   | _                 | _                     | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                     | _                | _                |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 |                   |                   | CSS<13            | 3:8> <sup>(1,2)</sup> |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CSS               | <7:0>             |                       |                  |                  |

### REGISTER 16-6: AD1CSS: ADC INPUT SCAN SELECT REGISTER

### Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31 Unimplemented: Read as '0'

bit 30-28 CSS<30:28>: ADC Input Pin Scan Selection bits

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- bit 27-14 Unimplemented: Read as '0'

- bit 13-0 CSS<13:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- Note 1: The CSS<13:11> bits are not implemented in 20-pin devices.

- **2:** The CSS<13:12> bits are not implemented in 28-pin devices.

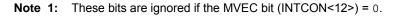

## 17.0 32-BIT PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 60. "32-Bit Programmable Cyclic Redundancy Check" (DS60001336) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. The 32-bit programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-Programmable CRC Polynomial Equation, up to 32 Bits

- Programmable Shift Direction (little or big-endian)

- Independent Data and Polynomial Lengths

- Configurable Interrupt Output

- Data FIFO

Figure 17-1 displays a simplified block diagram of the CRC generator.

### FIGURE 17-1: CRC BLOCK DIAGRAM

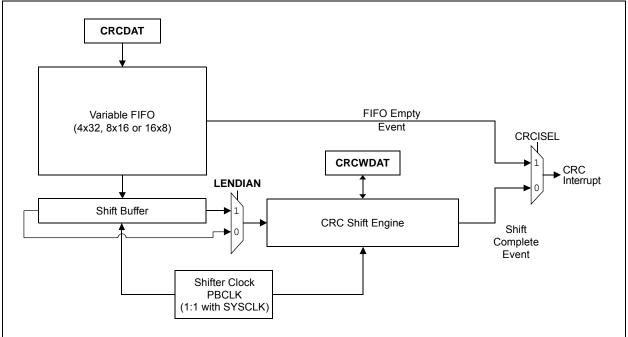

## **19.0 COMPARATOR**

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 19.** "Comparator" (DS60001110) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM. The comparator module provides two dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and VREF+). The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 19-1. Each comparator has its own control register, CMxCON (Register 19-2), for enabling and configuring its operation. The output and event status of two comparators is provided in the CMSTAT register (Register 19-1).

## PIC32MM0064GPL036 FAMILY

### REGISTER 19-2: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 AND 2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | -                 | _                 | _                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ON                | COE               | CPOL              | —                 | _                 | _                 | CEVT             | COUT             |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | EVPOI             | _<1:0>            | _                 | CREF              | _                 | _                 | CCH•             | <1:0>            |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit         |                    |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Comparator Enable bit

- 1 = Comparator is enabled

- 0 = Comparator is disabled

### bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is present on the CxOUT pin

- 0 = Comparator output is internal only

- bit 13 CPOL: Comparator Output Polarity Select bit

- 1 = Comparator output is inverted

- 0 = Comparator output is not inverted

### bit 12-10 Unimplemented: Read as '0'

- bit 9 CEVT: Comparator Event bit

- 1 = Comparator event that is defined by EVPOL<1:0> has occurred; subsequent triggers and interrupts are disabled until the bit is cleared

- 0 = Comparator event has not occurred

- bit 8 **COUT:** Comparator Output bit

$\frac{\text{When CPOL} = 0:}{1 = \text{VIN} + \text{VIN}-}$ 0 = VIN + VIN- $\frac{\text{When CPOL} = 1:}{1 = \text{VIN} + \text{VIN}-}$

0 = VIN + > VIN -

### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (CONTINUED)

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin and is compared with 1.2V band gap) 1110 = VDD trip point is  $2.11V^{(1)}$

- 1101 = VDD trip point is  $2.21V^{(1)}$

- 1100 = VDD trip point is 2.30V<sup>(1)</sup>

- 1011 = VDD trip point is 2.40V<sup>(1)</sup>

- 1010 = VDD trip point is  $2.52V^{(1)}$

- 1001 = VDD trip point is 2.63V<sup>(1)</sup>

- $1000 = \text{VDD trip point is } 2.82\text{V}^{(1)}$

- 0111 = VDD trip point is  $2.92V^{(1)}$

- $0110 = VDD trip point is <math>3.13V^{(1)}$

- 0101 = VDD trip point is  $3.44V^{(1)}$

- 0100-0000 = Reserved; do not use

- Note 1: The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in Section 26.0 "Electrical Characteristics" for minimum and maximum values.

## 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

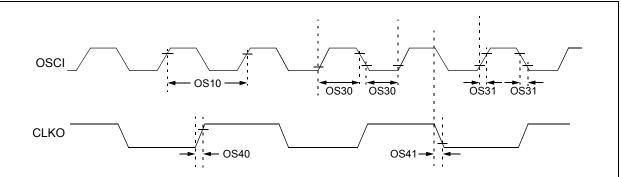

### FIGURE 26-3: EXTERNAL CLOCK TIMING

### TABLE 26-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| Operat       | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                               |                              |                    |                            |                                 |                                                                  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------|--------------------|----------------------------|---------------------------------|------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                | Min                          | Typ <sup>(1)</sup> | Мах                        | Units                           | Conditions                                                       |  |  |  |

| OS10         | Fosc                                                                                                                    | External CLKI Frequency                       | DC<br>2                      |                    | 25<br>12.5                 | MHz<br>MHz                      | EC<br>ECPLL <sup>(2)</sup>                                       |  |  |  |

|              |                                                                                                                         | Oscillator Frequency                          | 3.5<br>3.5<br>10<br>10<br>31 |                    | 10<br>10<br>25<br>25<br>50 | MHz<br>MHz<br>MHz<br>MHz<br>kHz | XT<br>XTPLL <sup>(2)</sup><br>HS<br>HSPLL <sup>(2)</sup><br>SOSC |  |  |  |

| OS30         | TosL,<br>TosH                                                                                                           | External Clock in (OSC1)<br>High or Low Time  | 0.45 x Tosc                  |                    | 0.55 x Tosc                | ns                              | EC                                                               |  |  |  |

| OS31         | TosR,<br>TosF                                                                                                           | External Clock in (OSC1)<br>Rise or Fall Time | _                            | _                  | 20                         | ns                              | EC                                                               |  |  |  |

| OS40         | TckR                                                                                                                    | CLKO Rise Time <sup>(3)</sup>                 |                              | 15                 | 20                         | ns                              |                                                                  |  |  |  |

| OS41         | TckF                                                                                                                    | CLKO Fall Time <sup>(3)</sup>                 |                              | 15                 | 20                         | ns                              |                                                                  |  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: PLL dividers and postscalers must be configured so that the system clock frequency does not exceed the maximum operating frequency.

3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

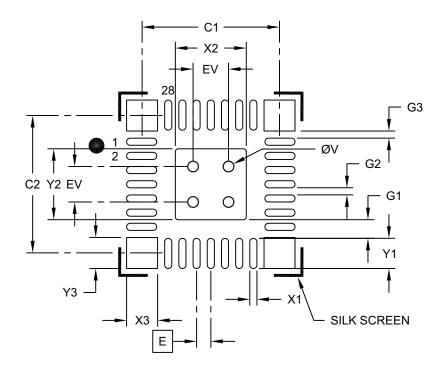

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### **RECOMMENDED LAND PATTERN**

|                                 | Ν   | <b>IILLIMETER</b> | S        |      |

|---------------------------------|-----|-------------------|----------|------|

| Dimension                       | MIN | NOM               | MAX      |      |

| Contact Pitch                   | E   |                   | 0.40 BSC |      |

| Center Pad Width                | X2  |                   |          | 2.00 |

| Center Pad Length               | Y2  |                   |          | 2.00 |

| Contact Pad Spacing             | C1  |                   | 3.90     |      |

| Contact Pad Spacing             | C2  |                   | 3.90     |      |

| Contact Pad Width (X28)         | X1  |                   |          | 0.20 |

| Contact Pad Length (X28)        | Y1  |                   |          | 0.85 |

| Contact Pad to Center Pad (X28) | G1  |                   | 0.52     |      |

| Contact Pad to Pad (X24)        | G2  | 0.20              |          |      |

| Contact Pad to Corner Pad (X8)  | G3  | 0.20              |          |      |

| Corner Anchor Width (X4)        | X3  |                   |          | 0.78 |