Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | <u>.</u>                                                                         |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |               |                | Pin                    | Number                        |                |                |             |                |                                            |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------------|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                                |

| AN0      | 19            | 2              | 27                     | 2                             | 33             | 36             | I           | ANA            | Analog-to-Digital Converter input channels |

| AN1      | 20            | 3              | 28                     | 3                             | 34             | 37             | Ι           | ANA            |                                            |

| AN2      | 1             | 4              | 1                      | 4                             | 35             | 38             | Ι           | ANA            |                                            |

| AN3      | 2             | 5              | 2                      | 5                             | 36             | 39             | Ι           | ANA            |                                            |

| AN4      | 3             | 6              | 3                      | 6                             | 1              | 1              | Ι           | ANA            |                                            |

| AN5      | 4             | 7              | 6                      | 9                             | 7              | 7              | Ι           | ANA            |                                            |

| AN6      | 5             | 8              | 7                      | 10                            | 8              | 8              | -           | ANA            |                                            |

| AN7      | 12            | 15             | 20                     | 23                            | 26             | 29             | -           | ANA            |                                            |

| AN8      | 13            | 16             | 21                     | 24                            | 27             | 30             | -           | ANA            |                                            |

| AN9      | 14            | 17             | 22                     | 25                            | 28             | 31             | Ι           | ANA            |                                            |

| AN10     | 15            | 18             | 23                     | 26                            | 29             | 32             | Ι           | ANA            | ]                                          |

| AN11     | _             | _              | 4                      | 7                             | 2              | 2              | Ι           | ANA            |                                            |

| AN12     | _             | —              | _                      | —                             | 3              | 3              | Ι           | ANA            | ]                                          |

| AN13     | I             | —              |                        | _                             | 4              | 4              | -           | ANA            | ]                                          |

| AVDD     | 17            | 20             | 25                     | 28                            | 31             | 34             | Р           | _              | Analog modules power supply                |

| AVss     | 16            | 19             | 24                     | 27                            | 30             | 33             | Р           |                | Analog modules ground                      |

| C1INA    | 5             | 8              | 4                      | 7                             | 2              | 2              | I           | ANA            | Comparator 1 Input A                       |

| C1INB    | 4             | 7              | 3                      | 6                             | 1              | 1              | -           | ANA            | Comparator 1 Input B                       |

| C1INC    | 2             | 5              | 2                      | 5                             | 36             | 39             | Ι           | ANA            | Comparator 1 Input C                       |

| C1IND    | 1             | 4              | 1                      | 4                             | 35             | 38             | Ι           | ANA            | Comparator 1 Input D                       |

| C1OUT    | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | Comparator 1 output                        |

| C2INA    | 2             | 5              | 2                      | 5                             | 36             | 39             | I           | ANA            | Comparator 2 Input A                       |

| C2INB    | 1             | 4              | 1                      | 4                             | 35             | 38             | I           | ANA            | Comparator 2 Input B                       |

| C2OUT    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | Comparator 2 output                        |

| CLKI     | 4             | 7              | 6                      | 9                             | 7              | 7              | I           | ST             | External Clock input (EC mode)             |

| CLKO     | 5             | 8              | 7                      | 10                            | 8              | 8              | 0           | DIG            | System clock output                        |

| CDAC1    | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | ANA            | Digital-to-Analog Converter output         |

| FSYNC1   | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | SPI1 frame signal input or output          |

| INT0     | 15            | 18             | 23                     | 26                            | 29             | 32             | I           | ST             | External Interrupt 0                       |

| INT1     | 14            | 17             | 22                     | 25                            | 28             | 31             | I           | ST             | External Interrupt 1                       |

| INT2     | 10            | 13             | 15                     | 18                            | 19             | 20             | I           | ST             | External Interrupt 2                       |

| INT3     | 19            | 2              | 27                     | 2                             | 33             | 36             | I           | ST             | External Interrupt 3                       |

| LVDIN    | 12            | 15             | 20                     | 23                            | 26             | 29             | I           | ANA            | High/Low-Voltage Detect input              |

| MCLR     | 18            | 1              | 26                     | 1                             | 32             | 35             | 1           | ST             | Master Clear (device Reset)                |

| OCM1A    | 9             | 12             | 14                     | 17                            | 18             | 18             | 0           | DIG            | MCCP1 Output A                             |

| OCM1B    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | MCCP1 Output B                             |

| OCM1C    | 4             | 7              | 6                      | 9                             | 7              | 7              | 0           | DIG            | MCCP1 Output C                             |

| OCM1D    | 5             | 8              | 7                      | 10                            | 8              | 8              | 0           | DIG            | MCCP1 Output D                             |

| OCM1E    | 19            | 2              | 27                     | 2                             | 33             | 36             | 0           | DIG            | MCCP1 Output E                             |

| OCM1F    | 20            | 3              | 28                     | 3                             | 34             | 37             | 0           | DIG            | MCCP1 Output F                             |

| OSC1     | 4             | 7              | 6                      | 9                             | 7              | 7              | _           |                | Primary Oscillator crystal                 |

| OSC2     | 5             | 8              | 7                      | 10                            | 8              | 8              | _           | _              | Primary Oscillator crystal                 |

#### TABLE 1-1: PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION

NOTES:

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> In-Circuit Emulator.

For more information on MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available from the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) (DS51765)

- "Development Tools Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector, and the JTAG pins on the device, as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

## 2.7 External Oscillator Pins

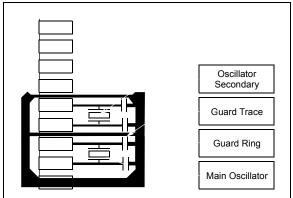

The PIC32MM0064GPL036 family has options for two external oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## 2.8 Unused I/Os

To minimize power consumption, unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic low or logic high state.

Alternatively, inputs can be reserved by ensuring the pin is always configured as an input and externally connecting the pin to Vss or VDD. A current-limiting resistor may be used to create this connection if there is any risk of inadvertently configuring the pin as an output with the logic output state opposite of the chosen power rail.

<sup>© 2015-2016</sup> Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | PLLODIV<2:0>      |                  |                  |  |  |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-1            |  |  |

| 23:16        | _                 | PLLMULT<6:0>      |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 7:0          | R/W-y             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | PLLICLK           | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |

## **REGISTER 8-2:** SPLLCON: SYSTEM PLL CONTROL REGISTER<sup>(1)</sup>

| Legend:           | y = Values set from Configuration bits on Reset     |                      |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-27 Unimplemented: Read as '0'

bit 26-24 **PLLODIV<2:0>:** System PLL Output Clock Divider bits

- 111 = PLL divide-by-256 110 = PLL divide-by-64 101 = PLL divide-by-32 100 = PLL divide-by-16 011 = PLL divide-by-8 010 = PLL divide-by-4 001 = PLL divide-by-2 000 = PLL divide-by-1 (default setting)

- bit 23 Unimplemented: Read as '0'

- bit 22-16 PLLMULT<6:0>: System PLL Multiplier bits

- 111111-0000111 = Reserved 0000110 = 24x 0000101 = 12x 0000100 = 8x 0000011 = 6x 0000010 = 4x 0000001 = 3x (default setting) 0000000 = 2x

- bit 15-8 Unimplemented: Read as '0'

- bit 7 PLLICLK: System PLL Input Clock Source bit

1 = FRC is selected as the input to the system PLL (not divided)

0 = POSC is selected as the input to the system PLL

The POR default value is specified by the PLLSRC Configuration bit in the FOSCSEL register. Refer to Register 23-9 in Section 23.0 "Special Features" for more information.

- bit 6-0 Unimplemented: Read as '0'

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details. All bits in this register must be modified only if the PLL is not used.

| Bit<br>Range        | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|-------------------|------------------|-----------------------|

| 21.24               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0                 |

| 31:24 — RODIV<14:8> |                   |                   |                   |                   |                           |                   |                  |                       |

| 00.40               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0                 |

| 23:16               |                   |                   |                   | RODIV             | <7:0>                     |                   |                  |                       |

| 45.0                | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0                     | U-0               | R/W-0, HC        | R-0, HS, HC           |

| 15:8                | ON <sup>(1)</sup> | —                 | SIDL              | OE                | RSLP <sup>(2)</sup>       | —                 | DIVSWEN          | ACTIVE <sup>(1)</sup> |

| 7.0                 | U-0               | U-0               | U-0               | U-0               | R/W-0                     | R/W-0             | R/W-0            | R/W-0                 |

| 7:0                 | _                 | —                 | _                 | —                 | ROSEL<3:0> <sup>(3)</sup> |                   |                  |                       |

#### REGISTER 8-3: REFO1CON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit         |                    |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31 Unimplemented: Read as '0'

- bit 30-16 RODIV<14:0> Reference Clock Divider bits

- The value selects the reference clock divider bits (see Figure 8-1 for details). A value of '0' selects no divider.

- bit 15 **ON:** Reference Oscillator Output Enable bit<sup>(1)</sup>

- 1 = Reference oscillator module is enabled 0 = Reference oscillator module is disabled

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on the REFCLKO pin

- 0 = Reference clock is not driven out on the REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference oscillator module output continues to run in Sleep

- 0 = Reference oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 **DIVSWEN:** Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- ACTIVE: Reference Clock Request Status bit<sup>(1)</sup>

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

bit 8

- Note 1: Do not write to this register when the ON bit is not equal to the ACTIVE bit.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000.

- 3: The ROSEL<3:0> bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

## 9.1 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (Clear), SET (Set) and INV (Invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

## 9.2 Parallel I/O (PIO) Ports

All port pins have 14 registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. The LATx register controls the pin level when it is configured as an output. Reads from the PORTx register read the port pins, while writes to the port pins write the latch, LATx. The I/Os state reflected in the PORTx register is synchronized with the system clock and delayed by 3 system clock cycles.

## 9.3 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, the port pins can also be individually configured for either digital or open-drain outputs. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired 5V tolerant pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 9.4 Configuring Analog and Digital Port Pins

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications. The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared. The ANSELx register has a default value of 0xFFFF. Therefore, all pins that share analog functions are analog (not digital) by default. If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is used by an analog peripheral, such as the ADC or comparator module.

## 9.5 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 9.6 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC32MM devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 9-1.

| <b>TABLE 9-1</b> : | CHANGE NOTIFICATION |  |  |  |

|--------------------|---------------------|--|--|--|

|                    | EVENT OPTIONS       |  |  |  |

| CNSTYLE Bit<br>(CNCONx<11>) | <u> </u>           | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

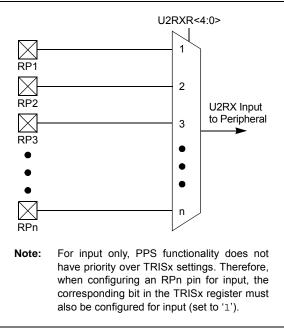

#### 9.8.4 INPUT MAPPING

The RPINRx registers are used to assign the peripheral input to the required remappable pin, RPn (refer to the peripheral inputs and the corresponding RPINRx registers listed in Table 9-2). Each RPINRx register contains sets of 5-bit fields. Programming these bits with the remappable pin number will connect the peripheral to this RPn pin. Example 9-1 and Figure 9-2 illustrate the remappable pin selection for the U2RX input.

#### EXAMPLE 9-1: UART2 RX INPUT ASSIGNMENT TO RP9/RB14 PIN

| RPINR9bits.U2RXR | = | 9; | 11 | connect UART2 RX |

|------------------|---|----|----|------------------|

|                  |   |    | // | input to RP9 pin |

## FIGURE 9-2: REMA

### REMAPPABLE INPUT EXAMPLE FOR U2RX

#### TABLE 9-2: INPUT PIN SELECTION

| Input Name              | Function Name | Register | Function Bits |

|-------------------------|---------------|----------|---------------|

| External Interrupt 4    | INT4          | RPINR1   | INT4R<4:0>    |

| MCCP1 Input Capture     | ICM1          | RPINR2   | ICM1R<4:0>    |

| SCCP2 Input Capture     | ICM2          | RPINR2   | ICM2R<4:0>    |

| SCCP3 Input Capture     | ICM3          | RPINR3   | ICM3R<4:0>    |

| Output Compare Fault A  | OCFA          | RPINR5   | OCFAR<4:0>    |

| Output Compare Fault B  | OCFB          | RPINR5   | OCFBR<4:0>    |

| CCP Clock Input A       | TCKIA         | RPINR6   | TCKIAR<4:0>   |

| CCP Clock Input B       | TCKIB         | RPINR6   | TCKIBR<4:0>   |

| UART2 Receive           | U2RX          | RPINR9   | U2RXR<4:0>    |

| UART2 Clear-to-Send     | U2CTS         | RPINR9   | U2CTSR<4:0>   |

| SPI2 Data Input         | SDI2          | RPINR11  | SDI2R<4:0>    |

| SPI2 Clock Input        | SCK2IN        | RPINR11  | SCK2INR<4:0>  |

| SPI2 Slave Select Input | SS2IN         | RPINR11  | SS2INR<4:0>   |

| CLC Input A             | CLCINA        | RPINR12  | CLCINAR<4:0>  |

| CLC Input B             | CLCINB        | RPINR12  | CLCINBR<4:0>  |

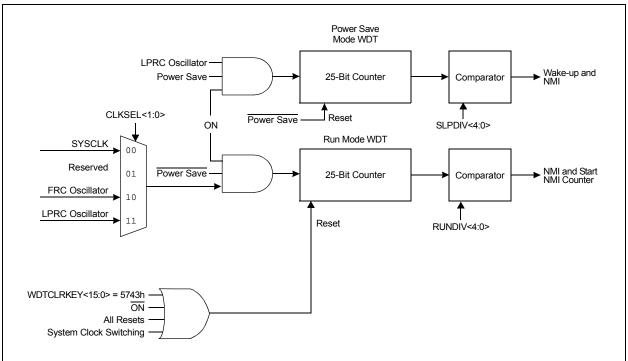

## 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

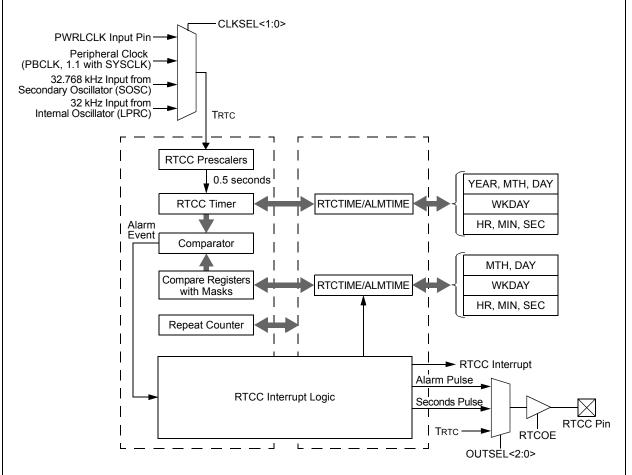

## 15.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 28. "RTCC with Timestamp" (DS60001362) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Lowpower optimization provides extended battery lifetime while keeping track of time. Key features of the RTCC module are:

- Time: Hours, Minutes and Seconds

- 24-Hour Format (military time)

- · Visibility of One-Half Second Period

- · Provides Calendar: Weekday, Date, Month and Year

- Alarm Intervals are Configurable for Half of a second, One Second, 10 Seconds, One Minute, 10 Minutes, One Hour, One Day, One Week, One Month and One Year

- Alarm Repeat with Decrementing Counter

- · Alarm with Indefinite Repeat: Chime

- Year Range: 2000 to 2099

- Leap Year Correction

- · BCD Format for Smaller Firmware Overhead

- Optimized for Long-Term Battery Operation

- · Fractional Second Synchronization

- User Calibration of the Clock Crystal Frequency with Auto-Adjust

- Uses External 32.768 kHz Crystal, 32 kHz Internal Oscillator, PWRLCLK Input Pin or Peripheral Clock

- Alarm Pulse, Seconds Clock or Internal Clock

Output on RTCC Pin

FIGURE 15-1: RTCC BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | _                   |                   |                   |                   |                   | —                 | —                | _                    |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | _                   | _                 |                   | _                 | —                 | —                 | —                | —                    |

| 45.0         | R/W-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0                |

| 15:8         | ASEN <sup>(1)</sup> | LPEN              | _                 | BGREQ             | —                 | —                 | ASINT            | <1:0> <sup>(2)</sup> |

| 7.0          | U-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | _                   | _                 | _                 |                   | WM<               | <1:0>             | CM<              | <1:0>                |

#### REGISTER 16-4: AD1CON5: ADC CONTROL REGISTER 5

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ASEN:** Auto-Scan Enable bit<sup>(1)</sup>

- 1 = Auto-scan is enabled

- 0 = Auto-scan is disabled

#### bit 14 LPEN: Low-Power Enable bit

- 1 = Low power is enabled after scan

- 0 = Full power is enabled after scan

- bit 13 Unimplemented: Read as '0'

#### bit 12 BGREQ: Band Gap Request bit

- 1 = Band gap is enabled when the ADC is enabled and active

- 0 = Band gap is not enabled by the ADC

#### bit 11-10 Unimplemented: Read as '0'

- bit 9-8 ASINT<1:0>: Auto-Scan (Threshold Detect) Interrupt Mode bits<sup>(2)</sup>

- 11 = Interrupt after Threshold Detect sequence has completed and a valid compare has occurred

- 10 = Interrupt after valid compare has occurred

- 01 = Interrupt after Threshold Detect sequence has completed

- 00 = No interrupt

- bit 7-4 Unimplemented: Read as '0'

#### bit 3-2 WM<1:0>: Write Mode bits

- 11 = Reserved

- 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid match occurs, as defined by the CM<1:0> and ASINT<1:0> bits)

- 01 = Convert and save (conversion results saved to ADC1BUFx registers when a match occurs, as defined by the CM<1:0> bits)

- 00 = Threshold (Comparison) mode is disabled, legacy operation (conversion data saved to ADC1BUFx registers)

- Note 1: When auto-scan is enabled (ASEN (AD1CON5<15>) = 1), the CSCNA (AD1CON2<10>) and SMPI<3:0> (AD1CON2<5:2>) bits are ignored.

- 2: The ASINT<1:0> bits setting only takes effect when ASEN (AD1CON5<15>) = 1. Interrupt generation is governed by the SMPI<3:0> bits field.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | —                 | _                 | _                 | —                | —                |

| 00.40        | U-0 U-0           |                   | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 |                   |                   | D                 | ACDAT<4:0>        |                  |                  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                  | R/W-0            |

| 15:8         | ON                | _                 | _                 | —                 | —                 | _                 | _                | DACOE            |

| 7.0          | U-0               | J-0 U-0 U-0       |                   | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | _                 |                   | _                 | REFSE            | EL<1:0>          |

#### REGISTER 20-1: DAC1CON: CDAC CONTROL REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

bit 20-16 **DACDAT<4:0>:** CDAC Voltage Reference Selection bits

11111 = (DACDAT<4:0> \* VREF+/32) or (DACDAT<4:0> \* AVDD/32) volts depending on the REFSEL<1:0> bits  $\cdot$

•

00000 = 0.0 volts

- bit 15 **ON:** Voltage Reference Enable bit

- 1 = Voltage reference is enabled

- 0 = Voltage reference is disabled

#### bit 14-9 Unimplemented: Read as '0'

- bit 8 DACOE: CDAC Voltage Reference Output Enable bit

- 1 = Voltage level is output on the CDAC1 pin

- 0 = Voltage level is disconnected from the CDAC1 pin

#### bit 7-2 Unimplemented: Read as '0'

- bit 1-0 REFSEL<1:0>: CDAC Voltage Reference Source Select bits

- 11 = Reference voltage is AVDD

- 10 = No reference is selected output is AVss

- 01 = Reference voltage is the VREF+ input pin voltage

- 00 = No reference is selected output is AVss

## 23.5 Band Gap Voltage Reference

PIC32MM0064GPL036 family devices have a precision voltage reference band gap circuit used by many modules. The analog buffers are implemented between the band gap circuit and these modules. The buffers are automatically enabled by the hardware if some part of the device needs the band gap reference. The stabilization time is required when the buffer is switched on. The software can enable these buffers in advance to allow the band gap voltage to stabilize before the module uses it. The ANCFG register contains bits to enable the band gap buffers for the comparators (VBGCMP bit) and ADC (VBGADC bit). Refer to Table 23-6 and Register 23-10 for more information.

## 23.6 Programming and Diagnostics

PIC32MM0064GPL036 family devices provide a complete range of programming and diagnostic features:

- Simplified Field Programmability using Two-Wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Interfaces

- Debugging using ICSP

- Programming and Debugging Capabilities using the EJTAG Extension of JTAG

- JTAG Boundary Scan Testing for Device and Board Diagnostics

## 23.7 Unique Device Identifier (UDID)

PIC32MM0064GPL036 family devices are individually encoded during final manufacturing with a Unique Device Identifier or UDID. The UDID cannot be erased by a bulk erase command or any other user accessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a requirement. It may also be used by the application manufacturer for any number of things that may require unique identification, such as:

- Tracking the device

- · Unique serial number

- Unique security key

The UDID comprises five 32-bit program words. When taken together, these fields form a unique 160-bit identifier.

The UDID is stored in five read-only locations, located from 0xBFC41840 to 0xBFC41854 in the device configuration space. Table 23-7 lists the addresses of the Identifier Words.

## 23.8 Reserved Registers

PIC32MM0064GPL036 family devices have 3 reserved registers, located at 0xBF800400, 0xBF800480 and 0xBF802280. The application code must not modify these reserved locations. Table 23-8 lists the addresses of these reserved registers.

## REGISTER 23-5: FOSCSEL/AFOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | r-1 r-1           |                   | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        |                   | _                 | _                 | _                 | —                 | _                 |                  | _                |

| 45.0         | R/P               | R/P               | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | FCKSM<1:0>        |                   | _                 | SOSCSEL           | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |

| 7.0          | R/P R/P           |                   | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 7:0          | 7:0 IESO SOSCEI   |                   |                   | PLLSRC            | _                 |                   | FNOSC<2:0>       | 1                |

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-16 | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15-14 | FCKSM<1:0>: Clock Switching and Fail-Safe Clock Monitor Enable bits                                                                                                                                                                                                                                                                |

|           | <ul> <li>11 = Clock switching is enabled; Fail-Safe Clock Monitor is enabled</li> <li>10 = Clock switching is disabled; Fail-Safe Clock Monitor is enabled</li> <li>01 = Clock switching is enabled; Fail-Safe Clock Monitor is disabled</li> <li>00 = Clock switching is disabled; Fail-Safe Clock Monitor is disabled</li> </ul> |

| bit 13    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 12    | SOSCSEL: Secondary Oscillator (SOSC) External Clock Enable bit                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Crystal is used (RA4 and RB4 pins are controlled by SOSC)</li><li>0 = External clock is connected to the SOSCO pin (RA4 and RB4 pins are controlled by I/O PORTx registers)</li></ul>                                                                                                                                  |

| bit 11    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 10    | OSCIOFNC: System Clock on CLKO Pin Enable bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = OSC2/CLKO pin operates as normal I/O</li> <li>0 = System clock is connected to the OSC2/CLKO pin</li> </ul>                                                                                                                                                                                                           |

| bit 9-8   | POSCMOD<1:0>: Primary Oscillator (POSC) Mode Selection bits                                                                                                                                                                                                                                                                        |

|           | <ul> <li>11 = Primary Oscillator is disabled</li> <li>10 = HS Oscillator mode is selected</li> <li>01 = XT Oscillator mode is selected</li> <li>00 = External Clock (EC) mode is selected</li> </ul>                                                                                                                               |

| bit 7     | IESO: Two-Speed Start-up Enable bit                                                                                                                                                                                                                                                                                                |

|           | <ul><li>1 = Two-Speed Start-up is enabled</li><li>0 = Two-Speed Start-up is disabled</li></ul>                                                                                                                                                                                                                                     |

| bit 6     | SOSCEN: Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Secondary Oscillator is enabled</li><li>0 = Secondary Oscillator is disabled</li></ul>                                                                                                                                                                                                                                 |

| bit 5     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 4     | PLLSRC: System PLL Input Clock Selection bit                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = FRC oscillator is selected as the PLL reference input on a device Reset</li> <li>0 = Primary Oscillator (POSC) is selected as the PLL reference input on a device Reset</li> </ul>                                                                                                                                    |

| bit 3     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

## TABLE 23-5: RAM CONFIGURATION, DEVICE ID AND SYSTEM LOCK REGISTERS MAP

| ess                         |                  | e         |       |               |       |       |       |       |      | Bit    | 5      |       |       |      |        |      |      |      | (1)                      |

|-----------------------------|------------------|-----------|-------|---------------|-------|-------|-------|-------|------|--------|--------|-------|-------|------|--------|------|------|------|--------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7   | 22/6  | 21/5  | 20/4 | 19/3   | 18/2 | 17/1 | 16/0 | All Resets <sup>(1</sup> |

| 2000                        | 050001           | 31:16     | _     |               |       |       |       |       |      |        |        |       | 0000  |      |        |      |      |      |                          |

| 3B00                        | CFGCON           | 15:0      |       | _             | _     | _     | _     | _     | _    | _      | _      | _     | _     | _    | JTAGEN | _    | _    | _    | 000x                     |

| 3B20                        | DEVID            | 31:16     |       | VER           | <3:0> |       |       |       |      |        |        | ID<27 | /:16> |      |        |      |      |      | xxxx                     |

| 3620                        | DEVID            | 15:0      |       | ID<15:0> xxxx |       |       |       |       |      |        |        |       |       |      |        |      |      |      |                          |

| 3B30                        | SYSKEY           | 31:16     |       | SYSKEY<31:0>  |       |       |       |       |      |        |        |       |       |      |        |      |      |      |                          |

| 3630                        | STOKET           | 15:0      |       |               |       |       |       |       |      | STORET | <31.02 |       |       |      |        |      |      |      | 0001                     |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the device variant.

## REGISTER 23-8: DEVID: DEVICE ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|---------------------|-------------------|--------------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R-x               | R-x               | R-x                 | R-x               | R-x                      |                   |                  | R-x              |  |  |  |

| 31:24        |                   | VER<3             | 3:0> <sup>(1)</sup> |                   | ID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |  |

| 00.40        | R-x               | R-x               | R-x                 | R-x               | R-x                      | R-x               | R-x              | R-x              |  |  |  |

| 23:16        |                   |                   |                     | ID<23:1           | 6>(1)                    |                   |                  |                  |  |  |  |

| 45.0         | R-x               | R-x               | R-x                 | R-x               | R-x                      | R-x               | R-x              | R-x              |  |  |  |

| 15:8         |                   |                   |                     | ID<15:            | 8>(1)                    |                   |                  |                  |  |  |  |

| 7.0          | R-x R-x           |                   | R-x                 | R-x R-x           |                          | R-x               | R-x              | R-x              |  |  |  |

| 7:0          |                   |                   |                     | ID<7:(            | )>(1)                    |                   |                  |                  |  |  |  |

| Legend: | L | eg | er | ۱d | : |

|---------|---|----|----|----|---|

|---------|---|----|----|----|---|

.

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID bits<sup>(1)</sup>

Note 1: Reset values are dependent on the device variant.

#### REGISTER 23-9: SYSKEY: SYSTEM UNLOCK REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | SYSKEY            | <31:24>           |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 23:16        | SYSKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | SYSKEY            | <15:8>            |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0 W-0 W-0       |                   |                   | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | SYSKE             | /<7:0>            |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 SYSKEY<31:0>: Unlock and Lock Key bits

## TABLE 23-7: UNIQUE DEVICE IDENTIFIER (UDID) REGISTER MAP

| ess                         |                  | Ċ,        |       |                    |       | ,     | ,     |       |      | В    | its        |      |      |      |      |      |      |      |            |

|-----------------------------|------------------|-----------|-------|--------------------|-------|-------|-------|-------|------|------|------------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7       | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 1840                        | UDID1            | 31:16     |       | UDID Word 1<31:0>  |       |       |       |       |      |      |            |      |      |      |      |      |      |      |            |

| 1010                        | OBIDT            | 15:0      |       |                    |       |       |       |       |      |      |            |      |      |      |      |      |      |      |            |

| 1844                        | UDID2            | 31:16     |       | LIDID Word 2c31:0> |       |       |       |       |      |      |            |      |      |      |      |      |      |      |            |

| 1044                        | ODIDZ            | 15:0      |       | UDID Word 2<31:0>  |       |       |       |       |      |      |            |      |      |      |      |      |      |      |            |

| 1848                        | UDID3            | 31:16     |       |                    |       |       |       |       |      |      | rd 3<31:0> |      |      |      |      |      |      |      | xxxx       |

| 1040                        | 00103            | 15:0      |       |                    |       |       |       |       |      |      | iu 3<31.02 |      |      |      |      |      |      |      | xxxx       |

| 184C                        | UDID4            | 31:16     |       | xxxx               |       |       |       |       |      |      |            |      |      | xxxx |      |      |      |      |            |

| 1040                        | 00104            | 15:0      |       | UDID Word 4<31:0>  |       |       |       |       |      |      |            |      |      |      |      |      |      |      |            |

| 1850                        | UDID5            | 31:16     |       |                    |       |       |       |       |      |      | rd 5<31:0> |      |      |      |      |      |      |      | xxxx       |

| 1000                        | 00105            | 15:0      |       |                    |       |       |       |       |      |      | iu 5~51.0~ |      |      |      |      |      |      |      | xxxx       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 23-8: RESERVED REGISTERS MAP

| ess                      | Virtual Address<br>(BF80_#)<br>Register<br>Name | Bit Range | Bits                      |                           |       |       |       |       |      |      |      |      |      |      | í    |      |      |

|--------------------------|-------------------------------------------------|-----------|---------------------------|---------------------------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|

| Virtual Addr<br>(BF80_#) |                                                 |           | 31/15                     | 30/14                     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 |

| 0400                     |                                                 | 31:16     | Descried Desister 1-24-05 |                           |       |       |       |       |      |      |      |      |      |      | 0000 |      |      |

| 0400                     | RESERVED1                                       | 15:0      |                           | Reserved Register 1<31:0> |       |       |       |       |      |      |      |      |      |      |      | 0000 |      |

| 0480                     | RESERVED2                                       | 31:16     | Descend Desister 0.494.0  |                           |       |       |       |       |      |      |      |      |      |      | 0000 |      |      |

| 0460                     | RESERVEDZ                                       | 15:0      | Reserved Register 2<31:0> |                           |       |       |       |       |      |      |      |      |      | 0000 |      |      |      |

| 2220                     | 2280 RESERVED3                                  | 31:16     |                           |                           |       |       |       |       |      |      |      |      |      | 0C00 |      |      |      |

| 2280                     |                                                 | 15:0      |                           | Reserved Register 3<31:0> |       |       |       |       |      |      |      |      |      |      | 0000 |      |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

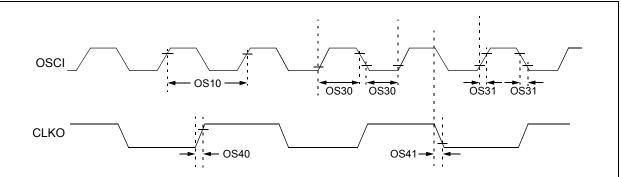

## FIGURE 26-3: EXTERNAL CLOCK TIMING

## TABLE 26-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |               |                                               |                              |                    |                            |                                 |                                                                  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------|------------------------------|--------------------|----------------------------|---------------------------------|------------------------------------------------------------------|--|--|

| Param<br>No.                                                                                                            | Symbol        | Characteristic                                | Min                          | Typ <sup>(1)</sup> | Мах                        | Units                           | Conditions                                                       |  |  |

| OS10                                                                                                                    | Fosc          | External CLKI Frequency                       | DC<br>2                      |                    | 25<br>12.5                 | MHz<br>MHz                      | EC<br>ECPLL <sup>(2)</sup>                                       |  |  |

|                                                                                                                         |               | Oscillator Frequency                          | 3.5<br>3.5<br>10<br>10<br>31 |                    | 10<br>10<br>25<br>25<br>50 | MHz<br>MHz<br>MHz<br>MHz<br>kHz | XT<br>XTPLL <sup>(2)</sup><br>HS<br>HSPLL <sup>(2)</sup><br>SOSC |  |  |

| OS30                                                                                                                    | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time  | 0.45 x Tosc                  |                    | 0.55 x Tosc                | ns                              | EC                                                               |  |  |

| OS31                                                                                                                    | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time | _                            | _                  | 20                         | ns                              | EC                                                               |  |  |

| OS40                                                                                                                    | TckR          | CLKO Rise Time <sup>(3)</sup>                 |                              | 15                 | 20                         | ns                              |                                                                  |  |  |

| OS41                                                                                                                    | TckF          | CLKO Fall Time <sup>(3)</sup>                 |                              | 15                 | 20                         | ns                              |                                                                  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: PLL dividers and postscalers must be configured so that the system clock frequency does not exceed the maximum operating frequency.

3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

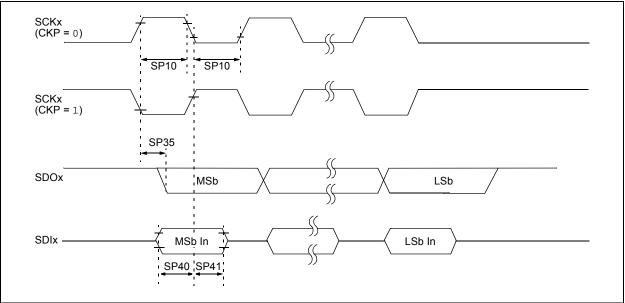

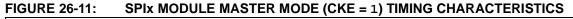

#### FIGURE 26-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

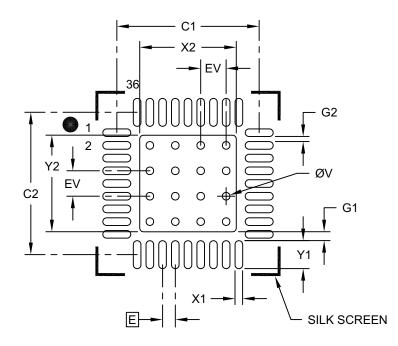

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x0.9 mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## **RECOMMENDED LAND PATTERN**

|                                  | MILLIMETERS |      |          |      |  |  |  |

|----------------------------------|-------------|------|----------|------|--|--|--|

| Dimension                        | MIN         | NOM  | MAX      |      |  |  |  |

| Contact Pitch                    | Е           |      | 0.50 BSC |      |  |  |  |

| Optional Center Pad Width        | X2          |      |          | 3.80 |  |  |  |

| Optional Center Pad Length       | Y2          |      |          | 3.80 |  |  |  |

| Contact Pad Spacing              | C1          |      | 5.60     |      |  |  |  |

| Contact Pad Spacing              | C2          |      | 5.60     |      |  |  |  |

| Contact Pad Width (X36)          | X1          |      |          | 0.30 |  |  |  |

| Contact Pad Length (X36)         | Y1          |      |          | 1.10 |  |  |  |

| Contact Pad to Center Pad (X36)  | G1          | 0.35 |          |      |  |  |  |

| Space Between Contact Pads (X32) | G2          | 0.20 |          |      |  |  |  |

| Thermal Via Diameter             | V           |      | 0.30     |      |  |  |  |

| Thermal Via Pitch                | EV          |      | 1.00     |      |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2272B-M2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0653-2