#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register<br>Number | Register<br>Name                                                                                   | Function                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3                | Reserved                                                                                           | Reserved in the microAptiv™ UC.                                                                                                                                                               |

| 4                  | UserLocal                                                                                          | User information that can be written by privileged software and read via RDHWR, Register 29.                                                                                                  |

| 5-6                | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 7                  | HWREna                                                                                             | Enables access via the RDHWR instruction to selected hardware registers in Non-Privileged mode.                                                                                               |

| 8                  | BadVAddr <sup>(1)</sup>                                                                            | Reports the address for the most recent address related exception.                                                                                                                            |

| 9                  | Count <sup>(1)</sup>                                                                               | Processor cycle count.                                                                                                                                                                        |

| 10                 | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 11                 | Compare <sup>(1)</sup>                                                                             | Timer interrupt control.                                                                                                                                                                      |

| 12                 | Status/<br>IntCtl/<br>SRSCtl/<br>SRSMap1/<br>View_IPL/<br>SRSMAP2                                  | Processor status and control; interrupt control and shadow set control.                                                                                                                       |

| 13                 | Cause <sup>(1)</sup> /<br>View_RIPL                                                                | Cause of last exception.                                                                                                                                                                      |

| 14                 | EPC <sup>(1)</sup>                                                                                 | Program Counter at last exception.                                                                                                                                                            |

| 15                 | PRId/<br>EBase/<br>CDMMBase                                                                        | Processor identification and revision; exception base address; Common Device Memory Map Base register.                                                                                        |

| 16                 | CONFIG/<br>CONFIG1/<br>CONFIG2/<br>CONFIG3/<br>CONFIG7                                             | Configuration registers.                                                                                                                                                                      |

| 7-22               | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 23                 | Debug/<br>Debug2/<br>TraceControl/<br>TraceControl2/<br>UserTraceData1/<br>TraceBPC <sup>(2)</sup> | EJTAG Debug register.<br>EJTAG Debug Register 2.<br>EJTAG Trace Control register.<br>EJTAG Trace Control Register 2.<br>EJTAG User Trace Data 1 register.<br>EJTAG Trace Breakpoint register. |

| 24                 | DEPC <sup>(2)</sup> /<br>UserTraceData2                                                            | Program Counter at last debug exception.<br>EJTAG User Trace Data 2 register.                                                                                                                 |

| 25                 | PerfCtl0/<br>PerfCnt0/<br>PerfCtl1/<br>PerfCnt1                                                    | Performance Counter 0 control.<br>Performance Counter 0.<br>Performance Counter 1 control.<br>Performance Counter 1.                                                                          |

| 26                 | ErrCtl                                                                                             | Software parity check enable.                                                                                                                                                                 |

| 27                 | CacheErr                                                                                           | Records information about SRAM parity errors.                                                                                                                                                 |

| 28-29              | Reserved                                                                                           | Reserved in the PIC32 core.                                                                                                                                                                   |

| 30                 | ErrorEPC <sup>(1)</sup>                                                                            | Program Counter at last error.                                                                                                                                                                |

| 31                 | DeSAVE <sup>(2)</sup>                                                                              | Debug Handler Scratchpad register.                                                                                                                                                            |

#### TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used in debug.

# 7.1 CPU Exceptions

CPU Coprocessor 0 contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events or program errors. Table 7-1 lists the exception types in order of priority.

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES

| Exception Type<br>(In Order of<br>Priority) | Description                                                                    | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set | EXCCODE     | XC32 Function Name         |

|---------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|-------------------|-------------|----------------------------|

|                                             |                                                                                | Highest Priority                                                         |                    |                   |             |                            |

| Reset                                       | Assertion of MCLR.                                                             | 0xBFC0_0000                                                              | BEV, ERL           | _                 | —           | _on_reset                  |

| Soft Reset                                  | Execution of a RESET instruction.                                              | 0xBFC0_0000                                                              | BEV, SR,<br>ERL    | —                 | —           | _on_reset                  |

| DSS                                         | EJTAG debug single step.                                                       | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | —                  | DSS               | —           | _                          |

| DINT                                        | EJTAG debug interrupt. Caused by setting the EjtagBrk bit in the ECR register. | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DINT              | _           | _                          |

| NMI                                         | Non-maskable interrupt.                                                        | 0xBFC0_0000                                                              | BEV, NMI,<br>ERL   | —                 | —           | _nmi_handler               |

| Interrupt                                   | Assertion of unmasked hardware or software interrupt signal.                   | See Table 7-2                                                            | IPL<2:0>           | _                 | Int (0x00)  | See Table 7-2              |

| DIB                                         | EJTAG debug hardware instruction break matched.                                | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIB               | _           | _                          |

| AdEL                                        | Load address alignment error.                                                  | EBASE + 0x180                                                            | EXL                | _                 | ADEL (0x04) | _general_exception_handler |

| IBE                                         | Instruction fetch bus error.                                                   | EBASE + 0x180                                                            | EXL                | —                 | IBE (0x06)  | _general_exception_handler |

| DBp                                         | EJTAG breakpoint (execution of SDBBP instruction).                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | DBp                | _                 | _           |                            |

| Sys                                         | Execution of SYSCALL instruction.                                              | EBASE + 0x180                                                            | EXL                | _                 | Sys (0x08)  | _general_exception_handler |

| Вр                                          | Execution of BREAK instruction.                                                | EBASE + 0x180                                                            | EXL                | _                 | Bp (0x09)   | _general_exception_handler |

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| CpU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | _                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          |                    |                                                                            |                |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | _                 | CNSTYLE           | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 |                   | _                 |                   |                   |                  |                  |

#### **REGISTER 9-1:** CNCONX: CHANGE NOTIFICATION CONTROL FOR PORTX REGISTER (x = A-C)

| -n = Value at POR | '1' = Bit is set |

|-------------------|------------------|

|                   |                  |

Legend:

R = Readable bit

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notification (CN) Control On bit

1 = CN is enabled

0 = CN is disabled

#### bit 14-12 Unimplemented: Read as '0'

bit 11 **CNSTYLE:** Change Notification Style Selection bit

1 = Edge style (detects edge transitions, CNFx bits are used for a Change Notice event)

W = Writable bit

Mismatch style (detects change from last PORTx read, CNSTATx bits are used for a Change Notification event)

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

bit 10-0 Unimplemented: Read as '0'

## REGISTER 10-1: T1CON: TIMER1 CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer1 External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit

- 1 = External clock is defined by the TECS<1:0> bits

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(1)</sup> | —                  |                   | _                     | —                 | —                 | SPIFE            | ENHBUF <sup>(1)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON                     | _                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE16            | SMP              | CKE <sup>(2)</sup>    |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

#### **REGISTER 13-1:** SPIxCON: SPIx CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled ( $\overline{SSx}$  pin is used as the FSYNC1 input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> Pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 **MSSEN:** Master Mode Slave Select Enable bit

- 1 = Slave select SPI support is enabled; the SSx pin is automatically driven during transmission in Master mode, polarity is determined by the FRMPOL bit

- 0 = Slave select SPI support is disabled

- bit 27 FRMSYPW: Frame Sync Pulse-Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits

Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generates a frame sync pulse on every 32 data characters

- 100 = Generates a frame sync pulse on every 16 data characters

- 011 = Generates a frame sync pulse on every 8 data characters

- 010 = Generates a frame sync pulse on every 4 data characters

- 001 = Generates a frame sync pulse on every 2 data characters

- 000 = Generates a frame sync pulse on every data character

- **Note 1:** These bits can only be written when the ON bit = 0. Refer to **Section 26.0 "Electrical Characteristics"** for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

#### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 24.04        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31:24        | _                    |                   | _                 | —                 | —                        | _                 |                  | _                       |

| 00.40        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23:16        | —                    | _                 | —                 | —                 | —                        | _                 | —                | _                       |

| 45.0         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 15:8         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   | —                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### REGISTER 13-2: SPIxCON2: SPIx CONTROL REGISTER 2

#### Legend:

| 0                 |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15        | <b>SPISGNEXT:</b> SPIx Sign-Extend Read Data from the RX FIFO bit<br>1 = Data from RX FIFO is sign-extended                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 0 = Data from RX FIFO is not sign-extended                                                                                                                                       |

| bit 14-13     | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 12        | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                                                                 |

|               | <ul><li>1 = Frame error overflow generates error events</li><li>0 = Frame error does not generate error events</li></ul>                                                         |

| bit 11        | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                                                                 |

|               | <ul><li>1 = Receive Overflow (ROV) generates error events</li><li>0 = Receive Overflow does not generate error events</li></ul>                                                  |

| bit 10        | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                                                                 |

|               | <ul><li>1 = Transmit Underrun (TUR) generates error events</li><li>0 = Transmit Underrun does not generate error events</li></ul>                                                |

| bit 9         | IGNROV: Ignore Receive Overflow (ROV) bit (for audio data transmissions)                                                                                                         |

|               | 1 = A ROV is not a critical error; during ROV, data in the FIFO is not overwritten by receive data<br>0 = A ROV is a critical error which stops SPIx operation                   |

| bit 8         | IGNTUR: Ignore Transmit Underrun (TUR) bit (for audio data transmissions)                                                                                                        |

|               | <ul> <li>1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty</li> <li>0 = A TUR is a critical error which stops SPIx operation</li> </ul> |

| bit 7         | AUDEN: Enable Audio Codec Support bit <sup>(1)</sup>                                                                                                                             |

|               | <ul><li>1 = Audio protocol is enabled</li><li>0 = Audio protocol is disabled</li></ul>                                                                                           |

| bit 6-4       | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 3         | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                                                         |

|               | <ul><li>1 = Audio data is mono (each data word is transmitted on both left and right channels)</li><li>0 = Audio data is stereo</li></ul>                                        |

| bit 2         | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 1-0       | AUDMOD<1:0>: Audio Protocol Mode bits <sup>(1,2)</sup><br>11 = PCM/DSP mode<br>10 = Right Justified mode<br>01 = Left Justified mode<br>00 = I <sup>2</sup> S mode               |

| Note 1:<br>2: | These bits can only be written when the ON bit = $0$ .<br>These bits are only valid for AUDEN = $1$ .                                                                            |

**2:** These bits are only valid for AUDEN = 1.

# 15.1 RTCC Control Registers

## TABLE 15-1: RTCC REGISTER MAP

| ess                         |                                 | 6         | Bits      |       |          |         |          | ú     |        |      |          |      |                         |        |        |       |          |         |            |

|-----------------------------|---------------------------------|-----------|-----------|-------|----------|---------|----------|-------|--------|------|----------|------|-------------------------|--------|--------|-------|----------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14 | 29/13    | 28/12   | 27/11    | 26/10 | 25/9   | 24/8 | 23/7     | 22/6 | 21/5                    | 20/4   | 19/3   | 18/2  | 17/1     | 16/0    | All Resets |

| 0000                        | RTCCON1                         | 31:16     | ALRMEN    | CHIME | -        |         |          | AMASK | <3:0>  |      |          |      |                         | ALMRP  | T<7:0> |       |          |         | 0000       |

| 0000                        | RICCONT                         | 15:0      | ON        | _     | _        |         | WRLOCK   | _     | —      |      | RTCOE    |      | OUTSEL<2:0              | >      | —      | —     | _        | —       | 0000       |

| 0010                        | RTCCON2                         | 31:16     | DIV<15:0> |       |          |         |          |       | 0000   |      |          |      |                         |        |        |       |          |         |            |

| 0010                        | RICCONZ                         | 15:0      |           |       | FDIV<4:0 | )>      |          |       |        | —    | —        | —    | —                       | —      | —      | CLKSE | L<1:0>   | 0000    |            |

| 0030                        | RTCSTAT                         | 31:16     | —         | —     | —        | _       | —        | _     | —      | _    | —        | _    | —                       | —      | —      | —     | —        | —       | 0000       |

| 0000                        | RIGOLAI                         | 15:0      | —         | —     | —        | —       | —        | _     | —      | —    | —        | _    | ALMEVT                  | —      | —      | SYNC  | ALMSYNC  | HALFSEC | 0000       |

| 0040                        | RTCTIME                         | 31:16     | —         | F     | IRTEN<2  | :0>     |          | HRONE | =<3:0> |      | —        |      | MINTEN<2:0> MINONE<3:0> |        |        | -     | xxxx     |         |            |

| 0040                        | RIGHME                          | 15:0      |           | SECTE | N<3:0>   |         |          | SECON | E<3:0> |      | —        | _    | _                       |        | _      | —     | —        | —       | xx00       |

| 0050                        | RTCDATE                         | 31:16     |           | YRTE  | N<3:0>   |         |          | YRONE | =<3:0> |      | —        | _    | —                       | MTHTEN |        | MTHC  | DNE<3:0> |         | 0000       |

| 0000                        | RIODAIL                         | 15:0      | —         | —     | DAYT     | EN<1:0> |          | DAYON | E<3:0> |      | —        | _    | _                       | —      | —      |       | WDAY<2:0 | >       | 0000       |

| 0060                        | ALMTIME                         | 31:16     | —         | F     | IRTEN<2  | :0>     |          | HRONE | =<3:0> |      | —        |      | MINTEN<2:0              | >      |        | MINC  | NE<3:0>  | -       | xxxx       |

| 0000                        |                                 | 15:0      |           | SECTE | N<3:0>   |         |          | SECON | E<3:0> |      | —        | _    | —                       | —      | —      | _     | _        | —       | xx00       |

| 0070                        | ALMDATE                         | 31:16     | _         | —     | _        | —       | MTHTEN M |       |        | MTHC | )NE<3:0> |      | 0000                    |        |        |       |          |         |            |

| 0070                        |                                 | 15:0      | _         | —     | DAYTI    | EN<1:0> |          | DAYON | E<3:0> |      | —        | _    | _                       | —      | —      |       | WDAY<2:0 | >       | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# 16.0 12-BIT ANALOG-TO-DIGITAL CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

#### 16.1 Introduction

The 12-bit ADC Converter with Threshold Detect includes the following features:

- Successive Approximation Register (SAR)

Conversion

- · User-Selectable Resolution of 10 or 12 Bits

- Conversion Speeds of up to 200 ksps for 12-bit mode and 300 ksps for 10-bit mode

- Up to 17 Analog Inputs (internal and external)

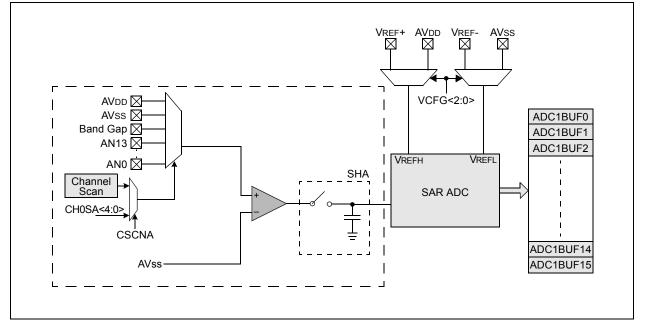

#### FIGURE 16-1: ADC BLOCK DIAGRAM

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold Amplifier (SHA)

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length Configurable Conversion Result

Buffer

- · Eight Options for Result Alignment and Encoding

- Configurable Interrupt Generation

- · Operation during CPU Sleep and Idle modes

Figure 16-1 illustrates a block diagram of the 12-bit ADC. The 12-bit ADC has 14 external analog inputs, AN0 through AN13, and 3 internal analog inputs connected to VDD, VSs and band gap. In addition, there are two analog input pins for external voltage reference connections.

The analog inputs are connected through a multiplexer to the SHA. Unipolar differential conversions are possible on all inputs (see Figure 16-1).

The Automatic Input Scan mode sequentially converts multiple analog inputs. A special control register specifies which inputs will be included in the scanning sequence. The 12-bit ADC is connected to a 16-word result buffer. The 12-bit result is converted to one of eight output formats in either 32-bit or 16-bit word widths.

#### 18.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCON

- CLCxSEL

- CLCxGLS

The CLCx Control register (CLCxCON) is used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select register (CLCxGLS) allows the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 | _                 | _                 | —                 | —                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | —                |

| 45.0         | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 |                   | DS4<2:0>          |                   | —                 |                   | DS3<2:0>         |                  |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   | DS2<2:0>          |                   | _                 | DS1<2:0>          |                  |                  |

#### REGISTER 18-2: CLCxSEL: CLCx INPUT MUX SELECT REGISTER

#### Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-15 Unimplemented: Read as '0'

bit 14-12 **DS4<2:0>:** Data Selection MUX 4 Signal Selection bits

For CLC1:

- 111 = SCCP3 compare match event

- 110 = MCCP1 compare match event

- 101 = RTCC event

- 100 = Reserved

- 011 = SPI1 SDI input

- 010 = SCCP3 OCM3 output

- 001 = CLC2 output

- 000 = CLCINB I/O pin

- For CLC2:

- 111 = SCCP3 compare match event

- 110 = MCCP1 compare match event 101 = RTCC event

- 100 = Reserved

- 011 = SPI2 SDI input

- 010 = SCCP3 OCM3 output

- 001 = CLC1 output

- 000 = CLCINB I/O pin

- bit 11 Unimplemented: Read as '0'

# PIC32MM0064GPL036 FAMILY

#### REGISTER 23-10: ANCFG: BAND GAP CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 |                   | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS, HC     | R/W-0, HS, HC    | U-0              |

| 7:0          | _                 |                   | _                 |                   |                   | VBGADC            | VBGCMP           | _                |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

- bit 2 **VBGADC:** ADC Band Gap Enable bit

- 1 = ADC band gap is enabled

- 0 = ADC band gap is disabled

bit 1 **VBGCMP:** Comparator Band Gap Enable bit

- 1 = Comparator band gap is enabled

- 0 = Comparator band gap is disabled

- bit 0 Unimplemented: Read as '0'

## 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### TABLE 26-14: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                      |                           |             |                    |             |       |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------|--------------------|-------------|-------|--|--|--|

| Param<br>No.                                                                                 | Symbol               | Characteristic            | Min         | Тур <sup>(2)</sup> | Мах         | Units |  |  |  |

| D300                                                                                         | VIOFF                | Input Offset Voltage      | -20         |                    | 20          | mV    |  |  |  |

| D301                                                                                         | VICM                 | Input Common-Mode Voltage | AVss - 0.3V | —                  | AVDD + 0.3V | V     |  |  |  |

| D307                                                                                         | TRESP <sup>(1)</sup> | Response Time             |             | 150                | —           | ns    |  |  |  |

Note 1: Measured with one input at VDD/2 and the other transitioning from Vss to VDD.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-15: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |        |                              |     |                    |     |       |  |  |

|----------------------------------------------------------------------------------------------|--------|------------------------------|-----|--------------------|-----|-------|--|--|

| Param<br>No.                                                                                 | Symbol | Characteristic               | Min | Тур <sup>(2)</sup> | Max | Units |  |  |

| VRD310                                                                                       | TSET   | Settling Time <sup>(1)</sup> | _   |                    | 10  | μs    |  |  |

| VRD311                                                                                       | VRA    | Accuracy                     | -1  | _                  | 1   | LSb   |  |  |

| VRD312                                                                                       | VRur   | Unit Resistor Value (R)      |     | 4.5                |     | kΩ    |  |  |

Note 1: Measures the interval while VRDAT<4:0> transitions from '11111' to '00000'.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

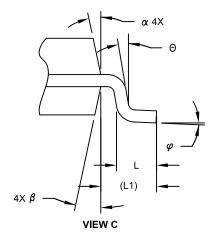

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |           |      |  |

|--------------------------|-------------|-----------|-----------|------|--|

| Dimensior                | Limits      | MIN       | NOM       | MAX  |  |

| Number of Pins           | N           |           | 28        |      |  |

| Pitch                    | е           |           | 1.27 BSC  |      |  |

| Overall Height           | A           | -         | -         | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -         | -    |  |

| Standoff §               | A1          | 0.10      | -         | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |           |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |           |      |  |

| Overall Length           | D           |           | 17.90 BSC |      |  |

| Chamfer (Optional)       | h           | 0.25      | -         | 0.75 |  |

| Foot Length              | L           | 0.40      | -         | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |           |      |  |

| Lead Angle               | Θ           | 0°        | -         | -    |  |

| Foot Angle               | φ           | 0°        | -         | 8°   |  |

| Lead Thickness           | С           | 0.18      | -         | 0.33 |  |

| Lead Width               | b           | 0.31      | -         | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -         | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -         | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5 Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

#### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | MILLIMETERS |      |  |

|-------------------------|--------|----------|-------------|------|--|

| Dimension               | Limits | MIN      | NOM         | MAX  |  |

| Number of Pins          | N      |          | 28          |      |  |

| Pitch                   | е      |          | 0.65 BSC    |      |  |

| Overall Height          | A      | 0.80     | 0.90        | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02        | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF |             |      |  |

| Overall Width           | E      |          | 6.00 BSC    |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70        | 4.20 |  |

| Overall Length          | D      |          | 6.00 BSC    |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70        | 4.20 |  |

| Terminal Width          | b      | 0.23     | 0.30        | 0.35 |  |

| Terminal Length         | L      | 0.50     | 0.55        | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20     | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

# APPENDIX A: REVISION HISTORY

## **Revision A (February 2015)**

This is the initial version of the document.

## Revision B (May 2016)

This revision incorporates the following updates:

- Registers:

- Updates Register 5-1, Register 5-3, Register 5-6, Register 5-7, Register 6-3, Register 6-4, Register 7-2, Register 8-2, Register 8-3, Register 8-5, Register 8-6, Register 11-1, Register 13-1, Register 14-1, Register 15-1, Register 15-5, Register 15-6, Register 16-1, Register 15-2, Register 15-6, Register 16-5, Register 16-2, Register 16-3, Register 16-5, Register 18-2, Register 19-1, Register 19-2 and Register 23-7

- · Tables:

- Updates Table 1-1, Table 5-1, Table 6-1, Table 7-2, Table 7-3, Table 9-3, Table 9-7, Table 15-1, Table 16-1, Table 19-1, Table 22-1, Table 23-4, Table 23-5 Table 26-2, Table 26-3, Table 26-4 and Table 26-6 through Table 26-33

- Adds Table 23-8

- · Figures:

- Updates Figure 1-1, Figure 3-1, Figure 8-1, Figure 10-1, Figure 14-1, Figure 13-1, Figure 14-1, Figure 14-1, Figure 15-1, Figure 17-1, Figure 18-1, Figure 18-3, Figure 26-1, Figure 26-3, Figure 26-4, Figure 26-9, Figure 26-10, Figure 26-11 and Figure 26-12

- Updates pin function descriptions in Section 1.0 "Device Overview"

- Updates text in Section 9.6 "Input Change Notification (ICN)", Section 9.8.4 "Input Mapping", Section 23.7 "Unique Device Identifier (UDID)", Section 22.5 "Low-Power Brown-out Reset" and Section 27.0 "Packaging Information"

- Adds Section 5.1 "Flash Controller Registers Write Protection", Section 8.0 "Oscillator Configuration", Section 23.4 "System Registers Write Protection", reference to Section 22.1 "Sleep Mode", Section 22.2 "Idle Mode" and Section 23.8 "Reserved Registers"

- Updates the Absolute Maximum Ratings in Section 26.0 "Electrical Characteristics"

This revision also includes minor typographical and formatting changes throughout the data sheet text.

# **PRODUCT IDENTIFICATION SYSTEM**

| To order or obtain info                                        | rmation, e.g., on pricing or delivery, refer to the factory or the listed sales o                | office.                                                                                                                                                             |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family<br>Key Feature Set _<br>Pin Count<br>Tape and Reel Flag |                                                                                                  | Example:<br>PIC32MM0064GPL036-I/M2:<br>PIC32 General Purpose Device<br>with MIPS32 <sup>®</sup> microAptiv™ UC<br>Core, 64-Kbyte Program Memory,<br>36-Pin Package. |

| Architecture                                                   | MM = MIPS32 <sup>®</sup> microAptiv™ UC CPU Core                                                 |                                                                                                                                                                     |

| Flash Memory Size                                              | 0016 = 16 Kbytes<br>0032 = 32 Kbytes<br>0064 = 64 Kbytes                                         |                                                                                                                                                                     |

| Family                                                         | GP = General Purpose Family                                                                      |                                                                                                                                                                     |

| Key Feature                                                    | L = Up to 25 MHz operating frequency with basic peripheral set of 2 UART<br>and 2 SPI modules    |                                                                                                                                                                     |

| Pin Count                                                      | 020 = 20-pin<br>028 = 28-pin<br>036 = 36/40-pin                                                  |                                                                                                                                                                     |

| Pattern                                                        | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample |                                                                                                                                                                     |

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15