#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Analog Features**

- Two Analog Comparators with Input Multiplexing

- Programmable High/Low-Voltage Detect (HLVD)

- 5-Bit DAC with Output Pin

- Up to 14-Channel, Software-Selectable 10/12-Bit SAR Analog-to-Digital Converter (ADC):

- 12-bit, 200K samples/second conversion rate (single Sample-and-Hold)

- 10-bit, 300K samples/second conversion rate (single Sample-and-Hold)

- Sleep mode operation

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

- Brown-out Reset (BOR)

|                   |       | (bytes)                 | (Kbytes)        | O/PPS                   | Maximum           | Maximum         |                                |               |                     | ppak<br>hera        |     | -                                    | (Channels)         |             |     |      |      |                                  |

|-------------------|-------|-------------------------|-----------------|-------------------------|-------------------|-----------------|--------------------------------|---------------|---------------------|---------------------|-----|--------------------------------------|--------------------|-------------|-----|------|------|----------------------------------|

| Device            | Pins  | Program Memory (Kbytes) | Data Memory (Kb | General Purpose I/O/PPS | 16-Bit Timers Max | PWM Outputs Max | UART <sup>(1)</sup> /LIN/J2602 | 16-Bit Timers | MCCP <sup>(3)</sup> | SCCP <sup>(4)</sup> | СГС | SPI <sup>(2)</sup> /I <sup>2</sup> S | 10/12-Bit ADC (Cha | Comparators | CRC | RTCC | JTAG | Packages                         |

| PIC32MM0016GPL020 | 20    | 16                      | 4               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0032GPL020 | 20    | 32                      | 8               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0064GPL020 | 20    | 64                      | 8               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0016GPL028 | 28    | 16                      | 4               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SSOP/SOIC/<br>QFN/UQFN           |

| PIC32MM0032GPL028 | 28    | 32                      | 8               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SSOP/ SOIC/<br>QFN/UQFN          |

| PIC32MM0064GPL028 | 28    | 64                      | 8               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SPDIP/SSOP/<br>SOIC/QFN/<br>UQFN |

| PIC32MM0016GPL036 | 36/40 | 16                      | 4               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

| PIC32MM0032GPL036 | 36/40 | 32                      | 8               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

| PIC32MM0064GPL036 | 36/40 | 64                      | 8               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

## TABLE 1: PIC32MM0064GPL036 FAMILY DEVICES

**Note 1:** UART1 has assigned pins. UART2 is remappable.

**2:** SPI1 has assigned pins. SPI2 is remappable.

**3:** MCCP can be configured as a PWM with up to 6 outputs, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

4: SCCP can be configured as a PWM with 1 output, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

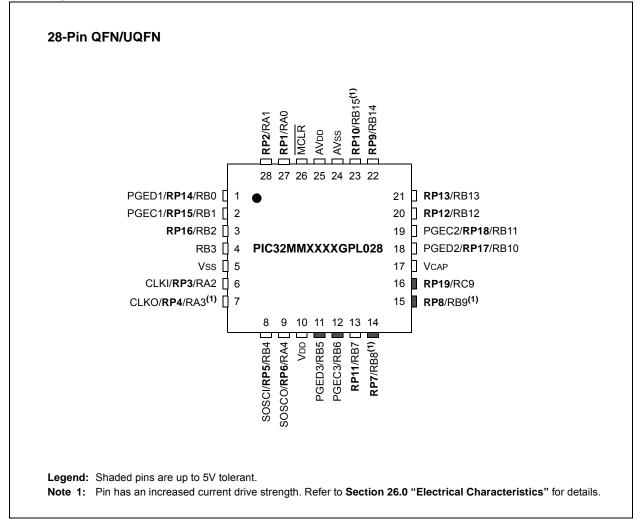

## **Pin Diagrams (Continued)**

### TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN QFN/UQFN DEVICES

| Pin | Function                                             | Pin | Function                                                                                    |

|-----|------------------------------------------------------|-----|---------------------------------------------------------------------------------------------|

| 1   | PGED1/AN2/C1IND/C2INB <b>/RP14</b> /RB0              | 15  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/<br>INT2/RB9 <sup>(1)</sup> |

| 2   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1              | 16  | RP19/RC9                                                                                    |

| 3   | AN4/C1INB/ <b>RP16</b> /RB2                          | 17  | VCAP                                                                                        |

| 4   | AN11/C1INA/RB3                                       | 18  | PGED2/TDO/ <b>RP17</b> /RB10                                                                |

| 5   | Vss                                                  | 19  | PGEC2/TDI/ <b>RP18</b> /RB11                                                                |

| 6   | OSC1/CLKI/AN5/ <b>RP3</b> /OCM1C/RA2                 | 20  | AN7/LVDIN/ <b>RP12</b> /RB12                                                                |

| 7   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>  | 21  | AN8/ <b>RP13</b> /RB13                                                                      |

| 8   | SOSCI/ <b>RP5</b> /RB4                               | 22  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                       |

| 9   | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                 | 23  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                                  |

| 10  | VDD                                                  | 24  | AVss                                                                                        |

| 11  | PGED3/RB5                                            | 25  | AVdd                                                                                        |

| 12  | PGEC3/RB6                                            | 26  | MCLR                                                                                        |

| 13  | RP11/RB7                                             | 27  | VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                                                       |

| 14  | TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup> | 28  | Vref-/AN1/ <b>RP2</b> /OCM1F/RA1                                                            |

Note 1: Pin has an increased current drive strength.

|          |               |                | Pin                    | Number                        |                |                |             | 1              |                                               |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|-----------------------------------------------|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                                   |

| RP1      | 19            | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | Remappable peripherals (input or output)      |

| RP2      | 20            | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         |                                               |

| RP3      | 4             | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         |                                               |

| RP4      | 5             | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         |                                               |

| RP5      | 6             | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         |                                               |

| RP6      | 7             | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         |                                               |

| RP7      | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         |                                               |

| RP8      | 10            | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         |                                               |

| RP9      | 14            | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         |                                               |

| RP10     | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         |                                               |

| RP11     | 8             | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         |                                               |

| RP12     | 12            | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         |                                               |

| RP13     | 13            | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         |                                               |

| RP14     | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         |                                               |

| RP15     | 2             | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         |                                               |

| RP16     | 3             | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         |                                               |

| RP17     |               | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         |                                               |

| RP18     | —             | —              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         |                                               |

| RP19     | —             | —              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         |                                               |

| RP20     | —             | —              | —                      | —                             | 11             | 11             | I/O         | ST/DIG         |                                               |

| RTCC     | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | Real-Time Clock alarm/seconds output          |

| SCK1     | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | SPI1 clock (input or output)                  |

| SCLKI    | 7             | 10             | 9                      | 12                            | 10             | 10             | Ι           | ST             | Secondary Oscillator external clock input     |

| SDI1     | 14            | 17             | 22                     | 25                            | 28             | 31             | Ι           | ST             | SPI1 data input                               |

| SDO1     | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | SPI1 data output                              |

| SOSCI    | 6             | 9              | 8                      | 11                            | 9              | 9              | —           | —              | Secondary Oscillator crystal                  |

| SOSCO    | 7             | 10             | 9                      | 12                            | 10             | 10             | —           | —              | Secondary Oscillator crystal                  |

| SS1      | 15            | 18             | 23                     | 26                            | 29             | 32             | Ι           | ST             | SPI1 slave select input                       |

| T1CK     | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | Timer1 external clock input                   |

| T1G      | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | Timer1 clock gate input                       |

| тск      | 9             | 12             | 14                     | 17                            | 18             | 18             | Ι           | ST             | JTAG clock input                              |

| TDI      | 13            | 16             | 19                     | 22                            | 25             | 28             | Ι           | ST             | JTAG data input                               |

| TDO      | 12            | 15             | 18                     | 21                            | 24             | 27             | 0           | DIG            | JTAG data output                              |

| TMS      | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | JTAG mode select input                        |

| U1BCLK   | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | UART1 IrDA <sup>®</sup> 16x baud clock output |

| U1CTS    | 9             | 12             | 14                     | 17                            | 18             | 18             | Ι           | ST             | UART1 transmission control input              |

| U1RTS    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | UART1 reception control output                |

| U1RX     | 15            | 18             | 23                     | 26                            | 29             | 32             | Ι           | ST             | UART1 receive data input                      |

| U1TX     | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | UART1 transmit data output                    |

| Legend:  | ST = Sc       | hmitt Tric     | ger input              | buffer                        | DIG = Dig      | nital input    | t/output    |                | ANA = Analog level input/output               |

#### PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED) **TABLE 1-1:**

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 2.1 Basic Connection Requirements

Getting started with the PIC32MM0064GPL036 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Capacitor on Internal Voltage Regulator (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Register<br>Number | Register<br>Name                                                                                   | Function                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3                | Reserved                                                                                           | Reserved in the microAptiv™ UC.                                                                                                                                                               |

| 4                  | UserLocal                                                                                          | User information that can be written by privileged software and read via RDHWR, Register 29.                                                                                                  |

| 5-6                | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 7                  | HWREna                                                                                             | Enables access via the RDHWR instruction to selected hardware registers in Non-Privileged mode.                                                                                               |

| 8                  | BadVAddr <sup>(1)</sup>                                                                            | Reports the address for the most recent address related exception.                                                                                                                            |

| 9                  | Count <sup>(1)</sup>                                                                               | Processor cycle count.                                                                                                                                                                        |

| 10                 | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 11                 | Compare <sup>(1)</sup>                                                                             | Timer interrupt control.                                                                                                                                                                      |

| 12                 | Status/<br>IntCtl/<br>SRSCtl/<br>SRSMap1/<br>View_IPL/<br>SRSMAP2                                  | Processor status and control; interrupt control and shadow set control.                                                                                                                       |

| 13                 | Cause <sup>(1)</sup> /<br>View_RIPL                                                                | Cause of last exception.                                                                                                                                                                      |

| 14                 | EPC <sup>(1)</sup>                                                                                 | Program Counter at last exception.                                                                                                                                                            |

| 15                 | PRId/<br>EBase/<br>CDMMBase                                                                        | Processor identification and revision; exception base address; Common Device Memory Map Base register.                                                                                        |

| 16                 | CONFIG/<br>CONFIG1/<br>CONFIG2/<br>CONFIG3/<br>CONFIG7                                             | Configuration registers.                                                                                                                                                                      |

| 7-22               | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 23                 | Debug/<br>Debug2/<br>TraceControl/<br>TraceControl2/<br>UserTraceData1/<br>TraceBPC <sup>(2)</sup> | EJTAG Debug register.<br>EJTAG Debug Register 2.<br>EJTAG Trace Control register.<br>EJTAG Trace Control Register 2.<br>EJTAG User Trace Data 1 register.<br>EJTAG Trace Breakpoint register. |

| 24                 | DEPC <sup>(2)</sup> /<br>UserTraceData2                                                            | Program Counter at last debug exception.<br>EJTAG User Trace Data 2 register.                                                                                                                 |

| 25                 | PerfCtl0/<br>PerfCnt0/<br>PerfCtl1/<br>PerfCnt1                                                    | Performance Counter 0 control.<br>Performance Counter 0.<br>Performance Counter 1 control.<br>Performance Counter 1.                                                                          |

| 26                 | ErrCtl                                                                                             | Software parity check enable.                                                                                                                                                                 |

| 27                 | CacheErr                                                                                           | Records information about SRAM parity errors.                                                                                                                                                 |

| 28-29              | Reserved                                                                                           | Reserved in the PIC32 core.                                                                                                                                                                   |

| 30                 | ErrorEPC <sup>(1)</sup>                                                                            | Program Counter at last error.                                                                                                                                                                |

| 31                 | DeSAVE <sup>(2)</sup>                                                                              | Debug Handler Scratchpad register.                                                                                                                                                            |

### TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used in debug.

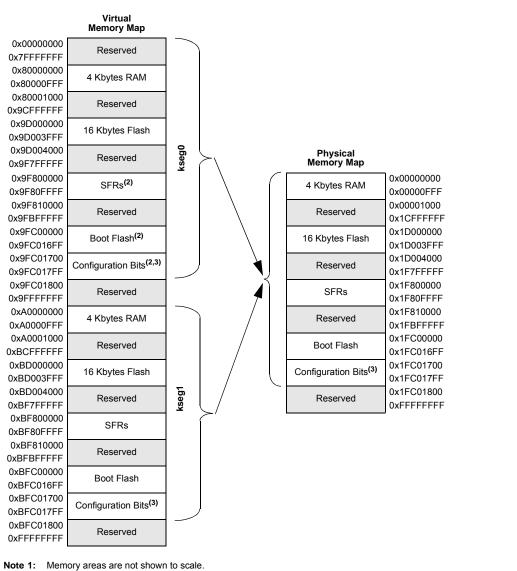

## FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 16 Kbytes OF PROGRAM MEMORY<sup>(1)</sup>

2: This region should be accessed from kseg1 space only.

3: Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768. Refer to Section 4.1 "Alternate Configuration Bits Space" for more information.

## 5.2 Flash Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |          |                                    |       |       |       |       |          | Bi      | ts        |      |      |      |      |      |      |      | 6          |

|-----------------------------|------------------------|-----------|----------|------------------------------------|-------|-------|-------|-------|----------|---------|-----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15    | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8    | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2380                        | NVMCON <sup>(1)</sup>  | 31:16     | _        |                                    |       |       |       |       |          |         |           |      |      |      |      |      |      |      | 0000       |

| 2300                        | INVINCOIN.             | 15:0      | WR       | WREN WRERR LVDERR — — — — — — 0000 |       |       |       |       |          |         |           |      |      |      | 0000 |      |      |      |            |

| 2390                        | NVMKEY                 | 31:16     |          | NVMKEY<31:0>                       |       |       |       |       |          |         |           |      |      |      |      |      |      |      |            |

| 2390                        |                        | 15:0      |          | NVMKEY<31:0>                       |       |       |       |       |          |         |           |      |      |      | 0000 |      |      |      |            |

| 23A0                        | NVMADDR <sup>(1)</sup> | 31:16     |          | NVMADDR<31:0>                      |       |       |       |       |          |         |           |      |      |      | 0000 |      |      |      |            |

| 2370                        | NUMADOR                | 15:0      |          |                                    |       |       |       |       |          | NVINADD | 1(\$01.02 |      |      |      |      |      |      |      | 0000       |

| 23B0                        | NVMDATA0               | 31:16     |          |                                    |       |       |       |       |          | NVMDAT  | A0<31·0>  |      |      |      |      |      |      |      | 0000       |

| 2020                        |                        | 15:0      |          |                                    |       |       |       |       |          |         | 10 101.01 |      |      |      |      |      |      |      | 0000       |

| 23C0                        | NVMDATA1               | 31:16     |          |                                    |       |       |       |       |          | NVMDAT  | A1<31·0>  |      |      |      |      |      |      |      | 0000       |

| 2000                        |                        | 15:0      |          |                                    |       |       |       |       |          |         | 11.01.0   |      |      |      |      |      |      |      | 0000       |

| 23D0                        | NVMSRCADDR             | 31:16     |          |                                    |       |       |       |       | N        | VMSRCA  | DDR<31:0  | >    |      |      |      |      |      |      | 0000       |

| 2020                        |                        | 15:0      |          |                                    |       |       |       |       |          |         |           |      |      |      |      |      |      |      | 0000       |

| 23E0                        | NVMPWP <sup>(1)</sup>  | 31:16     | PWPULOCK | WPULOCK — — — — PWP<23:16> 8000    |       |       |       |       |          |         |           |      |      | 8000 |      |      |      |      |            |

| -0-0                        |                        | 15:0      |          |                                    |       |       |       |       |          | PWP<    | 15:0>     |      |      |      |      |      |      |      | 0000       |

| 23F0                        | NVMBWP <sup>(1)</sup>  | 31:16     | —        | —                                  | —     | —     | _     | _     |          | _       | _         | _    | —    | _    | _    | _    | _    | —    | 0000       |

| 2010                        |                        | 15:0      | BWPULOCK | _                                  | _     | —     | —     |       | BWP<2:0> |         | _         | _    | —    | _    | _    | _    | _    | —    | 8700       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 31:24        |                   | NVMKEY<31:24>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 23:16        |                   |                   |                   | NVMKE             | Y<23:16>          |                   |                  |                  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 15:8         |                   |                   |                   | NVMKE             | EY<15:8>          |                   |                  |                  |  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMK              | NVMKEY<7:0>       |                   |                  |                  |  |  |  |  |  |

#### REGISTER 5-2: NVMKEY: NVM PROGRAMMING UNLOCK REGISTER

## Legend:

| Legenu.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-0 NVMKEY<31:0>: NVM Unlock Register bits

These bits are write-only and read as '0' on any read.

### REGISTER 5-3: NVMADDR: NVM FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0 R/    |                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        |                   | NVMADDR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        |                   | NVMADDR<23:16>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | NVMAD             | DR<15:8>          |                   |                  |                  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMAD             | )DR<7:0>          |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-0 NVMADDR<31:0>: NVM Flash Address bits

| NVMOP<3:0><br>Selection | Flash Address Bits (NVMADDR<31:0>)                                                      |

|-------------------------|-----------------------------------------------------------------------------------------|

| Page Erase              | Address identifies the page to erase (NVMADDR<10:0> are ignored).                       |

| Row Program             | Address identifies the row to program (NVMADDR<7:0> are ignored).                       |

| Double-Word Program     | Address identifies the double-word (64-bit) to program (NVMADDR<1:0> bits are ignored). |

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(3)</sup>

- 111 and 110 = Reserved (selects internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV))

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (SOSC)

- 011 = Reserved

- 010 = Primary Oscillator (POSC) (XT, HS or EC)

- 001 = System PLL (SPLL)

- 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (FOSCSEL<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

- bit 6-5 Unimplemented: Read as '0'

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 CF: Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- bit 2 Unimplemented: Read as '0'

- bit 1 SOSCEN: Secondary Oscillator (SOSC) Enable bit<sup>(4)</sup>

- 1 = Enables Secondary Oscillator

- 0 = Disables Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit<sup>(2)</sup>

- 1 = Initiates an oscillator switch to a selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: The Reset value for this bit depends on the setting of the IESO (FOSCSEL<7>) Configuration bit. When IESO = 1, the Reset value is '1'. When IESO = 0, the Reset value is '0'.

- **3:** The Reset value for these bits matches the setting of the FNOSC<2:0> (FOSCSEL<2:0>) Configuration bits.

- 4: The Reset value for this bit matches the setting of the SOSCEN (FOSCSEL<6>) Configuration bit.

### REGISTER 12-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER (CONTINUED)

- bit 14 ASDGM: CCPx Auto-Shutdown Gate Mode Enable bit

- 1 = Waits until the next Time Base Reset or rollover for shutdown to occur

- 0 = Shutdown event occurs immediately

- bit 13 Unimplemented: Read as '0'

- bit 12 SSDG: CCPx Software Shutdown/Gate Control bit

- 1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting the ASDGM bit still applies)

- 0 = Normal module operation

- bit 11-8 Unimplemented: Read as '0'

- bit 7-0 ASDG<7:0>: CCPx Auto-Shutdown/Gating Source Enable bits

- 1xxx xxxx = Auto-shutdown is controlled by the OCFB pin (remappable)

- x1xx xxxx = Auto-shutdown is controlled by the OCFA pin (remappable)

- xx1x xxxx = Auto-shutdown is controlled by CLC1 for MCCP1/SCCP2 and by CLC2 for SCCP3

- xxx1 xxxx = Auto-shutdown is controlled by the SCCP2 output for MCCP1 and by MCCP1 for SCCP2/SCCP3

- xxxx 1xxx = Auto-shutdown is controlled by the SCCP3 output for MCCP1/SCCP2 and by SCCP2 for SCCP3

- xxxx x1xx = Reserved

- xxxx xx1x = Auto-shutdown is controlled by Comparator 2

- xxxx xxx1 = Auto-shutdown is controlled by Comparator 1

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

#### REGISTER 18-2: CLCxSEL: CLCx INPUT MUX SELECT REGISTER (CONTINUED)

bit 10-8 DS3<2:0>: Data Selection MUX 3 Signal Selection bits

#### For CLC1:

- 111 = SCCP3 compare match event

- 110 = SCCP2 compare match event

- 101 = SCCP2 OCM2 output

- 100 = UART1 RX input

- 011 = SPI1 SDO output

- 010 = Comparator 2 output

- 001 = CLC1 output

- 000 = CLCINA I/O pin

#### For CLC2:

- 111 = SCCP3 compare match event

- 110 = SCCP2 compare match event

- 101 = SCCP2 OCM2 output

- 100 = UART2 RX input

- 011 = SPI2 SDO output

- 010 = Comparator 2 output

- 001 = CLC2 output

- 000 = CLCINA I/O pin

- bit 7 Unimplemented: Read as '0'

- bit 6-4 DS2<2:0>: Data Selection MUX 2 Signal Selection bits

#### For CLC1:

- 111 = Reserved

- 110 = MCCP1 compare match event

- 101 = Reserved

- 100 = ADC End-of-Conversion (EOC) event

- 011 = UART1 TX output

- 010 = Comparator 1 output

- 001 = CLC2 output

- 000 = CLCINB I/O pin

#### For CLC2:

- 111 = Reserved

- 110 = MCCP1 compare match event

- 101 = Reserved

- 100 = ADC End-of-Conversion event

- 011 = UART2 TX output

- 010 = Comparator 1 output

- 001 = CLC1 output

- 000 = CLCINB I/O pin

#### bit 3 Unimplemented: Read as '0'

- bit 2-0 DS1<2:0>: Data Selection MUX 1 Signal Selection bits

- 111 = MCCP1 OCM1C output

- 110 = MCCP1 OCM1B output

- 101 = MCCP1 OCM1A output

- 100 = REFCLKO output

- 011 = LPRC clock source

- 010 = SOSC clock source

- 001 = System clock (FSYS)

- 000 = CLCINA I/O pin

## 20.1 CDAC Control Registers

## TABLE 20-1: CDAC REGISTER MAP

| ess                       |                                 | Jge   |       |       |       |       |       |       |      | Bits  |      |      |      |      |      |          |       |        | 6         |

|---------------------------|---------------------------------|-------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|------|----------|-------|--------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> |       | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2     | 17/1  | 16/0   | All Reset |

| 0000                      | DACICON                         | 31:16 | _     | —     | —     | _     | _     | —     | _    | -     | —    | —    | —    |      | D    | ACDAT<4: | 0>    |        | 0000      |

| 0980                      | DAC1CON                         | 15:0  | ON    |       | —     |       |       | _     |      | DACOE |      | _    | —    | _    | —    | _        | REFSE | L<1:0> | 0000      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively.

## TABLE 22-3: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                                             | Ċ,        |       |       |       |        |         |        |        | Bits   |      |      |      |        |       |      |        |        |            |

|-----------------------------|-------------------------------------------------------------|-----------|-------|-------|-------|--------|---------|--------|--------|--------|------|------|------|--------|-------|------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Virtual Addr<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11   | 26/10  | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4   | 19/3  | 18/2 | 17/1   | 16/0   | All Resets |

| 2C00                        | PMDCON                                                      | 31:16     | —     | -     |       | _      | _       | _      |        | _      |      |      | —    |        | _     |      | —      | _      | 0000       |

| 2000                        | FINDCON                                                     | 15:0      | —     | _     | —     | —      | PMDLOCK | —      | —      | —      | -    | —    | —    | —      | —     | _    | —      | —      | 0000       |

| 2C10                        | PMD1                                                        | 31:16     | —     | _     | —     | —      | —       | —      | —      | —      | -    | —    | —    | HLVDMD | —     | _    | —      | —      | FFEF       |

| 2010                        | FINIDT                                                      | 15:0      | _     |       |       | VREFMD | —       | —      |        | —      |      |      | —    |        | _     |      | —      | ADCMD  | EFFE       |

| 2C20                        | PMD2                                                        | 31:16     | _     |       |       | _      | —       | —      | CLC2MD | CLC1MD |      |      | —    |        | _     |      | —      | _      | FCFF       |

| 2020                        | FINDZ                                                       | 15:0      | _     |       |       | _      | —       | —      |        | —      |      |      | —    |        | _     |      | CMP2MD | CMP1MD | FFFC       |

| 2C30                        | PMD3                                                        | 31:16     | _     |       |       | _      | —       | —      |        | —      |      |      | —    |        | _     |      | —      | _      | FFFF       |

| 2030                        | FIND3                                                       | 15:0      | _     |       |       | _      | —       | CCP3MD | CCP2MD | CCP1MD |      |      | —    |        | _     |      | —      | _      | F8FF       |

| 2C40                        | PMD4                                                        | 31:16     | _     |       |       | _      | —       | —      |        | —      |      |      | —    |        | _     |      | —      | _      | FFFF       |

| 2040                        | FIVID4                                                      | 15:0      | _     |       |       | _      | —       | —      |        | —      |      |      | —    |        | _     |      | —      | T1MD   | FFFE       |

| 2C50                        | PMD5                                                        | 31:16     | _     |       |       | _      | —       | —      |        | —      |      |      | —    |        | _     |      | r      | r      | FFFC       |

| 2000                        | FINDS                                                       | 15:0      | —     | —     | _     | —      | —       | —      | SPI2MD | SPI1MD | _    | _    | —    | _      | —     | _    | U2MD   | U1MD   | FCFC       |

| 2C60                        | PMD6                                                        | 31:16     | —     | _     | —     | —      | —       | —      | —      | —      | -    | —    | —    | —      | —     | _    | —      | —      | FFFF       |

| 2000                        | FIVIDO                                                      | 15:0      | _     |       |       | _      | _       | _      |        | REFOMD |      |      | _    |        | _     |      | _      | RTCCMD | FEFE       |

| 2C70                        | PMD7                                                        | 31:16     | _     | -     |       | —      | —       | _      |        | _      | _    |      | -    |        | _     | _    | -      | —      | FFFF       |

| 2070                        |                                                             | 15:0      | _     | -     |       | —      | —       | _      |        | _      | _    |      | -    |        | CRCMD | _    | -      | —      | FFF7       |

Legend: — = unimplemented, read as '1'; r = reserved bit, maintain as '1'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

## TABLE 23-5: RAM CONFIGURATION, DEVICE ID AND SYSTEM LOCK REGISTERS MAP

| ess                         |                  | Bits      |       |          |       |       |       | (1)   |           |        |               |           |      |      |        |      |      |      |                          |

|-----------------------------|------------------|-----------|-------|----------|-------|-------|-------|-------|-----------|--------|---------------|-----------|------|------|--------|------|------|------|--------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14    | 29/13 | 28/12 | 27/11 | 26/10 | 25/9      | 24/8   | 23/7          | 22/6      | 21/5 | 20/4 | 19/3   | 18/2 | 17/1 | 16/0 | All Resets <sup>(1</sup> |

| 2000                        | 050001           | 31:16     | _     | _        | —     | _     | —     | —     | -         | —      | EXECADDR<7:0> |           |      |      | 0000   |      |      |      |                          |

| 3B00                        | CFGCON           | 15:0      |       | _        | _     | _     | _     | _     | _         | _      | _             | _         | _    | _    | JTAGEN | _    | _    | _    | 000x                     |

| 3B20                        | DEVID            | 31:16     |       | VER      | <3:0> |       |       |       |           |        |               | ID<27:16> |      |      |        |      |      | xxxx |                          |

| 3620                        | DEVID            | 15:0      |       | ID<15:0> |       |       |       |       | .15:0> :: |        |               |           |      |      | xxxx   |      |      |      |                          |

| 3B30                        | SYSKEY           | 31:16     |       |          |       |       |       |       |           | SYSKEY | <31.0>        |           |      |      |        |      |      |      | 0000                     |

| 3630                        | STOKET           | 15:0      |       |          |       |       |       |       |           | STORET | <31.02        |           |      |      |        |      |      |      | 0001                     |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the device variant.

## PIC32MM0064GPL036 FAMILY

## REGISTER 23-10: ANCFG: BAND GAP CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | —                 |                   | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                 |                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 |                   | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS, HC     | R/W-0, HS, HC    | U-0              |

| 7:0          | _                 |                   | _                 |                   |                   | VBGADC            | VBGCMP           | _                |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

- bit 2 **VBGADC:** ADC Band Gap Enable bit

- 1 = ADC band gap is enabled

- 0 = ADC band gap is disabled

bit 1 **VBGCMP:** Comparator Band Gap Enable bit

- 1 = Comparator band gap is enabled

- 0 = Comparator band gap is disabled

- bit 0 Unimplemented: Read as '0'

## TABLE 26-22: RESET, BROWN-OUT RESET AND SLEEP MODES TIMING SPECIFICATIONS

| Operati      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                         |     |                    |     |       |                                                          |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|--------------------|-----|-------|----------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                          | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                               |  |  |  |  |

| SY10         | TMCL                                                                                                                    | MCLR Pulse Width (Low)                                  | 2   | —                  | _   | μs    |                                                          |  |  |  |  |

| SY13         | Tioz                                                                                                                    | I/O High-Impedance from<br>MCLR Low                     | _   | 1                  | _   | μs    |                                                          |  |  |  |  |

| SY25         | TBOR                                                                                                                    | Brown-out Reset Pulse<br>Width                          | 1   | —                  | —   | μs    | $VDD \leq VBOR$                                          |  |  |  |  |

| SY45         | TRST                                                                                                                    | Reset State Time                                        | _   | 25                 | _   | μs    |                                                          |  |  |  |  |

| SY71         | Twake <sup>(2)</sup>                                                                                                    | Wake-up Time with Main<br>Voltage Regulator             | _   | 22                 | _   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 0,<br>RETVR = 1 |  |  |  |  |

|              |                                                                                                                         |                                                         | _   | 3.8                | —   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 0,<br>RETVR = 1 |  |  |  |  |

| SY72         | Twakelvr <sup>(2)</sup>                                                                                                 | Wake-up Time with<br>Retention Low-Voltage<br>Regulator | _   | 163                | —   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 1,<br>RETVR = 0 |  |  |  |  |

|              |                                                                                                                         |                                                         |     | 23                 | _   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 1,<br>RETVR = 0 |  |  |  |  |

**Note 1:** Data in the "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The parameters are measured with the external clock source (EC). To get the full wake-up time, the oscillator start-up time must be added.

## 27.0 PACKAGING INFORMATION

## 27.1 Package Marking Information

20-Lead SSOP

Example PIC32MM0016 GPL020 \$ 1610017 ()

20-Lead QFN

## Example 32MM0016 GPL020 1610017

### 28-Lead SPDIP

## 28-Lead SOIC (7.5 mm)

Example

## Example

| Legend: | XXX       | Customer-specific information                                                                                                                                               |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | ΥY        | Year code (last 2 digits of calendar year)                                                                                                                                  |

|         | WW        | Week code (week of January 1 is week '01')                                                                                                                                  |

|         | NNN       | Alphanumeric traceability code                                                                                                                                              |

|         | *         | All packages are Pb-free                                                                                                                                                    |

| ł       | be carrie | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information. |

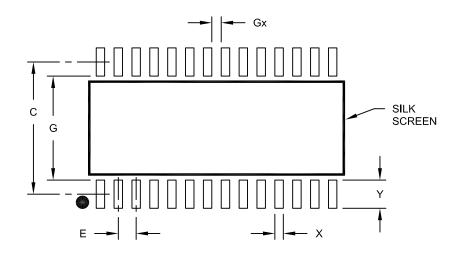

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension                | Limits      | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E           |      | 1.27 BSC |      |  |

| Contact Pad Spacing      | С           |      | 9.40     |      |  |

| Contact Pad Width (X28)  | X           |      |          | 0.60 |  |

| Contact Pad Length (X28) | Y           |      |          | 2.00 |  |

| Distance Between Pads    | Gx          | 0.67 |          |      |  |

| Distance Between Pads    | G           | 7.40 |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: