Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MM0064GPL036 FAMILY

#### **Pin Diagrams (Continued)** RP15/RB1/PGEC1 RP14/RB0/PGED1 40-Pin UQFN RP10/RB15<sup>(1)</sup> **RP9**/RB14 **RP1**/RA0 **RP2**/RA1 MCLR AVDD AVSS N N 35<u>∏</u> 33] 39 <del>6</del> 38 37 36 34 32 33 RP16/RB2 30 **RP13**/RB13 1 RB3 2 29 **RP12**/RB12 28 RP18/RB11/PGEC2 RC0 3 RC1 27 RP17/RB10/PGED2 4 26 VDD RC2 5 PIC32MMXXXXGPL036 25 N/C Vss 🛛 6 OSCI/RP3/RA2 7 24 VCAP OSCO/**RP4**/RA3<sup>(1)</sup> 23 N/C SOSCI/RP5/RB4 9 22 **RP19**/RC9 21 RC8 SOSCO/RP6/RA4 10 20 RP20/RA9 RC3 Vss NC VDD RB6/PGEC3 RB5/PGED3 **RP11**/RB7 RP7/RB8<sup>(1)</sup> RP8/RB9<sup>(1)</sup> Legend: Shaded pins are up to 5V tolerant. Note 1: Pin has an increased current drive strength. Refer to Section 26.0 "Electrical Characteristics" for details.

# TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 40-PIN UQFN DEVICES

| Pin | Function                                                                                                   | Pin | Function                                                            |

|-----|------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                                                                                | 21  | RC8                                                                 |

| 2   | AN11/C1INA/RB3                                                                                             | 22  | RP19/RC9                                                            |

| 3   | AN12/RC0                                                                                                   | 23  | N/C                                                                 |

| 4   | AN13/RC1                                                                                                   | 24  | VCAP                                                                |

| 5   | RC2                                                                                                        | 25  | N/C                                                                 |

| 6   | Vss                                                                                                        | 26  | Vdd                                                                 |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                                                                | 27  | PGED2/TDO/ <b>RP17</b> /RB10                                        |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>                                                        | 28  | PGEC2/TDI/ <b>RP18</b> /RB11                                        |

| 9   | SOSCI/ <b>RP5</b> /RB4                                                                                     | 29  | AN7/LVDIN/ <b>RP12</b> /RB12                                        |

| 10  | SOSCO/SCLKI/RP6/PWRLCLK/RA4                                                                                | 30  | AN8/ <b>RP13</b> /RB13                                              |

| 11  | <b>RP20</b> /RA9                                                                                           | 31  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14               |

| 12  | Vss                                                                                                        | 32  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup> |

| 13  | VDD                                                                                                        | 33  | AVss                                                                |

| 14  | RC3                                                                                                        | 34  | AVDD                                                                |

| 15  | PGED3/RB5                                                                                                  | 35  | MCLR                                                                |

| 16  | PGEC3/RB6                                                                                                  | 36  | VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                               |

| 17  | <b>RP11</b> /RB7                                                                                           | 37  | VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                    |

| 18  | TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                       | 38  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                             |

| 19  | N/C                                                                                                        | 39  | PGEC1/AN3/C1INC/C2INA/RP15/RB1                                      |

| 20  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <mark>U1RTS</mark> /U1BCLK/SDO1/<br>C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> | 40  | N/C                                                                 |

Note 1: Pin has an increased current drive strength.

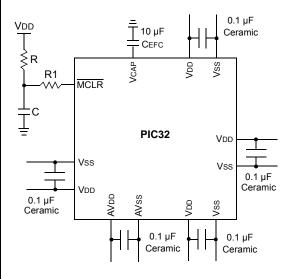

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

# 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

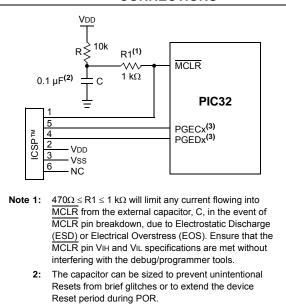

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS<sup>(1,2,3)</sup>

**<sup>3:</sup>** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

# 2.4 Capacitor on Internal Voltage Regulator (VCAP)

A low-ESR (<1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. The recommended value of the CEFC capacitor is 10  $\mu$ F. On the printed circuit board, it should be placed as close to the VCAP pin as possible. If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to this capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | IFS<31:24>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | IFS<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | IFS<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | IFS<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 7-5: IFSx: INTERRUPT FLAG STATUS REGISTER x<sup>(1)</sup>

| Legend:           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-0 IFS<31:0>: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

**Note 1:** This register represents a generic definition of the IFSx register. Refer to Table 7-3 for the exact bit definitions.

# **REGISTER 7-6:** IECx: INTERRUPT ENABLE CONTROL REGISTER x<sup>(1)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | IEC<31:24>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | IEC<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | IEC<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | IEC<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |  |  |  |  |

|-------------------|------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

bit 31-0 **IEC<31-0>:** Interrupt Enable bits 1 = Interrupt is enabled 0 = Interrupt is disabled

**Note 1:** This register represents a generic definition of the IECx register. Refer to Table 7-3 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

#### **REGISTER 8-4: REFO1TRIM: REFERENCE OSCILLATOR TRIM REGISTER**<sup>(1,2,3)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

- bit 22-0 Unimplemented: Read as '0'

- **Note 1:** While the ON bit (REFO1CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- Do not write to this register when the ON bit (REFO1CON<15>) is not equal to the ACTIVE bit (REFO1CON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> (REFO1CON<30:16>) = 0.

# REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 23    | MCLKSEL: Master Clock Enable bit <sup>(1)</sup>                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = REFCLKO is used by the Baud Rate Generator</li> <li>0 = PBCLK is used by the Baud Rate Generator (1:1 with SYSCLK)</li> </ul>                                                                                                         |

| bit 22-18 | Unimplemented: Read as '0'                                                                                                                                                                                                                         |

| bit 17    | SPIFE: SPIx Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                                                                |

|           | <ul> <li>1 = Frame synchronization pulse coincides with the first bit clock</li> <li>0 = Frame synchronization pulse precedes the first bit clock</li> </ul>                                                                                       |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(1)</sup>                                                                                                                                                                                                  |

|           | <ul><li>1 = Enhanced Buffer mode is enabled</li><li>0 = Enhanced Buffer mode is disabled</li></ul>                                                                                                                                                 |

| bit 15    | ON: SPIx Module On bit                                                                                                                                                                                                                             |

|           | <ul><li>1 = SPIx module is enabled</li><li>0 = SPIx module is disabled</li></ul>                                                                                                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                         |

| bit 13    | SIDL: SPIx Stop in Idle Mode bit                                                                                                                                                                                                                   |

|           | <ul> <li>1 = Discontinues operation when CPU enters Idle mode</li> <li>0 = Continues operation in Idle mode</li> </ul>                                                                                                                             |

| bit 12    | DISSDO: Disable SDOx Pin bit <sup>(4)</sup>                                                                                                                                                                                                        |

|           | <ul> <li>1 = SDOx pin is not used by the module; the pin is controlled by the associated PORTx register</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                                               |

| bit 11-10 | MODE<32,16>: 32/16/8-Bit Communication Select bits                                                                                                                                                                                                 |

|           | When AUDEN = 1:                                                                                                                                                                                                                                    |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |

|           | 1124-bit data, 32-bit FIFO, 32-bit channel/64-bit frame1032-bit data, 32-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                     |

|           | 0 1 16-bit data, 16-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                                                                          |

|           | 0 0 16-bit data, 16-bit FIFO, 16-bit channel/32-bit frame                                                                                                                                                                                          |

|           | When AUDEN = 0:                                                                                                                                                                                                                                    |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                                                                           |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                                                                   |

| bit 9     | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                                              |

|           | Master mode (MSTEN = 1):                                                                                                                                                                                                                           |

|           | <ul> <li>1 = Input data is sampled at the end of data output time</li> <li>0 = Input data is sampled at the middle of data output time</li> </ul>                                                                                                  |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                                                                            |

|           | SMP value is ignored when SPIx is used in Slave mode. The module always uses SMP = 0.                                                                                                                                                              |

| bit 8     | <b>CKE:</b> SPIx Clock Edge Select bit <sup>(2)</sup>                                                                                                                                                                                              |

|           | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)</li> </ul> |

| Note 1:   | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                            |

| 2:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                          |

| 3:        | When AUDEN = 1, the SPI/I <sup>2</sup> S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.                                                                                                        |

| 4:        | These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see <b>Section 9.8</b> " <b>Peripheral Pin Select (PPS)</b> " for more information).                                                     |

# 14.1 UART Control Registers

# TABLE 14-1: UART1 AND UART2 REGISTER MAP

| ess                         |                         |           |                                   |         |        |         |          |       |       | E          | lits        |         |       |            |             |       |        |        |            |

|-----------------------------|-------------------------|-----------|-----------------------------------|---------|--------|---------|----------|-------|-------|------------|-------------|---------|-------|------------|-------------|-------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name        | Bit Range | 31/15                             | 30/14   | 29/13  | 28/12   | 27/11    | 26/10 | 25/9  | 24/8       | 23/7        | 22/6    | 21/5  | 20/4       | 19/3        | 18/2  | 17/1   | 16/0   | All Resets |

| 0600                        | U1MODE <sup>(1)</sup>   | 31:16     |                                   | _       | —      | _       | _        | _     |       | —          | SLPEN       | ACTIVE  | _     | _          | -           | CLKSE | L<1:0> | OVFDIS | 0000       |

| 0000                        |                         | 15:0      | ON                                | -       | SIDL   | IREN    | RTSMD    | —     | UEN≤  | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV      | BRGH        | PDSE  | L<1:0> | STSEL  | 0000       |

| 0610                        | U1STA <sup>(1)</sup>    | 31:16     |                                   |         |        | UART1 M | ASK<7:0> |       |       |            |             |         |       | UART1 AD   | DR<7:0>     |       |        |        | 0000       |

| 0010                        | UISIA                   | 15:0      | UTXISE                            | L<1:0>  | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE      | PERR        | FERR  | OERR   | URXDA  | 0110       |

| 0620                        | U1TXREG                 | 31:16     | —                                 |         | —      |         |          |       |       | _          |             | —       | _     | _          |             | —     | _      | _      | 0000       |

| 0020                        | UTIAREG                 | 15:0      | —                                 |         | —      |         |          |       |       | TX8        |             |         | U     | ART1 Trans | mit Registe | er    |        |        | 0000       |

| 0630                        | U1RXREG                 | 31:16     | —                                 |         | —      |         |          |       |       | _          |             | —       | _     | _          |             | —     | _      | _      | 0000       |

|                             |                         | 15:0      | —                                 |         | —      |         |          |       |       | RX8        |             |         | U.    | ART1 Rece  | ive Registe | er    |        |        | 0000       |

| 0640                        | U1BRG <sup>(1)</sup>    | 31:16     | —                                 |         | _      |         |          |       |       | _          |             | _       | _     | _          |             | _     | —      | _      | 0000       |

| 0040                        | UIBKG.                  | 15:0      | 5:0 Baud Rate Generator Prescaler |         |        |         |          |       |       |            |             | 0000    |       |            |             |       |        |        |            |

| 0680                        | U2MODE <sup>(1)</sup>   | 31:16     | —                                 | -       | —      | —       | —        | —     | _     | —          | SLPEN       | ACTIVE  | —     | —          | _           | CLKSE | L<1:0> | OVFDIS | 0000       |

| 0000                        | UZIVIODE <sup>(</sup> ) | 15:0      | ON                                |         | SIDL   | IREN    | RTSMD    |       | UEN∙  | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV      | BRGH        | PDSE  | L<1:0> | STSEL  | 0000       |

| 0690                        | U2STA <sup>(1)</sup>    | 31:16     |                                   |         |        | UART2 M | ASK<7:0> |       |       |            |             |         |       | UART2 AD   | DR<7:0>     |       |        |        | 0000       |

| 0090                        | 0231A.7                 | 15:0      | UTXISE                            | EL<1:0> | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE      | PERR        | FERR  | OERR   | URXDA  | 0110       |

| 06A0                        | U2TXREG                 | 31:16     | —                                 |         | —      |         |          |       |       | _          |             | —       | _     | _          |             | —     | _      | _      | 0000       |

| UOAU                        | UZIAREG                 | 15:0      | —                                 |         | —      |         |          |       |       | TX8        |             |         | U     | ART2 Trans | mit Registe | er    |        |        | 0000       |

| 06B0                        | U2RXREG                 | 31:16     |                                   |         | —      |         |          | _     |       |            |             | —       | _     | _          |             | —     | _      |        | 0000       |

| 0080                        | UZKAREG                 | 15:0      |                                   |         | —      |         |          | _     |       | RX8        |             |         | U     | ART2 Rece  | ive Registe | er    |        |        | 0000       |

| 06C0                        | U2BRG <sup>(1)</sup>    | 31:16     |                                   |         | —      |         |          | _     |       |            |             | —       | _     | _          |             | —     | _      |        | 0000       |

| 0000                        | UZBRG''                 | 15:0      |                                   |         |        |         |          |       | Bau   | d Rate Ger | nerator Pre | scaler  |       |            |             |       |        |        | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### REGISTER 14-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits 11 = Reserved                                                                                                                                                                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full</li> <li>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full</li> <li>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</li> </ul> |

| bit 5   | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                          |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                        |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Data is being received</li></ul>                                                                                                                                                                                                                                   |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                            |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                          |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit                                                                                                                                                                                                                                                               |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to the empty state.<br>1 = Receive buffer has overflowed<br>0 = Receive buffer has not overflowed                                                              |

| bit 0   | URYDA: LIARTy Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                 |

- bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | DIV<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DIV<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         |                   |                   | FDIV<4:0>         |                   | -                 | _                 | _                |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | _                 | CLKSE             | CLKSEL<1:0>       |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 15-2: RTCCON2: RTCC CONTROL 2 REGISTER

#### Legend:

| 3                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 DIV<15:0>: Clock Divide bits

Sets the period of the clock divider counter; value should cause a nominal 1/2 second underflow.

bit 15-11 FDIV<4:0>: Fractional Clock Divide bits

11111 = Clock period increases by 31 RTCC input clock cycles every 16 seconds

11101 = Clock period increases by 30 RTCC input clock cycles every 16 seconds

...

00010 = Clock period increases by 2 RTCC input clock cycles every 16 seconds

00001 = Clock period increases by 1 RTCC input clock cycle every 16 seconds

00000 = No fractional clock division

#### bit 10-2 Unimplemented: Read as '0'

- bit 1-0 CLKSEL<1:0>: Clock Select bits

- 11 = Peripheral clock (FCY)

- 10 = PWRLCLK input pin

- 01 = LPRC

- 00 = SOSC

|  | REGISTER 16-7: | AD1CHIT: ADC COMPARE HIT REGISTER |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5          | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|----------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | —                 | _                 |                            | _                 | -                 | _                 | _                | —                |  |  |

| 00.10     | U-0               | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | —                 | _                 |                            | -                 |                   | _                 | -                | —                |  |  |

| 45.0      | U-0               | U-0               | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | —                 | _                 | CHH<13:8> <sup>(1,2)</sup> |                   |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       |                   |                   |                            | CHH<7             | /:0>              |                   |                  |                  |  |  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13-0 CHH<13:0>: ADC Compare Hit bits<sup>(1,2)</sup>

If CM<1:0> = 11:

1 = ADC Result Buffer x has been written with data or a match has occurred

0 = ADC Result Buffer x has not been written with data

- For All Other Values of CM<1:0>:

- 1 = A match has occurred on ADC Result Channel n

- 0 = No match has occurred on ADC Result Channel n

Note 1: The CHH<13:11> bits are not implemented in 20-pin devices.

2: The CHH<13:12> bits are not implemented in 28-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                 | —                 | -                 | —                 | —                 | —                 | -                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | _                 |                   | -                 | -                 | -                 |                  | _                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | —                 | _                 |                   | -                 | -                 | -                 |                  | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 7:0          |                   |                   |                   |                   | LPBOREN           | RETVR             | BORE             | N<1:0>           |

#### REGISTER 23-3: FPOR/AFPOR: POWER-UP SETTINGS CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit |                                    |  |  |  |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |  |

- bit 31-4 **Reserved:** Program as '1'

- bit 3 LPBOREN: Low-Power BOR Enable bit

- 1 = Low-Power BOR is enabled when the main BOR is disabled 0 = Low-Power BOR is disabled

- bit 2 **RETVR:** Retention Voltage Regulator Enable bit

- 1 = Retention regulator is disabled

- 0 = Retention regulator is enabled and controlled by the RETEN bit during Sleep

- bit 1-0 **BOREN<1:0>:** Brown-out Reset Enable bits

- 11 = Brown-out Reset is enabled in hardware; SBOREN bit is disabled

- 10 = Brown-out Reset is enabled only while device is active and is disabled in Sleep; SBOREN bit is disabled

- 01 = Brown-out Reset is controlled with the SBOREN bit setting

- 00 = Brown-out Reset is disabled in hardware; SBOREN bit is disabled

# REGISTER 23-8: DEVID: DEVICE ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|--------------------------|-------------------|---------------------|-------------------|--------------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R-x                      | R-x               | R-x                 | R-x               | R-x                      | R-x               | R-x              | R-x              |  |  |  |  |  |

| 31:24        |                          | VER<3             | 3:0> <sup>(1)</sup> |                   | ID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |

| 00.40        | R-x R-x                  |                   | R-x R-x             |                   | R-x                      | R-x               | R-x              | R-x              |  |  |  |  |  |

| 23:16        | ID<23:16> <sup>(1)</sup> |                   |                     |                   |                          |                   |                  |                  |  |  |  |  |  |

| 45.0         | R-x                      | R-x               | R-x                 | R-x               | R-x                      | R-x               | R-x              | R-x              |  |  |  |  |  |

| 15:8         | ID<15:8> <sup>(1)</sup>  |                   |                     |                   |                          |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-x R-x                  |                   | R-x R-x             |                   | R-x R-x                  |                   | R-x              | R-x              |  |  |  |  |  |

| 7:0          |                          |                   |                     | ID<7:(            | )>(1)                    |                   |                  |                  |  |  |  |  |  |

| Legend: | L | eg | er | ۱d | : |

|---------|---|----|----|----|---|

|---------|---|----|----|----|---|

.

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID bits<sup>(1)</sup>

Note 1: Reset values are dependent on the device variant.

#### REGISTER 23-9: SYSKEY: SYSTEM UNLOCK REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |     |     |     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------------|-----|-----|-----|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | W-0                              | W-0 | W-0 | W-0 | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 31:24        | SYSKEY<31:24>                    |     |     |     |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | W-0                              | W-0 | W-0 | W-0 | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 23:16        | SYSKEY<23:16>                    |     |     |     |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | W-0                              | W-0 | W-0 | W-0 | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 15:8         | SYSKEY<15:8>                     |     |     |     |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | W-0 W-0                          |     | W-0 | W-0 | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 7:0          | SYSKEY<7:0>                      |     |     |     |                   |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 SYSKEY<31:0>: Unlock and Lock Key bits

# TABLE 23-6: BAND GAP REGISTER MAP

| ess                       | ο                    | đ         | Bits  |       |       |       |       |       |      |      |      |      |      | s    |      |        |        |      |            |

|---------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|--------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1   | 16/0 | All Resets |

| 2200                      | ANCFG <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | _    | —    | —      | _      | _    | 0000       |

| 2300                      | ANCEG                | 15:0      |       | _     | —     | —     | _     | _     | _    | _    |      | _    | -    | _    | —    | VBGADC | VBGCMP | _    | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| <b>Operating Conditions:</b> $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |                        |      |       |      |               |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------|------|-------|------|---------------|--|--|--|

| Parameter No.                                                                             | Typical <sup>(1)</sup> | Max  | Units | Vdd  | Conditions    |  |  |  |

| DC40                                                                                      | 0.26                   | 0.46 | mA    | 2.0V | Fsys = 1 MHz  |  |  |  |

|                                                                                           | 0.26                   | 0.46 | mA    | 3.3V |               |  |  |  |

| DC41                                                                                      | 0.85                   | 1.5  | mA    | 2.0V |               |  |  |  |

|                                                                                           | 0.85                   | 1.5  | mA    | 3.3V | Fsys = 8 MHz  |  |  |  |

| DC42                                                                                      | 2.3                    | 3.7  | mA    | 2.0V | Fsys = 25 MHz |  |  |  |

|                                                                                           | 2.3                    | 3.7  | mA    | 3.3V |               |  |  |  |

| DC44                                                                                      | 0.18                   | 0.34 | mA    | 2.0V | Fsys = 32 kHz |  |  |  |

|                                                                                           | 0.18                   | 0.34 | mA    | 3.3V |               |  |  |  |

# TABLE 26-5: IDLE CURRENT (IIDLE)<sup>(2)</sup>

**Note 1:** Data in the "Typical" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Base IIDLE current is measured with:

- Oscillator is configured in EC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 010 and POSCMOD<1:0> (FOSCSEL<9:8>) = 00)

- + OSC1 pin is driven with external square wave with levels from 0.3V to VDD 0.3V

- OSC2 is configured as I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- All I/O pins (excepting OSC1) are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

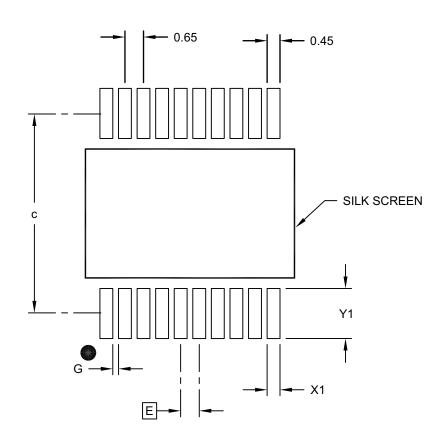

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X20)  | X1          |          |      | 0.45 |

| Contact Pad Length (X20) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B

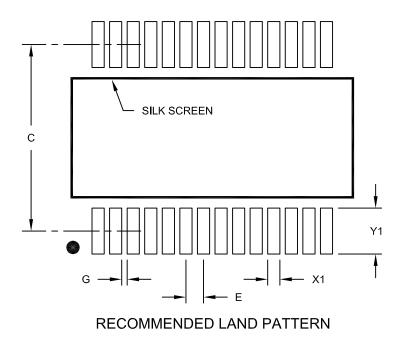

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |      |      |  |

|--------------------------|-------|-------------|------|------|--|

| Dimension Limits         |       | MIN         | NOM  | MAX  |  |

| Contact Pitch            | E     | 0.65 BSC    |      |      |  |

| Contact Pad Spacing      | С     |             | 7.20 |      |  |

| Contact Pad Width (X28)  | X1    |             |      | 0.45 |  |

| Contact Pad Length (X28) | Y1    |             |      | 1.75 |  |

| Distance Between Pads    | G     | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A