#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 22                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 4K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl028t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

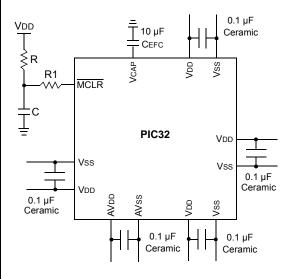

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

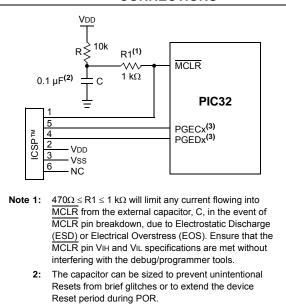

## 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### EXAMPLE OF MCLR PIN CONNECTIONS<sup>(1,2,3)</sup>

**<sup>3:</sup>** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

## 2.4 Capacitor on Internal Voltage Regulator (VCAP)

A low-ESR (<1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. The recommended value of the CEFC capacitor is 10  $\mu$ F. On the printed circuit board, it should be placed as close to the VCAP pin as possible. If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to this capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F.

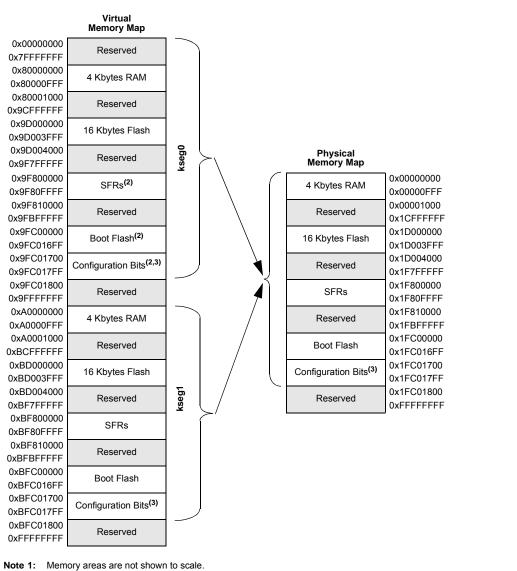

## FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 16 Kbytes OF PROGRAM MEMORY<sup>(1)</sup>

2: This region should be accessed from kseg1 space only.

3: Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768. Refer to Section 4.1 "Alternate Configuration Bits Space" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | IFS<31:24>        |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | IFS<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | IFS<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | IFS<7:0>          |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 7-5: IFSx: INTERRUPT FLAG STATUS REGISTER x<sup>(1)</sup>

| Legend:           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-0 IFS<31:0>: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

**Note 1:** This register represents a generic definition of the IFSx register. Refer to Table 7-3 for the exact bit definitions.

## **REGISTER 7-6:** IECx: INTERRUPT ENABLE CONTROL REGISTER x<sup>(1)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | IEC<31:24>        |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | IEC<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | IEC<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | IEC               | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **IEC<31-0>:** Interrupt Enable bits 1 = Interrupt is enabled 0 = Interrupt is disabled

**Note 1:** This register represents a generic definition of the IECx register. Refer to Table 7-3 for the exact bit definitions.

NOTES:

## TABLE 12-1: MCCP/SCCP REGISTER MAP

| ress                        | 50                              | e         |                      |                     |          |        |         |        |           |       | Bits        |         |         |        |         |          |          |        |               |

|-----------------------------|---------------------------------|-----------|----------------------|---------------------|----------|--------|---------|--------|-----------|-------|-------------|---------|---------|--------|---------|----------|----------|--------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                | 30/14               | 29/13    | 28/12  | 27/11   | 26/10  | 25/9      | 24/8  | 23/7        | 22/6    | 21/5    | 20/4   | 19/3    | 18/2     | 17/1     | 16/0   | All<br>Resets |

|                             |                                 | 31:16     | OPSSRC               | RTRGEN              | _        | _      |         | OPS<   | 3:0>      |       | TRIGEN      | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >        |        | 0000          |

| 0100                        | CCP1CON1                        | 15:0      | ON                   | _                   | SIDL     | CCPSLP | TMRSYNC | C      | LKSEL<2:0 | >     | TMRF        | S<1:0>  | T32     | CCSEL  |         | MOE      | )<3:0>   |        | 0000          |

|                             |                                 | 31:16     | OENSYNC              | _                   | OCFEN    | OCEEN  | OCDEN   | OCCEN  | OCBEN     | OCAEN | ICGS        | M<1:0>  | _       | AUXO   | UT<1:0> |          | ICS<2:0> |        | 0100          |

| 0110                        | CCP1CON2                        | 15:0      | PWMRSEN              | ASDGM               | _        | SSDG   | _       | _      | _         | _     |             |         |         | ASDO   | G<7:0>  |          |          |        | 0000          |

|                             |                                 | 31:16     | OETRIG               | 0                   | SCNT<2:0 | )>     | _       | (      | OUTM<2:0> |       | _           | _       | POLACE  | POLBDF | PSSAC   | E<1:0>   | PSSBD    | F<1:0> | 0000          |

| 0120                        | CCP1CON3                        | 15:0      | _                    | _                   |          | _      | _       | _      | _         | _     | _           | _       |         |        | DT<     | <5:0>    |          |        | 0000          |

| 0400                        | 00040747                        | 31:16     | _                    | _                   | _        | _      | —       | _      | _         | _     | _           |         | _       | PRLWIP | TMRHWIP | TMRLWIP  | RBWIP    | RAWIP  | 0000          |

| 0130                        | CCP1STAT                        | 15:0      | _                    | -                   | _        | _      | _       | ICGARM | _         | _     | CCPTRIG     | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV     | ICBNE  | 0000          |

| 04.40                       |                                 | 31:16     | CCP1 TMRH<15:0> 0000 |                     |          |        |         |        | 0000      |       |             |         |         |        |         |          |          |        |               |

| 0140                        | CCP1TMR                         | 15:0      |                      | CCP1 TMRL<15:0> 000 |          |        |         |        |           |       | 0000        |         |         |        |         |          |          |        |               |

| 0150                        | CCP1PR                          | 31:16     |                      | CCP1 PRH<15:0> 0000 |          |        |         |        |           |       | 0000        |         |         |        |         |          |          |        |               |

| 0150                        | CUPIPR                          | 15:0      | CCP1 PRL<15:0>       |                     |          |        |         |        | 0000      |       |             |         |         |        |         |          |          |        |               |

| 0160                        | CCP1RA                          | 31:16     | _                    |                     | _        | —      | —       | _      | —         |       | _           |         |         | —      | _       | _        |          | —      | 0000          |

| 0100                        | CUPIRA                          | 15:0      |                      |                     |          |        |         |        |           | CI    | MPA<15:0>   |         |         |        |         |          |          |        | 0000          |

| 0170                        | CCP1RB                          | 31:16     | _                    | —                   | _        | —      | —       | _      | _         | _     | —           | —       | —       | —      | —       | —        | —        | —      | 0000          |

| 0170                        | CCF IND                         | 15:0      |                      |                     |          |        |         |        |           | CN    | MPB<15:0>   |         |         |        |         |          |          |        | 0000          |

| 0180                        | CCP1BUF                         | 31:16     |                      |                     |          |        |         |        |           | CCP1  | BUFH<15:    | )>      |         |        |         |          |          |        | 0000          |

| 0100                        |                                 | 15:0      |                      |                     |          |        |         |        |           | CCP1  | 1 BUFL<15:( | )>      |         |        |         |          |          |        | 0000          |

| 0200                        | CCP2CON1                        | 31:16     | OPSSRC               | RTRGEN              |          |        |         | OPS<   | 3:0>      |       | TRIGEN      | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >        |        | 0000          |

| 0200                        | 001200111                       | 15:0      | ON                   | _                   | SIDL     | CCPSLP | TMRSYNC | С      | LKSEL<2:0 | >     | TMRF        | 'S<1:0> | T32     | CCSEL  |         | MOE      | )<3:0>   |        | 0000          |

| 0210                        | CCP2CON2                        | 31:16     | OENSYNC              | —                   | —        | —      | —       | —      | —         | OCAEN | ICGS        | M<1:0>  | —       | AUXO   | UT<1:0> |          | ICS<2:0> |        | 0100          |

| 0210                        | 001 200112                      | 15:0      | PWMRSEN              | ASDGM               | —        | SSDG   | —       | —      | —         | —     |             |         |         | ASDO   | G<7:0>  |          |          |        | 0000          |

| 0220                        | CCP2CON3                        | 31:16     | OETRIG               | _                   | _        | —      | —       | —      | _         | _     | —           | _       | POLACE  | —      | PSSAC   | E<1:0>   | _        | _      | 0000          |

| 0220                        | 00.200.10                       | 15:0      | —                    | _                   | _        | —      | _       | _      | _         | —     | —           | _       | _       | —      | —       | —        | _        | —      | 0000          |

| 0230                        | CCP2STAT                        | 31:16     | —                    | —                   | —        | —      | —       | —      | _         | _     | —           | —       | —       | PRLWIP | TMRHWIP | TMRLWIP  | RBWIP    | RAWIP  | 0000          |

|                             |                                 | 15:0      | _                    | —                   | —        | —      | —       | ICGARM | —         | —     | CCPTRIG     | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV     | ICBNE  | 0000          |

| 0240                        | CCP2TMR                         | 31:16     |                      |                     |          |        |         |        |           | CCP2  | 2 TMRH<15:  | 0>      |         |        |         |          |          |        | 0000          |

|                             | 20.2                            | 15:0      |                      |                     |          |        |         |        |           |       | 2 TMRL<15:  |         |         |        |         |          |          |        | 0000          |

| 0250                        | CCP2PR                          | 31:16     |                      |                     |          |        |         |        |           |       | 2 PRH<15:0  |         |         |        |         |          |          |        | 0000          |

|                             |                                 | 15:0      |                      |                     |          |        |         |        |           | CCP   | 2 PRL<15:0  | >       |         |        |         |          |          |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range             | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04                    | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24 — — — RXBUFELM<4:0 |                   |                   |                   |                   |                   | )>                |                  |                  |  |  |  |

| 00.40                    | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16                    | _                 | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |

| 15.0                     | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |  |

| 15:8                     | _                 | _                 |                   | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |  |  |

| 7.0                      | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |  |

| 7:0                      | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |  |  |  |

#### **REGISTER 13-3:** SPIxSTAT: SPIx STATUS REGISTER

| Legend: |                   | C = Clearable bit | HS = Hardware Settable bit         |                    |  |  |

|---------|-------------------|-------------------|------------------------------------|--------------------|--|--|

|         | R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

|         | -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 FRMERR: SPIx Frame Error status bit 1 = Frame error is detected 0 = No frame error is detected This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPIx Activity Status bit

- 1 = SPIx peripheral is currently busy with some transactions

- 0 = SPIx peripheral is currently Idle

- bit 10-9 **Unimplemented:** Read as '0'

- bit 8 SPITUR: SPIx Transmit Underrun (TUR) bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When the SPIx Shift register is empty

- 0 = When the SPIx Shift register is not empty

- bit 6 SPIROV: SPIx Receive Overflow (ROV) Flag bit

- 1 = New data is completely received and discarded; the user software has not read the previous data in the SPIxBUF register

- 0 = No overflow has occurred

- This bit is set in hardware; it can only be cleared (= 0) in software.

- bit 5 SPIRBE: SPIx RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CPU Read Pointer (CRPTR) = SPI Write Pointer (SWPTR))

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

## REGISTER 13-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when the CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   | YRTEN             | <3:0>             |                   |                   | YRON              | =<3:0>           |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 | _                 | _                 | MTHTEN            | MTHONE<3:0>       |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | —                 | _                 | DAYTE             | N<1:0>            | DAYONE<3:0>       |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | _                 | _                 |                   | WDAY<2:0>        |                  |  |

## REGISTER 15-5: RTCDATE: RTCC DATE REGISTERS

## Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-28 YRTEN<3:0>: Binary Coded Decimal Value of Years 10-Digit bits

- bit 27-24 YRONE<3:0>: Binary Coded Decimal Value of Years 1-Digit bits

- bit 23-21 Unimplemented: Read as '0'

- bit 20 MTHTEN: Binary Coded Decimal Value of Months 10-Digit bit Contains a value from 0 to 1.

- bit 19-16 **MTHONE<3:0>:** Binary Coded Decimal Value of Months 1-Digit bits Contains a value from 0 to 9.

- bit 15-14 Unimplemented: Read as '0'

- bit 13-12 **DAYTEN<1:0>:** Binary Coded Decimal Value of Days 10-Digit bits Contains a value from 0 to 3.

- bit 11-8 **DAYONE<3:0>:** Binary Coded Decimal Value of Days 1-Digit bits Contains a value from 0 to 9.

- bit 7-3 Unimplemented: Read as '0'

- bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekdays Digit bits Contains a value from 0 to 6.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|--|

| 24.24        | U-0                 | U-0                 |  |

| 31:24        | _                 | _                 | _                 |                   |                   | —                 | —                   | —                   |  |

| 23:16        | U-0                 | U-0                 |  |

| 23.10        | —                 | _                 | -                 | —                 | —                 | —                 | —                   | —                   |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |  |

| 15:8         | ON                | _                 | SIDL              |                   |                   |                   | FORM<2:0>           |                     |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HSC          | R/W-0, HSC          |  |

| 7:0          |                   | SSRO              | C<3:0>            |                   | MODE12            | ASAM              | SAMP <sup>(1)</sup> | DONE <sup>(2)</sup> |  |

#### REGISTER 16-1: AD1CON1: ADC CONTROL REGISTER 1

| Legend:           | HSC = Hardware Settable                             | HSC = Hardware Settable/Clearable bit |                    |  |  |  |  |

|-------------------|-----------------------------------------------------|---------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                                       |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit

- 1 = ADC module is operating

- 0 = ADC is off

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** ADC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- For 12-Bit Operation (MODE12 bit = 1):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dddd 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dddd 0000 0000 0000 0000)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd 0000)

- 001 = Signed Integer 16-bit (DOUT = 0000 0000 0000 0000 ssss sddd dddd)

#### For 10-Bit Operation (MODE12 bit = 0):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd ddd0 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- **Note 1:** The SAMP bit is cleared and cannot be written if the ADC is disabled (ON bit = 0).

- 2: The DONE bit is not persistent in Automatic modes; it is cleared by hardware at the beginning of the next sample.

## REGISTER 16-4: AD1CON5: ADC CONTROL REGISTER 5 (CONTINUED)

- bit 1-0 **CM<1:0>:** Compare Mode bits

- 11 = Outside Window mode (valid match occurs if the conversion result is outside of the window defined by the corresponding buffer pair)

- 10 = Inside Window mode (valid match occurs if the conversion result is inside the window defined by the corresponding buffer pair)

- 01 = Greater Than mode (valid match occurs if the result is greater than the value in the corresponding buffer register)

- 00 = Less Than mode (valid match occurs if the result is less than the value in the corresponding buffer register)

- Note 1: When auto-scan is enabled (ASEN (AD1CON5<15>) = 1), the CSCNA (AD1CON2<10>) and SMPI<3:0> (AD1CON2<5:2>) bits are ignored.

- 2: The ASINT<1:0> bits setting only takes effect when ASEN (AD1CON5<15>) = 1. Interrupt generation is governed by the SMPI<3:0> bits field.

## PIC32MM0064GPL036 FAMILY

## **19.0 COMPARATOR**

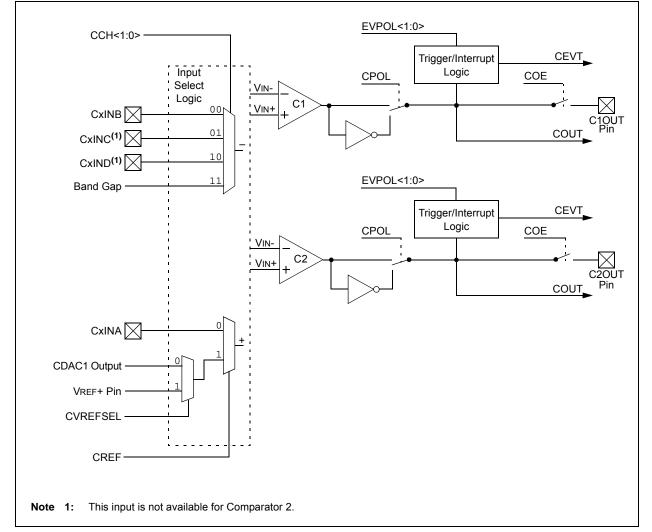

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 19.** "Comparator" (DS60001110) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM. The comparator module provides two dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and VREF+). The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 19-1. Each comparator has its own control register, CMxCON (Register 19-2), for enabling and configuring its operation. The output and event status of two comparators is provided in the CMSTAT register (Register 19-1).

NOTES:

## TABLE 26-14: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                      |                           |             |                    |             |       |  |  |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------|--------------------|-------------|-------|--|--|

| Param<br>No.                                                                                 | Symbol               | Characteristic            | Min         | Тур <sup>(2)</sup> | Мах         | Units |  |  |

| D300                                                                                         | VIOFF                | Input Offset Voltage      | -20         |                    | 20          | mV    |  |  |

| D301                                                                                         | VICM                 | Input Common-Mode Voltage | AVss - 0.3V | —                  | AVDD + 0.3V | V     |  |  |

| D307                                                                                         | TRESP <sup>(1)</sup> | Response Time             |             | 150                | —           | ns    |  |  |

Note 1: Measured with one input at VDD/2 and the other transitioning from Vss to VDD.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-15: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> $2.0V < VDD < 3.6V$ , $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |        |                              |     |                    |     |       |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------|------------------------------|-----|--------------------|-----|-------|--|--|

| Param<br>No.                                                                                                    | Symbol | Characteristic               | Min | Тур <sup>(2)</sup> | Max | Units |  |  |

| VRD310                                                                                                          | TSET   | Settling Time <sup>(1)</sup> | _   |                    | 10  | μs    |  |  |

| VRD311                                                                                                          | VRA    | Accuracy                     | -1  | _                  | 1   | LSb   |  |  |

| VRD312                                                                                                          | VRur   | Unit Resistor Value (R)      |     | 4.5                |     | kΩ    |  |  |

Note 1: Measures the interval while VRDAT<4:0> transitions from '11111' to '00000'.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 26-22: RESET, BROWN-OUT RESET AND SLEEP MODES TIMING SPECIFICATIONS

| Operati      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                         |     |                    |     |       |                                                          |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|--------------------|-----|-------|----------------------------------------------------------|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                          | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                               |  |

| SY10         | TMCL                                                                                                                    | MCLR Pulse Width (Low)                                  | 2   | —                  | _   | μs    |                                                          |  |

| SY13         | Tioz                                                                                                                    | I/O High-Impedance from<br>MCLR Low                     | _   | 1                  | _   | μs    |                                                          |  |

| SY25         | TBOR                                                                                                                    | Brown-out Reset Pulse<br>Width                          | 1   | —                  | —   | μs    | $VDD \leq VBOR$                                          |  |

| SY45         | TRST                                                                                                                    | Reset State Time                                        | _   | 25                 | _   | μs    |                                                          |  |

| SY71         | Twake <sup>(2)</sup>                                                                                                    | Wake-up Time with Main<br>Voltage Regulator             | _   | 22                 | _   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 0,<br>RETVR = 1 |  |

|              |                                                                                                                         |                                                         | _   | 3.8                | —   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 0,<br>RETVR = 1 |  |

| SY72         | Twakelvr <sup>(2)</sup>                                                                                                 | Wake-up Time with<br>Retention Low-Voltage<br>Regulator | _   | 163                | —   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 1,<br>RETVR = 0 |  |

|              |                                                                                                                         |                                                         |     | 23                 | _   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 1,<br>RETVR = 0 |  |

**Note 1:** Data in the "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The parameters are measured with the external clock source (EC). To get the full wake-up time, the oscillator start-up time must be added.

## PIC32MM0064GPL036 FAMILY

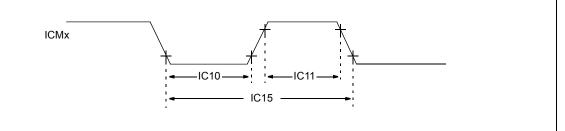

## FIGURE 26-7: MCCP AND SCCP INPUT CAPTURE x MODE TIMING CHARACTERISTICS

### TABLE 26-25: MCCP AND SCCP INPUT CAPTURE x MODE TIMING REQUIREMENTS

| Operati       | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                      |    |   |    |                               |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|----|---|----|-------------------------------|--|--|--|

| Param.<br>No. | Symbol Characteristics <sup>1</sup> Min Max Units Conditions                                                            |                      |    |   |    | Conditions                    |  |  |  |

| IC10          | TICL                                                                                                                    | ICMx Input Low Time  | 25 | _ | ns | Must also meet Parameter IC15 |  |  |  |

| IC11          | Тісн                                                                                                                    | ICMx Input High Time | 25 | - | ns | Must also meet Parameter IC15 |  |  |  |

| IC15          | TICP                                                                                                                    | ICMx Input Period    | 50 |   | ns |                               |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

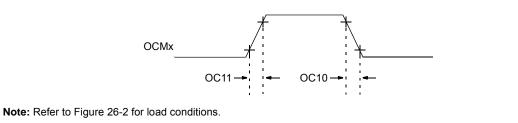

## FIGURE 26-8: MCCP AND SCCP OUTPUT COMPARE x MODE TIMING CHARACTERISTICS

## TABLE 26-26: MCCP AND SCCP OUTPUT COMPARE x MODE TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |        |                                |     |     |     |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|-----|-----|-----|-------|--|--|

| Param.<br>No.                                                                                                           | Symbol | Characteristics <sup>(1)</sup> | Min | Тур | Max | Units |  |  |

| OC10                                                                                                                    | TOCF   | OCMx Output Fall Time          |     | 10  | 25  | ns    |  |  |

| OC11                                                                                                                    | TOCR   | OCMx Output Rise Time          | —   | 10  | 25  | ns    |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

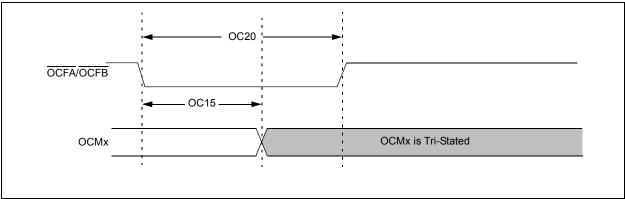

### TABLE 26-27: MCCP AND SCCP PWM MODE TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le V_{DD} \le 3.6V$ , $-40^{\circ}C \le T_A \le +85^{\circ}C$ (unless otherwise stated) |        |                                |     |     |       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|-----|-----|-------|--|--|

| Param<br>No.                                                                                                                | Symbol | Characteristics <sup>(1)</sup> | Min | Max | Units |  |  |

| OC15                                                                                                                        | Tfd    | Fault Input to PWM I/O Change  | _   | 30  | ns    |  |  |

| OC20                                                                                                                        | TFLT   | Fault Input Pulse Width        | 10  |     | ns    |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

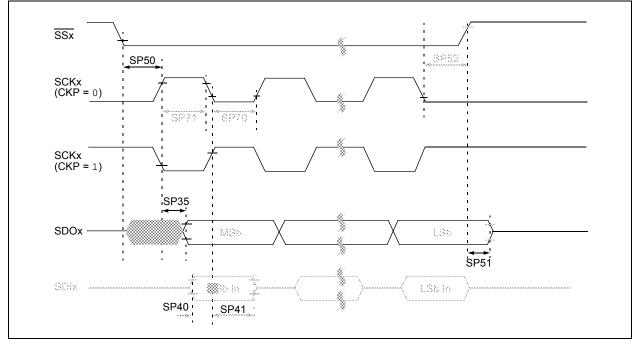

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                       |                                            |     |     |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------|-----|-----|-------|--|--|

| Param.<br>No.                                                                                                           | Symbol                | Characteristics <sup>(1)</sup>             | Min | Max | Units |  |  |

| SP10                                                                                                                    | TscL, TscH            | SCKx Output Low or High Time               | 10  | —   | ns    |  |  |

| SP35                                                                                                                    | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge     | —   | 7   | ns    |  |  |

| SP36                                                                                                                    | TDOV2sc,<br>TDOV2scL  | SDOx Data Output Setup to First SCKx Edge  | 7   | —   | ns    |  |  |

| SP40                                                                                                                    | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 7   | —   | ns    |  |  |

| SP41                                                                                                                    | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 7   | —   | ns    |  |  |

## TABLE 26-28: SPIX MODULE MASTER MODE TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

## FIGURE 26-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

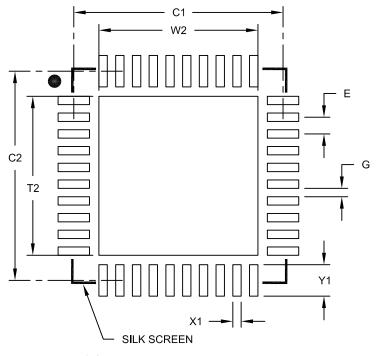

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS      |          |      |      |  |

|----------------------------|------------------|----------|------|------|--|

| Dimension                  | Dimension Limits |          |      | MAX  |  |

| Contact Pitch              | E                | 0.40 BSC |      |      |  |

| Optional Center Pad Width  | W2               |          |      | 3.80 |  |

| Optional Center Pad Length | T2               |          |      | 3.80 |  |

| Contact Pad Spacing        | C1               |          | 5.00 |      |  |

| Contact Pad Spacing        | C2               |          | 5.00 |      |  |

| Contact Pad Width (X40)    | X1               |          |      | 0.20 |  |

| Contact Pad Length (X40)   | Y1               |          |      | 0.75 |  |

| Distance Between Pads      | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support