Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-SQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0016gpl036-e-m2 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MM0064GPL036 FAMILY

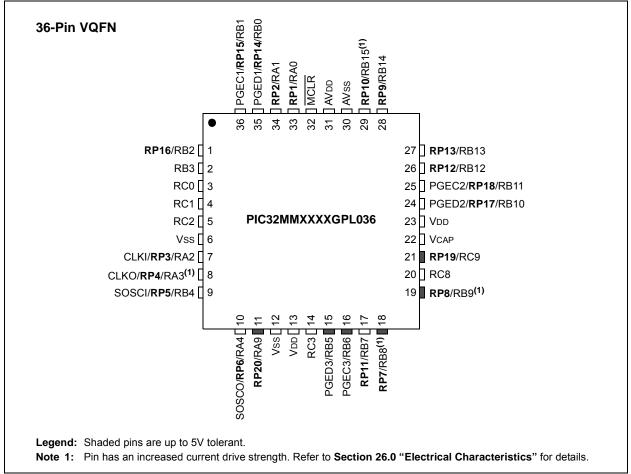

## Pin Diagrams (Continued)

#### TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN VQFN DEVICES

| Pin | Function                                            | Pin | Function                                                                       |

|-----|-----------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                         | 19  | TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | AN11/C1INA/RB3                                      | 20  | RC8                                                                            |

| 3   | AN12/RC0                                            | 21  | RP19/RC9                                                                       |

| 4   | AN13/RC1                                            | 22  | VCAP                                                                           |

| 5   | RC2                                                 | 23  | VDD                                                                            |

| 6   | Vss                                                 | 24  | PGED2/TDO/ <b>RP17</b> /RB10                                                   |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                         | 25  | PGEC2/TDI/ <b>RP18</b> /RB11                                                   |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 26  | AN7/LVDIN/ <b>RP12</b> /RB12                                                   |

| 9   | SOSCI/ <b>RP5</b> /RB4                              | 27  | AN8/ <b>RP13</b> /RB13                                                         |

| 10  | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                | 28  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                          |

| 11  | <b>RP20</b> /RA9                                    | 29  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>            |

| 12  | Vss                                                 | 30  | AVss                                                                           |

| 13  | Vdd                                                 | 31  | AVDD                                                                           |

| 14  | RC3                                                 | 32  | MCLR                                                                           |

| 15  | PGED3/RB5                                           | 33  | VREF+/AN0/RP1/OCM1E/INT3/RA0                                                   |

| 16  | PGEC3/RB6                                           | 34  | Vref-/AN1/ <b>RP2</b> /OCM1F/RA1                                               |

| 17  | <b>RP11</b> /RB7                                    | 35  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                                        |

| 18  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>         | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                                        |

Note 1: Pin has an increased current drive strength.

NOTES:

## 3.3 Power Management

The processor core offers a number of power management features, including low-power design, active power management and Power-Down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

The mechanism for invoking Power-Down mode is implemented through execution of the WAIT instruction. The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MM family makes extensive use of local gated clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The microAptiv UC core has an Enhanced JTAG (EJTAG) interface for use in the software debug. In addition to the standard mode of operation, the microAptiv UC core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the microAptiv UC core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

# 3.5 MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the microAptiv UC core, which is included on PIC32MM0064GPL036 family devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | -                 | _                 |                   | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | R-1               | R-0               | R-0               | R-1              | R-0              |

|              | _                 | _                 | _                 | PC                | WR                | CA                | EP               | FP               |

## REGISTER 3-2: CONFIG1: CONFIGURATION REGISTER 1; CP0 REGISTER 16, SELECT 1

| Legend:           | r = Reserved bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 **Reserved:** This bit is hardwired to a '1' to indicate the presence of the CONFIG2 register

- bit 30-5 Unimplemented: Read as '0'

- bit 4 **PC:** Performance Counter bit

- 1 = The processor core contains performance counters

- bit 3 WR: Watch Register Presence bit

- 0 = No Watch registers are present

- bit 2 CA: Code Compression Implemented bit

- 0 = No MIPS16e<sup>®</sup> are present

- bit 1 EP: EJTAG Present bit

- 1 = Core implements EJTAG

- bit 0 **FP:** Floating-Point Unit bit

- 0 = Floating-Point Unit is not implemented

#### **REGISTER 8-3: REFO1CON: REFERENCE OSCILLATOR CONTROL REGISTER (CONTINUED)**

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(3)</sup>

- 1111 = Reserved

- •

- .

- 1010 = Reserved

- 1001 = REFCLKI pin

- 1000 = Reserved

- 0111 = System PLL output (not divided)

- 0110 = Reserved

- 0101 = Secondary Oscillator (SOSC)

- 0100 = Low-Power RC Oscillator (LPRC)

- 0011 = Fast RC Oscillator (FRC)

- 0010 = Primary Oscillator (POSC)

- 0001 = Instruction/System Clock (SYSCLK)

- 0000 = Instruction/System Clock (SYSCLK)

- **Note 1:** Do not write to this register when the ON bit is not equal to the ACTIVE bit.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000.

- 3: The ROSEL<3:0> bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

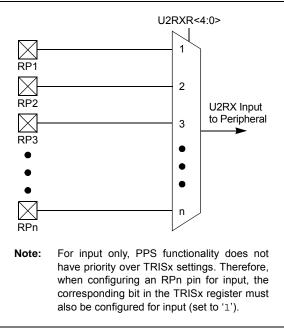

#### 9.8.4 INPUT MAPPING

The RPINRx registers are used to assign the peripheral input to the required remappable pin, RPn (refer to the peripheral inputs and the corresponding RPINRx registers listed in Table 9-2). Each RPINRx register contains sets of 5-bit fields. Programming these bits with the remappable pin number will connect the peripheral to this RPn pin. Example 9-1 and Figure 9-2 illustrate the remappable pin selection for the U2RX input.

#### EXAMPLE 9-1: UART2 RX INPUT ASSIGNMENT TO RP9/RB14 PIN

| RPINR9bits.U2RXR | = | 9; | 11 | connect UART2 RX |

|------------------|---|----|----|------------------|

|                  |   |    | // | input to RP9 pin |

# FIGURE 9-2: REMA

#### REMAPPABLE INPUT EXAMPLE FOR U2RX

#### TABLE 9-2: INPUT PIN SELECTION

| Input Name              | Function Name | Register | Function Bits |

|-------------------------|---------------|----------|---------------|

| External Interrupt 4    | INT4          | RPINR1   | INT4R<4:0>    |

| MCCP1 Input Capture     | ICM1          | RPINR2   | ICM1R<4:0>    |

| SCCP2 Input Capture     | ICM2          | RPINR2   | ICM2R<4:0>    |

| SCCP3 Input Capture     | ICM3          | RPINR3   | ICM3R<4:0>    |

| Output Compare Fault A  | OCFA          | RPINR5   | OCFAR<4:0>    |

| Output Compare Fault B  | OCFB          | RPINR5   | OCFBR<4:0>    |

| CCP Clock Input A       | TCKIA         | RPINR6   | TCKIAR<4:0>   |

| CCP Clock Input B       | TCKIB         | RPINR6   | TCKIBR<4:0>   |

| UART2 Receive           | U2RX          | RPINR9   | U2RXR<4:0>    |

| UART2 Clear-to-Send     | U2CTS         | RPINR9   | U2CTSR<4:0>   |

| SPI2 Data Input         | SDI2          | RPINR11  | SDI2R<4:0>    |

| SPI2 Clock Input        | SCK2IN        | RPINR11  | SCK2INR<4:0>  |

| SPI2 Slave Select Input | SS2IN         | RPINR11  | SS2INR<4:0>   |

| CLC Input A             | CLCINA        | RPINR12  | CLCINAR<4:0>  |

| CLC Input B             | CLCINB        | RPINR12  | CLCINBR<4:0>  |

# REGISTER 10-1: T1CON: TIMER1 CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer1 External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit

- 1 = External clock is defined by the TECS<1:0> bits

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 24.04        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31:24        | _                    |                   | _                 | —                 | —                        | _                 |                  | _                       |

| 00.40        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23:16        | —                    | _                 | —                 | —                 | —                        | _                 | —                | _                       |

| 45.0         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 15:8         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

|              | AUDEN <sup>(1)</sup> |                   |                   | —                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

## REGISTER 13-2: SPIxCON2: SPIx CONTROL REGISTER 2

## Legend:

| 0                 |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15        | <b>SPISGNEXT:</b> SPIx Sign-Extend Read Data from the RX FIFO bit<br>1 = Data from RX FIFO is sign-extended                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 0 = Data from RX FIFO is not sign-extended                                                                                                                                       |

| bit 14-13     | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 12        | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                                                                 |

|               | <ul><li>1 = Frame error overflow generates error events</li><li>0 = Frame error does not generate error events</li></ul>                                                         |

| bit 11        | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                                                                 |

|               | <ul><li>1 = Receive Overflow (ROV) generates error events</li><li>0 = Receive Overflow does not generate error events</li></ul>                                                  |

| bit 10        | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                                                                 |

|               | <ul><li>1 = Transmit Underrun (TUR) generates error events</li><li>0 = Transmit Underrun does not generate error events</li></ul>                                                |

| bit 9         | IGNROV: Ignore Receive Overflow (ROV) bit (for audio data transmissions)                                                                                                         |

|               | 1 = A ROV is not a critical error; during ROV, data in the FIFO is not overwritten by receive data<br>0 = A ROV is a critical error which stops SPIx operation                   |

| bit 8         | IGNTUR: Ignore Transmit Underrun (TUR) bit (for audio data transmissions)                                                                                                        |

|               | <ul> <li>1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty</li> <li>0 = A TUR is a critical error which stops SPIx operation</li> </ul> |

| bit 7         | AUDEN: Enable Audio Codec Support bit <sup>(1)</sup>                                                                                                                             |

|               | <ul><li>1 = Audio protocol is enabled</li><li>0 = Audio protocol is disabled</li></ul>                                                                                           |

| bit 6-4       | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 3         | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                                                         |

|               | <ul><li>1 = Audio data is mono (each data word is transmitted on both left and right channels)</li><li>0 = Audio data is stereo</li></ul>                                        |

| bit 2         | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 1-0       | AUDMOD<1:0>: Audio Protocol Mode bits <sup>(1,2)</sup><br>11 = PCM/DSP mode<br>10 = Right Justified mode<br>01 = Left Justified mode<br>00 = I <sup>2</sup> S mode               |

| Note 1:<br>2: | These bits can only be written when the ON bit = $0$ .<br>These bits are only valid for AUDEN = $1$ .                                                                            |

**2:** These bits are only valid for AUDEN = 1.

## REGISTER 14-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 11  | <b>RTSMD:</b> Mode Selection for UxRTS Pin bit<br>1 = UxRTS pin is in Simplex mode                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = UxRTS pin is in Flow Control mode                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 9-8 | UEN<1:0>: UARTx Enable bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register</li> </ul> |

| bit 7   | WAKE: Enable Wake-up on Start Bit Detect During Sleep Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Wake-up is enabled</li><li>0 = Wake-up is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul><li>1 = Loopback mode is enabled</li><li>0 = Loopback mode is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement is disabled or has completed</li> </ul>                                                                                                                                                                                                                                                                  |

| bit 4   | RXINV: Receive Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = High-Speed mode – 4x baud clock is enabled</li> <li>0 = Standard Speed mode – 16x baud clock is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | STSEL: Stop Selection bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note 1: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

#### REGISTER 14-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | <b>URXISEL&lt;1:0&gt;:</b> UARTx Receive Interrupt Mode Selection bits<br>11 = Reserved<br>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full<br>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full<br>00 = Interrupt flag bit is asserted while receive buffer is not ampty (i.e., has at least 1 data character) |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)<br><b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                 |

|         | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                     |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                   |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Data is being received</li></ul>                                                                                                                                                                                                                                                                                              |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                       |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                     |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit                                                                                                                                                                                                                                                                                                                          |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to the empty state.<br>1 = Receive buffer has overflowed<br>0 = Receive buffer has not overflowed                                                                                                                         |

| bit 0   | <b>LIRXDA:</b> LIARTy Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                    |

- bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

#### REGISTER 19-2: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 AND 2) (CONTINUED)

bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits

11 = Trigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0)10 = Trigger/event/interrupt is generated on transition of the comparator output:

If CPOL = 0 (non-inverted polarity):

High-to-low transition only. If CPOL = 1 (inverted polarity):

Low-to-high transition only.

01 = Trigger/event/interrupt is generated on transition of the comparator output:

If CPOL = 0 (non-inverted polarity):

Low-to-high transition only.

If CPOL = 1 (inverted polarity):

High-to-low transition only.

00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Reference Select bit (non-inverting input)

- 1 = Non-inverting input connects to the internal reference defined by the CVREFSEL bit in the CMSTAT register 0 = Non-inverting input connects to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits

- 11 = Inverting input of the comparator connects to the band gap reference voltage

- 10 = Inverting input of the comparator connects to the CxIND pin

- 01 = Inverting input of the comparator connects to the CxINC pin

- 00 = Inverting input of the comparator connects to the CxINB pin

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (CONTINUED)

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin and is compared with 1.2V band gap) 1110 = VDD trip point is  $2.11V^{(1)}$

- 1101 = VDD trip point is  $2.21V^{(1)}$

- 1100 = VDD trip point is 2.30V<sup>(1)</sup>

- 1011 = VDD trip point is 2.40V<sup>(1)</sup>

- 1010 = VDD trip point is  $2.52V^{(1)}$

- 1001 = VDD trip point is 2.63V<sup>(1)</sup>

- $1000 = \text{VDD trip point is } 2.82\text{V}^{(1)}$

- 0111 = VDD trip point is  $2.92V^{(1)}$

- $0110 = VDD trip point is <math>3.13V^{(1)}$

- 0101 = VDD trip point is  $3.44V^{(1)}$

- 0100-0000 = Reserved; do not use

- Note 1: The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in Section 26.0 "Electrical Characteristics" for minimum and maximum values.

# 25.0 INSTRUCTION SET

The PIC32MM0064GPL036 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0064GPL036 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for         | - |

|-------|----------------------------------------------|---|

|       | Programmers Volume II-B: The                 | 1 |

|       | microMIPS32 <sup>™</sup> Instruction Set" at |   |

|       | www.imgtec.com for more information.         |   |

## TABLE 26-14: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                      |                           |             |                    |             |       |  |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------|--------------------|-------------|-------|--|

| Param<br>No.                                                                                 | Symbol               | Characteristic            | Min         | Тур <sup>(2)</sup> | Мах         | Units |  |

| D300                                                                                         | VIOFF                | Input Offset Voltage      | -20         |                    | 20          | mV    |  |

| D301                                                                                         | VICM                 | Input Common-Mode Voltage | AVss - 0.3V | —                  | AVDD + 0.3V | V     |  |

| D307                                                                                         | TRESP <sup>(1)</sup> | Response Time             |             | 150                | —           | ns    |  |

Note 1: Measured with one input at VDD/2 and the other transitioning from Vss to VDD.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# TABLE 26-15: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |        |                              |     |                    |     |       |

|----------------------------------------------------------------------------------------------|--------|------------------------------|-----|--------------------|-----|-------|

| Param<br>No.                                                                                 | Symbol | Characteristic               | Min | Тур <sup>(2)</sup> | Max | Units |

| VRD310                                                                                       | TSET   | Settling Time <sup>(1)</sup> | _   |                    | 10  | μs    |

| VRD311                                                                                       | VRA    | Accuracy                     | -1  | _                  | 1   | LSb   |

| VRD312                                                                                       | VRur   | Unit Resistor Value (R)      |     | 4.5                |     | kΩ    |

Note 1: Measures the interval while VRDAT<4:0> transitions from '11111' to '00000'.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

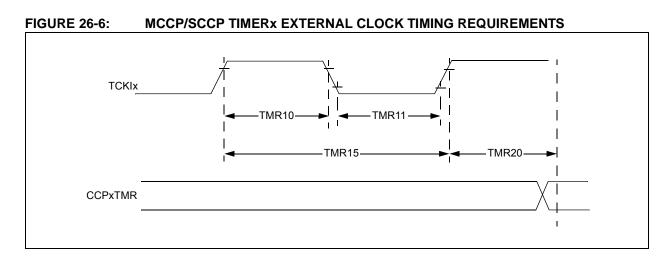

## TABLE 26-24: MCCP/SCCP TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le V_{DD} \le 3.6V$ , $-40^{\circ}C \le T_A \le +85^{\circ}C$ (unless otherwise stated) |           |                                          |                    |     |     |        |                                   |

|-----------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|--------------------|-----|-----|--------|-----------------------------------|

| Param.<br>No.                                                                                                               | Symbol    | Characteristics <sup>(1)</sup>           |                    | Min | Max | Units  | Conditions                        |

| TMR10                                                                                                                       | Тскн      | TCKIx High Time                          | Synchronous        | 1   | _   | TPBCLK | Must also meet<br>Parameter TMR15 |

|                                                                                                                             |           |                                          | Asynchronous       | 10  | —   | ns     |                                   |

| TMR11                                                                                                                       | TCKL      | TCKIx Low Time                           | Synchronous        | 1   | —   | TPBCLK | Must also meet<br>Parameter TMR15 |

|                                                                                                                             |           |                                          | Asynchronous       | 10  | _   | ns     |                                   |

| TMR15                                                                                                                       | Тскр      | TCKIx Input Period                       | Synchronous        | 2   | _   | TPBCLK |                                   |

|                                                                                                                             |           |                                          | Asynchronous       | 20  | _   | ns     |                                   |

| TMR20                                                                                                                       | TCKEXTMRL | Delay from Externa<br>to Timer Increment | I TCKIx Clock Edge | _   | 1   | TPBCLK |                                   |

**Note 1:** These parameters are characterized but not tested in manufacturing.

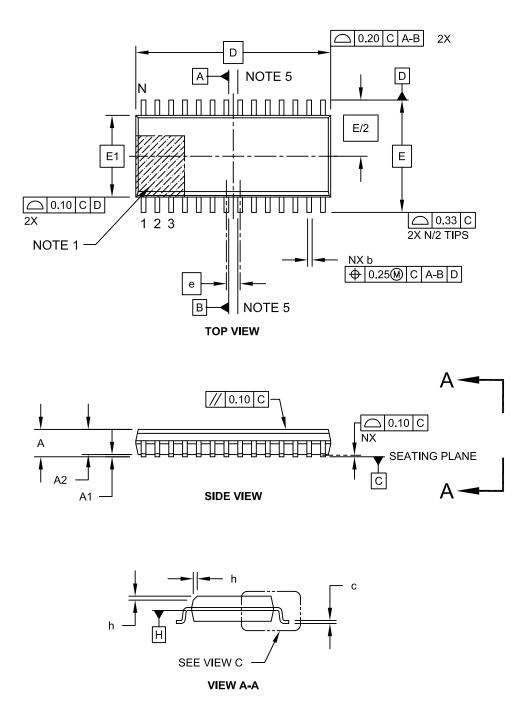

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

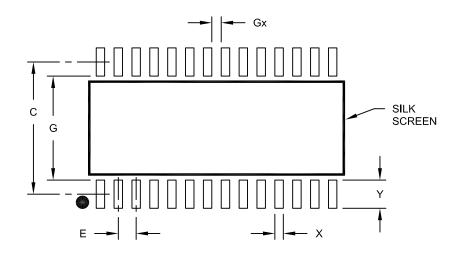

# RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | E  |             | 1.27 BSC |      |

| Contact Pad Spacing      | С  |             | 9.40     |      |

| Contact Pad Width (X28)  | X  |             |          | 0.60 |

| Contact Pad Length (X28) | Y  |             |          | 2.00 |

| Distance Between Pads    | Gx | 0.67        |          |      |

| Distance Between Pads    | G  | 7.40        |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

| CCPxCON3 (Capture/Compare/PWMx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CCPxSTAT (Capture/Compare/PWMx Status) 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CFGCON (Configuration Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLCxCON (CLCx Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLCxGLS (CLCx Gate Logic Input Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLCxSEL (CLCx Input MUX Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKSTAT (Clock Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CMSTAT (Comparator Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CMxCON (Comparator x Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CNCONx (Change Notification Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| for PORTx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CONFIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (CP0 Register 16, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONFIG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (Configuration Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CONFIG3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (Configuration Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CONFIG5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (Configuration Register 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CRCCON (CRC Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CRCXOR (CRC XOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DAC1CON (CDAC Control) 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DEVID (Device ID) 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FDEVOPT/AFDEVOPT (Device Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |