Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 16                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

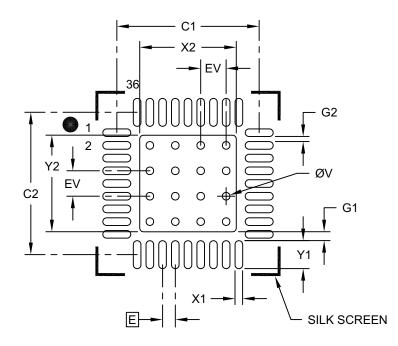

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 20-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl020-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                                                                                                                                                                                 |                | Pin                    | Number                        |                |                |             |                |                                      |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------|--|--|

| Pin Name | 20-Pin<br>QFN                                                                                                                                                                                   | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                          |  |  |

| PGEC1    | 2                                                                                                                                                                                               | 5              | 2                      | 5                             | 36             | 39             | Ι           | ST             | ICSP Port 1 programming clock input  |  |  |

| PGEC2    | 19                                                                                                                                                                                              | 2              | 19                     | 22                            | 25             | 28             | I           | ST             | ICSP Port 2 programming clock input  |  |  |

| PGEC3    | 7                                                                                                                                                                                               | 10             | 12                     | 15                            | 16             | 16             | I           | ST             | ICSP Port 3 programming clock input  |  |  |

| PGED1    | 1                                                                                                                                                                                               | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | ICSP Port 1 programming data         |  |  |

| PGED2    | 20                                                                                                                                                                                              | 3              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | ICSP Port 2 programming data         |  |  |

| PGED3    | 6                                                                                                                                                                                               | 9              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | ICSP Port 3 programming data         |  |  |

| PWRLCLK  | 7                                                                                                                                                                                               | 10             | 9                      | 12                            | 10             | 10             | I           | ST             | Real-Time Clock 50/60 Hz clock input |  |  |

| RA0      | 19                                                                                                                                                                                              | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RA1      | 20                                                                                                                                                                                              | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RA2      | 4                                                                                                                                                                                               | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RA3      | 5                                                                                                                                                                                               | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RA4      | 7                                                                                                                                                                                               | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RA9      | _                                                                                                                                                                                               | _              | _                      | _                             | 11             | 11             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |

| RB0      | 1                                                                                                                                                                                               | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB1      | 2                                                                                                                                                                                               | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB2      | 3                                                                                                                                                                                               | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB3      | _                                                                                                                                                                                               |                | 4                      | 7                             | 2              | 2              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB4      | 6                                                                                                                                                                                               | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB5      | _                                                                                                                                                                                               | _              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB6      | _                                                                                                                                                                                               |                | 12                     | 15                            | 16             | 16             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB7      | 8                                                                                                                                                                                               | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB8      | 9                                                                                                                                                                                               | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB9      | 10                                                                                                                                                                                              | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB10     | _                                                                                                                                                                                               | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB11     | _                                                                                                                                                                                               | _              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB12     | 12                                                                                                                                                                                              | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB13     | 13                                                                                                                                                                                              | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB14     | 14                                                                                                                                                                                              | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RB15     | 15                                                                                                                                                                                              | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |

| RC0      | —                                                                                                                                                                                               | _              | _                      | _                             | 3              | 3              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| RC1      | _                                                                                                                                                                                               | _              | _                      | _                             | 4              | 4              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| RC2      | _                                                                                                                                                                                               | _              | —                      | —                             | 5              | 5              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| RC3      | —                                                                                                                                                                                               | _              | _                      | _                             | 14             | 14             | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| RC8      | _                                                                                                                                                                                               | _              | _                      | _                             | 20             | 21             | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| RC9      | _                                                                                                                                                                                               | _              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |

| REFCLKI  | 10                                                                                                                                                                                              | 13             | 15                     | 18                            | 19             | 20             | I           | ST             | Reference clock input                |  |  |

| REFCLKO  | 15                                                                                                                                                                                              | 18             | 23                     | 26                            | 29             | 32             | 0           | DIG            | Reference clock output               |  |  |

| Legend:  | 0     15     18     23     26     29     32     O     DIG     Reference clock output       ST = Schmitt Trigger input buffer     DIG = Digital input/output     ANA = Analog level input/output |                |                        |                               |                |                |             |                |                                      |  |  |

#### **TABLE 1-1:** PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

NOTES:

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------|-----------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 24.04        | R/W-1, HS                        | R/W-1, HS | U-0               | U-0               | R/W-0, HS         | R/W-0, HS           | U-0              | U-0              |

| 31:24        | PORIO                            | PORCORE   |                   | —                 | BCFGERR           | BCFGFAIL            | _                | —                |

| 00.40        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        | —                                | _         | _                 | —                 | —                 | _                   | _                | —                |

| 45.0         | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0                 | R/W-0, HS        | U-0              |

| 15:8         | _                                | _         |                   | —                 | —                 | _                   | CMR              | _                |

| 7.0          | R/W-0, HS                        | R/W-0, HS | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS           | R/W-1, HS        | R/W-1, HS        |

| 7:0          | EXTR                             | SWR       | _                 | WDTO              | SLEEP             | IDLE <sup>(2)</sup> | BOR              | POR              |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| Legend:           | HS = Hardware Settable bit |                           |                    |

|-------------------|----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | PORIO: VDD POR Flag bit                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Set by hardware at detection of a VDD POR event.<br>1 = A Power-on Reset has occurred due to VDD voltage<br>0 = A Power-on Reset has not occurred due to VDD voltage                                        |

| bit 30    | PORCORE: Core Voltage POR Flag bit                                                                                                                                                                          |

|           | Set by hardware at detection of a core POR event.<br>1 = A Power-on Reset has occurred due to core voltage<br>0 = A Power-on Reset has not occurred due to core voltage                                     |

| bit 29-28 | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 27    | BCFGERR: Primary Configuration Registers Error Flag bit                                                                                                                                                     |

|           | <ul> <li>1 = An error occurred during a read of the Primary Configuration registers</li> <li>0 = No error occurred during a read of the Primary Configuration registers</li> </ul>                          |

| bit 26    | BCFGFAIL: Primary/Secondary Configuration Registers Error Flag bit                                                                                                                                          |

|           | <ul><li>1 = An error occurred during a read of the Primary and Alternate Configuration registers</li><li>0 = No error occurred during a read of the Primary and Alternate Configuration registers</li></ul> |

| bit 25-10 | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 9     | CMR: Configuration Mismatch Reset Flag bit                                                                                                                                                                  |

|           | <ul><li>1 = A Configuration Mismatch Reset has occurred</li><li>0 = A Configuration Mismatch Reset has not occurred</li></ul>                                                                               |

| bit 8     | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 7     | EXTR: External Reset (MCLR) Pin Flag bit                                                                                                                                                                    |

|           | <ul><li>1 = Master Clear (pin) Reset has occurred</li><li>0 = Master Clear (pin) Reset has not occurred</li></ul>                                                                                           |

| bit 6     | SWR: Software Reset Flag bit                                                                                                                                                                                |

|           | <ul><li>1 = Software Reset was executed</li><li>0 = Software Reset was not executed</li></ul>                                                                                                               |

| bit 5     | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 4     | WDTO: Watchdog Timer Time-out Flag bit                                                                                                                                                                      |

|           | 1 = WDT time-out has occurred                                                                                                                                                                               |

|           | 0 = WDT time-out has not occurred                                                                                                                                                                           |

| Note 1:   | User software must clear bits in this register to view the next detection.                                                                                                                                  |

2: The IDLE bit will also be set when the device wakes from Sleep mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |  |  |  |

| 31:24        | _                 | _                 |                   | _                 | _                 |                   | _                | WDTR             |  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | SWNMI             | —                 | _                 | _                 | GNMI              | —                 | CF               | WDTS             |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | NMICNT<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NMIC              | NT<7:0>           |                   |                  |                  |  |  |  |  |  |  |

#### **REGISTER 6-3:** RNMICON: NON-MASKABLE INTERRUPT (NMI) CONTROL REGISTER<sup>(1)</sup>

#### Legend:

| 9                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-25 Unimplemented: Read as '0'

- bit 24 WDTR: Watchdog Timer Time-out in Run Mode Flag bit

- 1 = A Run mode WDT time-out has occurred and caused an NMI

- 0 = WDT time-out has not occurred

- Setting this bit will cause a WDT NMI event and NMICNT<15:0> will begin counting.

- bit 23 SWNMI: Software NMI Trigger bit

- 1 = An NMI has been generated

- 0 = An NMI was not generated

- bit 22-20 Unimplemented: Read as '0'

- bit 19 **GNMI:** Software General NMI Trigger bit

- 1 = A general NMI has been generated

- 0 = A general NMI was not generated

- bit 18 Unimplemented: Read as '0'

- bit 17 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected clock failure and caused an NMI

- 0 = FSCM has not detected clock failure

- Setting this bit will cause a CF NMI event, but will not cause a clock switch to the FRC.

- bit 16 WDTS: Watchdog Timer Time-out in Sleep Mode Flag bit

- 1 = WDT time-out has occurred during Sleep mode and caused a wake-up from Sleep

0 = WDT time-out has not occurred during Sleep mode

Setting this bit will cause a WDT NMI.

#### bit 15-0 NMICNT<15:0>: NMI Reset Counter Value bits

These bits specify the reload value used by the NMI Reset counter. FFFFh-0001h = Number of SYSCLK cycles before a device Reset occurs<sup>(2)</sup> 0000h = No delay between NMI assertion and device Reset event

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: If a Watchdog Timer NMI event (when not in Sleep mode) is cleared before this counter reaches '0', no device Reset is asserted. This NMI Reset counter is only applicable to the Watchdog Timer NMI event.

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

### 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

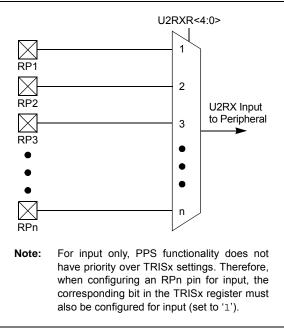

#### 9.8.4 INPUT MAPPING

The RPINRx registers are used to assign the peripheral input to the required remappable pin, RPn (refer to the peripheral inputs and the corresponding RPINRx registers listed in Table 9-2). Each RPINRx register contains sets of 5-bit fields. Programming these bits with the remappable pin number will connect the peripheral to this RPn pin. Example 9-1 and Figure 9-2 illustrate the remappable pin selection for the U2RX input.

#### EXAMPLE 9-1: UART2 RX INPUT ASSIGNMENT TO RP9/RB14 PIN

| RPINR9bits.U2RXR | = | 9; | 11 | connect UART2 RX |

|------------------|---|----|----|------------------|

|                  |   |    | // | input to RP9 pin |

## FIGURE 9-2: REMA

#### REMAPPABLE INPUT EXAMPLE FOR U2RX

#### TABLE 9-2: INPUT PIN SELECTION

| Input Name              | Function Name | Register | Function Bits |

|-------------------------|---------------|----------|---------------|

| External Interrupt 4    | INT4          | RPINR1   | INT4R<4:0>    |

| MCCP1 Input Capture     | ICM1          | RPINR2   | ICM1R<4:0>    |

| SCCP2 Input Capture     | ICM2          | RPINR2   | ICM2R<4:0>    |

| SCCP3 Input Capture     | ICM3          | RPINR3   | ICM3R<4:0>    |

| Output Compare Fault A  | OCFA          | RPINR5   | OCFAR<4:0>    |

| Output Compare Fault B  | OCFB          | RPINR5   | OCFBR<4:0>    |

| CCP Clock Input A       | TCKIA         | RPINR6   | TCKIAR<4:0>   |

| CCP Clock Input B       | TCKIB         | RPINR6   | TCKIBR<4:0>   |

| UART2 Receive           | U2RX          | RPINR9   | U2RXR<4:0>    |

| UART2 Clear-to-Send     | U2CTS         | RPINR9   | U2CTSR<4:0>   |

| SPI2 Data Input         | SDI2          | RPINR11  | SDI2R<4:0>    |

| SPI2 Clock Input        | SCK2IN        | RPINR11  | SCK2INR<4:0>  |

| SPI2 Slave Select Input | SS2IN         | RPINR11  | SS2INR<4:0>   |

| CLC Input A             | CLCINA        | RPINR12  | CLCINAR<4:0>  |

| CLC Input B             | CLCINB        | RPINR12  | CLCINBR<4:0>  |

#### TABLE 9-5: PORTB REGISTER MAP

| ess                                      |                                 | 0         |                                |       |        |       |         |       |         | Bits     |                      |      |      |      |      |       |                  |      |               |

|------------------------------------------|---------------------------------|-----------|--------------------------------|-------|--------|-------|---------|-------|---------|----------|----------------------|------|------|------|------|-------|------------------|------|---------------|

| Virtual Address<br>(BF80_#)<br>Reclister | Register<br>Name <sup>(2)</sup> | Bit Range | 31/15                          | 30/14 | 29/13  | 28/12 | 27/11   | 26/10 | 25/9    | 24/8     | 23/7                 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1             | 16/0 | All<br>Resets |

| 2700                                     | ANSELB                          | 31:16     | _                              | —     | —      | —     | —       | _     | _       | —        | -                    | _    | —    | —    | —    | —     | —                | _    | 0000          |

| 2700                                     | ANGLLD                          | 15:0      |                                | ANSB< | 15:12> |       | —       | —     | —       | —        | _                    | _    | —    | —    |      | ANSB< | :3:0> <b>(1)</b> |      | FOOF          |

| 2710                                     | TRISB                           | 31:16     | —                              | _     | _      | _     | —       | _     | _       | _        |                      |      | _    | _    | _    | _     | _                | _    | 0000          |

| 2710                                     | IRISD                           | 15:0      | TRISB<15:0> <sup>(1)</sup> F   |       |        |       |         |       |         |          |                      |      |      |      |      |       | FFFF             |      |               |

| 2720                                     | PORTB                           | 31:16     | —                              | _     | _      | _     | —       | _     | _       | _        |                      |      | _    | _    | _    | _     | _                | _    | 0000          |

| 2720                                     | FURID                           | 15:0      |                                |       |        |       |         |       |         | RB<15:0  | <sub>)&gt;</sub> (1) |      |      |      |      |       |                  |      | 0000          |

| 2730                                     | LATB                            | 31:16     | —                              | _     | _      | _     | —       | _     | _       | _        |                      |      | _    | _    | _    | _     | _                | _    | 0000          |

| 2730                                     | LAID                            | 15:0      | 0 LATB<15:0> <sup>(1)</sup> 01 |       |        |       |         |       |         |          |                      |      |      |      |      |       | 0000             |      |               |

| 2740                                     | ODCB                            | 31:16     | —                              | —     | —      | —     | —       | —     | _       | —        | _                    | _    | —    | —    | —    | —     | —                | _    | 0000          |

| 2740                                     |                                 | 15:0      |                                |       |        |       |         |       |         | ODCB<15  | :0>(1)               |      |      |      | -    |       |                  | _    | 0000          |

| 2750                                     | CNPUB                           | 31:16     | _                              | _     | _      | —     | —       | _     | _       |          | —                    | _    | —    |      | —    | —     |                  |      | 0000          |

| 2750                                     |                                 | 15:0      | CNPUB<15:0> <sup>(1)</sup> 00  |       |        |       |         |       |         |          |                      |      |      |      |      | 0000  |                  |      |               |

| 2760                                     | CNPDB                           | 31:16     | _                              | _     | —      | —     | —       | _     | _       | —        | _                    | _    | —    | —    | —    | —     | —                | —    | 0000          |

| 2100                                     |                                 | 15:0      | CNPDB<15:0> <sup>(1)</sup>     |       |        |       |         |       |         |          |                      |      |      |      |      | 0000  |                  |      |               |

| 2770                                     | CNCONB                          | 31:16     | _                              |       |        | _     | —       | —     | _       |          | _                    |      |      |      |      | —     |                  |      | 0000          |

| 2110                                     | ONCOME                          | 15:0      | ON                             | —     | —      | —     | CNSTYLE | —     | —       | —        | —                    | —    | —    | —    | —    | —     | —                | —    | 0000          |

| 2780                                     | CNEN0B                          | 31:16     | —                              | —     | —      | —     | —       | —     | —       | —        | —                    | —    | —    | —    | —    | —     | —                | —    | 0000          |

| 2100                                     | ONLIND                          | 15:0      |                                |       |        |       |         |       |         | CNIEB<1  | 5:0>(1)              |      |      |      |      |       |                  |      | 0000          |

| 2790                                     | CNSTATB                         | 31:16     | —                              | —     | —      | —     | —       |       | _       | —        | —                    | —    | —    | —    | —    | —     | —                |      | 0000          |

| 2100                                     | enten ni b                      | 15:0      |                                |       |        |       |         |       |         | CNSTATB< | 15:0> <b>(1)</b>     |      |      |      |      |       |                  |      | 0000          |

| 27A0                                     | CNEN1B                          | 31:16     | —                              | —     | —      | —     | —       |       | _       | —        | —                    | —    | —    | —    | —    | —     | —                |      | 0000          |

| 2.7.0                                    | SILLIND                         | 15:0      |                                |       |        |       |         |       |         | CNIE1B<1 | 5:0>(1)              |      |      |      |      |       |                  |      | 0000          |

| 27B0                                     | 27B0 CNFB                       | 31:16     | —                              | —     | —      | —     | —       |       | _       | —        | —                    | —    | —    | —    | —    | —     | —                |      | 0000          |

|                                          | 15:0                            |           |                                |       |        |       |         |       | CNFB<15 | :0>(1)   |                      |      |      |      |      |       |                  | 0000 |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** Bits<11:10,6:5,3> are not implemented in 20-pin devices.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### TABLE 9-6: PORTC REGISTER MAP

| DS60001324B-pa |

|----------------|

| age            |

| 84             |

| ess                                                            |                                 | <b>n</b>  | Bits              |       |       |       |                        |       |        |                      |      |      |      |      |      |         |                    |                       |               |

|----------------------------------------------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|------------------------|-------|--------|----------------------|------|------|------|------|------|---------|--------------------|-----------------------|---------------|

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(3)</sup> | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2    | 17/1               | 16/0                  | All<br>Resets |

| 2800                                                           | ANSELC                          | 31:16     | _                 | _     | _     | _     | _                      | _     |        | _                    |      | _    | _    | -    | —    | —       |                    | _                     | 0000          |

|                                                                |                                 | 15:0      | —                 | _     | _     |       |                        |       | _      | _                    | —    |      |      | _    | —    | _       | ANSC<              | 1:0> <sup>(1,2)</sup> | 0003          |

| 2810                                                           | TRISC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| -0.0                                                           |                                 | 15:0      | _                 | —     | —     | _     | _                      | _     | TRISC  | :9:8> <b>(1,2)</b>   | —    | _    | —    | _    |      | TRISC<  | 3:0> <b>(1,2)</b>  |                       | 030F          |

| 2820                                                           | PORTC                           | 31:16     | _                 | —     | _     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2020                                                           | TORTO                           | 15:0      | —                 |       |       |       | _                      | _     | RC<9   | :8> <sup>(1,2)</sup> | —    | _    |      | _    |      | RC<3:   | 0> <b>(1,2)</b>    |                       | 0000          |

| 2830                                                           | LATC                            | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | —    | —    | —    | —    | —       | —                  | —                     | 0000          |

| 2000                                                           | EATO                            | 15:0      | —                 |       |       |       | _                      | _     | LATC<  | 9:8> <b>(1,2)</b>    | —    | _    |      | _    |      | LATC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2840                                                           | ODCC                            | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 2040                                                           | 0000                            | 15:0      | —                 |       |       |       | _                      | _     | ODCC<  | :9:8> <b>(1,2)</b>   | —    | _    |      | _    |      | ODCC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2850                                                           | CNPUC                           | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 2000                                                           |                                 | 15:0      | —                 | —     | —     | —     | _                      | _     | CNPUC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPUC   | <3:0>(1,2)         |                       | 0000          |

| 2860                                                           | CNPDC                           | 31:16     | —                 | —     | —     | _     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | -                  | —                     | 0000          |

| 2000                                                           | CINFDC                          | 15:0      | —                 | —     | —     | —     | —                      | —     | CNPDC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPDC<  | <3:0> <b>(1,2)</b> |                       | 0000          |

| 2870                                                           | CNCONC                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2070                                                           | CINCOINC                        | 15:0      | ON <sup>(1)</sup> | —     | —     | —     | CNSTYLE <sup>(1)</sup> | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2880                                                           | CNEN0C                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2000                                                           | CINEINUC                        | 15:0      | _                 | —     | —     | —     | _                      | _     | CNIE0C | <9:8>(1,2)           | —    |      | _    | I    |      | CNIE0C4 | <3:0>(1,2)         |                       | 0000          |

| 2890                                                           | CNSTATC -                       | 31:16     | _                 | —     | —     | —     | _                      | _     | _      | —                    | —    |      | _    | I    | —    | _       |                    | _                     | 0000          |

| 2090                                                           | CINGTATE                        | 15:0      | —                 | —     | —     | —     | _                      | _     | CNSTAT | C<9:8>(1,2)          | —    | —    | —    |      |      | CNSTATO | <3:0>(1,2)         |                       | 0000          |

| 28A0                                                           | CNEN1C                          | 31:16     | _                 | -     | _     | -     | -                      | _     | _      | —                    | —    | _    | _    | I    | _    | -       |                    | _                     | 0000          |

| 2040                                                           | CINENTO                         | 15:0      | _                 | -     | -     | -     | —                      | _     | CNIE1C | <9:8>(1,2)           | _    |      |      |      |      | CNIE1C  | <3:0>(1,2)         |                       | 0000          |

| 28B0                                                           | CNFC                            | 31:16     | _                 | -     | —     | -     | —                      | _     | —      | —                    | —    |      |      |      | _    | —       | _                  | —                     | 0000          |

| 20BU                                                           | CINFC                           | 15:0      | _                 | —     | —     | —     | _                      | _     | CNFC<  | :9:8> <b>(1,2)</b>   | _    |      |      |      |      | CNFC<   | 3:0>(1,2)          |                       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **Note 1:** Bits<15,11,9:8,3:0> are not implemented in 20-pin devices.

**2:** Bits<8,3:0> are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

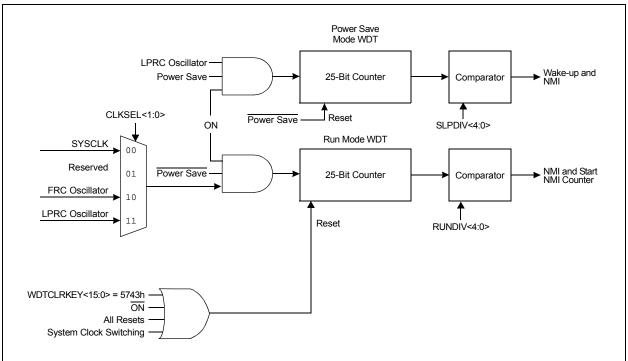

## 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|------------------|--|--|--|

| 04.04        | R/W-0             | U-0               | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-1            |  |  |  |

| 31:24        | OENSYNC           | -                 | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN            |  |  |  |

| 00.40        | R/W-0             | R/W-0             | U-0                  | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |

| 23:16        | ICGSM             | 1<1:0>            | _                    | AUXOL                | JT<1:0>              | ICS<2:0>             |                      |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | U-0                  | R/W-0                | U-0                  | U-0                  | U-0                  | U-0              |  |  |  |

| 15:8         | PWMRSEN           | ASDGM             | _                    | SSDG                 | —                    | _                    | _                    | —                |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |

| 7:0          | ASDG<7:0>         |                   |                      |                      |                      |                      |                      |                  |  |  |  |

#### REGISTER 12-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 **OENSYNC:** Output Enable Synchronization bit

- 1 = Update by output enable bits occurs on the next Time Base Reset or rollover

- 0 = Update by output enable bits occurs immediately

- bit 30 Unimplemented: Read as '0'

- bit 29-24 OC<F:A>EN: Output Enable/Steering Control bits<sup>(1)</sup>

- 1 = OCx pin is controlled by the CCPx module and produces an output compare or PWM signal

- 0 = OCx pin is not controlled by the CCPx module; the pin is available to the port logic or another peripheral multiplexed on the pin

#### bit 23-22 ICGSM<1:0>: Input Capture Gating Source Mode Control bits

- 11 = Reserved

- 10 = One-Shot mode: Falling edge from gating source disables future capture events (ICDIS = 1)

- 01 = One-Shot mode: Rising edge from gating source enables future capture events (ICDIS = 0)

- 00 = Level-Sensitive mode: A high level from gating source will enable future capture events; a low level will disable future capture events

- bit 21 Unimplemented: Read as '0'

- bit 20-19 AUXOUT<1:0>: Auxiliary Output Signal on Event Selection bits

- 11 = Input capture or output compare event; no signal in Timer mode

- 10 = Signal output depends on module operating mode

- 01 = Time base rollover event (all modes)

- 00 = Disabled

- bit 18-16 ICS<2:0>: Input Capture Source Select bits

- 111 = Reserved

- 110 = Reserved

- 101 = CLC2 output

- 100 = CLC1 output

- 011 = Reserved

- 010 = Comparator 2 output

- 001 = Comparator 1 output

- 000 = ICMx pin (remappable)

- bit 15 **PWMRSEN:** CCPx PWM Restart Enable bit

- 1 = ASEVT bit clears automatically at the beginning of the next PWM period, after the shutdown input has ended

- 0 = ASEVT must be cleared in software to resume PWM activity on output pins

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

### REGISTER 15-1: RTCCON1: RTCC CONTROL 1 REGISTER (CONTINUED)

- bit 11 WRLOCK: RTCC Registers Write Lock bit<sup>(2)</sup>

- 1 = Registers associated with accurate timekeeping are locked

- 0 = Registers associated with accurate timekeeping may be written to by user

- bit 10-8 Unimplemented: Read as '0'

- bit 7 RTCOE: RTCC Output Enable bit

1 = RTCC clock output is enabled; signal selected by OUTSEL<2:0> is presented on the RTCC pin 0 = RTCC clock output is disabled

- bit 6-4 OUTSEL<2:0>: RTCC Signal Output Selection bits

- 111 = Reserved

- •••

- 011 = Reserved

- 010 = RTCC input clock source

- 001 = Seconds clock

- 000 = Alarm event

- bit 3-0 Unimplemented: Read as '0'

- **Note 1:** The counter decrements on any alarm event. The counter is prevented from rolling over from '00' to 'FF' unless CHIME = 1.

- 2: To clear this bit, an unlock sequence is required. Refer to Section 23.4 "System Registers Write Protection" for details.

## PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | G4D4T             | G4D4N             | G4D3T             | G4D3N             | G4D2T             | G4D2N             | G4D1T            | G4D1N            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | G3D4T             | G3D4N             | G3D3T             | G3D3N             | G3D2T             | G3D2N             | G3D1T            | G3D1N            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | G2D4T             | G2D4N             | G2D3T             | G2D3N             | G2D2T             | G2D2N             | G2D1T            | G2D1N            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | G1D4T             | G1D4N             | G1D3T             | G1D3N             | G1D2T             | G1D2N             | G1D1T            | G1D1N            |

#### REGISTER 18-3: CLCxGLS: CLCx GATE LOGIC INPUT SELECT REGISTER

#### Legend:

| Ecgenia.          |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31 | <b>G4D4T:</b> Gate 4 Data Source 4 True Enable bit<br>1 = The Data Source 4 signal is enabled for Gate 4<br>0 = The Data Source 4 signal is disabled for Gate 4                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | <b>G4D4N:</b> Gate 4 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 4<br>0 = The Data Source 4 inverted signal is disabled for Gate 4 |

| bit 29 | <b>G4D3T:</b> Gate 4 Data Source 3 True Enable bit<br>1 = The Data Source 3 signal is enabled for Gate 4<br>0 = The Data Source 3 signal is disabled for Gate 4                      |

| bit 28 | <b>G4D3N:</b> Gate 4 Data Source 3 Negated Enable bit<br>1 = The Data Source 3 inverted signal is enabled for Gate 4<br>0 = The Data Source 3 inverted signal is disabled for Gate 4 |

| bit 27 | <b>G4D2T:</b> Gate 4 Data Source 2 True Enable bit<br>1 = The Data Source 2 signal is enabled for Gate 4<br>0 = The Data Source 2 signal is disabled for Gate 4                      |

| bit 26 | <b>G4D2N:</b> Gate 4 Data Source 2 Negated Enable bit<br>1 = The Data Source 2 inverted signal is enabled for Gate 4<br>0 = The Data Source 2 inverted signal is disabled for Gate 4 |

| bit 25 | <b>G4D1T:</b> Gate 4 Data Source 1 True Enable bit<br>1 = The Data Source 1 signal is enabled for Gate 4<br>0 = The Data Source 1 signal is disabled for Gate 4                      |

| bit 24 | <b>G4D1N:</b> Gate 4 Data Source 1 Negated Enable bit<br>1 = The Data Source 1 inverted signal is enabled for Gate 4<br>0 = The Data Source 1 inverted signal is disabled for Gate 4 |

| bit 23 | <b>G3D4T:</b> Gate 3 Data Source 4 True Enable bit<br>1 = The Data Source 4 signal is enabled for Gate 3<br>0 = The Data Source 4 signal is disabled for Gate 3                      |

| bit 22 | <b>G3D4N:</b> Gate 3 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 3<br>0 = The Data Source 4 inverted signal is disabled for Gate 3 |

| bit 21 | <b>G3D3T:</b> Gate 3 Data Source 3 True Enable bit<br>1 = The Data Source 3 signal is enabled for Gate 3<br>0 = The Data Source 3 signal is disabled for Gate 3                      |

### **19.1 Comparator Control Registers**

#### TABLE 19-1: COMPARATOR 1 AND 2 REGISTER MAP

| ess                         |                                                                          | n     | Bits  |       |       |       |       |       |      |          |      |        |      |      | ú    |      |       |       |            |

|-----------------------------|--------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|------|----------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Virtual Addr<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup><br>Bit Range |       | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 0000                        | OMOTAT                                                                   | 31:16 | —     | _     | —     | —     | _     | —     | —    | —        | _    | -      | -    | —    | —    | _    | C2EVT | C1EVT | 0000       |

| 0900                        | CMSTAT                                                                   | 15:0  | _     | _     | SIDL  | _     | _     | _     | _    | CVREFSEL | _    | _      | _    | _    | _    | _    | C2OUT | C10UT | 0000       |

| 0910                        | CM1CON                                                                   | 31:16 | _     | _     | _     | _     | _     | _     | _    | _        | _    | _      | _    | _    | _    | _    | _     | _     | 0000       |

| 0910                        | CINICON                                                                  | 15:0  | ON    | COE   | CPOL  | _     | _     | _     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | 0000       |

| 0930                        | CM2CON                                                                   | 31:16 | _     | _     | _     | _     | _     | _     | _    |          | _    | _      | _    | _    | _    | _    | _     | _     | 0000       |

| 0930                        | CIMZCON                                                                  | 15:0  | ON    | COE   | CPOL  | —     | _     |       | CEVT | COUT     | EVPO | L<1:0> | -    | CREF |      | _    | CCH   | <1:0> | 0000       |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### 22.3 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not take effect and read values are invalid.

To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). To prevent accidental configuration changes under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK bit in PMDCON register (PMDCON<11>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes. To set or clear PMDLOCK, an unlock sequence must be executed. Refer to Section 23.4 "System Registers Write Protection" for details.

Table 22-1 lists the module disable bits and locations for all modules.

| Peripheral                                               | PMDx Bit Name | Register Name and Bit Location |

|----------------------------------------------------------|---------------|--------------------------------|

| Analog-to-Digital Converter (ADC)                        | ADCMD         | PMD1<0>                        |

| Voltage Reference (VR)                                   | VREFMD        | PMD1<12>                       |

| High/Low-Voltage Detect (HLVD)                           | HLVDMD        | PMD1<20>                       |

| Comparator 1 (CMP1)                                      | CMP1MD        | PMD2<0>                        |

| Comparator 2 (CMP2)                                      | CMP2MD        | PMD2<1>                        |

| Configurable Logic Cell 1 (CLC1)                         | CLC1MD        | PMD2<24>                       |

| Configurable Logic Cell 2 (CLC2)                         | CLC2MD        | PMD2<25>                       |

| Multiple Outputs Capture/Compare/PWM/<br>Timer1 (MCCP1)  | CCP1MD        | PMD3<8>                        |

| Single Output Capture/Compare/PWM/Timer2<br>(SCCP2)      | CCP2MD        | PMD3<9>                        |

| Single Output Capture/Compare/PWM/Timer3 (SCCP3)         | CCP3MD        | PMD3<10>                       |

| Timer1 (TMR1)                                            | T1MD          | PMD4<0>                        |

| Universal Asynchronous Receiver<br>Transmitter 1 (UART1) | U1MD          | PMD5<0>                        |

| Universal Asynchronous Receiver<br>Transmitter 2 (UART2) | U2MD          | PMD5<1>                        |

| Serial Peripheral Interface 1 (SPI1)                     | SPI1MD        | PMD5<8>                        |

| Serial Peripheral Interface 2 (SPI2)                     | SPI2MD        | PMD5<9>                        |

| Real-Time Clock and Calendar (RTCC)                      | RTCCMD        | PMD6<0>                        |

| Reference Clock Output (REFCLKO)                         | REFOMD        | PMD6<8>                        |

| Programmable Cyclic Redundancy Check<br>(CRC)            | CRCMD         | PMD7<3>                        |

#### TABLE 22-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS

NOTES:

### 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 25.0 INSTRUCTION SET

The PIC32MM0064GPL036 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0064GPL036 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for         | - |  |  |  |  |  |  |  |

|-------|----------------------------------------------|---|--|--|--|--|--|--|--|

|       | Programmers Volume II-B: The                 |   |  |  |  |  |  |  |  |

|       | microMIPS32 <sup>™</sup> Instruction Set" at |   |  |  |  |  |  |  |  |

|       | www.imgtec.com for more information.         |   |  |  |  |  |  |  |  |

## 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MM0064GPL036 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MM0064GPL036 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

+

| Ambient temperature under bias<br>Storage temperature                                        |                               |

|----------------------------------------------------------------------------------------------|-------------------------------|

| Voltage on VDD with respect to Vss                                                           | 0.3V to +4.0V                 |

| Voltage on any general purpose digital or analog pin (not 5.5V tolerant) with respect to Vs  | s0.3V to (VDD + 0.3V)         |

| Voltage on any general purpose digital or analog pin (5.5V tolerant) with respect to Vss:    |                               |

| When VDD = 0V:                                                                               | -0.3V to +4.0V                |

| When VDD $\geq$ 2.0V:                                                                        | -0.3V to +6.0V                |

| Voltage on AVDD with respect to Vss                                                          | ser of: 4.0V or (VDD + 0.3V)) |

| Voltage on AVss with respect to Vss                                                          | 0.3V to +0.3V                 |

| Maximum current out of Vss pin                                                               |                               |

| Maximum current into VDD pin <sup>(1)</sup>                                                  |                               |

| Maximum output current sunk by I/O pin                                                       | 11 mA                         |

| Maximum output current sourced by I/O pin                                                    |                               |

| Maximum output current sunk by I/O pin with increased current drive strength (RA3, RB8,      | RB9 and RB15) 17 mA           |

| Maximum output current sourced by I/O pin with increased current drive strength (RA3, RB8, F | RB9 and RB15)24 mA            |

| Maximum current sunk by all ports                                                            |                               |

| Maximum current sourced by all ports <sup>(1)</sup>                                          |                               |

|                                                                                              |                               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 26-1).

**NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 26-4: OPERATING CURRENT (IDD)<sup>(2)</sup>

| <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |                        |      |       |      |                    |  |  |  |  |

|---------------------------------------------------------------------------|------------------------|------|-------|------|--------------------|--|--|--|--|

| Parameter No.                                                             | Typical <sup>(1)</sup> | Max  | Units | Vdd  | Conditions         |  |  |  |  |

| DC19                                                                      | 0.45                   | 0.65 | mA    | 2.0V | Fsys = 1 MHz       |  |  |  |  |

| DC19                                                                      | 0.45                   | 0.65 | mA    | 3.3V |                    |  |  |  |  |

| DC23                                                                      | 2.5                    | 3.5  | mA    | 2.0V | Fsys = 8 MHz       |  |  |  |  |

|                                                                           | 2.5                    | 3.5  | mA    | 3.3V | 1 3 1 3 - 0 101 12 |  |  |  |  |

| DC24                                                                      | 7.0                    | 9.2  | mA    | 2.0V | Fsys = 25 MHz      |  |  |  |  |

|                                                                           | 7.0                    | 9.2  | mA    | 3.3V | 1 STS - 25 WI 12   |  |  |  |  |

| DC25                                                                      | 0.26                   | 0.35 | mA    | 2.0V | Fsys = 32 kHz      |  |  |  |  |

|                                                                           | 0.26                   | 0.35 | mA    | 3.3V | TSTS - 52 NIZ      |  |  |  |  |

**Note 1:** Data in the "Typical" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Base IDD current is measured with: