Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

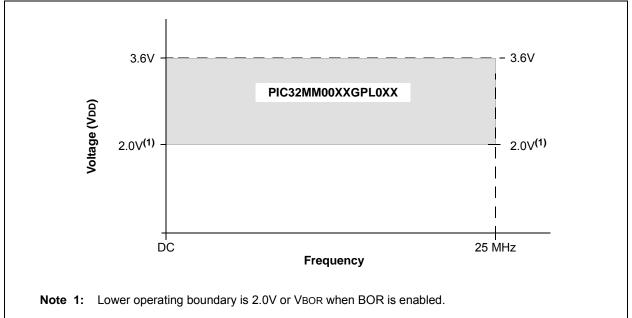

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 16                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 20-QFN (4x4)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl020t-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,   |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | browse the documentation section of the |  |  |  |  |  |

|       | Microchip web site (www.microchip.com). |  |  |  |  |  |

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 60. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS60001336)

- Section 62. "Dual Watchdog Timer" (DS60001365)

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1             | R/W-0            | r-0              |

| 31:24        |                   | K23<2:0>          |                   |                   | KU<2:0>           |                   |                  | _                |

| 00.40        | r-0               | R-0               | R-1               | R-0               | r-0               | r-0               | r-0              | R-1              |

| 23:16        | —                 | UDI               | SB                | MDU               | _                 | —                 | _                | DS               |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-1               | R-0              | R-1              |

| 15:8         | BE                | AT<1:0>           |                   | AR<2:0> MT<       |                   |                   | 2:1>             |                  |

| 7.0          | R-1               | r-0               | r-0               | r-0               | r-0               | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | MT<0>             | _                 | _                 | _                 | _                 |                   | K0<2:0>          |                  |

#### REGISTER 3-1: CONFIG: CONFIGURATION REGISTER; CP0 REGISTER 16, SELECT 0

| Legend: r = Reserved bit |                  |                                    |                    |  |

|--------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31 Reserved: This bit is hardwired to '1' to indicate the presence of the CONFIG1 register

| DIUST     | <b>Reserved.</b> This bit is hardwired to $\pm$ to indicate the presence of the CC |

|-----------|------------------------------------------------------------------------------------|

| bit 30-28 | <b>K23&lt;2:0&gt;:</b> Cacheability of the kseg2 and kseg3 Segments bits           |

|           | 010 = Cache is not implemented                                                     |

| bit 27-25 | KU<2:0>: Cacheability of the kuseg and useg Segments bits                          |

|           | 010 = Cache is not implemented                                                     |

| bit 24-23 | Reserved: Must be written as zeros; returns zeros on reads                         |

| bit 22    | UDI: User-Defined bit                                                              |

|           | 0 = CorExtend user-defined instructions are not implemented                        |

| bit 21    | SB: SimpleBE bit                                                                   |

|           | 1 = Only simple byte enables are allowed on the internal bus interface             |

| bit 20    | MDU: Multiply/Divide Unit bit                                                      |

|           | 0 = Fast, high-performance MDU                                                     |

| bit 19-17 | Reserved: Must be written as zeros; returns zeros on reads                         |

| bit 16    | DS: Dual SRAM Interface bit                                                        |

|           | 1 = Dual instruction/data SRAM interface                                           |

| bit 15    | BE: Endian Mode bit                                                                |

|           | 0 = Little-endian                                                                  |

| bit 14-13 | AT<1:0>: Architecture Type bits                                                    |

|           | 00 = MIPS32 <sup>®</sup>                                                           |

| bit 12-10 | AR<2:0>: Architecture Revision Level bits                                          |

|           | 001 = MIPS32 Release 2                                                             |

| bit 9-7   | MT<2:0>: MMU Type bits                                                             |

|           | 011 = Fixed mapping                                                                |

| bit 6-3   | Reserved: Must be written as zeros; returns zeros on reads                         |

|           |                                                                                    |

bit 2-0 **K0<2:0>:** kseg0 Coherency Algorithm bits 010 = Cache is not implemented

© 2015-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | r-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | —                 |                  | —                |

| 00.40        | U-0               | R-0               | R-1               | R-0               | R-0               | R-0               | R-1              | R-1              |

| 23:16        | —                 | IPLW<1:0>         |                   | MMAR<2:0>         |                   |                   | MCU              | ISAONEXC         |

| 45.0         | R-0               | R-1               | R-1               | R-1               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ISA<              | :1:0>             | ULRI              | RXI               | —                 | —                 | _                | ITL              |

| 7.0          | U-0               | R-1               | R-1               | R-0               | R-1               | U-0               | U-0              | R-0              |

| 7:0          | _                 | VEIC              | VINT              | SP                | CDMM              | _                 | _                | TL               |

#### REGISTER 3-3: CONFIG3: CONFIGURATION REGISTER 3; CP0 REGISTER 16, SELECT 3

| Legend:           | r = Reserved bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 31    | <b>Reserved:</b> This bit is hardwired as '0'                    |

|-----------|------------------------------------------------------------------|

| bit 30-23 | Unimplemented: Read as '0'                                       |

| bit 22-21 | IPLW<1:0>: Width of the Status IPL and Cause RIPL bits           |

|           | 01 = IPL and RIPL bits are 8 bits in width                       |

| bit 20-18 | MMAR<2:0>: microMIPS™ Architecture Revision Level bits           |

|           | 000 = Release 1                                                  |

| bit 17    | MCU: MIPS <sup>®</sup> MCU ASE Implemented bit                   |

|           | 1 = MCU ASE is implemented                                       |

| bit 16    | ISAONEXC: ISA on Exception bit                                   |

|           | 1 = microMIPS is used on entrance to an exception vector         |

| bit 15-14 | ISA<1:0>: Instruction Set Availability bits                      |

|           | 01 = Only microMIPS is implemented                               |

| bit 13    | ULRI: UserLocal Register Implemented bit                         |

|           | 1 = UserLocal Coprocessor 0 register is implemented              |

| bit 12    | RXI: RIE and XIE Implemented in PageGrain bit                    |

|           | 1 = RIE and XIE bits are implemented                             |

| bit 11-9  | Unimplemented: Read as '0'                                       |

| bit 8     | ITL: Indicates that iFlowtrace™ Hardware is Present bit          |

|           | 0 = The iFlowtrace hardware is not implemented in the core       |

| bit 7     | Unimplemented: Read as '0'                                       |

| bit 6     | VEIC: External Vector Interrupt Controller bit                   |

|           | 1 = Support for an external interrupt controller is implemented. |

| bit 5     | VINT: Vector Interrupt bit                                       |

|           | 1 = Vector interrupts are implemented                            |

| bit 4     | SP: Small Page bit                                               |

|           | 0 = 4-Kbyte page size                                            |

| bit 3     | CDMM: Common Device Memory Map bit                               |

|           | 1 = CDMM is implemented                                          |

| bit 2-1   | Unimplemented: Read as '0'                                       |

| bit 0     | TL: Trace Logic bit                                              |

|           | 0 = Trace logic is not implemented                               |

|           |                                                                  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMDATAx<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMDATAx<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | NVMDATAx<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              |                   |                   |                   | NVMDA             | NVMDATAx<7:0>     |                   |                  |                  |  |  |  |  |

#### **REGISTER 5-4: NVMDATAX: NVM FLASH DATA x REGISTER (x = 0-1)**

| Legend:           |                                                             |                      |                    |  |

|-------------------|-------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | ble bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-0 NVMDATAx<31:0>: NVM Flash Data x bits

Double-Word Program: Writes NVMDATA1:NVMDATA0 to the target Flash address defined in NVMADDR. NVMDATA0 contains the least significant instruction word.

### REGISTER 5-5: NVMSRCADDR: NVM SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 NVMSRCADDR<31:0>: NVM Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

NOTES:

## 9.1 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (Clear), SET (Set) and INV (Invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

## 9.2 Parallel I/O (PIO) Ports

All port pins have 14 registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. The LATx register controls the pin level when it is configured as an output. Reads from the PORTx register read the port pins, while writes to the port pins write the latch, LATx. The I/Os state reflected in the PORTx register is synchronized with the system clock and delayed by 3 system clock cycles.

## 9.3 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, the port pins can also be individually configured for either digital or open-drain outputs. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired 5V tolerant pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 9.4 Configuring Analog and Digital Port Pins

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications. The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared. The ANSELx register has a default value of 0xFFFF. Therefore, all pins that share analog functions are analog (not digital) by default. If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is used by an analog peripheral, such as the ADC or comparator module.

## 9.5 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 9.6 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC32MM devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 9-1.

| <b>TABLE 9-1</b> : | CHANGE NOTIFICATION |

|--------------------|---------------------|

|                    | EVENT OPTIONS       |

| CNSTYLE Bit<br>(CNCONx<11>) | <u> </u>           | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

### TABLE 9-6: PORTC REGISTER MAP

| DS60001324B-pa |

|----------------|

| age            |

| 84             |

| ess                         |                                 | <b>n</b>  |                   |       |       |       |                        |       |        | Bits                 |      |      |      |      |      |         |                       |                       |               |

|-----------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|------------------------|-------|--------|----------------------|------|------|------|------|------|---------|-----------------------|-----------------------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2    | 17/1                  | 16/0                  | All<br>Resets |

| 2800                        | ANSELC                          | 31:16     | _                 | _     | _     | _     | _                      | _     |        | _                    |      | _    | _    | -    | —    | —       |                       | _                     | 0000          |

|                             |                                 | 15:0      | —                 | _     | _     |       |                        |       | _      | _                    | —    |      |      | _    | —    | _       | ANSC<                 | 1:0> <sup>(1,2)</sup> | 0003          |

| 2810                        | TRISC                           | 31:16     | _                 | —     | _     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| -0.0                        |                                 | 15:0      | _                 | —     | _     | _     | _                      | _     | TRISC  | :9:8> <b>(1,2)</b>   | —    | _    | —    | _    |      | TRISC<  | 3:0> <b>(1,2)</b>     |                       | 030F          |

| 2820                        | PORTC                           | 31:16     | _                 | —     | _     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2020                        | TORTO                           | 15:0      | —                 |       |       |       | _                      | _     | RC<9   | :8> <sup>(1,2)</sup> | —    | _    |      | _    |      | RC<3:   | 0> <b>(1,2)</b>       |                       | 0000          |

| 2830                        | LATC                            | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | —    | —    | —    | —    | —       | —                     | —                     | 0000          |

| 2000                        | EATO                            | 15:0      | —                 |       |       |       | _                      | _     | LATC<  | 9:8> <b>(1,2)</b>    | —    | _    |      | _    |      | LATC<   | 3:0> <b>(1,2)</b>     |                       | 0000          |

| 2840                        | ODCC                            | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                     | —                     | 0000          |

| 2040                        | 0000                            | 15:0      | —                 |       |       |       | _                      | _     | ODCC<  | :9:8> <b>(1,2)</b>   | —    | _    |      | _    |      | ODCC<   | 3:0> <b>(1,2)</b>     |                       | 0000          |

| 2850                        | CNPUC                           | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                     | —                     | 0000          |

| 2000                        |                                 | 15:0      | —                 | —     | —     | —     | _                      | _     | CNPUC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPUC   | <3:0>(1,2)            |                       | 0000          |

| 2860                        | CNPDC                           | 31:16     | —                 | —     | —     | _     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | -                     | —                     | 0000          |

| 2000                        | CINFDC                          | 15:0      | —                 | —     | —     | —     | —                      | —     | CNPDC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPDC<  | <3:0> <b>(1,2)</b>    |                       | 0000          |

| 2870                        | CNCONC                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2070                        | CINCOINC                        | 15:0      | ON <sup>(1)</sup> | —     | —     | —     | CNSTYLE <sup>(1)</sup> | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2880                        | CNEN0C                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                     | —                     | 0000          |

| 2000                        | CINEINUC                        | 15:0      | _                 | —     | —     | —     | _                      | _     | CNIE0C | <9:8>(1,2)           | —    |      | _    | I    |      | CNIE0C4 | <3:0>(1,2)            |                       | 0000          |

| 2890                        | CNSTATC -                       | 31:16     | _                 | —     | —     | —     | _                      | _     | _      | —                    | —    |      | _    | I    | —    | _       |                       | _                     | 0000          |

| 2090                        | CINGTATE                        | 15:0      | —                 | —     | —     | —     | _                      | _     | CNSTAT | C<9:8>(1,2)          | —    | —    | —    |      |      | CNSTATO | <3:0>(1,2)            |                       | 0000          |

| 28A0                        | CNEN1C                          | 31:16     | _                 | -     | _     | -     | -                      | _     | _      | —                    | —    | _    | _    | I    | _    | -       |                       | _                     | 0000          |

| 2040                        | CINENTO                         | 15:0      | _                 | -     | -     | -     | —                      | _     | CNIE1C | <9:8>(1,2)           | _    |      |      |      |      | CNIE1C  | <3:0>(1,2)            |                       | 0000          |

| 28B0                        | CNFC                            | 31:16     | _                 | -     | —     | -     | —                      | _     | —      | —                    | —    |      |      |      | _    | —       | _                     | —                     | 0000          |

| 20BU                        | CINFC                           | 15:0      | _                 | —     | —     | —     | _                      | _     | CNFC<  | :9:8> <b>(1,2)</b>   | _    |      |      |      |      | CNFC<   | 3:0> <sup>(1,2)</sup> |                       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **Note 1:** Bits<15,11,9:8,3:0> are not implemented in 20-pin devices.

**2:** Bits<8,3:0> are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## REGISTER 17-1: CRCCON: CRC CONTROL REGISTER (CONTINUED)

- bit 2 MOD: CRC Calculation Mode bit

- 1 = Alternate mode

- 0 = Legacy mode

- bit 1-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | X<31:24>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | X<23:16>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | X<1               | 5:8>              |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0 R/W-0 R/W-0 |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              |                  |  |  |  |  |  |

| 7:0          |                   |                   |                   | X<7:1>            |                   |                   |                  | _                |  |  |  |  |  |

### REGISTER 17-2: CRCXOR:CRC XOR REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-1 X<31:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

# 23.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Programming and Diagnostics" (DS61129) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 23.1 Configuration Bits

PIC32MM0064GPL036 family devices contain a Boot Flash Memory (BFM) with an associated configuration space. All Configuration Words are listed in Table 23-3 and Table 23-4; Register 23-1 through Register 23-6 describe the configuration options.

## 23.2 Code Execution from RAM

PIC32MM0064GPL036 family devices allow executing the code from RAM. The starting boundary of this special RAM space can be adjusted using the EXECADDR<7:0> bits in the CFGCON register with a 1-Kbyte step. Writing a non-zero value to these bits will move the boundary, effectively reducing the total amount of program memory space in RAM. Refer to Table 23-5 and Register 23-7 for more information.

### 23.3 Device ID

The Device ID identifies the device used. The ID can be read from the DEVID register. The Device IDs for PIC32MM0064GPL036 family devices are listed in Table 23-1. Also refer to Table 23-5 and Register 23-8 for more information.

#### TABLE 23-1: DEVICE IDs FOR PIC32MM0064GPL036 FAMILY DEVICES

| -                 | -          |

|-------------------|------------|

| Device            | DEVID      |

| PIC32MM0016GPL020 | 0x06B04053 |

| PIC32MM0032GPL020 | 0x06B0C053 |

| PIC32MM0064GPL020 | 0x06B14053 |

| PIC32MM0016GPL028 | 0x06B02053 |

| PIC32MM0032GPL028 | 0x06B0A053 |

| PIC32MM0064GPL028 | 0x06B12053 |

| PIC32MM0016GPL036 | 0x06B06053 |

| PIC32MM0032GPL036 | 0x06B0E053 |

| PIC32MM0064GPL036 | 0x06B16053 |

## 23.4 System Registers Write Protection

The critical registers in the PIC32MM0064GPL036 family devices are protected (locked) from an accidental write. If the registers are locked, a special unlock sequence is required to modify the content of these registers.

To unlock the registers, the following steps should be done:

- 1. Disable interrupts prior to the system unlock sequence.

- 2. Execute the system unlock sequence by writing the key values of 0xAA996655 and 0x556699AA to the SYSKEY register, in two back-to-back assembly or 'C' instructions.

- 3. Write the new value to the required register.

- 4. Write a non-key value (such as 0x0000000) to the SYSKEY register to perform a lock.

- 5. Re-enable interrupts.

The registers that require this unlocking sequence are listed in Table 23-2.

| Register<br>Name | Register Description                   | Peripheral |

|------------------|----------------------------------------|------------|

| OSCCON           | Oscillator Control                     | Oscillator |

| SPLLCON          | System PLL Control                     | Oscillator |

| OSCTUN           | FRC Tuning                             | Oscillator |

| PMDCON           | Peripheral Module<br>Disable Control   | PMD        |

| RSWRST           | Software Reset                         | Reset      |

| RPCON            | Peripheral Pin Select<br>Configuration | I/O Ports  |

| RNMICON          | Non-Maskable Interrupt<br>Control      | Reset      |

| PWRCON           | Power Control                          | Reset      |

| RTCCON1          | RTCC Control 1                         | RTCC       |

TABLE 23-2:SYSTEM LOCKED REGISTERS

The SYSKEY register read value indicates the status. A value of '0' indicates the system registers are locked. A value of '1' indicates the system registers are unlocked. For more information about the SYSKEY register, refer to Table 23-5 and Register 23-9.

<sup>© 2015-2016</sup> Microchip Technology Inc.

## 23.9 Configuration Words and System Registers

## TABLE 23-3: CONFIGURATION WORDS SUMMARY

| sse                         |                  |           |        |              |         |         |       |            |       | E       | Bits   |                            |      |            |         |        |          |        |

|-----------------------------|------------------|-----------|--------|--------------|---------|---------|-------|------------|-------|---------|--------|----------------------------|------|------------|---------|--------|----------|--------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31\15  | 30/14        | 29/13   | 28/12   | 27/11 | 26/10      | 25/9  | 24/8    | 23/7   | 22/6                       | 21/5 | 20/4       | 19/3    | 18/2   | 17/1     | 16/0   |

| 17C0                        | RESERVED         | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 1700                        | RESERVED         | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17C4                        | FDEVOPT          | 31:16     |        | USERID<15:0> |         |         |       |            |       |         |        |                            |      |            |         |        |          |        |

| 1704                        | FDEVOFI          | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | SOSCHP  | r-1    | r-1      | r-1    |

| 17C8                        | FICD             | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 1700                        | FICD             | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | ICS        | <1:0>   | JTAGEN | r-1      | r-1    |

| 17CC                        | FPOR             | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 1700                        | FFUR             | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | LPBOREN | RETVR  | BOREN    | l<1:0> |

| 17D0                        | FWDT             | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 1700                        | FVUDI            | 15:0      | FWDTEN | RCLKS        | EL<1:0> |         | RV    | VDTPS<4:0> |       |         | WINDIS | FWDTWINSZ<1:0> SWDTPS<4:0> |      |            |         |        | •        |        |

| 17D4                        | FOSCSEL          | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17.04                       | TUSUSEE          | 15:0      | FCKSM  | <1:0>        | r-1     | SOSCSEL | r-1   | OSCIOFNC   | POSCM | OD<1:0> | IESO   | SOSCEN                     | r-1  | PLLSRC r-1 |         | FI     | NOSC<2:0 | >      |

| 17D8                        | FSEC             | 31:16     | CP     | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 1700                        | FOEU             | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17DC                        | RESERVED         | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| TIDC                        | RESERVED         | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17E0                        | RESERVED         | 31:16     | r-0    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| ITEU                        | RESERVED         | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17E4                        | RESERVED         | 31:16     | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

| 17 E4                       | RESERVED         | 15:0      | r-1    | r-1          | r-1     | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1                        | r-1  | r-1        | r-1     | r-1    | r-1      | r-1    |

Legend: r-0 = Reserved bit, must be programmed as '0'; r-1 = Reserved bit, must be programmed as '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R/P               | R/P R/P           |                   | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 31:24        |                   |                   |                   | USERI             | D<15:8>           |                   |                  |                  |  |  |  |  |

| 00.40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 23:16        | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |  |  |

| 15:8         |                   | _                 |                   |                   | _                 |                   |                  | —                |  |  |  |  |

| 7.0          | r-1 r-1           |                   | r-1               | r-1               | R/P               | r-1               | r-1              | r-1              |  |  |  |  |

| 7:0          |                   | _                 |                   | _                 | SOSCHP            | _                 |                  |                  |  |  |  |  |

#### REGISTER 23-1: FDEVOPT/AFDEVOPT: DEVICE OPTIONS CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 **USERID<15:0>:** User ID bits (2 bytes which can be programmed to any value)

- bit 15-4 Reserved: Program as '1'

- bit 3 **SOSCHP:** Secondary Oscillator (SOSC) High-Power Enable bit 1 = SOSC operates in Normal Power mode 0 = SOSC operates in High-Power mode

- bit 2-0 Reserved: Program as '1'

## TABLE 23-7: UNIQUE DEVICE IDENTIFIER (UDID) REGISTER MAP

| ess                         |                  | Ċ,        |       |                                                                                       |  | , | , |  |  | В           | its          |  |  |      |            |      |  |      |

|-----------------------------|------------------|-----------|-------|---------------------------------------------------------------------------------------|--|---|---|--|--|-------------|--------------|--|--|------|------------|------|--|------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |  |   |   |  |  |             |              |  |  | 16/0 | All Resets |      |  |      |

| 1840                        | UDID1            | 31:16     |       | UDID Word 1<31:0>                                                                     |  |   |   |  |  |             |              |  |  |      |            |      |  |      |

| 1010                        | OBIDT            | 15:0      |       | UDID Wold 1<31.0>                                                                     |  |   |   |  |  |             |              |  |  |      |            |      |  |      |

| 1844                        | UDID2            | 31:16     |       |                                                                                       |  |   |   |  |  | ע חוחוו אין | rd 2<31:0>   |  |  |      |            |      |  | xxxx |

| 1044                        | ODIDZ            | 15:0      |       |                                                                                       |  |   |   |  |  | ODID WO     | 10 2 30 1.05 |  |  |      |            |      |  | xxxx |

| 1848                        | UDID3            | 31:16     |       |                                                                                       |  |   |   |  |  |             | rd 3<31:0>   |  |  |      |            |      |  | xxxx |

| 1040                        | 00103            | 15:0      |       |                                                                                       |  |   |   |  |  |             | iu 3<31.02   |  |  |      |            |      |  | xxxx |

| 184C                        | UDID4            | 31:16     |       | LIDID Word 4-24-05                                                                    |  |   |   |  |  |             |              |  |  |      |            | xxxx |  |      |

| 1040                        | 00104            | 15:0      |       | UDID Word 4<31:0>                                                                     |  |   |   |  |  |             |              |  |  |      |            | xxxx |  |      |

| 1850                        | UDID5            | 31:16     |       |                                                                                       |  |   |   |  |  |             | rd 5<31:0>   |  |  |      |            |      |  | xxxx |

| 1000                        | 00105            | 15:0      |       |                                                                                       |  |   |   |  |  |             | iu 5~51.0~   |  |  |      |            |      |  | xxxx |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 23-8: RESERVED REGISTERS MAP

| ess                      |                                                 | 0         | Bits                      |                           |                           |       |       |       |      |            |      |      | ú    |      |      |      |      |      |            |

|--------------------------|-------------------------------------------------|-----------|---------------------------|---------------------------|---------------------------|-------|-------|-------|------|------------|------|------|------|------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Virtual Address<br>(BF80_#)<br>Register<br>Name | Bit Range | 31/15                     | 30/14                     | 29/13                     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0400                     | RESERVED1                                       | 31:16     |                           |                           |                           |       |       |       |      |            |      |      | 0000 |      |      |      |      |      |            |

| 0400                     |                                                 | 15:0      |                           |                           | Reserved Register 1<31:0> |       |       |       |      |            |      |      |      | 0000 |      |      |      |      |            |

| 0480                     | RESERVED2 31:16<br>15:0                         | 31:16     |                           |                           |                           |       |       |       |      |            |      |      | 0000 |      |      |      |      |      |            |

| 0460                     |                                                 | 15:0      |                           | Reserved Register 2<31:0> | .0>                       |       |       |       |      |            |      | 0000 |      |      |      |      |      |      |            |

| 2220                     |                                                 | 31:16     | Reserved Register 3<31:0> |                           |                           |       |       |       |      |            |      | 0C00 |      |      |      |      |      |      |            |

| 2280                     | RESERVED3                                       | 15:0      |                           |                           |                           |       |       |       | Res  | served Reg |      | .0>  |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 26.1 DC Characteristics

#### FIGURE 26-1: PIC32MM0064GPL036 FAMILY VOLTAGE-FREQUENCY GRAPH

### TABLE 26-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min           | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| PIC32MM00XXGPL0XX:                                                                                                                                                                      |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40           | —   | +105 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40           | —   | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O   |     | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (TJ – TA)/θJA |     |      | W    |

### TABLE 26-2: PACKAGE THERMAL RESISTANCE<sup>(1)</sup>

| Package      | Symbol | Тур  | Unit |

|--------------|--------|------|------|

| 20-Pin SSOP  | θJA    | 87.3 | °C/W |

| 20-Pin QFN   | θJA    | 43.0 | °C/W |

| 28-Pin SPDIP | θJA    | 60.0 | °C/W |

| 28-Pin SSOP  | θJA    | 71.0 | °C/W |

| 28-Pin SOIC  | θJA    | 69.7 | °C/W |

| 28-Pin UQFN  | θJA    | 27.5 | °C/W |

| 28-Pin QFN   | θJA    | 20.0 | °C/W |

| 36-Pin VQFN  | θJA    | 31.1 | °C/W |

| 40-Pin UQFN  | θJA    | 41.0 | °C/W |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| Operatin      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , -40°C $\le$ TA $\le$ +85°C (unless otherwise stated) |                                                                       |                    |                       |       |                                                                                                                                                          |  |

|---------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol                                                                                                      | Characteristics                                                       | Min.               | Max.                  | Units | Conditions                                                                                                                                               |  |

| Dl60a         | licl                                                                                                        | Input Low Injection<br>Current                                        | 0                  | <sub>-5</sub> (1,4)   | mA    | This parameter applies to all pins.                                                                                                                      |  |

| DI60b         | Іісн                                                                                                        | Input High Injection<br>Current                                       | 0                  | +5 <sup>(2,3,4)</sup> | mA    | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins and SOSCI. Maximum IICH<br>current for these exceptions is<br>0 mA. |  |

| DI60c         | ∑ІІСТ                                                                                                       | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(5)</sup> | +20 <sup>(5)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents from<br>all I/O pins,<br>(   IICL +   IICH   ) $\leq \sum$ IICT                      |  |

**Note 1:** VIL Source < (Vss - 0.3). Characterized but not tested.

2: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

**3:** Digital 5V tolerant pins do not have an internal high-side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

4: Injection currents can affect the ADC results.

5: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit.

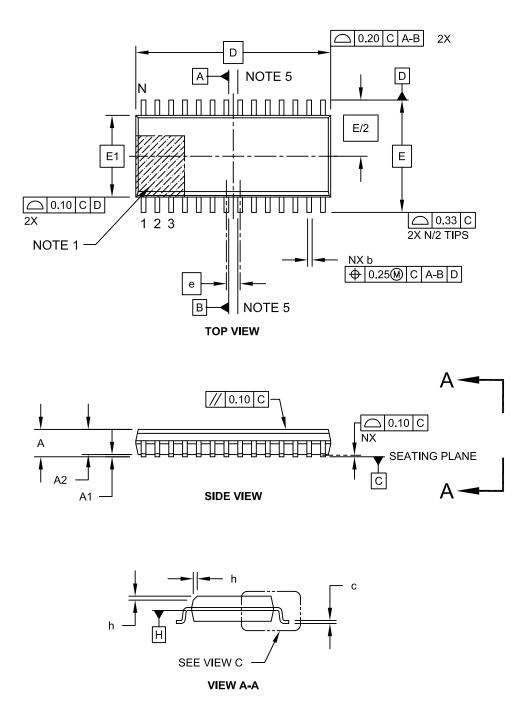

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

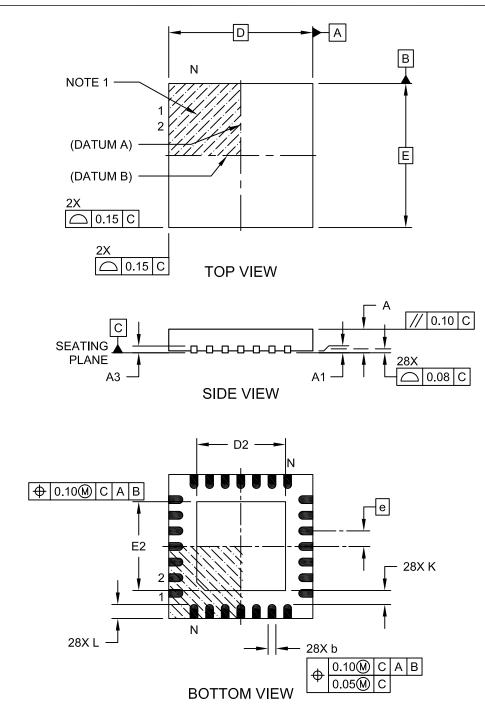

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2

## F

| Fail-Safe Clock Monitor (FSCM) | 65 |

|--------------------------------|----|

| Flash Program Memory           |    |

| Write Protection               |    |

## G

| 19 |

|----|

| 19 |

| 19 |

| 21 |

| 21 |

| 20 |

| 21 |

| 20 |

| 21 |

|    |

# н

| High/Low-Voltage Detect (HLVD)1    | 73 |

|------------------------------------|----|

| High/Low-Voltage Detect. See HLVD. |    |

## L

| I/O Ports                              | 77  |

|----------------------------------------|-----|

| Analog/Digital Port Pins Configuration | 78  |

| Open-Drain Configuration               | 78  |

| Parallel I/O (PIO)                     | 78  |

| Pull-up/Pull-Down Pins                 |     |

| Write/Read Timing                      | 78  |

| Input Change Notification (ICN)        | 78  |

| Instruction Set                        | 203 |

| Inter-IC Sound. See I <sup>2</sup> S.  |     |

| Internet Address                       |     |

## Μ

| MCCP/SCCP                                       |     |

|-------------------------------------------------|-----|

| Registers                                       |     |

| Memory Maps                                     |     |

| Devices with 16 Kbytes Program Memory           |     |

| Devices with 32 Kbytes Program Memory           | 35  |

| Devices with 64 Kbytes Program Memory           |     |

| Memory Organization                             |     |

| Alternate Configuration Bits Space              | 33  |

| Microchip Internet Web Site                     |     |

| MIPS32® microAptiv™ UC Core Configuration       |     |

| MPLAB Assembler, Linker, Librarian              |     |

| MPLAB ICD 3 In-Circuit Debugger                 | 201 |

| MPLAB PM3 Device Programmer                     | 201 |

| MPLAB REAL ICE In-Circuit Emulator System       | 201 |

| MPLAB X Integrated Development                  |     |

| Environment Software                            |     |

| MPLAB X SIM Software Simulator                  | 201 |

| MPLIB Object Librarian                          | 200 |

| MPLINK Object Linker                            | 200 |

| Multiply/Divide Unit Latencies and Repeat Rates |     |

| 0                                               |     |

| Oscillator Configuration                        | 65  |

| Р                                               |     |

| Package Thermal Resistance                      | 206 |

| Packaging                                       |     |

| Details                                         |     |

| Marking                                         |     |

| Peripheral Pin Select (PPS)                     |     |

| PICkit 3 In-Circuit Debugger/Programmer         |     |

Pinout Description ......14

| Power-Saving Features                     | 177 |

|-------------------------------------------|-----|

| Idle Mode                                 | 177 |

| Low-Power Brown-out Reset                 | 179 |

| On-Chip Voltage Regulator Low-Power Modes | 179 |

| Regulator Retention                       | 179 |

| Regulator Standby                         | 179 |

| Peripheral Module Disable                 |     |

| Sleep Mode                                |     |

| PPS                                       |     |

| Available Peripherals                     | 79  |

| Available Pins                            |     |

| Controlling                               |     |

| Controlling Configuration Changes         |     |

| Input Mapping                             |     |

| Input Pin Selection                       |     |

| Output Mapping                            |     |

| Output Pin Selection                      |     |

| Programming and Diagnostics               |     |

| 5 5 5 5                                   |     |

### R

| Real-Time Clock and Calendar (RTCC)          | 123 |

|----------------------------------------------|-----|

| Real-Time Clock and Calendar. See RTCC.      |     |

| Register Map                                 |     |

| ADC                                          | 135 |

| Alternate Configuration Words Summary        | 184 |

| Band Gap                                     | 195 |

| CDAC                                         |     |

| CLC1 and CLC2                                | 155 |

| Comparator 1 and 2                           | 164 |

| Configurations Words Summary                 |     |

| CRC                                          | 148 |

| Flash Controller                             | 38  |

| High/Low Voltage Detect                      | 174 |

| Interrupts                                   |     |

| MCCP/SCCP                                    |     |

| Oscillator Configuration                     | 67  |

| Peripheral Module Disable                    |     |

| Peripheral Pin Select                        |     |

| PORTA                                        | 82  |

| PORTB                                        |     |

| PORTC                                        | 84  |

| RAM Configuration, Device ID and System Lock | 192 |

| Reserved Registers                           |     |

| Resets                                       |     |

| RTCC                                         | 124 |

| SPI1 and SPI2                                |     |

| Timer1                                       |     |

| UART1 and UART2                              | 118 |

| UDID                                         | 197 |

| Watchdog Timer                               |     |

| Registers                                    |     |

| AD1CHIT (ADC Compare Hit)                    | 145 |

| AD1CHS (ADC Input Select)                    |     |

| AD1CON1 (ADC Control 1)                      |     |

| AD1CON2 (ADC Control 2)                      |     |

| AD1CON3 (ADC Control 3)                      |     |

| AD1CON5 (ADC Control 5)                      |     |

| AD1CSS (ADC Input Scan Select)               |     |

| ALMDATE (Alarm Date)                         |     |

| ANCFG (Band Gap Control)                     |     |

| CCPxCON1 (Capture/Compare/PWMx               |     |

| Control 1)                                   | 99  |

| CCPxCON2 (Capture/Compare/PWMx               |     |

| Control 2)                                   | 102 |

|                                              |     |