Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

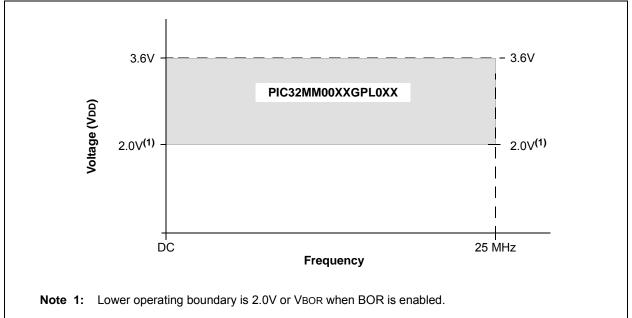

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 16                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 20-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl020t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

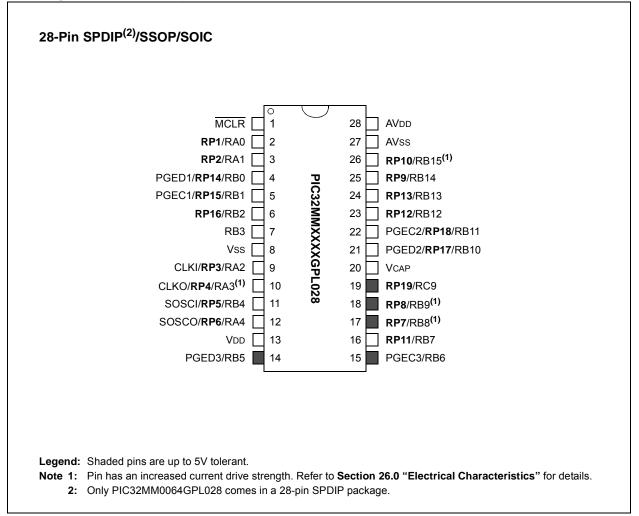

## **Pin Diagrams (Continued)**

#### TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN SPDIP/SSOP/SOIC DEVICES

| Pin | Function                                   | Pin | Function                                                                                |

|-----|--------------------------------------------|-----|-----------------------------------------------------------------------------------------|

| 1   | MCLR                                       | 15  | PGEC3/RB6                                                                               |

| 2   | VREF+/AN0/RP1/OCM1E/INT3/RA0               | 16  | <b>RP11</b> /RB7                                                                        |

| 3   | VREF-/AN1/ <b>RP2</b> /OCM1F/RA1           | 17  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                             |

| 4   | PGED1/AN2/C1IND/C2INB/RP14/RB0             | 18  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 5   | PGEC1/AN3/C1INC/C2INA/RP15/RB1             | 19  | RP19/RC9                                                                                |

| 6   | AN4/C1INB/ <b>RP16</b> /RB2                | 20  | VCAP                                                                                    |

| 7   | AN11/C1INA/RB3                             | 21  | PGED2/TDO/ <b>RP17</b> /RB10                                                            |

| 8   | Vss                                        | 22  | PGEC2/TDI/ <b>RP18</b> /RB11                                                            |

| 9   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                | 23  | AN7/LVDIN/ <b>RP12</b> /RB12                                                            |

| 10  | OSC2/CLKO/AN6/RP4/OCM1D/RA3 <sup>(1)</sup> | 24  | AN8/ <b>RP13</b> /RB13                                                                  |

| 11  | SOSCI/ <b>RP5</b> /RB4                     | 25  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                   |

| 12  | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4       | 26  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                              |

| 13  | Vdd                                        | 27  | AVss                                                                                    |

| 14  | PGED3/RB5                                  | 28  | AVDD                                                                                    |

Note 1: Pin has an increased current drive strength.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,   |

|-------|-----------------------------------------|

|       | browse the documentation section of the |

|       | Microchip web site (www.microchip.com). |

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 60. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS60001336)

- Section 62. "Dual Watchdog Timer" (DS60001365)

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. This data sheet contains device-specific information for the PIC32MM0064GPL036 family devices.

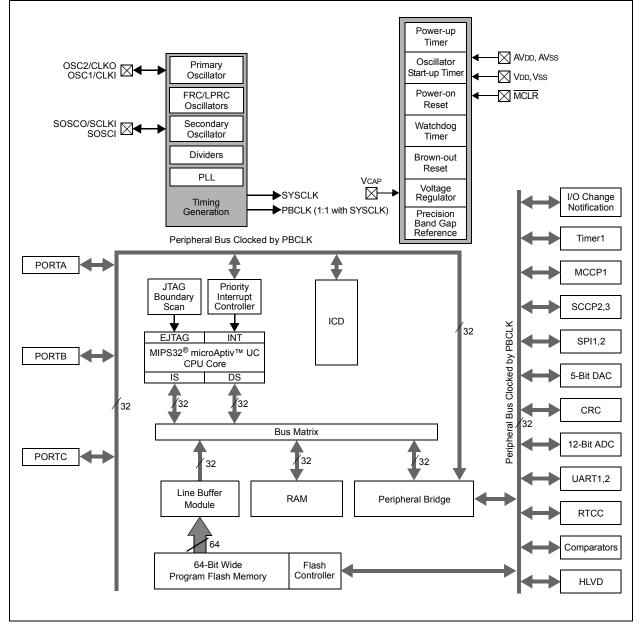

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0064GPL036 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

## FIGURE 1-1: PIC32MM0064GPL036 FAMILY BLOCK DIAGRAM

# PIC32MM0064GPL036 FAMILY

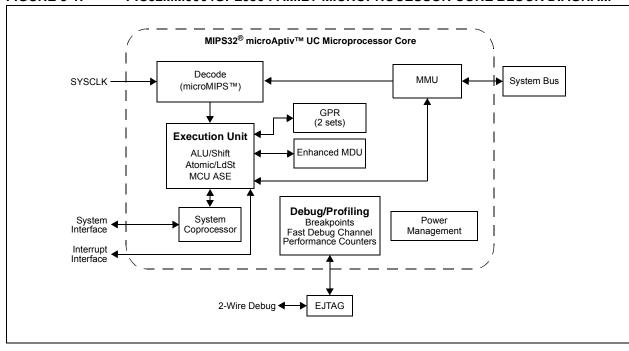

#### FIGURE 3-1: PIC32MM0064GPL036 FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|---------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 31:24        | _                 |                   | —                 | _                 | _                 | _                   | _                   | —                   |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 23:16        | —                 | _                 | _                 | -                 | _                 | —                   | _                   | _                   |

| 45.0         | R/W-1             | U-0               | U-0               | U-0               | U-0               | R/W-1               | R/W-1               | R/W-1               |

| 15:8         | BWPULOCK          | _                 | _                 | _                 | _                 | BWP2 <sup>(2)</sup> | BWP1 <sup>(2)</sup> | BWP0 <sup>(2)</sup> |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 7:0          |                   |                   | _                 | _                 | _                 |                     | _                   | —                   |

## REGISTER 5-7: NVMBWP: NVM BOOT FLASH (PAGE) WRITE-PROTECT REGISTER<sup>(1)</sup>

### Legend:

| 9                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BWPULOCK:** Boot Alias Write-Protect Unlock bit

- 1 = BWPx bits are not locked and can be modified

- 0 = BWPx bits are locked and cannot be modified

- This bit is only clearable and cannot be set except by any Reset.

- bit 14-11 Unimplemented: Read as '0'

- bit 10 **BWP2:** Boot Alias Page 2 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC00000 through 0x1FC007FF, is enabled 0 = Write protection for physical address, 0x1FC00000 through 0x1FC007FF, is disabled

- bit 9 **BWP1:** Boot Alias Page 1 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC00800 through 0x1FC00FFF, is enabled

- 0 = Write protection for physical address, 0x1FC00800 through 0x1FC00FFF, is disabled

- bit 8 **BWP0:** Boot Alias Page 0 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC01000 through 0x1FC017FF, is enabled

- 0 = Write protection for physical address, 0x1FC01000 through 0x1FC017FF, is disabled

- bit 7-0 Unimplemented: Read as '0'

- Note 1: Writes to this register require an NVMKEY unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

- 2: These bits can be modified only when the associated unlock bit (BWPULOCK) is set.

## 7.1 CPU Exceptions

CPU Coprocessor 0 contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events or program errors. Table 7-1 lists the exception types in order of priority.

## TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES

| Exception Type<br>(In Order of<br>Priority) | Description                                                                    | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set | EXCCODE     | XC32 Function Name         |

|---------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|-------------------|-------------|----------------------------|

|                                             |                                                                                | Highest Priority                                                         |                    |                   |             |                            |

| Reset                                       | Assertion of MCLR.                                                             | 0xBFC0_0000                                                              | BEV, ERL           | _                 | —           | _on_reset                  |

| Soft Reset                                  | Execution of a RESET instruction.                                              | 0xBFC0_0000                                                              | BEV, SR,<br>ERL    | —                 | —           | _on_reset                  |

| DSS                                         | EJTAG debug single step.                                                       | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | —                  | DSS               | —           | _                          |

| DINT                                        | EJTAG debug interrupt. Caused by setting the EjtagBrk bit in the ECR register. | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DINT              | _           | _                          |

| NMI                                         | Non-maskable interrupt.                                                        | 0xBFC0_0000                                                              | BEV, NMI,<br>ERL   | —                 | —           | _nmi_handler               |

| Interrupt                                   | Assertion of unmasked hardware or software interrupt signal.                   | See Table 7-2                                                            | IPL<2:0>           | _                 | Int (0x00)  | See Table 7-2              |

| DIB                                         | EJTAG debug hardware instruction break matched.                                | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIB               | _           | _                          |

| AdEL                                        | Load address alignment error.                                                  | EBASE + 0x180                                                            | EXL                | _                 | ADEL (0x04) | _general_exception_handler |

| IBE                                         | Instruction fetch bus error.                                                   | EBASE + 0x180                                                            | EXL                | —                 | IBE (0x06)  | _general_exception_handler |

| DBp                                         | EJTAG breakpoint (execution of SDBBP instruction).                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | DBp                | _                 | _           |                            |

| Sys                                         | Execution of SYSCALL instruction.                                              | EBASE + 0x180                                                            | EXL                | _                 | Sys (0x08)  | _general_exception_handler |

| Вр                                          | Execution of BREAK instruction.                                                | EBASE + 0x180                                                            | EXL                | _                 | Bp (0x09)   | _general_exception_handler |

## TABLE 7-3: INTERRUPT REGISTER MAP

| ress<br>()                  | <b>b a</b>                      | Ð         |             |        |        |        |               |                      |            | Bit    | 3        |          |          |               |             |            |             |                  | S2         |

|-----------------------------|---------------------------------|-----------|-------------|--------|--------|--------|---------------|----------------------|------------|--------|----------|----------|----------|---------------|-------------|------------|-------------|------------------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15       | 30/14  | 29/13  | 28/12  | 27/11         | 26/10                | 25/9       | 24/8   | 23/7     | 22/6     | 21/5     | 20/4          | 19/3        | 18/2       | 17/1        | 16/0             | All Resets |

|                             | IN IT COLU                      | 31:16     | _           | _      | _      | _      | _             | _                    | _          | _      | _        |          |          | VS<6:0>       |             |            |             |                  | 0000       |

| F000                        | INTCON                          | 15:0      |             | —      | _      | MVEC   |               |                      | TPC<2:0>   | •      | —        | —        | —        | INT4EP        | INT3EP      | INT2EP     | INT1EP      | INT0EP           | 0000       |

| 5040                        | <b>DDIOO</b>                    | 31:16     |             | PRI7S  | S<3:0> |        |               | PRI6SS               | S<3:0>     |        |          | PRI5S    | S<3:0>   |               |             | PRI4S      | S<3:0>      | •                | 0000       |

| F010                        | PRISS                           | 15:0      |             | PRI3S  | S<3:0> |        |               | PRI2S                | 6<3:0>     |        |          | PRI1S    | S<3:0>   |               | _           | _          | _           | SS0              | 0000       |

| F020                        | INTSTAT                         | 31:16     | _           | _      | _      | _      |               |                      |            | _      | _        | —        | _        | _             | _           | _          | _           | _                | 0000       |

| F020                        | INTSTAT                         | 15:0      | _           | _      | _      | _      | _             |                      | SRIPL<2:0> |        |          |          |          | SIRQ<         | 7:0>        |            |             |                  | 0000       |

| F030                        | IPTMR                           | 31:16     |             |        |        |        |               |                      |            | IPTMR< | 31.0>    |          |          |               |             |            |             |                  | 0000       |

|                             |                                 | 15:0      | IPTMR<31:0> |        |        |        |               |                      |            |        |          |          | 0000     |               |             |            |             |                  |            |

| F040                        | IFS0                            | 31:16     | CCP2IF      | CCT1IF | CCP1IF | —      |               | —                    | U1EIF      | U1TXIF | U1RXIF   | SPI1RXIF | SPI1TXIF | SPI1EIF       | CLC2IF      | CLC1IF     | LVDIF       | CRCIF            | 0000       |

|                             |                                 | 15:0      | AD1IF       | RTCCIF | CMP2IF | CMP1IF | T1IF          | CNCIF <sup>(2)</sup> | CNBIF      | CNAIF  | INT4IF   | INT3IF   | INT2IF   | INT1IF        | INTOIF      | CS1IF      | CS0IF       | CTIF             | 0000       |

| F050                        | IFS1                            | 31:16     | —           | —      | _      | _      | _             | —                    | —          | —      | —        | —        | —        |               | —           | —          | —           | —                | 0000       |

|                             |                                 | 15:0      | CPCIF       | NVMIF  | _      | —      | _             | U2EIF                | U2TXIF     | U2RXIF | SPI2RXIF | SPI2TXIF | SPI2EIF  | —             | —           | CCT3IF     | CCP3IF      | CCT2IF           | 0000       |

| F0C0                        | IEC0                            | 31:16     | CCP2IE      | CCT1IE | CCP1IE | —      | —             | —                    | U1EIE      | U1TXIE | U1RXIE   | SPI1RXIE | SPI1TXIE | SPI1EIE       | CLC2IE      | CLC1IE     | LVDIE       | CRCIE            | 0000       |

| 1000                        | IL00                            | 15:0      | AD1IE       | RTCCIE | CMP2IE | CMP1IE | T1IE          | CNCIE <sup>(2)</sup> | CNBIE      | CNAIE  | INT4IE   | INT3IE   | INT2IE   | INT1IE        | INT0IE      | CS1IE      | CS0IE       | CTIE             | 0000       |

| F0D0                        | IEC1                            | 31:16     | —           | —      | —      | —      | _             | —                    | —          | —      | —        | —        | —        | —             | —           | —          | _           | —                | 0000       |

| 1 020                       | ie01                            | 15:0      | CPCIE       | NVMIE  | —      | —      | —             | U2EIE                | U2TXIE     | U2RXIE | SPI2RXIE | SPI2TXIE | SPI2EIE  | —             | —           | CCT3IE     | CCP3IE      | CCT2IE           | 0000       |

| F140                        | IPC0                            | 31:16     |             |        |        |        | INT0IP<2:0>   | •                    | INTOIS     | i<1:0> |          | _        |          | CS1IP<2:0>    |             | CS1IS<1:0> |             | 0000             |            |

| 1 1 10                      | 1 00                            | 15:0      | _           |        |        |        | CS0IP<2:0>    |                      | CS0IS      | <1:0>  |          | _        | _        |               | CTIP<2:0>   |            | CTIS<       | :1:0>            | 0000       |

| F150                        | IPC1                            | 31:16     | _           |        |        |        | INT4IP<2:0>   | •                    | INT4IS     | 6<1:0> | _        |          | _        |               | INT3IP<2:0> | •          | INT3IS<1:0> |                  | 0000       |

| 1 100                       | 101                             | 15:0      | —           | —      | —      |        | INT2IP<2:0>   | •                    | INT2IS     | 6<1:0> | —        | —        | —        |               | INT1IP<2:0> |            | INT1IS      | <1:0>            | 0000       |

| F160                        | IPC2                            | 31:16     | —           | —      | —      |        | T1IP<2:0>     |                      | T1IS<      | <1:0>  | —        | —        | —        | C             | NCIP<2:0>(2 | 2)         | CNCIS<      | :1:0> <b>(2)</b> | 0000       |

| 1 100                       | 11 02                           | 15:0      | —           | —      | —      |        | CNBIP<2:0>    | •                    | CNBIS      | i<1:0> | —        | —        | —        |               | CNAIP<2:0>  |            | CNAIS       | <1:0>            | 0000       |

| F170                        | IPC3                            | 31:16     |             |        |        |        | AD1IP<2:0>    |                      | AD1IS      | <1:0>  |          | _        |          | F             | RTCCIP<2:0> | >          | RTCCIS      | S<1:0>           | 0000       |

| 1 170                       | 1 00                            | 15:0      | —           | —      | —      |        | CMP2IP<2:0    | >                    | CMP2I      | S<1:0> | —        | —        | —        | (             | CMP1IP<2:0  | >          | CMP1IS      | S<1:0>           | 0000       |

| F180                        | IPC4                            | 31:16     | _           |        |        |        | CLC2IP<2:0    | >                    | CLC2IS     | S<1:0> |          | _        | _        | (             | CLC1IP<2:0> | >          | CLC1IS      | 5<1:0>           | 0000       |

| 1 100                       | 11 04                           | 15:0      | —           | —      | —      |        | LVDIP<2:0>    |                      | LVDIS      | <1:0>  | —        | —        | —        | CRCIP<2:0>    |             | CRCIS      | <1:0>       | 0000             |            |

| F190                        | IPC5                            | 31:16     | —           | —      | —      |        | U1RXIP<2:0>   |                      |            | S<1:0> | —        | —        | —        | SPI1RXIP<2:0> |             |            | SPI1RXI     | S<1:0>           | 0000       |

| 1 130                       | 1 00                            | 15:0      | —           | —      | —      |        | SPI1TXIP<2:0> |                      |            | S<1:0> | —        | —        | —        | 5             | SPI1EIP<2:0 | >          | SPI1EIS     | 6<1:0>           | 0000       |

| F1A0                        | IPC6                            | 31:16     | —           | —      | _      | _      | -             | —                    | _          | —      | —        | —        | —        | _             | —           | —          | —           | —                | 0000       |

| 1 170                       | 1 00                            | 15:0      | _           | _      | —      |        | U1EIP<2:0>    |                      | U1EIS      | <1:0>  | —        | —        | —        | U1TXIP<2:0>   |             |            | U1TXIS      | 6<1:0>           | 0000       |

| F1B0                        | IPC7                            | 31:16     |             |        |        |        | CCP2IP<2:0    | >                    | CCP28      | S<1:0> | —        | —        | —        | (             | CCT1IP<2:0> | >          | CCT1IS      | 6<1:0>           | 0000       |

| 1 160                       | ii 0/                           | 15:0      | —           | _      | _      |        | CCP1IP<2:0    | >                    | CCP18      | S<1:0> | —        | —        | —        | _             | —           | —          | _           | —                | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

2: These bits are not available on 20-pin devices.

## REGISTER 12-4: CCPxSTAT: CAPTURE/COMPARE/PWMx STATUS REGISTER (CONTINUED)

| bit 3 | SCEVT: Single Edge Compare Event Status bit                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = A single edge compare event has occurred                                                                                                               |

|       | 0 = A single edge compare event has not occurred                                                                                                           |

| bit 2 | ICDIS: Input Capture Disable bit                                                                                                                           |

|       | <ul> <li>1 = Event on input capture pin does not generate a capture event</li> <li>0 = Event on input capture pin will generate a capture event</li> </ul> |

| bit 1 | ICOV: Input Capture Buffer Overflow Status bit                                                                                                             |

|       | 1 = The input capture FIFO buffer has overflowed                                                                                                           |

|       | 0 = The input capture FIFO buffer has not overflowed                                                                                                       |

| bit 0 | ICBNE: Input Capture Buffer Status bit                                                                                                                     |

|       | 1 = The input capture buffer has data available                                                                                                            |

|       | 0 = The input capture buffer is empty                                                                                                                      |

Note 1: This is not a physical bit location and will always read as '0'. A write of '1' will initiate the hardware event.

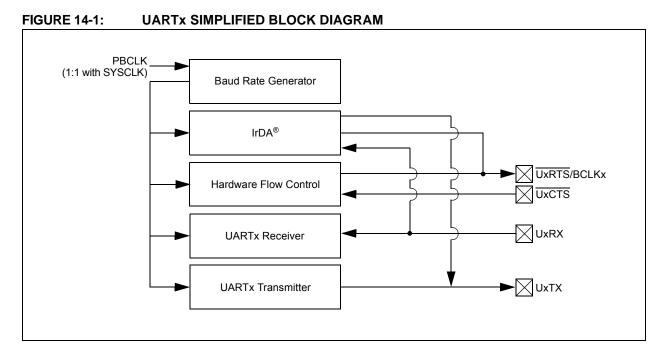

## 14.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21. "UART"** (DS61107) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

The UART module is one of the serial I/O modules available in the PIC32MM0064GPL036 family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN/J2602 and IrDA<sup>®</sup>. The module also supports the hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Auto-Baud Feature

- · Hardware Flow Control Option

- Fully Integrated Baud Rate Generator (BRG) with 16-Bit Prescaler

- Baud Rates Ranging from 47.7 bps to 6.26 Mbps at 25 MHz

- 8-Level Deep First-In-First-Out (FIFO) Transmit Data Buffer

- 8-Level Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for Interrupt Only on Address Detect (9th bit = 1)

- Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- LIN/J2602 Protocol Support

- IrDA Encoder and Decoder with 16x Baud Clock Output for External IrDA Encoder/Decoder Support

- · Supports Separate UART Baud Clock Input

- Ability to Continue to Run when a Receive Overflow (ROV) Condition Exists

- Ability to Run and Receive Data during Sleep mode

Figure 14-1 illustrates a simplified block diagram of the UART module.

© 2015-2016 Microchip Technology Inc.

## TABLE 16-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       | Bits            |           |        |          |         |         |       |          |                 |        |      |         |           |      |       |            |

|-----------------------------|---------------------------------|-----------|-------|-----------------|-----------|--------|----------|---------|---------|-------|----------|-----------------|--------|------|---------|-----------|------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15 | 30/14           | 29/13     | 28/12  | 27/11    | 26/10   | 25/9    | 24/8  | 23/7     | 22/6            | 21/5   | 20/4 | 19/3    | 18/2      | 17/1 | 16/0  | All Resets |

| 0750                        | ADC1BUF14                       | 31:16     |       |                 |           |        |          |         |         |       | 4 -04-05 |                 |        |      |         |           |      |       | 0000       |

| 07E0                        | ADC1B0F14                       | 15:0      |       | ADC1BUF14<31:0> |           |        |          |         |         |       |          |                 |        |      |         | 0000      |      |       |            |

| 0750                        | ADC1BUF15                       | 31:16     |       |                 |           |        |          |         | 10      |       | 5~31:0>  |                 |        |      |         |           |      |       | 0000       |

| 07F0                        | ADC IBUF 15                     | 15:0      |       | ADC1BUF15<31:0> |           |        |          |         |         |       |          |                 |        |      | 0000    |           |      |       |            |

| 0800                        | AD1CON1                         | 31:16     | _     | —               | —         | —      | —        | —       | —       | _     | —        | _               | —      | —    | _       | _         | _    | _     | 0000       |

| 0000                        | ADICONI                         | 15:0      | ON    |                 | SIDL      | —      | —        | F       | ORM<2:0 | >     |          | SSR             | C<3:0> | -    | MODE12  | ASAM      | SAMP | DONE  | 0000       |

| 0810                        | AD1CON2                         | 31:16     | _     | —               | —         | _      | _        | —       | —       | _     | —        | -               |        | —    | —       | _         | _    | _     | 0000       |

| 0010                        | AD TOON2                        | 15:0      |       | VCFG<2:0        | )>        | OFFCAL | BUFREGEN | CSCNA   | —       | —     | BUFS     | —               |        | SMF  | PI<3:0> |           | BUFM | —     | 0000       |

| 0820                        | AD1CON3                         | 31:16     | —     | —               | —         | —      | —        | —       | —       | —     | —        | —               | —      | —    | —       | —         | —    | —     | 0000       |

| 0020                        |                                 | 15:0      | ADRC  | EXTSAM          | —         |        | SAN      | 1C<4:0> |         |       |          |                 |        | AD   | CS<7:0> |           |      |       | 0000       |

| 0840                        | AD1CHS                          | 31:16     | _     | —               | —         | _      | _        | —       | —       | _     | —        | —               | —      | —    | —       | —         | —    | —     | 0000       |

|                             | 7.5 10110                       | 15:0      | —     | —               | —         | _      | _        | —       | —       | _     | C        | H0NA<2:         | 0>     |      | (       | CH0SA<4:0 | >    |       | 0000       |

| 0850                        | AD1CSS                          | 31:16     | —     |                 | CSS<30:28 | >      | —        | —       | —       | —     | —        | _               | —      | —    | —       | —         | —    | —     | 0000       |

| CSS<13:0> <sup>(1,2)</sup>  |                                 |           |       |                 |           |        |          | 0000    |         |       |          |                 |        |      |         |           |      |       |            |

| 0870                        | AD1CON5                         | 31:16     | —     | —               |           | —      | _        | —       | —       | _     | —        | _               |        |      | —       | _         | _    | —     | 0000       |

|                             |                                 | 15:0      | ASEN  | LPEN            |           | BGREQ  | _        | —       | ASINT   | <1:0> | —        | _               |        |      | WM<     | 1:0>      | CM<  | :1:0> | 0000       |

| 0880                        | AD1CHIT                         | 31:16     | —     | —               | —         | —      | —        | —       | —       | —     | —        | -               | —      | —    | —       | —         | —    | —     | 0000       |

| 2000                        |                                 | 15:0      | —     | —               |           |        |          |         |         |       | CHH<13   | 0> <b>(1,2)</b> |        |      |         |           |      |       | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The CSS<13:11> and CHH<13:11> bits are not implemented in 20-pin devices.

2: The CSS<13:12> and CHH<13:12> bits are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|--|

| 04.04        | U-0                 | U-0                 |  |

| 31:24        | _                 | _                 | _                 |                   |                   | —                 | —                   | —                   |  |

| 23:16        | U-0                 | U-0                 |  |

| 23.10        | —                 | _                 | -                 | —                 | —                 | —                 | —                   | —                   |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |  |

| 15:8         | ON                | _                 | SIDL              |                   |                   |                   | FORM<2:0>           |                     |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HSC          | R/W-0, HSC          |  |

| 7:0          |                   | SSRO              | C<3:0>            |                   | MODE12            | ASAM              | SAMP <sup>(1)</sup> | DONE <sup>(2)</sup> |  |

#### REGISTER 16-1: AD1CON1: ADC CONTROL REGISTER 1

| Legend:           | HSC = Hardware Settable | HSC = Hardware Settable/Clearable bit |                    |  |  |  |  |  |  |

|-------------------|-------------------------|---------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0'    |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit

- 1 = ADC module is operating

- 0 = ADC is off

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** ADC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- For 12-Bit Operation (MODE12 bit = 1):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dddd 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dddd 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 dddd dddd)

## For 10-Bit Operation (MODE12 bit = 0):

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd ddd0 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- **Note 1:** The SAMP bit is cleared and cannot be written if the ADC is disabled (ON bit = 0).

- 2: The DONE bit is not persistent in Automatic modes; it is cleared by hardware at the beginning of the next sample.

NOTES:

# PIC32MM0064GPL036 FAMILY

## REGISTER 19-2: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 AND 2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | -                 | _                 | _                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ON                | COE               | CPOL              | —                 | _                 | _                 | CEVT             | COUT             |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | EVPO              | _<1:0>            | _                 | CREF              | _                 | _                 | CCH•             | <1:0>            |

| Legend:         HC = Hardware Clearable bit |                  | HS = Hardware Settable bit         |                    |  |  |

|---------------------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit                            | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                           | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Comparator Enable bit

- 1 = Comparator is enabled

- 0 = Comparator is disabled

#### bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is present on the CxOUT pin

- 0 = Comparator output is internal only

- bit 13 CPOL: Comparator Output Polarity Select bit

- 1 = Comparator output is inverted

- 0 = Comparator output is not inverted

#### bit 12-10 Unimplemented: Read as '0'

- bit 9 CEVT: Comparator Event bit

- 1 = Comparator event that is defined by EVPOL<1:0> has occurred; subsequent triggers and interrupts are disabled until the bit is cleared

- 0 = Comparator event has not occurred

- bit 8 **COUT:** Comparator Output bit

$\frac{\text{When CPOL} = 0:}{1 = \text{VIN} + \text{VIN}-}$ 0 = VIN + VIN- $\frac{\text{When CPOL} = 1:}{1 = \text{VIN} + \text{VIN}-}$

0 = VIN + > VIN -

## 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 26.1 DC Characteristics

## FIGURE 26-1: PIC32MM0064GPL036 FAMILY VOLTAGE-FREQUENCY GRAPH

## TABLE 26-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min           | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| PIC32MM00XXGPL0XX:                                                                                                                                                                      |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                    |        | -40           | —   | +105 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40           | —   | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | Pint + Pi/o W |     | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                       |        | (Tj – Ta)/θja |     |      | W    |

## TABLE 26-2: PACKAGE THERMAL RESISTANCE<sup>(1)</sup>

| Package      | Symbol | Тур  | Unit |

|--------------|--------|------|------|

| 20-Pin SSOP  | θJA    | 87.3 | °C/W |

| 20-Pin QFN   | θJA    | 43.0 | °C/W |

| 28-Pin SPDIP | θJA    | 60.0 | °C/W |

| 28-Pin SSOP  | θJA    | 71.0 | °C/W |

| 28-Pin SOIC  | θJA    | 69.7 | °C/W |

| 28-Pin UQFN  | θJA    | 27.5 | °C/W |

| 28-Pin QFN   | θJA    | 20.0 | °C/W |

| 36-Pin VQFN  | θJA    | 31.1 | °C/W |

| 40-Pin UQFN  | θJA    | 41.0 | °C/W |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| Operatin      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                       |                    |                       |       |                                                                                                                                                          |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol                                                                                                                  | Characteristics                                                       | Min.               | Max.                  | Units | Conditions                                                                                                                                               |  |

| Dl60a         | licl                                                                                                                    | Input Low Injection<br>Current                                        | 0                  | <sub>-5</sub> (1,4)   | mA    | This parameter applies to all pins.                                                                                                                      |  |

| DI60b         | Іісн                                                                                                                    | Input High Injection<br>Current                                       | 0                  | +5 <sup>(2,3,4)</sup> | mA    | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins and SOSCI. Maximum IICH<br>current for these exceptions is<br>0 mA. |  |

| DI60c         | ∑ІІСТ                                                                                                                   | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(5)</sup> | +20 <sup>(5)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents from<br>all I/O pins,<br>(   IICL +   IICH   ) $\leq \sum$ IICT                      |  |

**Note 1:** VIL Source < (Vss - 0.3). Characterized but not tested.

2: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

**3:** Digital 5V tolerant pins do not have an internal high-side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

4: Injection currents can affect the ADC results.

5: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit.

## TABLE 26-22: RESET, BROWN-OUT RESET AND SLEEP MODES TIMING SPECIFICATIONS

| Operati      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                         |     |                    |     |       |                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|--------------------|-----|-------|----------------------------------------------------------|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                          | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                               |

| SY10         | TMCL                                                                                                                    | MCLR Pulse Width (Low)                                  | 2   | —                  | _   | μs    |                                                          |

| SY13         | Tioz                                                                                                                    | I/O High-Impedance from<br>MCLR Low                     | _   | 1                  | _   | μs    |                                                          |

| SY25         | TBOR                                                                                                                    | Brown-out Reset Pulse<br>Width                          | 1   | —                  | —   | μs    | $VDD \leq VBOR$                                          |

| SY45         | TRST                                                                                                                    | Reset State Time                                        | _   | 25                 | _   | μs    |                                                          |

| SY71         | Twake <sup>(2)</sup>                                                                                                    | Wake-up Time with Main<br>Voltage Regulator             | _   | 22                 | _   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 0,<br>RETVR = 1 |

|              |                                                                                                                         |                                                         | _   | 3.8                | —   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 0,<br>RETVR = 1 |

| SY72         | Twakelvr <sup>(2)</sup>                                                                                                 | Wake-up Time with<br>Retention Low-Voltage<br>Regulator | _   | 163                | —   | μs    | Sleep wake-up with<br>VREGS = 0, RETEN = 1,<br>RETVR = 0 |

|              |                                                                                                                         |                                                         |     | 23                 | _   | μs    | Sleep wake-up with<br>VREGS = 1, RETEN = 1,<br>RETVR = 0 |

**Note 1:** Data in the "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The parameters are measured with the external clock source (EC). To get the full wake-up time, the oscillator start-up time must be added.

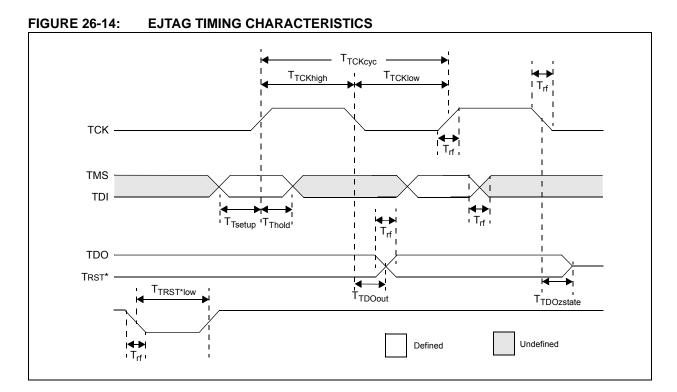

# TABLE 26-33: EJTAG TIMING REQUIREMENTS

| Operati       | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                     |     |     |       |            |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-------|------------|--|

| Param.<br>No. | Symbol                                                                                                                  | Description <sup>(1)</sup>                          | Min | Max | Units | Conditions |  |

| EJ1           | Ттсксүс                                                                                                                 | TCK Cycle Time                                      | 25  |     | ns    |            |  |

| EJ2           | Ттскнідн                                                                                                                | TCK High Time                                       | 10  | _   | ns    |            |  |

| EJ3           | TTCKLOW                                                                                                                 | TCK Low Time                                        | 10  | _   | ns    |            |  |

| EJ4           | TTSETUP                                                                                                                 | TAP Signals Setup Time before<br>Rising TCK         | 5   |     | ns    |            |  |

| EJ5           | TTHOLD                                                                                                                  | TAP Signals Hold Time after<br>Rising TCK           | 3   |     | ns    |            |  |

| EJ6           | Ττροουτ                                                                                                                 | TDO Output Delay Time from<br>Falling TCK           | —   | 5   | ns    |            |  |

| EJ7           | TTDOZSTATE                                                                                                              | TDO 3-State Delay Time from<br>Falling TCK          | —   | 5   | ns    |            |  |

| EJ8           | TTRSTLOW                                                                                                                | TRST Low Time                                       | 25  | _   | ns    |            |  |

| EJ9           | Trf                                                                                                                     | TAP Signals Rise/Fall Time,<br>All Input and Output | —   | _   | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

NOTES: