#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl028-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Power Management

The processor core offers a number of power management features, including low-power design, active power management and Power-Down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

The mechanism for invoking Power-Down mode is implemented through execution of the WAIT instruction. The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MM family makes extensive use of local gated clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The microAptiv UC core has an Enhanced JTAG (EJTAG) interface for use in the software debug. In addition to the standard mode of operation, the microAptiv UC core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the microAptiv UC core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

# 3.5 MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the microAptiv UC core, which is included on PIC32MM0064GPL036 family devices.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0064GPL036 family devices contain an internal Flash program memory for executing user code. The Program and Boot Flash Memory can be write-protected. The erase page size is 512 32-bit words. The program row size is 64 32-bit words. The memory can be programmed by rows or by two 32-bit words.

The devices implement an Error Correcting Code (ECC). The memory control block contains a logic to write and read ECC bits to and from the Flash memory. The Flash is programmed at the same time as the corresponding ECC bits. The ECC provides improved resistance to Flash errors. The ECC single-bit error will be transparently corrected. The ECC double-bit error results in a bus error exception.

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is described in **Section 5. "Flash Programming"** in the *"PIC32 Family Reference Manual"*. EJTAG programming is performed using the JTAG port of the device. ICSP programming requires fewer connections than for EJTAG programming. The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip web site.

#### 5.1 Flash Controller Registers Write Protection

The NVMPWP and NVMBWP registers, and the WR bit in the NVMCON register are protected (locked) from an accidental write. A special unlock sequence is required to modify the content of these registers or bits.

To unlock, the following steps should be done:

- 1. Disable interrupts prior to the unlock sequence.

- 2. Execute the system unlock sequence by writing the key values of 0xAA996655 and 0x556699AA to the NVMKEY register in two back-to-back Assembly or 'C' instructions.

- 3. Write the new value to the required bits.

- 4. Re-enable interrupts.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 24.04        | R/W-1, HS         | R/W-1, HS         | U-0               | U-0               | R/W-0, HS         | R/W-0, HS           | U-0              | U-0              |

| 31:24        | PORIO             | PORCORE           |                   | —                 | BCFGERR           | BCFGFAIL            | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | —                 | _                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | R/W-0, HS        | U-0              |

| 15:8         | _                 | _                 |                   | —                 | —                 | _                   | CMR              | _                |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS           | R/W-1, HS        | R/W-1, HS        |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE <sup>(2)</sup> | BOR              | POR              |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | PORIO: VDD POR Flag bit                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Set by hardware at detection of a VDD POR event.<br>1 = A Power-on Reset has occurred due to VDD voltage<br>0 = A Power-on Reset has not occurred due to VDD voltage                                        |

| bit 30    | PORCORE: Core Voltage POR Flag bit                                                                                                                                                                          |

|           | Set by hardware at detection of a core POR event.<br>1 = A Power-on Reset has occurred due to core voltage<br>0 = A Power-on Reset has not occurred due to core voltage                                     |

| bit 29-28 | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 27    | BCFGERR: Primary Configuration Registers Error Flag bit                                                                                                                                                     |

|           | <ul> <li>1 = An error occurred during a read of the Primary Configuration registers</li> <li>0 = No error occurred during a read of the Primary Configuration registers</li> </ul>                          |

| bit 26    | BCFGFAIL: Primary/Secondary Configuration Registers Error Flag bit                                                                                                                                          |

|           | <ul><li>1 = An error occurred during a read of the Primary and Alternate Configuration registers</li><li>0 = No error occurred during a read of the Primary and Alternate Configuration registers</li></ul> |

| bit 25-10 | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 9     | CMR: Configuration Mismatch Reset Flag bit                                                                                                                                                                  |

|           | <ul><li>1 = A Configuration Mismatch Reset has occurred</li><li>0 = A Configuration Mismatch Reset has not occurred</li></ul>                                                                               |

| bit 8     | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 7     | EXTR: External Reset (MCLR) Pin Flag bit                                                                                                                                                                    |

|           | <ul><li>1 = Master Clear (pin) Reset has occurred</li><li>0 = Master Clear (pin) Reset has not occurred</li></ul>                                                                                           |

| bit 6     | SWR: Software Reset Flag bit                                                                                                                                                                                |

|           | <ul><li>1 = Software Reset was executed</li><li>0 = Software Reset was not executed</li></ul>                                                                                                               |

| bit 5     | Unimplemented: Read as '0'                                                                                                                                                                                  |

| bit 4     | WDTO: Watchdog Timer Time-out Flag bit                                                                                                                                                                      |

|           | 1 = WDT time-out has occurred                                                                                                                                                                               |

|           | 0 = WDT time-out has not occurred                                                                                                                                                                           |

| Note 1:   | User software must clear bits in this register to view the next detection.                                                                                                                                  |

2: The IDLE bit will also be set when the device wakes from Sleep mode.

# 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupts" (DS60001108) and Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM

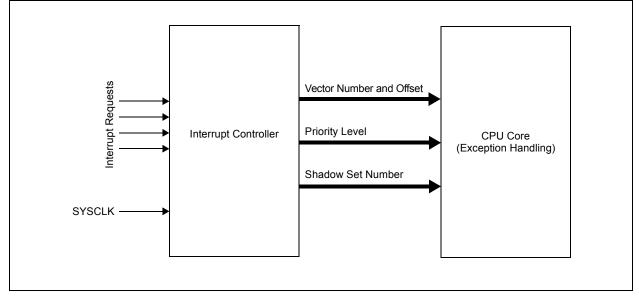

PIC32MM0064GPL036 family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in Section 7.1 "CPU Exceptions". The PIC32MM0064GPL036 family device interrupt module includes the following features:

- · Single Vector or Multivector mode Operation

- Five External Interrupts with Edge Polarity Control

- · Interrupt Proximity Timer

- Module Freeze in Debug mode

- Seven User-Selectable Priority Levels for each Vector

- Four User-Selectable Subpriority Levels within each Priority

- One Shadow Register Set that can be used for any Priority Level, Eliminating Software Context Switching and Reducing Interrupt Latency

- · Software can Generate any Interrupt

- User-Configurable Interrupt Vectors' Offset and Vector Table Location

Figure 7-1 shows the block diagram for the interrupt controller and CPU exceptions.

#### FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| CpU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | _                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          |                    |                                                                            |                |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

# 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRI             | //<8:1>           |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | _                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### **REGISTER 8-4: REFO1TRIM: REFERENCE OSCILLATOR TRIM REGISTER**<sup>(1,2,3)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

- bit 22-0 Unimplemented: Read as '0'

- **Note 1:** While the ON bit (REFO1CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- Do not write to this register when the ON bit (REFO1CON<15>) is not equal to the ACTIVE bit (REFO1CON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> (REFO1CON<30:16>) = 0.

#### REGISTER 12-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER (CONTINUED)

- bit 14 ASDGM: CCPx Auto-Shutdown Gate Mode Enable bit

- 1 = Waits until the next Time Base Reset or rollover for shutdown to occur

- 0 = Shutdown event occurs immediately

- bit 13 Unimplemented: Read as '0'

- bit 12 SSDG: CCPx Software Shutdown/Gate Control bit

- 1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting the ASDGM bit still applies)

- 0 = Normal module operation

- bit 11-8 Unimplemented: Read as '0'

- bit 7-0 ASDG<7:0>: CCPx Auto-Shutdown/Gating Source Enable bits

- 1xxx xxxx = Auto-shutdown is controlled by the OCFB pin (remappable)

- x1xx xxxx = Auto-shutdown is controlled by the OCFA pin (remappable)

- xx1x xxxx = Auto-shutdown is controlled by CLC1 for MCCP1/SCCP2 and by CLC2 for SCCP3

- xxx1 xxxx = Auto-shutdown is controlled by the SCCP2 output for MCCP1 and by MCCP1 for SCCP2/SCCP3

- xxxx 1xxx = Auto-shutdown is controlled by the SCCP3 output for MCCP1/SCCP2 and by SCCP2 for SCCP3

- xxxx x1xx = Reserved

- xxxx xx1x = Auto-shutdown is controlled by Comparator 2

- xxxx xxx1 = Auto-shutdown is controlled by Comparator 1

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

# PIC32MM0064GPL036 FAMILY

#### REGISTER 15-3: RTCSTAT: RTCC STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | _                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 |                   | —                 | _                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | R-0, HS, HC       | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          | _                 | _                 | ALMEVT            | _                 | _                 | SYNC              | ALMSYNC          | HALFSEC          |

| Legend:HC = Hardware Clearable bit |                  | HS = Hardware Settable bit         |                    |  |

|------------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

#### bit 5 ALMEVT: Alarm Event bit

- 1 = An alarm event has occurred

- 0 = An alarm event has not occurred

#### bit 4-3 Unimplemented: Read as '0'

- bit 2 SYNC: Synchronization Status bit

- 1 = Time registers may change during software read

- 0 = Time registers may be read safely

#### bit 1 ALMSYNC: Alarm Synchronization status bit

- 1 = Alarm registers (ALMTIME and ALMDATE) and RTCCON1 should not be modified; the ALRMEN and ALMRPT<7:0> bits may change during software read

- 0 = Alarm registers and Alarm Control registers may be modified safely

#### bit 0 HALFSEC: Half Second Status bit

- 1 = Second half of 1-second period

- 0 = First half of 1-second period

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 | -                 | —                 | —                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | CH0NA<2:0>        |                   |                   |                   | C                 | H0SA<4:0>(1       | )                |                  |

#### REGISTER 16-5: AD1CHS: ADC INPUT SELECT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

- bit 7-5 CH0NA<2:0>: Negative Input Select bits

- 111-001 = Reserved 000 = Negative input is AVss

- bit 4-0 CH0SA<4:0>: Positive Input Select bits<sup>(1)</sup>

- 11111 = Reserved

- 11110 = Positive input is AVDD

- 11101 = Positive input is AVss

- 11100 = Positive input is Band Gap Reference (VBG)

- 11011-01110 = Reserved

- 01101 = Positive input is  $AN13^{(2,3)}$

- 01100 = Positive input is AN12<sup>(2,3)</sup>

- 01011 = Positive input is AN11<sup>(2)</sup>

- 01010 = Positive input is AN10

- 01001 = Positive input is AN9

- 01000 = Positive input is AN8

- 00111 = Positive input is AN7

- 00110 = Positive input is AN6

- 00101 = Positive input is AN5 00100 = Positive input is AN4

- 00011 = Positive input is AN3

- 00011 = Positive input is AN3 00010 = Positive input is AN2

- 00010 = Positive input is AN2 00001 = Positive input is AN1

- 00000 = Positive input is AN0

- **Note 1:** The CH0SA<4:0> positive input selection is only used when CSCNA (AD1CON2<10>) = 0 and ASEN (AD1CON5<15>) = 0. The AD1CSS bits specify the positive inputs when CSCNA = 1 or ASEN = 1.

- 2: This option is not implemented in the 20-pin devices.

- 3: This option is not implemented in the 28-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                 | _                 | —                 |                   | DWIDTH<4:0>       |                   |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | _                 | —                 | PLEN<4:0>         |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |

| 15:8         | ON                | _                 | SIDL              |                   | ١                 | /WORD<4:0>        |                  |                  |  |  |

| 7.0          | R-0, HS, HC       | R-1, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |

| 7:0          | CRCFUL            | CRCMPT            | CRCISEL           | CRCGO             | LENDIAN           | MOD               | _                | _                |  |  |

#### REGISTER 17-1: CRCCON: CRC CONTROL REGISTER

| Legend:         HC = Hardware Clearable bit |                  | HS = Hardware Settable bit              |  |  |

|---------------------------------------------|------------------|-----------------------------------------|--|--|

| R = Readable bit                            | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |

| -n = Value at POR                           | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **DWIDTH<4:0>:** Data Word Width Configuration bits Configures the width of the data word (Data Word Width – 1).

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **PLEN<4:0>:** Polynomial Length Configuration bits Configures the length of the polynomial (Polynomial Length – 1).

- bit 15 ON: CRC Enable bit

- 1 = Enables module

- 0 = Disables module

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: CRC Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12-8 VWORD<4:0>: Counter Value bits

Indicates the number of valid words in the FIFO. Has a maximum value of 16 when DWIDTH<4:0>  $\leq$  (data words, 8-bit wide or less). Has a maximum value of 8 when DWIDTH<4:0>  $\leq$  15 (data words from 9 to 16-bit wide). Has a maximum value of 4 when DWIDTH<4:0>  $\leq$  31 (data words from 17 to 32-bit wide).

- bit 7 CRCFUL: CRC FIFO Full bit 1 = FIFO is full

- 0 = FIFO is not full

- bit 6 **CRCMPT:** CRC FIFO Empty bit

- 1 = FIFO is empty

- 0 = FIFO is not empty

- bit 5 CRCISEL: CRC Interrupt Selection bit

- 1 = Interrupt on FIFO is empty; final word of data is still shifted through CRC

- 0 = Interrupt on shift is complete (FIFO is empty and no data is shifted from the shift buffer)

- bit 4 CRCGO: Start CRC bit

- 1 = Starts CRC serial shifter; clearing the bit aborts shifting

- 0 = CRC serial shifter is turned off

#### bit 3 LENDIAN: Data Word Little-Endian Configuration bit

- 1 = Data word is shifted into the CRC, starting with the LSb (little-endian); reflected input data

- 0 = Data word is shifted into the CRC, starting with the MSb (big-endian); non-reflected input data

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | —                 | _                 | _                 | —                | —                |

| 00.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 |                   | —                |                  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0             | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ON                | _                 | SIDL              | _                 | VDIR              | BGVST             | IRVST            | HLEVT            |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   |                   | HLVDL             | <3:0>            |                  |

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| Legend: HC = Hardware Clearable bit |                  | HS = Hardware Settable bit       |            |  |  |

|-------------------------------------|------------------|----------------------------------|------------|--|--|

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit, read as ' | 0'         |  |  |

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared x = Bit     | is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** HLVD Power Enable bit

- 1 = HLVD is enabled

- 0 = HLVD is disabled

#### bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** HLVD Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12 Unimplemented: Read as '0'

- bit 11 VDIR: Voltage Change Direction Select bit

- 1 = Event occurs when voltage equals or exceeds the trip point (HLVDL<3:0>)

- 0 = Event occurs when voltage equals or falls below the trip point (HLVDL<3:0>)

- bit 10 BGVST: Band Gap Voltage Stable Flag bit

- 1 = Indicates that the band gap voltage is stable

- 0 = Indicates that the band gap voltage is unstable

- bit 9 IRVST: Internal Reference Voltage Stable Flag bit

- 1 = Internal reference voltage is stable; the High-Voltage Detect logic generates the interrupt flag at the specified voltage range

- 0 = Internal reference voltage is unstable; the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the HLVD interrupt should not be enabled

- bit 8 HLEVT: High/Low-Voltage Detection Event Status bit

- 1 = Indicates HLVD event is active

- 0 = Indicates HLVD event is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in **Section 26.0** "**Electrical Characteristics**" for minimum and maximum values.

## 22.4 On-Chip Voltage Regulator Low-Power Modes

The main on-chip regulator always consumes an incremental amount of current over IDD/IPD, including when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator can be made to enter Standby mode and/ or Retention mode. Standby mode is controlled by the VREGS bit (PWRCON<0>), and Retention mode is controlled by the RETEN (PWRCON<1>) and RETVR (FPOR<2>) bits. The available Regulator Low-Power modes are listed in Table 22-2. For more information about the wake-up time and the current consumption for different modes, refer to the electrical specifications listed in Table 26-6 and Table 26-22.

| <b>TABLE 22-2:</b> | VOLTAGE REGULATOR LOW-POWER MODES |

|--------------------|-----------------------------------|

|                    |                                   |

| Mode                  | VREGS Bit<br>(PWRCON<0>) | RETEN Bit<br>(PWRCON<1>) | RETVR Bit<br>(FPOR<2>) | Wake-up Time<br>(Table 26-22) | Current<br>(Table 26-6) |

|-----------------------|--------------------------|--------------------------|------------------------|-------------------------------|-------------------------|

| Normal                | 1                        | 0                        | 1                      | Fastest                       | Highest                 |

| Standby Only          | 0                        | 0                        | 1                      | Medium                        | Medium                  |

| Retention Only        | 1                        | 1                        | 0                      | Medium                        | Medium                  |

| Standby and Retention | 0                        | 1                        | 0                      | Slowest                       | Lowest                  |

#### 22.4.1 REGULATOR STANDBY MODE

Whenever the device goes into Sleep mode, the regulator can be made to enter Standby mode. This feature is controlled by the VREGS bit (PWRCON<0>). Clearing the VREGS bit enables Standby mode. If Standby mode is used, the voltage regulator needs some time to switch to normal operation mode and generate output. During this time, the code execution is disabled. The delay is applied every time the device resumes operation after Standby mode.

# 22.4.2 REGULATOR RETENTION MODE

When in Sleep mode, the device can use a separate low-power, low-voltage/retention regulator to power critical circuits. This regulator, which operates at 1V nominal, maintains power to data RAM, WDT, Timer1 and the RTCC, while all other core digital logic is powered down. The low-voltage/retention regulator is available only when Sleep mode is invoked. It is controlled by the RETVR Configuration bit (FPOR<2>) and in firmware by the RETEN bit (PWRCON<1>). RETVR must be programmed to zero (= 0) and the RETEN bit must be set (= 1) for the retention regulator to be enabled.

# 22.5 Low-Power Brown-out Reset

The PIC32MM0064GPL036 family devices have a second low-power Brown-out Reset circuit with a reduced precision of the trip point. This low-power BOR circuit can be activated when the main BOR is disabled. The circuit is enabled by programming the LPBOREN Configuration bit (FPOR<3>) to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                 | —                 | —                 |                   |                   | _                 | —                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | —                 | —                 |                   |                   | _                 | —                | —                |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 15:8         | FWDTEN            | RCLKS             | EL<1:0>           |                   |                   | RWDTPS<4:         | 0>               |                  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 7:0          | WINDIS            | FWDTWI            | NSZ<1:0>          | SWDTPS<4:0>       |                   |                   |                  |                  |

#### REGISTER 23-4: FWDT/AFWDT: WATCHDOG TIMER CONFIGURATION REGISTER

| Legend: r = Reserved bit |                  | P = Programmable bit                    |  |  |

|--------------------------|------------------|-----------------------------------------|--|--|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |

| -n = Value at POR        | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |

- bit 31-16 Reserved: Program as '1'

- bit 15 **FWDTEN:** Watchdog Timer Enable bit

- 1 = WDT is enabled

- 0 = WDT is disabled

#### bit 14-13 RCLKSEL<1:0>: Run Mode Watchdog Timer Clock Source Selection bits

- 11 = Clock source is the LPRC oscillator (same as for Sleep mode)

- 10 = Clock source is the FRC oscillator

- 01 = Reserved

- $\tt 00$  = Clock source is the system clock

#### bit 12-8 RWDTPS<4:0>: Run Mode Watchdog Timer Postscale Select bits

| From 10100 to 11111 = 1:1048576. |

|----------------------------------|

| 10011 <b>= 1:524288</b>          |

| 10010 <b>= 1:262144</b>          |

| 10001 <b>= 1:131072</b>          |

| 10000 <b>= 1:65536</b>           |

| 01111 <b>= 1:32768</b>           |

| 01110 <b>= 1:16384</b>           |

| 01101 <b>= 1:8192</b>            |

| 01100 = 1:4096                   |

| 01011 <b>= 1:2048</b>            |

| 01010 = 1:1024                   |

| 01001 = 1:512                    |

| 01000 <b>= 1:256</b>             |

| 00111 <b>= 1:128</b>             |

| 00110 = 1:64                     |

| 00101 <b>= 1:32</b>              |

| 00100 = 1:16                     |

| 00011 = 1:8                      |

| 00010 = 1:4                      |

| 00001 = 1:2                      |

| 00000 = 1:1                      |

bit 7 WINDIS: Windowed Watchdog Timer Disable bit

- 1 = Windowed mode is disabled

- 0 = Windowed mode is enabled

# 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MM0064GPL036 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MM0064GPL036 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(†)</sup>

+

| Ambient temperature under bias<br>Storage temperature                                        |                               |

|----------------------------------------------------------------------------------------------|-------------------------------|

| Voltage on VDD with respect to Vss                                                           | -0.3V to +4.0V                |

| Voltage on any general purpose digital or analog pin (not 5.5V tolerant) with respect to Vs  | s0.3V to (VDD + 0.3V)         |

| Voltage on any general purpose digital or analog pin (5.5V tolerant) with respect to Vss:    |                               |

| When VDD = 0V:                                                                               | -0.3V to +4.0V                |

| When VDD $\geq$ 2.0V:                                                                        | -0.3V to +6.0V                |

| Voltage on AVDD with respect to Vss                                                          | ser of: 4.0V or (VDD + 0.3V)) |

| Voltage on AVss with respect to Vss                                                          | -0.3V to +0.3V                |

| Maximum current out of Vss pin                                                               |                               |

| Maximum current into Vod pin <sup>(1)</sup>                                                  |                               |

| Maximum output current sunk by I/O pin                                                       | 11 mA                         |

| Maximum output current sourced by I/O pin                                                    |                               |

| Maximum output current sunk by I/O pin with increased current drive strength (RA3, RB8,      | RB9 and RB15)17 mA            |

| Maximum output current sourced by I/O pin with increased current drive strength (RA3, RB8, F | RB9 and RB15)24 mA            |

| Maximum current sunk by all ports                                                            |                               |

| Maximum current sourced by all ports <sup>(1)</sup>                                          |                               |

|                                                                                              |                               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 26-1).

**NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Operatin      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                       |                    |                       |       |                                                                                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol                                                                                                                  | Characteristics                                                       | Min.               | Max.                  | Units | Conditions                                                                                                                                               |

| Dl60a         | licl                                                                                                                    | Input Low Injection<br>Current                                        | 0                  | <sub>-5</sub> (1,4)   | mA    | This parameter applies to all pins.                                                                                                                      |

| DI60b         | Іісн                                                                                                                    | Input High Injection<br>Current                                       | 0                  | +5 <sup>(2,3,4)</sup> | mA    | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins and SOSCI. Maximum IICH<br>current for these exceptions is<br>0 mA. |

| DI60c         | ∑ІІСТ                                                                                                                   | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(5)</sup> | +20 <sup>(5)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents from<br>all I/O pins,<br>(   IICL +   IICH   ) $\leq \sum$ IICT                      |

**Note 1:** VIL Source < (Vss - 0.3). Characterized but not tested.

2: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

**3:** Digital 5V tolerant pins do not have an internal high-side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

4: Injection currents can affect the ADC results.

5: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit.

| TABLE 26-18: | PLL CLOCK TIMING SPECIFICATIONS |

|--------------|---------------------------------|

|--------------|---------------------------------|

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |        |                                           |       |      |       |  |

|-------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------|-------|------|-------|--|

| Param<br>No.                                                                                                            | Symbol | Characteristic                            | Min   | Мах  | Units |  |

| OS50                                                                                                                    | Fplli  | PLL Input Frequency Range <sup>(1)</sup>  | 2     | 24   | MHz   |  |

| OS54                                                                                                                    | Fpllo  | PLL Output Frequency Range <sup>(1)</sup> | 16    | 96   | MHz   |  |

| OS52                                                                                                                    | TLOCK  | PLL Start-up Time (Lock Time)             | —     | 24   | μs    |  |

| OS53                                                                                                                    | DCLK   | CLKO Stability (Jitter)                   | -0.12 | 0.12 | %     |  |

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 26-19: INTERNAL OSCILLATOR ACCURACY<sup>(1)</sup>

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                         |     |                    |     |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|--------------------|-----|-------|--|--|

| Param No.                                                                                                               | Characteristic                          | Min | Тур <sup>(2)</sup> | Max | Units |  |  |

| F20                                                                                                                     | FRC Accuracy @ 8 MHz                    | -3  | _                  | 3   | %     |  |  |

| F21                                                                                                                     | LPRC @ 32 kHz                           | -20 |                    | 20  | %     |  |  |

| F22                                                                                                                     | FRC Tune Step-Size (in OSCTUN register) |     | 0.05               |     | %/Bit |  |  |

**Note 1:** To achieve this accuracy, physical stress applied to the microcontroller package (ex., by flexing the PCB) must be kept to a minimum.

2: Data in the "Typ" column is 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 26-20: INTERNAL OSCILLATOR START-UP TIME

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                       |                                       |     |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------|-----|-------|--|--|

| Param<br>No.                                                                                                            | Symbol Characteristic |                                       | Мах | Units |  |  |

| FR0                                                                                                                     | TFRC                  | FRC Oscillator Start-up Time          | 2   | μs    |  |  |

| FR1                                                                                                                     | TLPRC                 | Low-Power RC Oscillator Start-up Time | 70  | μs    |  |  |

# 27.1 Package Marking Information (Continued)

28-Lead SSOP

28-Lead QFN

28-Lead UQFN

36-Lead VQFN

40-Lead UQFN

Example

# Example

# Example

# Example

# Example

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

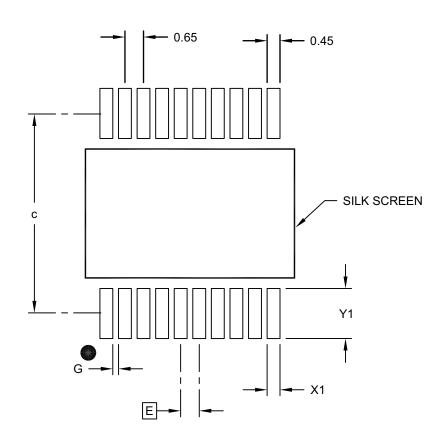

# RECOMMENDED LAND PATTERN

| Units                    |                  | MILLIMETERS |      |      |

|--------------------------|------------------|-------------|------|------|

| Dimensio                 | Dimension Limits |             | NOM  | MAX  |

| Contact Pitch            | E                | 0.65 BSC    |      |      |

| Contact Pad Spacing      | С                |             | 7.20 |      |

| Contact Pad Width (X20)  | X1               |             |      | 0.45 |

| Contact Pad Length (X20) | Y1               |             |      | 1.75 |

| Distance Between Pads    | G                | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B

NOTES: