#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

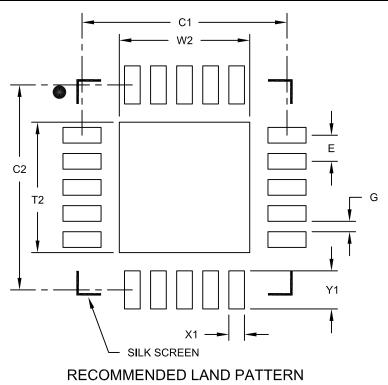

| Package / Case             | 28-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (4x4)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl028-i-m6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. This data sheet contains device-specific information for the PIC32MM0064GPL036 family devices.

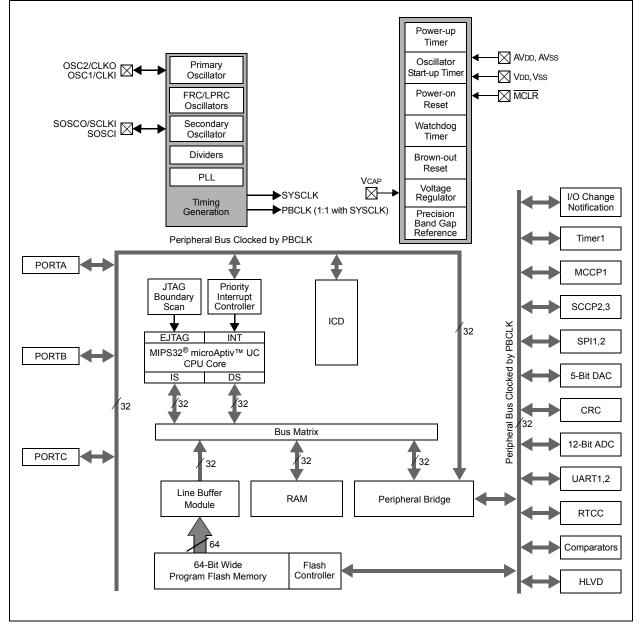

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0064GPL036 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

## FIGURE 1-1: PIC32MM0064GPL036 FAMILY BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6   | Bit<br>29/21/13/5      | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|---------------------|---------------------|------------------------|-------------------------|-------------------|-------------------|----------------------|------------------|

| 24.24        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 31:24        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 00.40        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 23:16        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 45-0         | R/W-0, HC           | R/W-0               | R-0, HS, HC            | R-0, HS, HC             | r-0               | U-0               | U-0                  | U-0              |

| 15:8         | WR <sup>(1,4)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1,2)</sup> | LVDERR <sup>(1,2)</sup> | —                 | _                 | _                    | —                |

| 7.0          | U-0                 | U-0                 | U-0                    | U-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 7:0          |                     | -                   |                        | _                       |                   | NVMOP             | <3:0> <sup>(3)</sup> |                  |

#### REGISTER 5-1: NVMCON: NVM PROGRAMMING CONTROL REGISTER

| Legend:HS = Hardware Settable bit |                                                     | HC = Hardware Clearable bit           |  |  |

|-----------------------------------|-----------------------------------------------------|---------------------------------------|--|--|

| R = Readable bit                  | W = Writable bit U = Unimplemented bit, read as '0' |                                       |  |  |

| -n = Value at POR                 | '1' = Bit is set                                    | '0' = Bit is cleared r = Reserved bit |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 WR: Write Control bit<sup>(1,4)</sup>

- This bit cannot be cleared and can be set only when WREN = 1, and the unlock sequence has been performed. 1 = Initiates a Flash operation

- 0 = Flash operation is complete or inactive

#### bit 14 WREN: Write Enable bit<sup>(1)</sup>

- 1 = Enables writes to the WR bit and disables writes to the NVMOP<3:0> bits

- 0 = Disables writes to the WR bit and enables writes to the NVMOP<3:0> bits

#### bit 13 WRERR: Write Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

- 1 = Program or erase sequence did not complete successfully

- 0 = Program or erase sequence completed normally

#### bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation. 1 = Low voltage is detected (possible data corruption if WRERR is set)

- 0 = Voltage level is acceptable for programming

- bit 11 Reserved: Maintain as '0'

- bit 10-4 Unimplemented: Read as '0'

- **Note 1:** These bits are only reset by a Power-on Reset (POR) and are not affected by other Reset sources.

- 2: These bits are cleared by setting NVMOP<3:0> = 0000 and initiating a Flash operation (i.e., WR).

- 3: NVMOP<3:0> bits are write-protected if the WREN bit is set.

- 4: Writes to the WR bit require an unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|----------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 31.24        | —                 | _                 | —                 | -                 | —                 | _                     | _                    | _                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                     | —                    | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                     | _                    | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                | R/W-0                |

| 7:0          | _                 |                   |                   |                   | _                 | SBOREN <sup>(3)</sup> | RETEN <sup>(2)</sup> | VREGS <sup>(2)</sup> |

## REGISTER 6-4: PWRCON: POWER CONTROL REGISTER<sup>(1)</sup>

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-3 Unimplemented: Read as '0'

- bit 2 SBOREN: BOR During Sleep Control bit<sup>(3)</sup>

- 1 = BOR is turned on

- 0 = BOR is turned off

- bit 1 **RETEN:** Output Level of the Regulator During Sleep Selection bit<sup>(2)</sup>

- 1 = Writing a '1' to this bit will cause the main regulator to be put in a low-power state during Sleep mode 0 = Writing a '0' to this bit will have no effect

- bit 0 VREGS: Voltage Regulator Standby Enable bit<sup>(2)</sup>

- 1 = Voltage regulator will remain active during Sleep mode

- 0 = Voltage regulator will go to Standby mode during Sleep mode

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: Refer to Section 22.4 "On-Chip Voltage Regulator Low-Power Modes" for details.

- 3: This bit is enabled only when the BOREN<1:0> Configuration bits (FPOR<1:0>) are set to '01'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|

| 24.24        | U-0                       | U-0              |

| 31:24        | _                 | _                 |                   |                   | _                 | —                 | —                         | _                |

| 00.10        | U-0                       | U-0              |

| 23:16        | —                 | -                 | _                 |                   | _                 | —                 | —                         | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC               | R-0, HS, HC      |

| 15:8         | _                 | _                 | _                 | —                 | _                 | S                 | 8RIPL<2:0> <sup>(1)</sup> |                  |

| 7.0          | R-0, HS, HC               | R-0, HS, HC      |

| 7:0          |                   |                   |                   | SIRQ<             | 7:0>              |                   |                           |                  |

#### REGISTER 7-3: INTSTAT: INTERRUPT STATUS REGISTER

| Legend: HS = Hardware Settable bit |                  | HC = Hardware Clearable bit |                    |  |

|------------------------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, r    | ead as '0'         |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 31-11 Unimplemented: Read as '0'

bit 10-8 **SRIPL<2:0>:** Requested Priority Level for Single Vector Mode bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

bit 7-0 SIRQ<7:0>: Last Interrupt Request Serviced Status bits 1111111-00000000 = The last interrupt request number serviced by the CPU

Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

#### REGISTER 7-4: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 IPTMR<31:0>: Interrupt Proximity Timer Reload bits

Used by the interrupt proximity timer as a reload value when the interrupt proximity timer is triggered by an interrupt event.

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

## 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | 1:24 ROTRIM<8:1>  |                   |                   |                   |                   |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### **REGISTER 8-4: REFO1TRIM: REFERENCE OSCILLATOR TRIM REGISTER**<sup>(1,2,3)</sup>

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

- bit 22-0 Unimplemented: Read as '0'

- **Note 1:** While the ON bit (REFO1CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- Do not write to this register when the ON bit (REFO1CON<15>) is not equal to the ACTIVE bit (REFO1CON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> (REFO1CON<30:16>) = 0.

## 9.1 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (Clear), SET (Set) and INV (Invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

## 9.2 Parallel I/O (PIO) Ports

All port pins have 14 registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. The LATx register controls the pin level when it is configured as an output. Reads from the PORTx register read the port pins, while writes to the port pins write the latch, LATx. The I/Os state reflected in the PORTx register is synchronized with the system clock and delayed by 3 system clock cycles.

## 9.3 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, the port pins can also be individually configured for either digital or open-drain outputs. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired 5V tolerant pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 9.4 Configuring Analog and Digital Port Pins

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications. The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared. The ANSELx register has a default value of 0xFFFF. Therefore, all pins that share analog functions are analog (not digital) by default. If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is used by an analog peripheral, such as the ADC or comparator module.

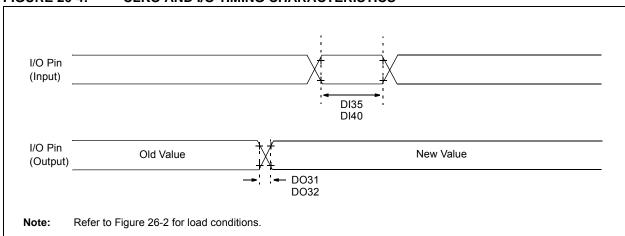

## 9.5 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 9.6 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC32MM devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 9-1.

| <b>TABLE 9-1</b> : | CHANGE NOTIFICATION |

|--------------------|---------------------|

|                    | EVENT OPTIONS       |

| CNSTYLE Bit<br>(CNCONx<11>) | <u> </u>           | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

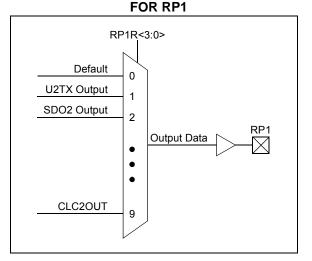

## 9.8.5 OUTPUT MAPPING

The RPORx registers are used to assign the peripheral output to the required remappable pin, RPn. Each RPORx register contains 4-bit fields corresponding to the remappable pins. A special value is defined for each peripheral output. This value should be written to the remappable pin bit field in the RPORx register to connect the peripheral output to the RPn pin. All possible (implemented) values for the peripheral's outputs are listed in Table 9-3.

Example 9-2 and Figure 9-3 illustrate the peripheral's output selection for the remappable pin.

### EXAMPLE 9-2: UART2 TX OUTPUT ASSIGNMENT TO RP13/RB13 PIN

| RPOR4bits.RP13R = 1; | // connect UART2 TX (= 1) |

|----------------------|---------------------------|

|                      | // to RP13 pin            |

## FIGURE 9-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT

### 9.8.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32MM0064GPL036 family devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Configuration bit select lock

### 9.8.6.1 Control Register Lock

Under normal operation, the RPORx and RPINRx registers can be written, but they can also be locked to prevent accidental writes. This feature is controlled by the IOLOCK bit in the RPCON register. If the IOLOCK bit is set, then the contents of the RPORx and RPINRx registers cannot be changed.

To modify the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 23.4** "**System Registers Write Protection**" for details.

| TABLE 9-3: | OUTPUT PIN SELECTION |

|------------|----------------------|

|            |                      |

| Output Function Number | Function             | Output Name              |

|------------------------|----------------------|--------------------------|

| 0                      | None (not connected) | _                        |

| 1                      | U2TX                 | UART2 Transmit           |

| 2                      | U2RTS                | UART2 Request-to-Send    |

| 3                      | SDO2                 | SPI2 Data Output         |

| 4                      | SCK2OUT              | SPI2 Clock Output        |

| 5                      | SS2OUT               | SPI2 Slave Select Output |

| 6                      | OCM2                 | SCCP2 Output Compare     |

| 7                      | OCM3                 | SCCP3 Output Compare     |

| 8                      | CLC1OUT              | CLC1 Output              |

| 9                      | CLC2OUT              | CLC2 Output              |

## TABLE 9-6: PORTC REGISTER MAP

| DS60001324B-pa |

|----------------|

| age            |

| 84             |

| ess                         |                                 | <b>n</b>  | Bits              |       |       |       |                        |       |        |                      |      |      |      |      |      |         |                    |                       |               |

|-----------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|------------------------|-------|--------|----------------------|------|------|------|------|------|---------|--------------------|-----------------------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2    | 17/1               | 16/0                  | All<br>Resets |

| 2800                        | ANSELC                          | 31:16     | _                 | _     | _     | _     | _                      | _     |        | _                    |      | _    | _    | -    | —    | —       |                    | _                     | 0000          |

|                             |                                 | 15:0      | —                 | _     | _     | _     |                        |       | _      | _                    | —    |      |      | _    | —    | _       | ANSC<              | 1:0> <sup>(1,2)</sup> | 0003          |

| 2810                        | TRISC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| -0.0                        |                                 | 15:0      | _                 | —     | —     | _     | _                      | _     | TRISC  | :9:8> <b>(1,2)</b>   | —    | _    | —    | _    |      | TRISC<  | 3:0> <b>(1,2)</b>  |                       | 030F          |

| 2820                        | PORTC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2020                        | TORTO                           | 15:0      | —                 |       |       |       | _                      | _     | RC<9   | :8> <sup>(1,2)</sup> | —    | _    |      | _    |      | RC<3:   | 0> <b>(1,2)</b>    |                       | 0000          |

| 2830                        | LATC                            | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | —    | —    | —    | —    | —       | —                  | —                     | 0000          |

| 2000                        | EATO                            | 15:0      | —                 |       |       |       | _                      | _     | LATC<  | 9:8> <b>(1,2)</b>    | —    | _    |      | _    |      | LATC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2840                        | ODCC                            | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 2040                        | 0000                            | 15:0      | —                 |       |       |       | _                      | _     | ODCC<  | :9:8> <b>(1,2)</b>   | —    | _    |      | _    |      | ODCC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2850                        | CNPUC                           | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 2000                        |                                 | 15:0      | —                 | —     | —     | —     | _                      | _     | CNPUC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPUC   | <3:0>(1,2)         |                       | 0000          |

| 2860                        | CNPDC                           | 31:16     | —                 | —     | —     | _     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | -                  | —                     | 0000          |

| 2000                        | CINFDC                          | 15:0      | —                 | —     | —     | —     | —                      | —     | CNPDC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPDC<  | <3:0> <b>(1,2)</b> |                       | 0000          |

| 2870                        | CNCONC                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2070                        | CINCOINC                        | 15:0      | ON <sup>(1)</sup> | —     | —     | —     | CNSTYLE <sup>(1)</sup> | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2880                        | CNEN0C                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2000                        | CINEINUC                        | 15:0      | _                 | —     | —     | —     | _                      | _     | CNIE0C | <9:8>(1,2)           | —    |      | _    | I    |      | CNIE0C4 | <3:0>(1,2)         |                       | 0000          |

| 2890                        | CNSTATC -                       | 31:16     | _                 | —     | —     | —     | _                      | _     | _      | —                    | —    |      | _    | I    | —    | _       |                    | _                     | 0000          |

| 2090                        | CINGTATE                        | 15:0      | —                 | —     | —     | —     | _                      | _     | CNSTAT | C<9:8>(1,2)          | —    | —    | —    |      |      | CNSTATO | <3:0>(1,2)         |                       | 0000          |

| 28A0                        | CNEN1C                          | 31:16     | _                 | -     | _     | -     |                        | _     | _      | —                    | —    | _    | _    | I    | _    | -       |                    | _                     | 0000          |

| 2040                        | CINENTO                         | 15:0      | _                 | -     | -     | -     | —                      | _     | CNIE1C | <9:8>(1,2)           | _    |      |      |      |      | CNIE1C  | <3:0>(1,2)         |                       | 0000          |

| 28B0                        | CNFC                            | 31:16     | _                 | -     | —     | -     | —                      | _     | —      | —                    | —    |      |      |      | _    | _       | _                  | —                     | 0000          |

| 20BU                        | CINFC                           | 15:0      | _                 | —     | —     | —     | _                      | _     | CNFC<  | :9:8> <b>(1,2)</b>   | _    |      |      |      |      | CNFC<   | 3:0>(1,2)          |                       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **Note 1:** Bits<15,11,9:8,3:0> are not implemented in 20-pin devices.

**2:** Bits<8,3:0> are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------------|------------------|------------------|--|--|

| 04.04        | R/W-0                 | R/W-0                 | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0            | R/W-0            |  |  |

| 31:24        | OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup> | —                 |                   |                   | OPS<3:0> <sup>(3)</sup> |                  |                  |  |  |

| 00.40        | R/W-0                 |                       | R/W-0             | R/W-0             | R/W-0 R/W-0       |                         | R/W-0            | R/W-0            |  |  |

| 23:16        | TRIGEN                | ONESHOT               | ALTSYNC           |                   | SYNC<4:0>         |                         |                  |                  |  |  |

| 45.0         | R/W-0                 | U-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0            | R/W-0            |  |  |

| 15:8         | ON <sup>(1)</sup> —   |                       | SIDL              | CCPSLP            | TMRSYNC           | (                       | CLKSEL<2:0>      | <b>`</b>         |  |  |

| 7.0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0            | R/W-0            |  |  |

| 7:0          | TMRPS                 | S<1:0>                | T32               | CCSEL             | CCSEL MOD<3:0>    |                         |                  |                  |  |  |

#### REGISTER 12-1: CCPxCON1: CAPTURE/COMPARE/PWMx CONTROL 1 REGISTER

#### Legend:

| 9                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31 **OPSSRC:** Output Postscaler Source Select bit<sup>(1)</sup>

- 1 = Output postscaler scales the Special Event Trigger output events

- 0 = Output postscaler scales the timer interrupt events

- bit 30 RTRGEN: Retrigger Enable bit<sup>(2)</sup>

- 1 = Time base can be retriggered when CCPTRIG = 1

- 0 = Time base may not be retriggered when CCPTRIG = 1

- bit 29-28 Unimplemented: Read as '0'

- bit 27-24 **OPS<3:0>:** CCPx Interrupt Output Postscale Select bits<sup>(3)</sup>

- 1111 = Interrupt every 16th time base period match

- 1110 = Interrupt every 15th time base period match

- ...

- 0100 = Interrupt every 5th time base period match

- 0011 = Interrupt every 4th time base period match or 4th input capture event

- 0010 = Interrupt every 3rd time base period match or 3rd input capture event

- 0001 = Interrupt every 2nd time base period match or 2nd input capture event

- 0000 = Interrupt after each time base period match or input capture event

- bit 23 TRIGEN: CCPx Triggered Enable bit

- 1 = Triggered operation of the timer is enabled

- 0 = Triggered operation of the timer is disabled

- bit 22 **ONESHOT:** One-Shot Mode Enable bit

- 1 = One-Shot Triggered mode is enabled; trigger duration is set by OSCNT<2:0>

- 0 = One-Shot Triggered mode is disabled

#### bit 21 ALTSYNC: CCPx Clock Select bit

- 1 = An alternate signal is used as the module synchronization output signal

0 = The module synchronization output signal is the Time Base Reset/rollover event

- **Note 1:** This control bit has no function in Input Capture modes.

- 2: This control bit has no function when TRIGEN = 0.

- **3:** Values greater than '0011' will cause a FIFO buffer overflow in Input Capture mode.

## REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 23    | MCLKSEL: Master Clock Enable bit <sup>(1)</sup>                                                                                                                                                                                                    |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|           | <ul> <li>1 = REFCLKO is used by the Baud Rate Generator</li> <li>0 = PBCLK is used by the Baud Rate Generator (1:1 with SYSCLK)</li> </ul>                                                                                                         |  |  |  |  |  |

| bit 22-18 | Unimplemented: Read as '0'                                                                                                                                                                                                                         |  |  |  |  |  |

| bit 17    | SPIFE: SPIx Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                                                                |  |  |  |  |  |

|           | <ul> <li>1 = Frame synchronization pulse coincides with the first bit clock</li> <li>0 = Frame synchronization pulse precedes the first bit clock</li> </ul>                                                                                       |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(1)</sup>                                                                                                                                                                                                  |  |  |  |  |  |

|           | <ul><li>1 = Enhanced Buffer mode is enabled</li><li>0 = Enhanced Buffer mode is disabled</li></ul>                                                                                                                                                 |  |  |  |  |  |

| bit 15    | ON: SPIx Module On bit                                                                                                                                                                                                                             |  |  |  |  |  |

|           | <ul><li>1 = SPIx module is enabled</li><li>0 = SPIx module is disabled</li></ul>                                                                                                                                                                   |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                         |  |  |  |  |  |

| bit 13    | SIDL: SPIx Stop in Idle Mode bit                                                                                                                                                                                                                   |  |  |  |  |  |

|           | <ul> <li>1 = Discontinues operation when CPU enters Idle mode</li> <li>0 = Continues operation in Idle mode</li> </ul>                                                                                                                             |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx Pin bit <sup>(4)</sup>                                                                                                                                                                                                        |  |  |  |  |  |

|           | <ul> <li>1 = SDOx pin is not used by the module; the pin is controlled by the associated PORTx register</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                                               |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16/8-Bit Communication Select bits                                                                                                                                                                                                 |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                                                                                                                                                                    |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |  |  |  |  |  |

|           | 1124-bit data, 32-bit FIFO, 32-bit channel/64-bit frame1032-bit data, 32-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                     |  |  |  |  |  |

|           | 0 1 16-bit data, 16-bit FIFO, 32-bit channel/64-bit frame                                                                                                                                                                                          |  |  |  |  |  |

|           | 0 0 16-bit data, 16-bit FIFO, 16-bit channel/32-bit frame                                                                                                                                                                                          |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                                                                                                                                                                    |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |  |  |  |  |  |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                                                                           |  |  |  |  |  |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                                                                   |  |  |  |  |  |

| bit 9     | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                                              |  |  |  |  |  |

|           | Master mode (MSTEN = 1):                                                                                                                                                                                                                           |  |  |  |  |  |

|           | <ul> <li>1 = Input data is sampled at the end of data output time</li> <li>0 = Input data is sampled at the middle of data output time</li> </ul>                                                                                                  |  |  |  |  |  |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                                                                            |  |  |  |  |  |

|           | SMP value is ignored when SPIx is used in Slave mode. The module always uses SMP = 0.                                                                                                                                                              |  |  |  |  |  |

| bit 8     | <b>CKE:</b> SPIx Clock Edge Select bit <sup>(2)</sup>                                                                                                                                                                                              |  |  |  |  |  |

|           | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)</li> </ul> |  |  |  |  |  |

| Note 1:   | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                            |  |  |  |  |  |

| 2:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                          |  |  |  |  |  |

| 3:        | When AUDEN = 1, the SPI/I <sup>2</sup> S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.                                                                                                        |  |  |  |  |  |

| 4:        | These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see <b>Section 9.8</b> " <b>Peripheral Pin Select (PPS)</b> " for more information).                                                     |  |  |  |  |  |

### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

## **19.1 Comparator Control Registers**

### TABLE 19-1: COMPARATOR 1 AND 2 REGISTER MAP

| ess                         |                                             | n         |       | Bits  |       |       |       |       |      |          |      |        |      | ú    |      |      |       |       |            |

|-----------------------------|---------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|----------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | (BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 0000                        | OMOTAT                                      | 31:16     | _     | _     | —     | —     | _     | —     | —    | —        | _    | -      | -    | —    | —    | _    | C2EVT | C1EVT | 0000       |

| 0900                        | CMSTAT                                      | 15:0      | _     | _     | SIDL  | _     | -     | _     | —    | CVREFSEL | _    | _      | _    | —    | _    | _    | C2OUT | C10UT | 0000       |

| 0910                        | CM1CON                                      | 31:16     |       | _     | _     | _     | _     | _     | _    | _        | _    | _      | _    | _    | _    | _    | _     | _     | 0000       |

| 0910                        | CINICON                                     | 15:0      | ON    | COE   | CPOL  | _     | _     | _     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | 0000       |

| 0930                        | CM2CON                                      | 31:16     | _     | —     | _     | _     |       |       | —    | _        | _    | —      | —    | _    |      |      | _     |       | 0000       |

| 0930                        | CIVIZCON                                    | 15:0      | ON    | COE   | CPOL  | _     | _     | -     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

NOTES:

## 22.4 On-Chip Voltage Regulator Low-Power Modes

The main on-chip regulator always consumes an incremental amount of current over IDD/IPD, including when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator can be made to enter Standby mode and/ or Retention mode. Standby mode is controlled by the VREGS bit (PWRCON<0>), and Retention mode is controlled by the RETEN (PWRCON<1>) and RETVR (FPOR<2>) bits. The available Regulator Low-Power modes are listed in Table 22-2. For more information about the wake-up time and the current consumption for different modes, refer to the electrical specifications listed in Table 26-6 and Table 26-22.

| <b>TABLE 22-2:</b> | VOLTAGE REGULATOR LOW-POWER MODES |

|--------------------|-----------------------------------|

|                    |                                   |

| Mode                  | VREGS Bit<br>(PWRCON<0>) | RETEN Bit<br>(PWRCON<1>) | RETVR Bit<br>(FPOR<2>) | Wake-up Time<br>(Table 26-22) | Current<br>(Table 26-6) |  |

|-----------------------|--------------------------|--------------------------|------------------------|-------------------------------|-------------------------|--|

| Normal                | 1                        | 0                        | 1                      | Fastest                       | Highest                 |  |

| Standby Only          | 0                        | 0                        | 1                      | Medium                        | Medium                  |  |

| Retention Only        | 1                        | 1                        | 0                      | Medium                        | Medium                  |  |

| Standby and Retention | 0                        | 1                        | 0                      | Slowest                       | Lowest                  |  |

## 22.4.1 REGULATOR STANDBY MODE

Whenever the device goes into Sleep mode, the regulator can be made to enter Standby mode. This feature is controlled by the VREGS bit (PWRCON<0>). Clearing the VREGS bit enables Standby mode. If Standby mode is used, the voltage regulator needs some time to switch to normal operation mode and generate output. During this time, the code execution is disabled. The delay is applied every time the device resumes operation after Standby mode.

## 22.4.2 REGULATOR RETENTION MODE

When in Sleep mode, the device can use a separate low-power, low-voltage/retention regulator to power critical circuits. This regulator, which operates at 1V nominal, maintains power to data RAM, WDT, Timer1 and the RTCC, while all other core digital logic is powered down. The low-voltage/retention regulator is available only when Sleep mode is invoked. It is controlled by the RETVR Configuration bit (FPOR<2>) and in firmware by the RETEN bit (PWRCON<1>). RETVR must be programmed to zero (= 0) and the RETEN bit must be set (= 1) for the retention regulator to be enabled.

## 22.5 Low-Power Brown-out Reset

The PIC32MM0064GPL036 family devices have a second low-power Brown-out Reset circuit with a reduced precision of the trip point. This low-power BOR circuit can be activated when the main BOR is disabled. The circuit is enabled by programming the LPBOREN Configuration bit (FPOR<3>) to '1'.

# REGISTER 23-5: FOSCSEL/AFOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        |                   | _                 | _                 | _                 | —                 | _                 |                  | _                |

| 45.0         | R/P               | R/P               | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | FCKS              | M<1:0>            | _                 | SOSCSEL           | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |

| 7.0          | R/P               | R/P               | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 7:0          | IESO              | SOSCEN            |                   | PLLSRC            | _                 |                   | FNOSC<2:0>       | 1                |

| Legend:         r = Reserved bit         P = Programmable bit |                  |                                    |                    |

|---------------------------------------------------------------|------------------|------------------------------------|--------------------|

| R = Readable bit                                              | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR                                             | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31-16 | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15-14 | FCKSM<1:0>: Clock Switching and Fail-Safe Clock Monitor Enable bits                                                                                                                                                                                                                                                                |

|           | <ul> <li>11 = Clock switching is enabled; Fail-Safe Clock Monitor is enabled</li> <li>10 = Clock switching is disabled; Fail-Safe Clock Monitor is enabled</li> <li>01 = Clock switching is enabled; Fail-Safe Clock Monitor is disabled</li> <li>00 = Clock switching is disabled; Fail-Safe Clock Monitor is disabled</li> </ul> |

| bit 13    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 12    | SOSCSEL: Secondary Oscillator (SOSC) External Clock Enable bit                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Crystal is used (RA4 and RB4 pins are controlled by SOSC)</li><li>0 = External clock is connected to the SOSCO pin (RA4 and RB4 pins are controlled by I/O PORTx registers)</li></ul>                                                                                                                                  |

| bit 11    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 10    | OSCIOFNC: System Clock on CLKO Pin Enable bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = OSC2/CLKO pin operates as normal I/O</li> <li>0 = System clock is connected to the OSC2/CLKO pin</li> </ul>                                                                                                                                                                                                           |

| bit 9-8   | POSCMOD<1:0>: Primary Oscillator (POSC) Mode Selection bits                                                                                                                                                                                                                                                                        |

|           | <ul> <li>11 = Primary Oscillator is disabled</li> <li>10 = HS Oscillator mode is selected</li> <li>01 = XT Oscillator mode is selected</li> <li>00 = External Clock (EC) mode is selected</li> </ul>                                                                                                                               |

| bit 7     | IESO: Two-Speed Start-up Enable bit                                                                                                                                                                                                                                                                                                |

|           | <ul><li>1 = Two-Speed Start-up is enabled</li><li>0 = Two-Speed Start-up is disabled</li></ul>                                                                                                                                                                                                                                     |

| bit 6     | SOSCEN: Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Secondary Oscillator is enabled</li><li>0 = Secondary Oscillator is disabled</li></ul>                                                                                                                                                                                                                                 |

| bit 5     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 4     | PLLSRC: System PLL Input Clock Selection bit                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = FRC oscillator is selected as the PLL reference input on a device Reset</li> <li>0 = Primary Oscillator (POSC) is selected as the PLL reference input on a device Reset</li> </ul>                                                                                                                                    |

| bit 3     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| <b>Operating Conditions:</b> $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |                        |      |       |      |                 |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------|------|-------|------|-----------------|--|--|--|

| Parameter No.                                                                             | Typical <sup>(1)</sup> | Max  | Units | Vdd  | Conditions      |  |  |  |

| DC40                                                                                      | 0.26                   | 0.46 | mA    | 2.0V | Fsys = 1 MHz    |  |  |  |

| DC40                                                                                      | 0.26                   | 0.46 | mA    | 3.3V |                 |  |  |  |

| 5044                                                                                      | 0.85                   | 1.5  | mA    | 2.0V |                 |  |  |  |

| DC41                                                                                      | 0.85                   | 1.5  | mA    | 3.3V | Fsys = 8 MHz    |  |  |  |

| DC 42                                                                                     | 2.3                    | 3.7  | mA    | 2.0V | Fsys = 25 MHz   |  |  |  |

| DC42                                                                                      | 2.3                    | 3.7  | mA    | 3.3V |                 |  |  |  |

| DC44                                                                                      | 0.18                   | 0.34 | mA    | 2.0V | — Fsys = 32 kHz |  |  |  |

|                                                                                           | 0.18                   | 0.34 | mA    | 3.3V |                 |  |  |  |

## TABLE 26-5: IDLE CURRENT (IIDLE)<sup>(2)</sup>