#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 22                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

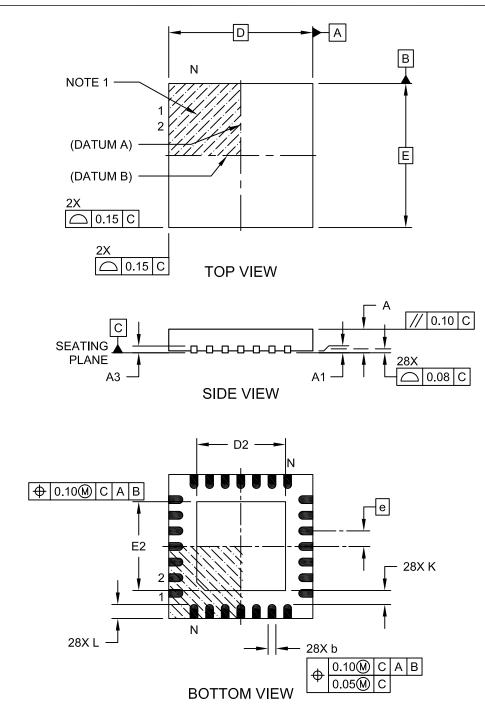

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl028-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

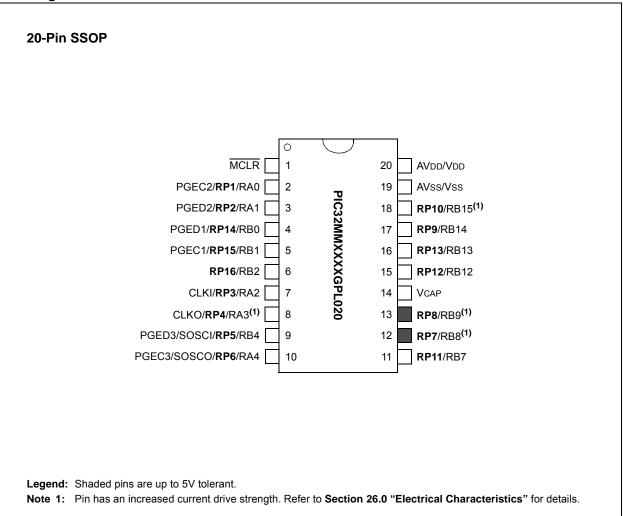

#### TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 20-PIN SSOP DEVICES

| Pin | Function                                                  | Pin | Function                                                                                                 |

|-----|-----------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------|

| 1   | MCLR                                                      | 11  | RP11/RB7                                                                                                 |

| 2   | PGEC2/VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0               | 12  | TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                     |

| 3   | PGED2/VREF-/AN1/RP2/OCM1F/RA1                             | 13  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <del>U1RTS</del> /U1BCLK/SDO1/C2OUT/OCM1B/<br>INT2/RB9 <sup>(1)</sup> |

| 4   | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                   | 14  | VCAP                                                                                                     |

| 5   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                   | 15  | TDO/AN7/LVDIN/ <b>RP12</b> /RB12                                                                         |

| 6   | AN4/ <b>RP16</b> /RB2                                     | 16  | TDI/AN8/ <b>RP13</b> /RB13                                                                               |

| 7   | OSC1/CLKI/AN5/C1INB/ <b>RP3</b> /OCM1C/RA2                | 17  | CDAC1/AN9/RP9/RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                                             |

| 8   | OSC2/CLKO/AN6/C1INA/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 18  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                                               |

| 9   | PGED3/SOSCI/ <b>RP5</b> /RB4                              | 19  | AVss/Vss                                                                                                 |

| 10  | PGEC3/SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                | 20  | AVdd/Vdd                                                                                                 |

Note 1: Pin has an increased current drive strength.

NOTES:

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC microprocessor core resources are available at: www.imgtec.com. The information in this data sheet supersedes the information in the FRM.

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC microprocessor core is the heart of the PIC32MM0064GPL036 family devices. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of the instruction execution to the proper destinations.

# 3.1 Features

The PIC32MM0064GPL036 family processor core key features include:

- 5-Stage Pipeline

- · 32-Bit Address and Data Paths

- MIPS32 Enhanced Architecture:

- Multiply-add and multiply-subtract instructions

- Targeted multiply instruction

- Zero and one detect instructions

- WAIT instruction

- Conditional move instructions

- Vectored interrupts

- Atomic interrupt enable/disable

- One GPR shadow set to minimize latency of interrupts

- Bit field manipulation instructions

- microMIPS<sup>™</sup> Instruction Set:

- microMIPS allows improving the code size density over MIPS32, while maintaining MIPS32 performance.

- microMIPS supports all MIPS32 instructions (except for branch-likely instructions) with new optimized 32-bit encoding. Frequent MIPS32 instructions are available as 16-bit instructions.

- Added seventeen new and thirty-five MIPS32<sup>®</sup> corresponding commonly used instructions in 16-bit opcode format.

- Stack Pointer implicit in instruction.

- MIPS32 assembly and ABI compatible.

- Memory Management Unit with Simple Fixed Mapping Translation (FMT) Mechanism

- Multiply/Divide Unit (MDU):

- Configurable using high-performance multiplier array.

- Maximum issue rate of one 32x16 multiply per clock.

- Maximum issue rate of one 32x32 multiply every other clock.

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension dependent).

- · Power Control:

- No minimum frequency: 0 MHz.

- Power-Down mode (triggered by WAIT instruction).

- · EJTAG Debug/Profiling:

- CPU control with start, stop and single stepping.

- Software breakpoints via the SDBBP instruction.

- Optional simple hardware breakpoints on virtual addresses, 4 instruction and 2 data breakpoints.

- PC and/or load/store address sampling for profiling.

- Performance counters.

- Supports Fast Debug Channel (FDC).

A block diagram of the PIC32MM0064GPL036 family processor core is shown in Figure 3-1.

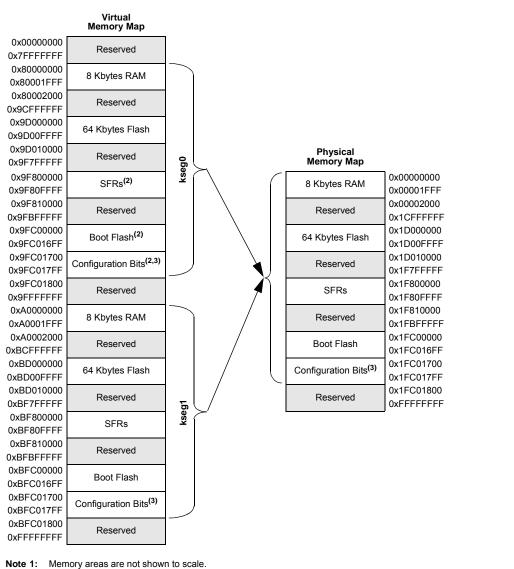

# FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 64 Kbytes OF PROGRAM MEMORY<sup>(1)</sup>

2: This region should be accessed from kseg1 space only.

3: Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768. Refer to Section 4.1 "Alternate Configuration Bits Space" for more information.

# 5.2 Flash Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |          |                        |       |        |       |       |          | Bi      | ts        |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|----------|------------------------|-------|--------|-------|-------|----------|---------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15    | 30/14                  | 29/13 | 28/12  | 27/11 | 26/10 | 25/9     | 24/8    | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| 2380                        | NVMCON <sup>(1)</sup>  | 31:16     | _        |                        |       |        |       |       |          |         |           |      |      |      |      |      |        |      | 0000       |

| 2300                        | INVINCOIN.             | 15:0      | WR       | WREN                   | WRERR | LVDERR | _     |       | _        | _       | —         |      | —    |      |      | NVMO | P<3:0> |      | 0000       |

| 2390                        | NVMKEY                 | 31:16     |          |                        |       |        |       |       |          | NVMKE   | /~31.0>   |      |      |      |      |      |        |      | 0000       |

| 2390                        |                        | 15:0      |          |                        |       |        |       |       |          |         | 1~31.02   |      |      |      |      |      |        |      | 0000       |

| 23A0                        | NVMADDR <sup>(1)</sup> | 31:16     |          |                        |       |        |       |       |          | NVMADD  | P<31.0>   |      |      |      |      |      |        |      | 0000       |

| 2370                        | NUMADOR                | 15:0      |          |                        |       |        |       |       |          | NVINADD | 1(\$01.02 |      |      |      |      |      |        |      | 0000       |

| 23B0                        | NVMDATA0               | 31:16     |          |                        |       |        |       |       |          | NVMDAT  | A0<31·0>  |      |      |      |      |      |        |      | 0000       |

| 2020                        |                        | 15:0      |          |                        |       |        |       |       |          |         | 10 10 1.0 |      |      |      |      |      |        |      | 0000       |

| 23C0                        | NVMDATA1               | 31:16     |          |                        |       |        |       |       |          | NVMDAT  | A1<31·0>  |      |      |      |      |      |        |      | 0000       |

| 2000                        |                        | 15:0      |          |                        |       |        |       |       |          |         | 11.01.0   |      |      |      |      |      |        |      | 0000       |

| 23D0                        | NVMSRCADDR             | 31:16     |          |                        |       |        |       |       | N        | VMSRCA  | DDR<31:0  | >    |      |      |      |      |        |      | 0000       |

| 2020                        |                        | 15:0      |          |                        |       |        |       |       |          |         |           |      |      |      |      |      |        |      | 0000       |

| 23E0                        | NVMPWP <sup>(1)</sup>  | 31:16     | PWPULOCK | PWPULOCK PWP<23:16> 80 |       |        |       |       |          | 8000    |           |      |      |      |      |      |        |      |            |

| -0-0                        |                        | 15:0      |          |                        |       |        |       |       |          | PWP<    | 15:0>     |      |      |      |      |      |        |      | 0000       |

| 23F0                        | NVMBWP <sup>(1)</sup>  | 31:16     | —        | —                      | —     | —      | _     | _     |          | _       | _         | _    | —    | _    | _    | _    | _      | —    | 0000       |

| 2010                        |                        | 15:0      | BWPULOCK | _                      | _     | —      | —     |       | BWP<2:0> |         | _         | _    | —    | _    | _    | _    | _      | —    | 8700       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|----------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 31.24        | —                 | _                 | —                 | -                 | —                 | _                     | _                    | _                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                     | —                    | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                     | _                    | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                | R/W-0                |

| 7:0          | _                 |                   |                   |                   | _                 | SBOREN <sup>(3)</sup> | RETEN <sup>(2)</sup> | VREGS <sup>(2)</sup> |

# REGISTER 6-4: PWRCON: POWER CONTROL REGISTER<sup>(1)</sup>

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-3 Unimplemented: Read as '0'

- bit 2 SBOREN: BOR During Sleep Control bit<sup>(3)</sup>

- 1 = BOR is turned on

- 0 = BOR is turned off

- bit 1 **RETEN:** Output Level of the Regulator During Sleep Selection bit<sup>(2)</sup>

- 1 = Writing a '1' to this bit will cause the main regulator to be put in a low-power state during Sleep mode 0 = Writing a '0' to this bit will have no effect

- bit 0 VREGS: Voltage Regulator Standby Enable bit<sup>(2)</sup>

- 1 = Voltage regulator will remain active during Sleep mode

- 0 = Voltage regulator will go to Standby mode during Sleep mode

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: Refer to Section 22.4 "On-Chip Voltage Regulator Low-Power Modes" for details.

- 3: This bit is enabled only when the BOREN<1:0> Configuration bits (FPOR<1:0>) are set to '01'.

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| CpU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | _                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          |                    |                                                                            |                |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

| TABLE 7-2: | INTERRUPTS | (CONTINUED) |

|------------|------------|-------------|

|------------|------------|-------------|

| Intermed Course                      |                                     | Vector | I        | nterrupt Rela | ted Bits Locatio | on           | Persistent |

|--------------------------------------|-------------------------------------|--------|----------|---------------|------------------|--------------|------------|

| Interrupt Source                     | MPLAB <sup>®</sup> XC32 Vector Name | Number | Flag     | Enable        | Priority         | Subpriority  | Interrupt  |

| UART1 Reception                      | _UART1_RX_VECTOR                    | 23     | IFS0<23> | IEC0<23>      | IPC5<28:26>      | IPC5<25:24>  | Yes        |

| UART1 Transmission                   | _UART1_TX_VECTOR                    | 24     | IFS0<24> | IEC0<24>      | IPC6<4:2>        | IPC6<1:0>    | Yes        |

| UART1 Error                          | _UART1_ERR_VECTOR                   | 25     | IFS0<25> | IEC0<25>      | IPC6<12:10>      | IPC6<9:8>    | Yes        |

| CCP1 Input Capture or Output Compare | _CCP1_VECTOR                        | 29     | IFS0<29> | IEC0<29>      | IPC7<12:10>      | IPC7<9:8>    | No         |

| CCP1 Timer                           | _CCT1_VECTOR                        | 30     | IFS0<30> | IEC0<30>      | IPC7<20:18>      | IPC7<17:16>  | No         |

| CCP2 Input Capture or Output Compare | _CCP2_VECTOR                        | 31     | IFS0<31> | IEC0<31>      | IPC7<28:26>      | IPC7<25:24>  | No         |

| CCP2 Timer                           | _CCT2_VECTOR                        | 32     | IFS1<0>  | IEC1<0>       | IPC8<4:2>        | IPC8<1:0>    | No         |

| CCP3 Input Capture or Output Compare | _CCP3_VECTOR                        | 33     | IFS1<1>  | IEC1<1>       | IPC8<12:10>      | IPC8<9:8>    | No         |

| CCP3 Timer                           | _CCT3_VECTOR                        | 34     | IFS1<2>  | IEC1<2>       | IPC8<20:18>      | IPC8<17:16>  | No         |

| RESERVED                             | —                                   | 35     | —        | —             | —                | —            | —          |

| RESERVED                             | —                                   | 36     | —        | -             | —                | —            | —          |

| SPI2 Error                           | _SPI2_ERR_VECTOR                    | 37     | IFS1<5>  | IEC1<5>       | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| SPI2 Transmission                    | _SPI2_TX_VECTOR                     | 38     | IFS1<6>  | IEC1<6>       | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| SPI2 Reception                       | _SPI2_RX_VECTOR                     | 39     | IFS1<7>  | IEC1<7>       | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| UART2 Reception                      | _UART2_RX_VECTOR                    | 40     | IFS1<8>  | IEC1<8>       | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| UART2 Transmission                   | _UART2_TX_VECTOR                    | 41     | IFS1<9>  | IEC1<9>       | IPC10<12:10>     | IPC10<9:8>   | Yes        |

| UART2 Error                          | _UART2_ERR_VECTOR                   | 42     | IFS1<10> | IEC1<10>      | IPC10<20:18>     | IPC10<17:16> | Yes        |

| NVM Program or Erase Complete        | _NVM_VECTOR                         | 46     | IFS1<14> | IEC1<14>      | IPC11<20:18>     | IPC11<17:16> | Yes        |

| Core Performance Counter             | _PERFORMANCE_COUNTER_VECTOR         | 47     | IFS1<15> | IEC1<15>      | IPC11<28:26>     | IPC11<25:24> | No         |

#### REGISTER 12-1: CCPxCON1: CAPTURE/COMPARE/PWMx CONTROL 1 REGISTER (CONTINUED)

- bit 7-6 **TMRPS<1:0>:** CCPx Time Base Prescale Select bits

- 11 = 1:64 prescaler

- 10 = 1:16 prescaler

- 01 = 1:4 prescaler

- 00 = 1:1 prescaler

- bit 5 **T32:** 32-Bit Time Base Select bit

- 1 = 32-bit time base for timer, single edge output compare or input capture function

- 0 = 16-bit time base for timer, single edge output compare or input capture function

- bit 4 CCSEL: Capture/Compare Mode Select bit

- 1 = Input Capture mode

- 0 = Output Compare/PWM or Timer mode (exact function is selected by the MOD<3:0> bits)

- bit 3-0 MOD<3:0>: CCPx Mode Select bits

- CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

- CCSEL = 0 (Output Compare modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Variable Frequency Pulse mode

- 0110 = Center-Aligned Pulse Compare mode, buffered

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode: Toggles output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode: Drives output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode: Drives output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode: Output functions are disabled

- **Note 1:** This control bit has no function in Input Capture modes.

- 2: This control bit has no function when TRIGEN = 0.

- 3: Values greater than '0011' will cause a FIFO buffer overflow in Input Capture mode.

# REGISTER 13-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when the CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

# 16.0 12-BIT ANALOG-TO-DIGITAL CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 16.1 Introduction

The 12-bit ADC Converter with Threshold Detect includes the following features:

- Successive Approximation Register (SAR)

Conversion

- · User-Selectable Resolution of 10 or 12 Bits

- Conversion Speeds of up to 200 ksps for 12-bit mode and 300 ksps for 10-bit mode

- Up to 17 Analog Inputs (internal and external)

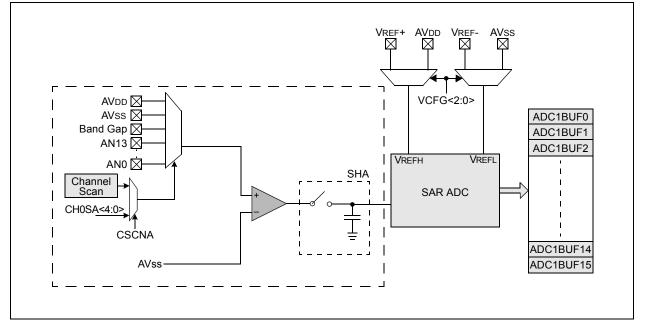

#### FIGURE 16-1: ADC BLOCK DIAGRAM

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold Amplifier (SHA)

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length Configurable Conversion Result

Buffer

- · Eight Options for Result Alignment and Encoding

- Configurable Interrupt Generation

- · Operation during CPU Sleep and Idle modes

Figure 16-1 illustrates a block diagram of the 12-bit ADC. The 12-bit ADC has 14 external analog inputs, AN0 through AN13, and 3 internal analog inputs connected to VDD, VSs and band gap. In addition, there are two analog input pins for external voltage reference connections.

The analog inputs are connected through a multiplexer to the SHA. Unipolar differential conversions are possible on all inputs (see Figure 16-1).

The Automatic Input Scan mode sequentially converts multiple analog inputs. A special control register specifies which inputs will be included in the scanning sequence. The 12-bit ADC is connected to a 16-word result buffer. The 12-bit result is converted to one of eight output formats in either 32-bit or 16-bit word widths.

# REGISTER 16-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 7-4 SSRC<3:0>: Conversion Trigger Source Select bits 1111-1101 = Reserved 1100 = CLC2 module event ends sampling and starts conversion 1011 = CLC1 module event ends sampling and starts conversion 1010 = SCCP3 module event ends sampling and starts conversion 1001 = SCCP2 module event ends sampling and starts conversion 1000 = MCCP1 module event ends sampling and starts conversion 0111 = Internal counter ends sampling and starts conversion (auto-convert) 0110 = Timer1 period match ends sampling and starts conversion (can trigger during Sleep mode) 0101 = Timer1 period match ends sampling and starts conversion (will not trigger during Sleep mode) 0100-0010 = Reserved 0001 = Active transition on INTO pin ends sampling and starts conversion 0000 = Clearing the SAMP bit ends sampling and starts conversion bit 3 MODE12: 12-Bit Operation Mode bit 1 = 12-bit ADC operation 0 = 10-bit ADC operation bit 2 ASAM: ADC Sample Auto-Start bit 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set 0 = Sampling begins when SAMP bit is set bit 1 SAMP: ADC Sample Enable bit<sup>(1)</sup> 1 = The ADC Sample-and-Hold Amplifier (SHA) is sampling 0 = The ADC Sample-and-Hold Amplifier is holding bit 0 DONE: ADC Conversion Status bit<sup>(2)</sup> 1 = Analog-to-Digital conversion is done

- analog-to-Digital conversion is done

analog-to-Digital conversion is not done or has not started

- Clearing this bit will not affect any operation in progress.

- Note 1: The SAMP bit is cleared and cannot be written if the ADC is disabled (ON bit = 0).

- 2: The DONE bit is not persistent in Automatic modes; it is cleared by hardware at the beginning of the next sample.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0                   | U-0              | U-0              |  |  |  |

| 31:24        | _                 |                   | CSS<30:28>        |                   | _                 | _                     | _                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                     | _                | —                |  |  |  |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | —                 |                   |                   | CSS<13            | 3:8> <sup>(1,2)</sup> |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | CSS<7:0>          |                   |                   |                   |                       |                  |                  |  |  |  |

### REGISTER 16-6: AD1CSS: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logona.           |                     |                      |                    |  |

|-------------------|---------------------|----------------------|--------------------|--|

| R = Readable bit  | it W = Writable bit |                      | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31 Unimplemented: Read as '0'

bit 30-28 CSS<30:28>: ADC Input Pin Scan Selection bits

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- bit 27-14 Unimplemented: Read as '0'

- bit 13-0 CSS<13:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- Note 1: The CSS<13:11> bits are not implemented in 20-pin devices.

- **2:** The CSS<13:12> bits are not implemented in 28-pin devices.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | G4D4T             | G4D4N             | G4D3T             | G4D3N             | G4D2T             | G4D2N             | G4D1T            | G4D1N            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | G3D4T             | G3D4N             | G3D3T             | G3D3N             | G3D2T             | G3D2N             | G3D1T            | G3D1N            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | G2D4T             | G2D4N             | G2D3T             | G2D3N             | G2D2T             | G2D2N             | G2D1T            | G2D1N            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | G1D4T             | G1D4N             | G1D3T             | G1D3N             | G1D2T             | G1D2N             | G1D1T            | G1D1N            |

# REGISTER 18-3: CLCxGLS: CLCx GATE LOGIC INPUT SELECT REGISTER

# Legend:

| Ecgenia.          |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31 | <b>G4D4T:</b> Gate 4 Data Source 4 True Enable bit<br>1 = The Data Source 4 signal is enabled for Gate 4<br>0 = The Data Source 4 signal is disabled for Gate 4                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | <b>G4D4N:</b> Gate 4 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 4<br>0 = The Data Source 4 inverted signal is disabled for Gate 4 |

| bit 29 | <b>G4D3T:</b> Gate 4 Data Source 3 True Enable bit<br>1 = The Data Source 3 signal is enabled for Gate 4<br>0 = The Data Source 3 signal is disabled for Gate 4                      |

| bit 28 | <b>G4D3N:</b> Gate 4 Data Source 3 Negated Enable bit<br>1 = The Data Source 3 inverted signal is enabled for Gate 4<br>0 = The Data Source 3 inverted signal is disabled for Gate 4 |

| bit 27 | <b>G4D2T:</b> Gate 4 Data Source 2 True Enable bit<br>1 = The Data Source 2 signal is enabled for Gate 4<br>0 = The Data Source 2 signal is disabled for Gate 4                      |

| bit 26 | <b>G4D2N:</b> Gate 4 Data Source 2 Negated Enable bit<br>1 = The Data Source 2 inverted signal is enabled for Gate 4<br>0 = The Data Source 2 inverted signal is disabled for Gate 4 |

| bit 25 | <b>G4D1T:</b> Gate 4 Data Source 1 True Enable bit<br>1 = The Data Source 1 signal is enabled for Gate 4<br>0 = The Data Source 1 signal is disabled for Gate 4                      |

| bit 24 | <b>G4D1N:</b> Gate 4 Data Source 1 Negated Enable bit<br>1 = The Data Source 1 inverted signal is enabled for Gate 4<br>0 = The Data Source 1 inverted signal is disabled for Gate 4 |

| bit 23 | <b>G3D4T:</b> Gate 3 Data Source 4 True Enable bit<br>1 = The Data Source 4 signal is enabled for Gate 3<br>0 = The Data Source 4 signal is disabled for Gate 3                      |

| bit 22 | <b>G3D4N:</b> Gate 3 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 3<br>0 = The Data Source 4 inverted signal is disabled for Gate 3 |

| bit 21 | <b>G3D3T:</b> Gate 3 Data Source 3 True Enable bit<br>1 = The Data Source 3 signal is enabled for Gate 3<br>0 = The Data Source 3 signal is disabled for Gate 3                      |

# 24.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 24.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 25.0 INSTRUCTION SET

The PIC32MM0064GPL036 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0064GPL036 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for         | - |  |  |  |  |  |

|-------|----------------------------------------------|---|--|--|--|--|--|

|       | Programmers Volume II-B: The                 | 1 |  |  |  |  |  |

|       | microMIPS32 <sup>™</sup> Instruction Set" at |   |  |  |  |  |  |

|       | www.imgtec.com for more information.         |   |  |  |  |  |  |

# 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MM0064GPL036 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MM0064GPL036 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(†)</sup>

+

| Ambient temperature under bias<br>Storage temperature                                                            |                               |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|

| Voltage on VDD with respect to Vss                                                                               | -0.3V to +4.0V                |  |  |  |  |  |

| Voltage on any general purpose digital or analog pin (not 5.5V tolerant) with respect to Vss0.3V to (VDD + 0.3V) |                               |  |  |  |  |  |

| Voltage on any general purpose digital or analog pin (5.5V tolerant) with respect to Vss:                        |                               |  |  |  |  |  |

| When VDD = 0V:                                                                                                   | -0.3V to +4.0V                |  |  |  |  |  |

| When VDD $\geq$ 2.0V:                                                                                            | -0.3V to +6.0V                |  |  |  |  |  |

| Voltage on AVDD with respect to Vss                                                                              | ser of: 4.0V or (VDD + 0.3V)) |  |  |  |  |  |

| Voltage on AVss with respect to Vss                                                                              | -0.3V to +0.3V                |  |  |  |  |  |

| Maximum current out of Vss pin                                                                                   | 100 mA                        |  |  |  |  |  |

| Maximum current into VDD pin <sup>(1)</sup>                                                                      |                               |  |  |  |  |  |

| Maximum output current sunk by I/O pin                                                                           | 11 mA                         |  |  |  |  |  |

| Maximum output current sourced by I/O pin                                                                        |                               |  |  |  |  |  |

| Maximum output current sunk by I/O pin with increased current drive strength (RA3, RB8,                          | RB9 and RB15)17 mA            |  |  |  |  |  |

| Maximum output current sourced by I/O pin with increased current drive strength (RA3, RB8, F                     | RB9 and RB15)24 mA            |  |  |  |  |  |

| Maximum current sunk by all ports                                                                                |                               |  |  |  |  |  |

| Maximum current sourced by all ports <sup>(1)</sup>                                                              |                               |  |  |  |  |  |

|                                                                                                                  |                               |  |  |  |  |  |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 26-1).

**NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 26.2 AC Characteristics and Timing Parameters

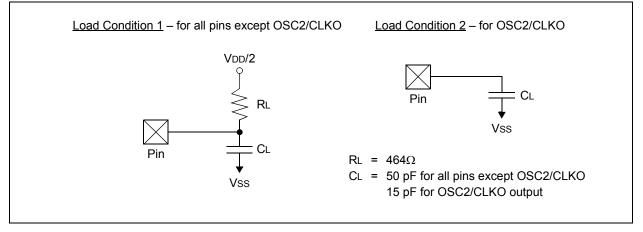

#### FIGURE 26-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-16: CAPACITIVE LOADING CONDITIONS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Max | Units | Conditions                                                              |

|--------------|--------|-----------------------|-----|-----|-------|-------------------------------------------------------------------------|

| DO50         | Cosco  | OSC2/CLKO Pin         | _   | 15  | •     | In XT and HS modes when<br>external clock is used to drive<br>OSC1/CLKI |

| DO56         | Сю     | All I/O Pins and OSC2 | _   | 50  | рF    | EC mode                                                                 |

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2