Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 40-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 40-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl036-e-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,   |

|-------|-----------------------------------------|

|       | browse the documentation section of the |

|       | Microchip web site (www.microchip.com). |

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 60. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS60001336)

- Section 62. "Dual Watchdog Timer" (DS60001365)

# PIC32MM0064GPL036 FAMILY

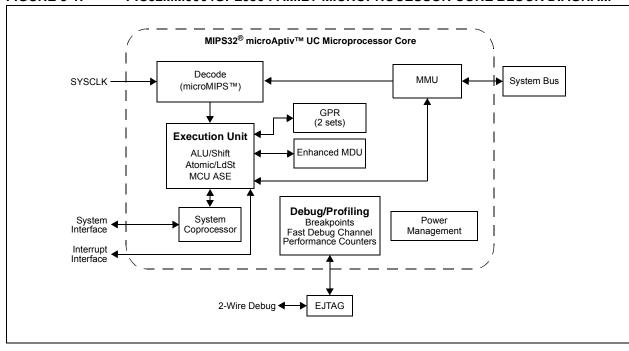

#### FIGURE 3-1: PIC32MM0064GPL036 FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

The MIPS<sup>®</sup> architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS architecture also defines a Multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. These configuration options and other system information is available by accessing the CP0 registers listed in Table 3-2.

## 3.3 Power Management

The processor core offers a number of power management features, including low-power design, active power management and Power-Down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

The mechanism for invoking Power-Down mode is implemented through execution of the WAIT instruction. The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MM family makes extensive use of local gated clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The microAptiv UC core has an Enhanced JTAG (EJTAG) interface for use in the software debug. In addition to the standard mode of operation, the microAptiv UC core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the microAptiv UC core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

# 3.5 MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the microAptiv UC core, which is included on PIC32MM0064GPL036 family devices.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0064GPL036 family devices contain an internal Flash program memory for executing user code. The Program and Boot Flash Memory can be write-protected. The erase page size is 512 32-bit words. The program row size is 64 32-bit words. The memory can be programmed by rows or by two 32-bit words.

The devices implement an Error Correcting Code (ECC). The memory control block contains a logic to write and read ECC bits to and from the Flash memory. The Flash is programmed at the same time as the corresponding ECC bits. The ECC provides improved resistance to Flash errors. The ECC single-bit error will be transparently corrected. The ECC double-bit error results in a bus error exception.

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is described in **Section 5. "Flash Programming"** in the *"PIC32 Family Reference Manual"*. EJTAG programming is performed using the JTAG port of the device. ICSP programming requires fewer connections than for EJTAG programming. The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip web site.

### 5.1 Flash Controller Registers Write Protection

The NVMPWP and NVMBWP registers, and the WR bit in the NVMCON register are protected (locked) from an accidental write. A special unlock sequence is required to modify the content of these registers or bits.

To unlock, the following steps should be done:

- 1. Disable interrupts prior to the unlock sequence.

- 2. Execute the system unlock sequence by writing the key values of 0xAA996655 and 0x556699AA to the NVMKEY register in two back-to-back Assembly or 'C' instructions.

- 3. Write the new value to the required bits.

- 4. Re-enable interrupts.

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|----------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 31.24        | —                 | _                 | —                 | -                 | —                 | _                     | _                    | _                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                     | —                    | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                  | U-0                  |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                     | _                    | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                | R/W-0                |

| 7:0          | _                 |                   |                   |                   | _                 | SBOREN <sup>(3)</sup> | RETEN <sup>(2)</sup> | VREGS <sup>(2)</sup> |

# REGISTER 6-4: PWRCON: POWER CONTROL REGISTER<sup>(1)</sup>

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-3 Unimplemented: Read as '0'

- bit 2 SBOREN: BOR During Sleep Control bit<sup>(3)</sup>

- 1 = BOR is turned on

- 0 = BOR is turned off

- bit 1 **RETEN:** Output Level of the Regulator During Sleep Selection bit<sup>(2)</sup>

- 1 = Writing a '1' to this bit will cause the main regulator to be put in a low-power state during Sleep mode 0 = Writing a '0' to this bit will have no effect

- bit 0 VREGS: Voltage Regulator Standby Enable bit<sup>(2)</sup>

- 1 = Voltage regulator will remain active during Sleep mode

- 0 = Voltage regulator will go to Standby mode during Sleep mode

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: Refer to Section 22.4 "On-Chip Voltage Regulator Low-Power Modes" for details.

- 3: This bit is enabled only when the BOREN<1:0> Configuration bits (FPOR<1:0>) are set to '01'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|

| 24.24        | U-0                       | U-0              |

| 31:24        | _                 | _                 |                   |                   | _                 | —                 | —                         | _                |

| 00.10        | U-0                       | U-0              |

| 23:16        | —                 | -                 | _                 |                   | _                 | —                 | —                         | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC               | R-0, HS, HC      |

| 15:8         | _                 | _                 | _                 | —                 | _                 | S                 | 8RIPL<2:0> <sup>(1)</sup> |                  |

| 7.0          | R-0, HS, HC               | R-0, HS, HC      |

| 7:0          |                   |                   |                   | SIRQ<             | 7:0>              |                   |                           |                  |

#### REGISTER 7-3: INTSTAT: INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit |                    |  |  |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, r    | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |  |  |

bit 31-11 Unimplemented: Read as '0'

bit 10-8 **SRIPL<2:0>:** Requested Priority Level for Single Vector Mode bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

bit 7-0 SIRQ<7:0>: Last Interrupt Request Serviced Status bits 1111111-00000000 = The last interrupt request number serviced by the CPU

Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

#### REGISTER 7-4: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | IPTMR<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   |                   |                   | IPTMF             | ?<23:16>          |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 IPTMR<31:0>: Interrupt Proximity Timer Reload bits

Used by the interrupt proximity timer as a reload value when the interrupt proximity timer is triggered by an interrupt event.

# REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup> (CONTINUED)

- bit 12-10 IP1<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 9-8 IS1<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 Unimplemented: Read as '0' bit 7-5 bit 4-2 IP0<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 1-0 ISO<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

# 11.1 Watchdog Timer Control Registers

## TABLE 11-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | ø         |       |                     |       |       |                                              |       |      |      | Bits |      |      |      |      |      |      |      | s         |

|---------------------------|-----------------------|-----------|-------|---------------------|-------|-------|----------------------------------------------|-------|------|------|------|------|------|------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14               | 29/13 | 28/12 | 27/11                                        | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 2500                      | WDTCON <sup>(1)</sup> | 31:16     |       | WDTCLRKEY<15:0> 000 |       |       |                                              |       |      |      | 0000 |      |      |      |      |      |      |      |           |

| 3E80                      | WDICON                | 15:0      | ON    |                     | _     |       | RUNDIV<4:0> CLKSEL<1:0> SLPDIV<4:0> WDTWINEN |       |      |      |      | xxxx |      |      |      |      |      |      |           |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## TABLE 12-1: MCCP/SCCP REGISTER MAP (CONTINUED)

|                             | LL 1 <u>2</u> -1.               |           |         |            |          | ·      |                                         |        |            |      |             |         |         |        |         |          |        |       |               |

|-----------------------------|---------------------------------|-----------|---------|------------|----------|--------|-----------------------------------------|--------|------------|------|-------------|---------|---------|--------|---------|----------|--------|-------|---------------|

| ress<br>)                   | 20                              | е         |         |            |          |        |                                         |        |            |      | Bits        |         |         |        |         |          |        |       |               |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14      | 29/13    | 28/12  | 27/11                                   | 26/10  | 25/9       | 24/8 | 23/7        | 22/6    | 21/5    | 20/4   | 19/3    | 18/2     | 17/1   | 16/0  | All<br>Resets |

| 0260                        |                                 | 31:16     | —       | _          | —        |        | _                                       | _      | —          | _    | _           | _       | —       | _      | —       | —        | _      | —     | 0000          |

| 0200                        | 0012101                         | 15:0      |         |            |          |        |                                         |        |            | CN   | /IPA<15:0>  |         |         |        |         |          |        |       | 0000          |

| 0270                        | CCP2RB                          | 31:16     | —       | —          | —        | —      | —                                       | —      | —          | —    | —           | —       |         | —      | —       | —        | —      | —     | 0000          |

| 0210                        |                                 | 15:0      |         |            |          |        |                                         |        |            | CN   | /IPB<15:0>  |         |         |        |         |          |        |       | 0000          |

| 0280                        | CCP2BUF                         | 31:16     |         |            |          |        |                                         |        |            | CCP2 | BUFH<15:0   | )>      |         |        |         |          |        |       | 0000          |

| 0200                        | 001 2001                        | 15:0      |         |            |          |        |                                         |        |            | CCP2 | 8 BUFL<15:0 | )>      |         |        |         |          |        |       | 0000          |

| 0300                        | CCP3CON1                        | 31:16     | OPSSRC  | RTRGEN     | —        | —      |                                         | OPS<   | 3:0>       |      |             | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >      |       | 0000          |

| 0000                        | 001000111                       | 15:0      | ON      | _          | SIDL     | CCPSLP | TMRSYNC                                 | С      | LKSEL<2:0> | >    | TMRP        | S<1:0>  | T32     | CCSEL  |         | MOE      | )<3:0> |       | 0000          |

| 0310                        | CCP3CON2                        | 31:16     | OENSYNC | _          |          | _      | OCAEN ICGSM<1:0> - AUXOUT<1:0> ICS<2:0> |        |            |      | 0100        |         |         |        |         |          |        |       |               |

| 0010                        | 001 000112                      | 15:0      | PWMRSEN | ASDGM      | —        | SSDG   | _                                       | —      | _          | —    |             |         |         | ASDO   | G<7:0>  |          |        |       | 0000          |

| 0320                        | CCP3CON3                        | 31:16     | OETRIG  | 0          | SCNT<2:0 | >      | _                                       | —      | _          |      | _           | _       | POLACE  | _      | PSSAC   | E<1:0>   | _      |       | 0000          |

| 0020                        |                                 | 15:0      | —       | _          |          | _      | _                                       | —      | _          |      | _           | _       | _       | _      | _       | —        | _      |       | 0000          |

| 0330                        | CCP3STAT                        | 31:16     | —       | —          | —        | —      | —                                       | —      | —          | —    | —           | —       | —       | PRLWIP | TMRHWIP | TMRLWIP  | RBWIP  | RAWIP | 0000          |

| 0000                        | 001001/1                        | 15:0      | —       | —          | —        | —      | —                                       | ICGARM | —          | —    | CCPTRIG     | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV   | ICBNE | 0000          |

| 0340                        | CCP3TMR                         | 31:16     |         |            |          |        |                                         |        |            | CCP3 | TMRH<15:0   | )>      |         |        |         |          |        |       | 0000          |

| 00.0                        | 001 011111                      | 15:0      |         |            |          |        |                                         |        |            | CCP3 | TMRL<15:0   | )>      |         |        |         |          |        |       | 0000          |

| 0350                        | CCP3PR                          | 31:16     |         |            |          |        |                                         |        |            |      | 3 PRH<15:0  |         |         |        |         |          |        |       | 0000          |

|                             |                                 | 15:0      |         |            | 1        |        |                                         |        |            | CCP  | 3 PRL<15:0  | >       |         |        |         |          |        |       | 0000          |

| 0360                        | CCP3RA                          | 31:16     | —       | _          |          | —      | —                                       | —      | _          | —    | —           | _       | _       | —      | —       | —        | —      | —     | 0000          |

|                             |                                 | 15:0      |         |            | 1        |        |                                         |        |            | CN   | /IPA<15:0>  |         |         |        |         |          |        |       | 0000          |

| 0370                        | CCP3RB                          | 31:16     | —       | —          | —        | —      | —                                       | —      | —          | —    | —           | _       | _       | —      | —       | —        | —      | —     | 0000          |

|                             |                                 | 15:0      |         | CMPB<15:0> |          |        |                                         |        |            |      |             | 0000    |         |        |         |          |        |       |               |

| 0380                        | CCP3BUF                         | 31:16     |         |            |          |        |                                         |        |            |      | BUFH<15:(   | -       |         |        |         |          |        |       | 0000          |

|                             |                                 | 15:0      |         |            |          |        |                                         |        |            | CCP3 | 8 BUFL<15:0 | )>      |         |        |         |          |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0      |

|-----------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|-------------------------|-----------------------|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | U-0               | R/W-0             | R/W-0                   | R/W-0                 |

| 31:24     | OETRIG            |                   | OSCNT<2:0>        | •                     | -                 | (                 | OUTM<2:0> <sup>(1</sup> | )                     |

| 00.40     | U-0               | U-0               | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0                   | R/W-0                 |

| 23:16     | —                 | —                 | POLACE            | POLBDF <sup>(1)</sup> | PSSAC             | E<1:0>            | PSSBDF                  | <sup>=</sup> <1:0>(1) |

| 45.0      | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0               | U-0                     | U-0                   |

| 15:8      | —                 | —                 | -                 | —                     | -                 | —                 | -                       | —                     |

| 7.0       | U-0               | U-0               | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0                   | R/W-0                 |

| 7:0       | _                 | —                 |                   |                       | DT<5              |                   |                         |                       |

#### REGISTER 12-3: CCPxCON3: CAPTURE/COMPARE/PWMx CONTROL 3 REGISTER

| 1    |      |

|------|------|

| i ea | end: |

|      |      |

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | ad as '0'          |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

|           | <ul> <li>1 = For Triggered mode (TRIGEN = 1), the module does not drive enabled output pins until triggered</li> <li>0 = Normal output pin operation</li> </ul>                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-28 | OSCNT<2:0>: One-Shot Event Count bits                                                                                                                                                                                                                                                                                                                                                                |

|           | Extends the duration of a one-shot trigger event by an additional n clock cycles (n+1 total cycles).<br>111 = 7 timer count periods (8 cycles total)<br>110 = 6 timer count periods (7 cycles total)<br>101 = 5 timer count periods (6 cycles total)<br>100 = 4 timer count periods (5 cycles total)<br>011 = 3 timer count periods (4 cycles total)<br>010 = 2 timer count periods (3 cycles total) |

001 = 1 timer count period (2 cycles total)

**OETRIG:** PWM Dead-Time Select bit

000 = Does not extend the one-shot trigger event (the event takes 1 timer count period)

- bit 27 Unimplemented: Read as '0'

- bit 26-24 OUTM<2:0>: PWMx Output Mode Control bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Output Scan mode

- 101 = Brush DC Output mode, forward

- 100 = Brush DC Output mode, reverse

- 011 = Reserved

- 010 = Half-Bridge Output mode

- 001 = Push-Pull Output mode

- 000 = Steerable Single Output mode

- bit 23-22 Unimplemented: Read as '0'

```

bit 21 POLACE: CCPx Output Pins, OCxA, OCxC and OCxE, Polarity Control bit

```

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

- bit 20 **POLBDF:** CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit<sup>(1)</sup>

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

```

bit 19-18 PSSACE<1:0>: PWMx Output Pins, OCxA, OCxC and OCxE, Shutdown State Control bits

```

- 11 = Pins are driven active when a shutdown event occurs

- ${\tt 10}$  = Pins are driven inactive when a shutdown event occurs

- 0x = Pins are in a high-impedance state when a shutdown event occurs

- **Note 1:** These bits are implemented in MCCP modules only.

### REGISTER 14-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 11  | RTSMD: Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{\text{UxRTS}}$ pin is in Simplex mode                                                                                                                                                                                                                                                                                                |

|         | $0 = \overline{\text{UxRTS}}$ pin is in Flow Control mode                                                                                                                                                                                                                                                                                           |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                          |

| bit 9-8 | UEN<1:0>: UARTx Enable bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register</li> </ul> |

|         | 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register                                                                                                                                                                                                                |

| bit 7   | WAKE: Enable Wake-up on Start Bit Detect During Sleep Mode bit                                                                                                                                                                                                                                                                                      |

|         | <ul><li>1 = Wake-up is enabled</li><li>0 = Wake-up is disabled</li></ul>                                                                                                                                                                                                                                                                            |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                              |

|         | <ul><li>1 = Loopback mode is enabled</li><li>0 = Loopback mode is disabled</li></ul>                                                                                                                                                                                                                                                                |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync character (0x55);<br/>cleared by hardware upon completion</li> <li>0 = Baud rate measurement is disabled or has completed</li> </ul>                                                                                                                |

| bit 4   | <b>RXINV:</b> Receive Polarity Inversion bit                                                                                                                                                                                                                                                                                                        |

| 2       | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                                                                                                                            |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = High-Speed mode – 4x baud clock is enabled</li> <li>0 = Standard Speed mode – 16x baud clock is enabled</li> </ul>                                                                                                                                                                                                                     |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                                                                                                                                       |

| bit 0   | STSEL: Stop Selection bit                                                                                                                                                                                                                                                                                                                           |

|         | 1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                                                                                                                                                   |

Note 1: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ADRC              | EXTSAM            | _                 | SAMC<4:0>         |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | ADCS<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 16-3: AD1CON3: ADC CONTROL REGISTER 3

| Legend:           |                  |                      |                                    |  |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source (TSRC) bit

- 1 = Clock derived from Fast RC (FRC) oscillator

- 0 = Clock derived from Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK)

#### bit 14 EXTSAM: Extended Sampling Time bit

- 1 = ADC is still sampling after SAMP bit = 0

- 0 = ADC stops sampling when SAMP bit = 0

- bit 13 Unimplemented: Read as '0'

- bit 12-8 SAMC<4:0>: Auto-Sample Time bits

11111 **= 31 T**AD

- •

- .

- 00001 = 1 TAD

00000 = 0 TAD (Not allowed)

# bit 7-0 ADCS<7:0>: ADC Conversion Clock Select bits

- 11111111 = 2 TSRC ADCS<7:0> = 510 TSRC = TAD

- •

- .

00000001 = 2 • TSRC • ADCS<7:0> = 2 • TSRC = TAD 00000000 = 1 • TSRC = TAD

Where TSRC is a period of clock selected by the ADRC bit (AD1CON3<15>).

# 18.0 CONFIGURABLE LOGIC CELL (CLC)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 36. "Configurable Logic Cell" (DS60001363) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

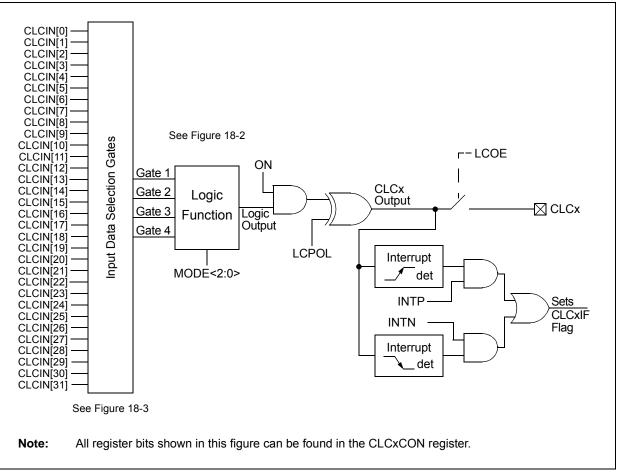

FIGURE 18-1: CLCx MODULE

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flex-ibility and potential in embedded designs since the CLC module can operate outside the limitations of software execution, and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 18-1 shows an overview of the module. Figure 18-3 shows the details of the data source multiplexers and logic input gate connections.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0              | U-0              |

| 31:24        |                   | _                 | —                 |                   | _                   | _                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | —                 | —                 | G4POL               | G3POL               | G2POL            | G1POL            |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | INTP <sup>(1)</sup> | INTN <sup>(1)</sup> |                  | _                |

| 7.0          | R/W-0             | R-0, HS, HC       | R/W-0             | U-0               | U-0                 | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | LCOE              | LCOUT             | LCPOL             | _                 | _                   |                     | MODE<2:0>        |                  |

## REGISTER 18-1: CLCxCON: CLCx CONTROL REGISTER

| Legend: HC = Hardware Clearal |                  | HS = Hardware Settable                | e bit              |

|-------------------------------|------------------|---------------------------------------|--------------------|

| R = Readable bit              | W = Writable bit | it U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR             | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |

#### bit 31-20 Unimplemented: Read as '0'

bit 19 **G4POL:** Gate 4 Polarity Control bit 1 = The output of Channel 4 logic is inverted when applied to the logic cell 0 = The output of Channel 4 logic is not inverted

#### bit 18 **G3POL:** Gate 3 Polarity Control bit

- 1 = The output of Channel 3 logic is inverted when applied to the logic cell

- 0 = The output of Channel 3 logic is not inverted

#### bit 17 G2POL: Gate 2 Polarity Control bit

1 = The output of Channel 2 logic is inverted when applied to the logic cell0 = The output of Channel 2 logic is not inverted

# bit 16 **G1POL:** Gate 1 Polarity Control bit

- 1 = The output of Channel 1 logic is inverted when applied to the logic cell

- 0 = The output of Channel 1 logic is not inverted

#### bit 15 ON: CLCx Enable bit

- 1 = CLCx is enabled and mixing input signals

- 0 = CLCx is disabled and has logic zero outputs

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 INTP: CLCx Positive Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a rising edge occurs on LCOUT

- 0 = Interrupt will not be generated

- bit 10 INTN: CLCx Negative Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a falling edge occurs on LCOUT0 = Interrupt will not be generated

- bit 9-8 Unimplemented: Read as '0'

- bit 7 LCOE: CLCx Port Enable bit

- 1 = CLCx port pin output is enabled

- 0 = CLCx port pin output is disabled

- bit 6 LCOUT: CLCx Data Output Status bit

- 1 = CLCx output high 0 = CLCx output low

- Note 1: The INTP and INTN bits should not be set at the same time for proper interrupt functionality.

# REGISTER 23-5: FOSCSEL/AFOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        |                   | _                 | _                 | _                 | —                 | _                 |                  | _                |

| 45.0         | R/P               | R/P               | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | FCKSM<1:0>        |                   | _                 | SOSCSEL           | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |

| 7.0          | R/P               | R/P               | r-1               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 7:0          | IESO              | SOSCEN            |                   | PLLSRC            | _                 |                   | FNOSC<2:0>       | 1                |

| Legend:r = Reserved bitP = Programmable bit |                  |                        |                    |  |

|---------------------------------------------|------------------|------------------------|--------------------|--|

| R = Readable bit                            | W = Writable bit | U = Unimplemented bit, | t, read as '0'     |  |

| -n = Value at POR                           | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

| bit 31-16 | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15-14 | FCKSM<1:0>: Clock Switching and Fail-Safe Clock Monitor Enable bits                                                                                                                                                                                                                                                                |

|           | <ul> <li>11 = Clock switching is enabled; Fail-Safe Clock Monitor is enabled</li> <li>10 = Clock switching is disabled; Fail-Safe Clock Monitor is enabled</li> <li>01 = Clock switching is enabled; Fail-Safe Clock Monitor is disabled</li> <li>00 = Clock switching is disabled; Fail-Safe Clock Monitor is disabled</li> </ul> |

| bit 13    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 12    | SOSCSEL: Secondary Oscillator (SOSC) External Clock Enable bit                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Crystal is used (RA4 and RB4 pins are controlled by SOSC)</li><li>0 = External clock is connected to the SOSCO pin (RA4 and RB4 pins are controlled by I/O PORTx registers)</li></ul>                                                                                                                                  |

| bit 11    | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 10    | OSCIOFNC: System Clock on CLKO Pin Enable bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = OSC2/CLKO pin operates as normal I/O</li> <li>0 = System clock is connected to the OSC2/CLKO pin</li> </ul>                                                                                                                                                                                                           |

| bit 9-8   | POSCMOD<1:0>: Primary Oscillator (POSC) Mode Selection bits                                                                                                                                                                                                                                                                        |

|           | <ul> <li>11 = Primary Oscillator is disabled</li> <li>10 = HS Oscillator mode is selected</li> <li>01 = XT Oscillator mode is selected</li> <li>00 = External Clock (EC) mode is selected</li> </ul>                                                                                                                               |

| bit 7     | IESO: Two-Speed Start-up Enable bit                                                                                                                                                                                                                                                                                                |

|           | <ul><li>1 = Two-Speed Start-up is enabled</li><li>0 = Two-Speed Start-up is disabled</li></ul>                                                                                                                                                                                                                                     |

| bit 6     | SOSCEN: Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = Secondary Oscillator is enabled</li><li>0 = Secondary Oscillator is disabled</li></ul>                                                                                                                                                                                                                                 |

| bit 5     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

| bit 4     | PLLSRC: System PLL Input Clock Selection bit                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = FRC oscillator is selected as the PLL reference input on a device Reset</li> <li>0 = Primary Oscillator (POSC) is selected as the PLL reference input on a device Reset</li> </ul>                                                                                                                                    |

| bit 3     | Reserved: Program as '1'                                                                                                                                                                                                                                                                                                           |

#### TABLE 26-12: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Operating                           | <b>Dperating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                         |                    |     |       |          |                                                                    |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|-----|-------|----------|--------------------------------------------------------------------|--|--|

| Param<br>No. Symbol Characteristics |                                                                                                                         | Min                                     | Typ <sup>(1)</sup> | Max | Units | Comments |                                                                    |  |  |

| DVR10                               | Vbg                                                                                                                     | Band Gap Reference Voltage              | _                  | 1.2 | _     | V        |                                                                    |  |  |

| DVR20                               | Vrgout                                                                                                                  | Regulator Output Voltage                | _                  | 1.8 | _     | V        | VDD > 1.9V                                                         |  |  |

| DVR21                               | CEFC                                                                                                                    | External Filter Capacitor Value         | 4.7                | 10  | —     | μF       | Series Resistance < $3\Omega$<br>recommended; < $5\Omega$ required |  |  |

| DVR30                               | Vlvr                                                                                                                    | Low-Voltage Regulator<br>Output Voltage | 0.9                | —   | 1.2   | V        | RETEN = 1,<br>RETVR (FPOR<2>) = 0                                  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 26-13: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

| Operating    | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                         |                   |      |                    |      |       |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|------|--------------------|------|-------|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                          |                   |      | Тур <sup>(2)</sup> | Max  | Units |  |

| DC18         | VHLVD <sup>(1)</sup>                                                                                                    | HLVD Voltage on VDD                     | HLVDL<3:0> = 0101 | 3.25 | _                  | 3.63 | V     |  |

|              |                                                                                                                         | Transition                              | HLVDL<3:0> = 0110 | 2.95 | —                  | 3.30 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 0111 | 2.75 | —                  | 3.09 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1000 | 2.65 | _                  | 2.98 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1001 | 2.45 | —                  | 2.80 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1010 | 2.35 | —                  | 2.69 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1011 | 2.25 | —                  | 2.55 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1100 | 2.15 | —                  | 2.44 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1101 | 2.08 | —                  | 2.33 | V     |  |

|              |                                                                                                                         |                                         | HLVDL<3:0> = 1110 | 2.00 | —                  | 2.22 | V     |  |

| DC101        | VTHL                                                                                                                    | HLVD Voltage on<br>LVDIN Pin Transition | HLVDL<3:0> = 1111 | _    | 1.2                |      | V     |  |

**Note 1:** Trip points for values of HLVD<3:0>, from '0000' to '0100', are not implemented.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

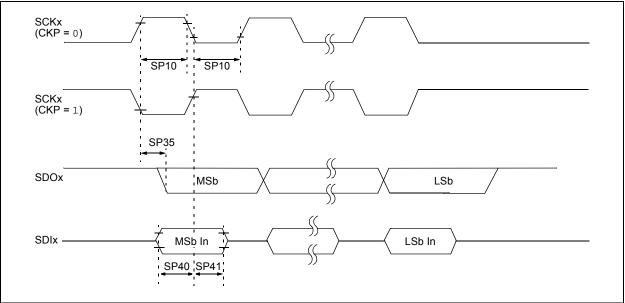

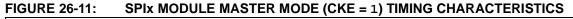

#### FIGURE 26-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |          |      |  |

|-------------------------|--------|-------------|----------|------|--|

| Dimension               | Limits | MIN         | NOM      | MAX  |  |

| Number of Pins          | N      | 28          |          |      |  |

| Pitch                   | е      | 0.65 BSC    |          |      |  |

| Overall Height          | A      | 0.80        | 0.90     | 1.00 |  |

| Standoff                | A1     | 0.00        | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF    |          |      |  |

| Overall Width           | E      | 6.00 BSC    |          |      |  |

| Exposed Pad Width       | E2     | 3.65        | 3.70     | 4.20 |  |

| Overall Length          | D      |             | 6.00 BSC |      |  |

| Exposed Pad Length      | D2     | 3.65        | 3.70     | 4.20 |  |

| Terminal Width          | b      | 0.23        | 0.30     | 0.35 |  |

| Terminal Length         | L      | 0.50        | 0.55     | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20        | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

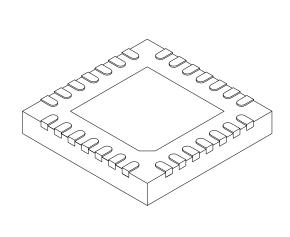

## 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2