Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-SQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl036-i-m2 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Analog Features**

- Two Analog Comparators with Input Multiplexing

- Programmable High/Low-Voltage Detect (HLVD)

- 5-Bit DAC with Output Pin

- Up to 14-Channel, Software-Selectable 10/12-Bit SAR Analog-to-Digital Converter (ADC):

- 12-bit, 200K samples/second conversion rate (single Sample-and-Hold)

- 10-bit, 300K samples/second conversion rate (single Sample-and-Hold)

- Sleep mode operation

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

- Brown-out Reset (BOR)

|                   |       | (bytes)                 | (Kbytes)        | O/PPS                   | Maximum           | Maximum         |                                |               |                     | ppak<br>hera        |     | -                                    | (Channels)         |             |     |      |      |                                  |

|-------------------|-------|-------------------------|-----------------|-------------------------|-------------------|-----------------|--------------------------------|---------------|---------------------|---------------------|-----|--------------------------------------|--------------------|-------------|-----|------|------|----------------------------------|

| Device            | Pins  | Program Memory (Kbytes) | Data Memory (Kb | General Purpose I/O/PPS | 16-Bit Timers Max | PWM Outputs Max | UART <sup>(1)</sup> /LIN/J2602 | 16-Bit Timers | MCCP <sup>(3)</sup> | SCCP <sup>(4)</sup> | СГС | SPI <sup>(2)</sup> /I <sup>2</sup> S | 10/12-Bit ADC (Cha | Comparators | CRC | RTCC | JTAG | Packages                         |

| PIC32MM0016GPL020 | 20    | 16                      | 4               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0032GPL020 | 20    | 32                      | 8               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0064GPL020 | 20    | 64                      | 8               | 16/16                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                 | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |

| PIC32MM0016GPL028 | 28    | 16                      | 4               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SSOP/SOIC/<br>QFN/UQFN           |

| PIC32MM0032GPL028 | 28    | 32                      | 8               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SSOP/ SOIC/<br>QFN/UQFN          |

| PIC32MM0064GPL028 | 28    | 64                      | 8               | 22/19                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                 | 2           | Yes | Yes  | Yes  | SPDIP/SSOP/<br>SOIC/QFN/<br>UQFN |

| PIC32MM0016GPL036 | 36/40 | 16                      | 4               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

| PIC32MM0032GPL036 | 36/40 | 32                      | 8               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

| PIC32MM0064GPL036 | 36/40 | 64                      | 8               | 29/20                   | 7                 | 8               | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                 | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |

#### TABLE 1: PIC32MM0064GPL036 FAMILY DEVICES

**Note 1:** UART1 has assigned pins. UART2 is remappable.

**2:** SPI1 has assigned pins. SPI2 is remappable.

**3:** MCCP can be configured as a PWM with up to 6 outputs, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

4: SCCP can be configured as a PWM with 1 output, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. This data sheet contains device-specific information for the PIC32MM0064GPL036 family devices.

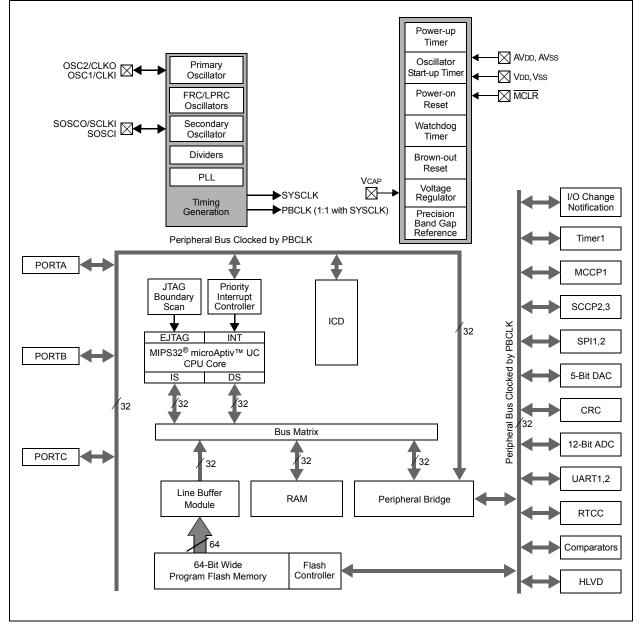

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0064GPL036 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

#### FIGURE 1-1: PIC32MM0064GPL036 FAMILY BLOCK DIAGRAM

|          |               |                | Pin                    | Number                        |                |                |             |                |                                      |  |  |  |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------|--|--|--|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                          |  |  |  |

| PGEC1    | 2             | 5              | 2                      | 5                             | 36             | 39             | Ι           | ST             | ICSP Port 1 programming clock input  |  |  |  |

| PGEC2    | 19            | 2              | 19                     | 22                            | 25             | 28             | I           | ST             | ICSP Port 2 programming clock input  |  |  |  |

| PGEC3    | 7             | 10             | 12                     | 15                            | 16             | 16             | I           | ST             | ICSP Port 3 programming clock input  |  |  |  |

| PGED1    | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | ICSP Port 1 programming data         |  |  |  |

| PGED2    | 20            | 3              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | ICSP Port 2 programming data         |  |  |  |

| PGED3    | 6             | 9              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | ICSP Port 3 programming data         |  |  |  |

| PWRLCLK  | 7             | 10             | 9                      | 12                            | 10             | 10             | I           | ST             | Real-Time Clock 50/60 Hz clock input |  |  |  |

| RA0      | 19            | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RA1      | 20            | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RA2      | 4             | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RA3      | 5             | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RA4      | 7             | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RA9      | _             | _              | _                      | _                             | 11             | 11             | I/O         | ST/DIG         | PORTA digital I/O                    |  |  |  |

| RB0      | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB1      | 2             | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB2      | 3             | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB3      | _             |                | 4                      | 7                             | 2              | 2              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB4      | 6             | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB5      | _             | _              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB6      | _             |                | 12                     | 15                            | 16             | 16             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB7      | 8             | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB8      | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB9      | 10            | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB10     | _             | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB11     | _             | _              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB12     | 12            | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB13     | 13            | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB14     | 14            | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RB15     | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | PORTB digital I/O                    |  |  |  |

| RC0      | —             | _              | _                      | _                             | 3              | 3              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |  |

| RC1      | _             | _              | _                      | _                             | 4              | 4              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |  |

| RC2      | _             | _              | —                      | —                             | 5              | 5              | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |  |

| RC3      | —             | _              | _                      | _                             | 14             | 14             | I/O         | ST/DIG         | PORTC digital I/O                    |  |  |  |

| RC8      | _             | _              | _                      | _                             | 20             | 21             | I/O         | ST/DIG         | G PORTC digital I/O                  |  |  |  |

| RC9      | _             | _              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         | IG PORTC digital I/O                 |  |  |  |

| REFCLKI  | 10            | 13             | 15                     | 18                            | 19             | 20             | I           | ST             | Reference clock input                |  |  |  |

| REFCLKO  | 15            | 18             | 23                     | 26                            | 29             | 32             | 0           | DIG            |                                      |  |  |  |

| Legend:  | ST = Sc       | hmitt Tric     | ger input              | buffer                        | DIG = Dig      | nital innu     | t/output    |                |                                      |  |  |  |

#### **TABLE 1-1:** PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

|          |               |                | Pin                    | Number                        |                |                |             | 1              |                                               |  |  |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|-----------------------------------------------|--|--|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                                   |  |  |

| RP1      | 19            | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | Remappable peripherals (input or output)      |  |  |

| RP2      | 20            | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         |                                               |  |  |

| RP3      | 4             | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         |                                               |  |  |

| RP4      | 5             | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         |                                               |  |  |

| RP5      | 6             | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         |                                               |  |  |

| RP6      | 7             | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         |                                               |  |  |

| RP7      | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         |                                               |  |  |

| RP8      | 10            | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         |                                               |  |  |

| RP9      | 14            | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         |                                               |  |  |

| RP10     | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         |                                               |  |  |

| RP11     | 8             | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         |                                               |  |  |

| RP12     | 12            | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         |                                               |  |  |

| RP13     | 13            | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         |                                               |  |  |

| RP14     | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         |                                               |  |  |

| RP15     | 2             | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         |                                               |  |  |

| RP16     | 3             | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         |                                               |  |  |

| RP17     |               | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         |                                               |  |  |

| RP18     | —             | —              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         |                                               |  |  |

| RP19     | —             | —              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         |                                               |  |  |

| RP20     | —             | —              | —                      | —                             | 11             | 11             | I/O         | ST/DIG         |                                               |  |  |

| RTCC     | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | Real-Time Clock alarm/seconds output          |  |  |

| SCK1     | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | SPI1 clock (input or output)                  |  |  |

| SCLKI    | 7             | 10             | 9                      | 12                            | 10             | 10             | Ι           | ST             | Secondary Oscillator external clock input     |  |  |

| SDI1     | 14            | 17             | 22                     | 25                            | 28             | 31             | Ι           | ST             | SPI1 data input                               |  |  |

| SDO1     | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | SPI1 data output                              |  |  |

| SOSCI    | 6             | 9              | 8                      | 11                            | 9              | 9              | —           | —              | Secondary Oscillator crystal                  |  |  |

| SOSCO    | 7             | 10             | 9                      | 12                            | 10             | 10             | —           | —              | Secondary Oscillator crystal                  |  |  |

| SS1      | 15            | 18             | 23                     | 26                            | 29             | 32             | Ι           | ST             | SPI1 slave select input                       |  |  |

| T1CK     | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | Timer1 external clock input                   |  |  |

| T1G      | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | Timer1 clock gate input                       |  |  |

| тск      | 9             | 12             | 14                     | 17                            | 18             | 18             | Ι           | ST             | JTAG clock input                              |  |  |

| TDI      | 13            | 16             | 19                     | 22                            | 25             | 28             | Ι           | ST             | JTAG data input                               |  |  |

| TDO      | 12            | 15             | 18                     | 21                            | 24             | 27             | 0           | DIG            | JTAG data output                              |  |  |

| TMS      | 10            | 13             | 15                     | 18                            | 19             | 20             | Ι           | ST             | JTAG mode select input                        |  |  |

| U1BCLK   | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | UART1 IrDA <sup>®</sup> 16x baud clock output |  |  |

| U1CTS    | 9             | 12             | 14                     | 17                            | 18             | 18             | Ι           | ST             | UART1 transmission control input              |  |  |

| U1RTS    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | G UART1 reception control output              |  |  |

| U1RX     | 15            | 18             | 23                     | 26                            | 29             | 32             | Ι           | ST             | UART1 receive data input                      |  |  |

| U1TX     | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | UART1 transmit data output                    |  |  |

| Legend:  | ST = Sc       | hmitt Tric     | ger input              | buffer                        | DIG = Dig      | nital input    | t/output    |                | ANA = Analog level input/output               |  |  |

#### PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED) **TABLE 1-1:**

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

## PIC32MM0064GPL036 FAMILY

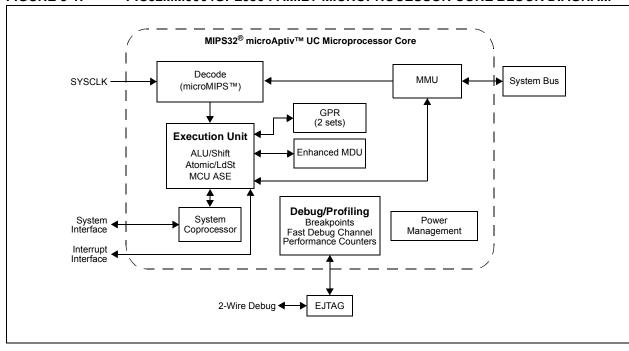

#### FIGURE 3-1: PIC32MM0064GPL036 FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS60001118) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

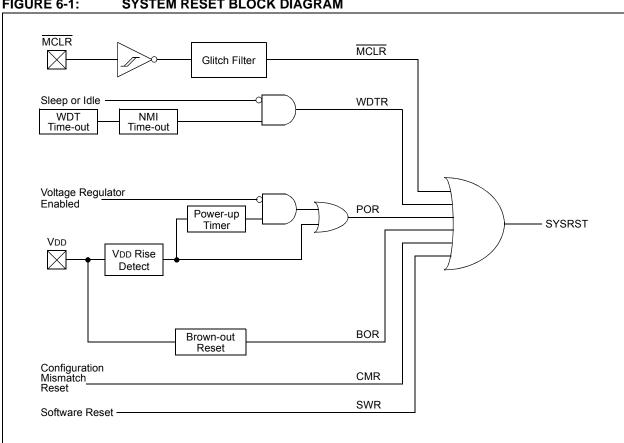

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The device Reset sources are as follows:

- Power-on Reset (POR)

- Master Clear Reset Pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### SYSTEM RESET BLOCK DIAGRAM FIGURE 6-1:

#### TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)

| lress<br>#)                | 50                              | je        |       |       |       |       |              |       |        | Bits   | 6    |      |      |      |             |      |         |        | ets      |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------------|-------|--------|--------|------|------|------|------|-------------|------|---------|--------|----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11        | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3        | 18/2 | 17/1    | 16/0   | All Rese |

| F4.00                      | IPC8                            | 31:16     | _     |       | —     | —     | _            | _     | —      | _      | _    | —    | _    | (    | CCT3IP<2:0> | •    | CCT3IS  | <1:0>  | 0000     |

| F1C0                       | IPC8                            | 15:0      | -     | _     | _     |       | CCP3IP<2:0>  | >     | CCP38  | S<1:0> | _    | _    | _    | (    | CCT2IP<2:0> | •    | CCT2IS  | <1:0>  | 0000     |

| 5400                       | IDOO                            | 31:16     |       | _     | _     |       | SPI2RXIP<2:0 | )>    | SPI2RX | S<1:0> | _    | _    | _    | S    | PI2TXIP<2:0 | >    | SPI2TXI | S<1:0> | 0000     |

| F1D0                       | IPC9                            | 15:0      | _     | _     | _     |       | SPI2EIP<2:0  | >     | SPI2EI | S<1:0> | _    | —    | _    | _    |             | _    | —       | _      | 0000     |

| <b>F4F0</b>                | 10040                           | 31:16     | _     | _     | _     |       | _            | _     | —      | _      | _    | —    | _    |      | U2EIP<2:0>  |      | U2EIS•  | <1:0>  | 0000     |

| F1E0                       | IPC10                           | 15:0      | -     | _     | _     |       | U2TXIP<2:0>  |       | U2TXIS | 6<1:0> | _    | _    | _    | ι    | J2RXIP<2:0> | •    | U2RXIS  | <1:0>  | 0000     |

| <b>E4E0</b>                | 10044                           | 31:16     | _     | _     | _     |       | CPCIP<2:0>   |       | CPCIS  | <1:0>  | _    | —    | _    |      | NVMIP<2:0>  |      | NVMIS   | <1:0>  | 0000     |

| F1F0                       | IPC11                           | 15:0      | _     | -     | —     | _     |              | _     | _      | _      | _    |      | _    | _    | _           | _    | —       |        | 0000     |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

2: These bits are not available on 20-pin devices.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

#### REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|-------------------|----------------------------|-------------------|----------------------|------------------|--|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   | PRI6SS<3:0> <sup>(1)</sup> |                   |                      |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   |                            | PRI4SS            | <3:0> <sup>(1)</sup> |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |  |

| 15:8         |                   | PRI3SS            | <3:0> <sup>(1)</sup> |                   |                            | PRI2SS            | <3:0>(1)             |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0                        | U-0               | U-0                  | R/W-0            |  |  |  |  |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> |                   | —                          | —                 | —                    | SS0              |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

0001 = Interrupt with a priority level of 6 uses Shadow Set 1

0000 = Interrupt with a priority level of 6 uses Shadow Set 0

#### 9.7 Pin Pull-up and Pull-Down

Each I/O pin also has a weak pull-up and a weak pulldown connected to it. The pull-ups act as a current source, or sink source, connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

#### 9.8 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 9.8.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation, "RPn", in their full pin designation, where "RP" designates a Remappable Peripheral and "n" is the remappable port number.

#### 9.8.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (MCCP, SCCP) and others.

In comparison, some digital only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 9.8.3 CONTROLLING PPS

PPS features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

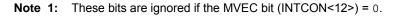

## 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

#### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

#### TABLE 16-1: ADC REGISTER MAP (CONTINUED)

|                             |                                 | _         |       |          |       |        |          |         |         |         |          |                 |        |      |          |           |      |       |            |

|-----------------------------|---------------------------------|-----------|-------|----------|-------|--------|----------|---------|---------|---------|----------|-----------------|--------|------|----------|-----------|------|-------|------------|

| ess                         |                                 |           |       |          |       |        |          |         |         | Bits    | 6        |                 |        |      |          |           |      |       |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15 | 30/14    | 29/13 | 28/12  | 27/11    | 26/10   | 25/9    | 24/8    | 23/7     | 22/6            | 21/5   | 20/4 | 19/3     | 18/2      | 17/1 | 16/0  | All Resets |

| 0750                        |                                 | 31:16     |       |          |       |        |          |         |         | DC1BUF1 | 1-21:0>  |                 |        |      |          |           |      |       | 0000       |

| 07E0                        | ADC1BUF14                       | 15:0      |       |          |       |        |          |         | A       | JCIBUFI | 4<31:0>  |                 |        |      |          |           |      |       | 0000       |

| 0750                        | ADC1BUF15                       | 31:16     |       |          |       |        |          |         |         | DC1BUF1 | E <21:0> |                 |        |      |          |           |      |       | 0000       |

| 07F0                        | ADCIBUEIS                       | 15:0      |       |          |       |        |          |         | A       | JCIBUFI | 5<31.0>  |                 |        |      |          |           |      |       | 0000       |

| 0800                        | AD1CON1                         | 31:16     |       | —        | _     | _      | —        | —       | _       | —       | _        | _               | —      | _    | —        |           | —    |       | 0000       |

| 0800                        | ADICONT                         | 15:0      | ON    |          | SIDL  | _      | —        | F       | ORM<2:0 | >       |          | SSR             | C<3:0> |      | MODE12   | ASAM      | SAMP | DONE  | 0000       |

| 0810                        | AD1CON2                         | 31:16     | _     | —        | —     | —      | —        | —       | —       | —       | —        | —               | —      | —    | —        | —         | —    | _     | 0000       |

| 0010                        | ADICONZ                         | 15:0      |       | VCFG<2:0 | 0>    | OFFCAL | BUFREGEN | CSCNA   | —       | _       | BUFS     | _               |        | SMF  | PI<3:0>  |           | BUFM | _     | 0000       |

| 0820                        | AD1CON3                         | 31:16     | _     | —        | _     | _      | -        | —       | —       | _       | —        | —               | —      | —    | —        |           | —    | _     | 0000       |

| 0020                        | AB TOONG                        | 15:0      | ADRC  | EXTSAM   |       |        | SAN      | 1C<4:0> |         |         |          |                 |        | AD   | )CS<7:0> |           |      |       | 0000       |

| 0840                        | AD1CHS                          | 31:16     | _     | —        | _     | _      |          | —       | —       | _       | —        | _               | —      | —    | —        | _         | _    | —     | 0000       |

| 0040                        | ABTOHO                          | 15:0      | —     | —        | —     | —      | —        | —       | —       | —       | С        | H0NA<2:         | 0>     |      | (        | CH0SA<4:0 | >    |       | 0000       |

| 0850                        | AD1CSS                          | 31:16     |       |          |       |        |          |         |         |         |          | 0000            |        |      |          |           |      |       |            |

| 0000                        | 7101000                         | 15:0      | _     | —        |       |        |          |         |         |         | CSS<13   | 0> <b>(1,2)</b> |        |      |          |           |      |       | 0000       |

| 0870                        | AD1CON5                         | 31:16     | _     | —        | _     | —      |          | —       | —       | _       | —        | _               |        | _    | _        | _         |      | —     | 0000       |

| 0070                        | AB TOONS                        | 15:0      | ASEN  | LPEN     | _     | BGREQ  | _        | —       | ASINT   | <1:0>   | —        | -               |        | —    | WM<      | :1:0>     | CM<  | :1:0> | 0000       |

| 0880                        | AD1CHIT                         | 31:16     | _     | _        | _     | —      | -        | —       | —       | _       | —        | _               | —      | —    | —        |           | _    | —     | 0000       |

| 0000                        |                                 | 15:0      | —     | —        |       |        |          |         |         |         | CHH<13   | (1,2 <b>)</b>   |        |      |          |           |      |       | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The CSS<13:11> and CHH<13:11> bits are not implemented in 20-pin devices.

2: The CSS<13:12> and CHH<13:12> bits are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### REGISTER 17-1: CRCCON: CRC CONTROL REGISTER (CONTINUED)

- bit 2 MOD: CRC Calculation Mode bit

- 1 = Alternate mode

- 0 = Legacy mode

- bit 1-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | X<3               | 1:24>             |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | X<2               | 3:16>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | X<1               | 5:8>              |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          |                   |                   |                   | X<7:1>            |                   |                   |                  | _                |

#### REGISTER 17-2: CRCXOR:CRC XOR REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 X<31:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0              | U-0              |

| 31:24        |                   | _                 | —                 |                   | _                   | _                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | —                 | —                 | G4POL               | G3POL               | G2POL            | G1POL            |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | INTP <sup>(1)</sup> | INTN <sup>(1)</sup> |                  | _                |

| 7.0          | R/W-0             | R-0, HS, HC       | R/W-0             | U-0               | U-0                 | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | LCOE              | LCOUT             | LCPOL             | _                 | _                   |                     | MODE<2:0>        |                  |

#### REGISTER 18-1: CLCxCON: CLCx CONTROL REGISTER

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable | e bit              |

|-------------------|-----------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-20 Unimplemented: Read as '0'

bit 19 **G4POL:** Gate 4 Polarity Control bit 1 = The output of Channel 4 logic is inverted when applied to the logic cell 0 = The output of Channel 4 logic is not inverted

#### bit 18 **G3POL:** Gate 3 Polarity Control bit

- 1 = The output of Channel 3 logic is inverted when applied to the logic cell

- 0 = The output of Channel 3 logic is not inverted

#### bit 17 G2POL: Gate 2 Polarity Control bit

1 = The output of Channel 2 logic is inverted when applied to the logic cell0 = The output of Channel 2 logic is not inverted

## bit 16 **G1POL:** Gate 1 Polarity Control bit

- 1 = The output of Channel 1 logic is inverted when applied to the logic cell

- 0 = The output of Channel 1 logic is not inverted

#### bit 15 ON: CLCx Enable bit

- 1 = CLCx is enabled and mixing input signals

- 0 = CLCx is disabled and has logic zero outputs

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 INTP: CLCx Positive Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a rising edge occurs on LCOUT

- 0 = Interrupt will not be generated

- bit 10 INTN: CLCx Negative Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a falling edge occurs on LCOUT0 = Interrupt will not be generated

- bit 9-8 Unimplemented: Read as '0'

- bit 7 LCOE: CLCx Port Enable bit

- 1 = CLCx port pin output is enabled

- 0 = CLCx port pin output is disabled

- bit 6 LCOUT: CLCx Data Output Status bit

- 1 = CLCx output high 0 = CLCx output low

- Note 1: The INTP and INTN bits should not be set at the same time for proper interrupt functionality.

#### **19.1 Comparator Control Registers**

#### TABLE 19-1: COMPARATOR 1 AND 2 REGISTER MAP

| ess                         |                                 | n         |       | Bits  |       |       |       |       |      |          |      |        |      | ú    |      |      |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|----------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 0000                        | OMOTAT                          | 31:16     | —     | _     | —     | —     | _     | —     | —    | —        | _    | -      | -    | —    | —    | _    | C2EVT | C1EVT | 0000       |

| 0900                        | CMSTAT                          | 15:0      | _     | _     | SIDL  | _     | _     | _     | _    | CVREFSEL | —    | _      | _    | _    | _    | _    | C2OUT | C10UT | 0000       |

| 0910                        | CM1CON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _        | _    | _      | _    | _    | _    | _    | _     | _     | 0000       |

| 0910                        | CINICON                         | 15:0      | ON    | COE   | CPOL  | _     | _     | _     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | 0000       |

| 0930                        | CM2CON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    |          | _    | _      | _    | _    | _    | _    | _     | _     | 0000       |

| 0930                        | CIMZCON                         | 15:0      | ON    | COE   | CPOL  | _     | _     |       | CEVT | COUT     | EVPO | L<1:0> | -    | CREF |      | _    | CCH   | <1:0> | 0000       |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# REGISTER 23-5: FOSCSEL/AFOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER (CONTINUED)

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 110 and 111 = Reserved (selects Fast RC (FRC) Oscillator with Divide-by-N)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Reserved

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Primary or FRC Oscillator with PLL

- 000 = Fast RC (FRC) Oscillator with Divide-by-N

#### REGISTER 23-6: FSEC/AFSEC: CODE-PROTECT CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/P               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | CP                | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | —                 | —                 | —                 | _                 | —                 | _                 | —                | —                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| Legend:           | r = Reserved bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 CP: Code Protection Enable bit

1 = Code protection is disabled

0 = Code protection is enabled

bit 30-0 Reserved: Program as '1'

### TABLE 26-4: OPERATING CURRENT (IDD)<sup>(2)</sup>

| <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |                        |      |       |      |                    |  |  |  |

|---------------------------------------------------------------------------|------------------------|------|-------|------|--------------------|--|--|--|

| Parameter No.                                                             | Typical <sup>(1)</sup> | Max  | Units | Vdd  | Conditions         |  |  |  |

| DC19                                                                      | 0.45                   | 0.65 | mA    | 2.0V |                    |  |  |  |

| DC19                                                                      | 0.45                   | 0.65 | mA    | 3.3V | Fsys = 1 MHz       |  |  |  |

| DC23                                                                      | 2.5                    | 3.5  | mA    | 2.0V | Fsys = 8 MHz       |  |  |  |

|                                                                           | 2.5                    | 3.5  | mA    | 3.3V | 1 3 1 3 - 0 101 12 |  |  |  |

| DC24                                                                      | 7.0                    | 9.2  | mA    | 2.0V | Fsys = 25 MHz      |  |  |  |

|                                                                           | 7.0                    | 9.2  | mA    | 3.3V | 1 STS - 25 WI 12   |  |  |  |

| DC25                                                                      | 0.26                   | 0.35 | mA    | 2.0V | Fsys = 32 kHz      |  |  |  |

|                                                                           | 0.26                   | 0.35 | mA    | 3.3V | TSTS - 52 NIZ      |  |  |  |

**Note 1:** Data in the "Typical" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Base IDD current is measured with:

- Oscillator is configured in EC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 010 and POSCMOD<1:0> (FOSCSEL<9:8>) = 00)

- + OSC1 pin is driven with external square wave with levels from 0.3V to VDD 0.3V

- OSC2 is configured as an I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- · All I/O pins (except OSC1) are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- NOP instructions are executed

| Parameter<br>No. | Typical <sup>(1)</sup> | Max  | Units | Operating<br>Temperature | Vdd  | Conditions                                                        |  |  |  |

|------------------|------------------------|------|-------|--------------------------|------|-------------------------------------------------------------------|--|--|--|

| DC60             | 134                    | 198  | μA    | -40°C                    |      |                                                                   |  |  |  |

|                  | 136                    | 208  | μA    | +25°C                    | 2.0V |                                                                   |  |  |  |

|                  | 141                    | 217  | μA    | +85°C                    |      | Sleep with active main voltage regulator                          |  |  |  |

|                  | 139                    | 209  | μA    | -40°C                    |      | - (VREGS (PWRCON<0>) = 1,<br>RETEN (PWRCON<1>) =0)                |  |  |  |

|                  | 141                    | 217  | μA    | +25°C                    | 3.3V |                                                                   |  |  |  |

|                  | 143                    | 231  | μA    | +85°C                    |      |                                                                   |  |  |  |

| DC61             | 4.3                    | 11.7 | μA    | -40°C                    |      |                                                                   |  |  |  |

|                  | 5.1                    | 15.6 | μA    | +25°C                    | 2.0V | Sleep with main voltage regulator in                              |  |  |  |

|                  | 11.4                   | 34.3 | μA    | +85°C                    |      | Standby mode<br>(VREGS (PWRCON<0>) = 0,<br>RETEN (PWRCON<1>) = 0) |  |  |  |

|                  | 6.1                    | 16.8 | μA    | -40°C                    | 3.3V |                                                                   |  |  |  |

|                  | 6.9                    | 20.1 | μA    | +25°C                    |      |                                                                   |  |  |  |

|                  | 12.7                   | 36.0 | μA    | +85°C                    |      |                                                                   |  |  |  |

| DC62             | 2.3                    | _    | μA    | -40°C                    |      | Sleep with enabled retention voltage                              |  |  |  |

|                  | 2.7                    |      | μA    | +25°C                    | 2.0V |                                                                   |  |  |  |

|                  | 5.2                    |      | μA    | +85°C                    |      | regulator (VREGS (PWRCON<0>) = 1,                                 |  |  |  |

|                  | 2.3                    | —    | μA    | -40°C                    |      | RETEN (PWRCON<1>) = 1,                                            |  |  |  |

|                  | 2.7                    | —    | μA    | +25°C                    | 3.3V | RETVR(FPOR<2>)=0)                                                 |  |  |  |

|                  | 5.4                    | —    | μA    | +85°C                    |      |                                                                   |  |  |  |

| DC63             | 0.28                   | —    | μA    | -40°C                    |      |                                                                   |  |  |  |

|                  | 0.44                   | —    | μA    | +25°C                    | 2.0V | Sleep with enabled retention voltage                              |  |  |  |

|                  | 2.52                   |      | μA    | +85°C                    |      | regulator (VREGS (PWRCON<0>) = 0,                                 |  |  |  |

|                  | 0.29                   | _    | μA    | -40°C                    |      | <b>RETEN</b> (PWRCON<1>) = 1,                                     |  |  |  |

|                  | 0.44                   | _    | μA    | +25°C                    | 3.3V | RETVR(FPOR<2>)=0)                                                 |  |  |  |

|                  | 2.62                   |      | μA    | +85°C                    |      |                                                                   |  |  |  |

#### TABLE 26-6: POWER-DOWN CURRENT (IPD)<sup>(2)</sup>

**Note 1:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with:

- Oscillator is configured in FRC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 000)

- OSC2 is configured as I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- All I/O pins are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

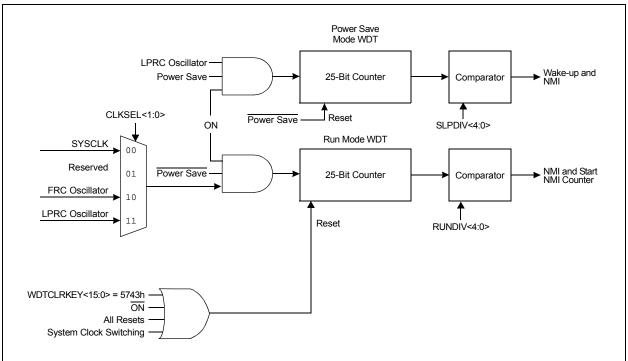

#### TABLE 26-27: MCCP AND SCCP PWM MODE TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |        |                                |     |     |       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|-----|-----|-------|--|--|--|--|

| Param<br>No.                                                                                                            | Symbol | Characteristics <sup>(1)</sup> | Min | Max | Units |  |  |  |  |

| OC15                                                                                                                    | Tfd    | Fault Input to PWM I/O Change  | _   | 30  | ns    |  |  |  |  |

| OC20                                                                                                                    | TFLT   | Fault Input Pulse Width        | 10  |     | ns    |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

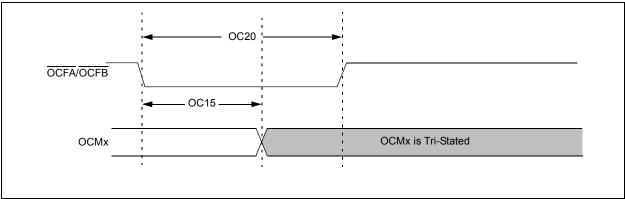

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES |          |       |  |

|----------------------------|----------|--------|----------|-------|--|

| Dimensio                   | n Limits | MIN    | NOM      | MAX   |  |

| Number of Pins             | Ν        |        | 28       |       |  |

| Pitch                      | е        |        | .100 BSC |       |  |

| Top to Seating Plane       | А        | -      | -        | .200  |  |

| Molded Package Thickness   | A2       | .120   | .135     | .150  |  |

| Base to Seating Plane      | A1       | .015   | -        | -     |  |

| Shoulder to Shoulder Width | Е        | .290   | .310     | .335  |  |

| Molded Package Width       | E1       | .240   | .285     | .295  |  |

| Overall Length             | D        | 1.345  | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L        | .110   | .130     | .150  |  |

| Lead Thickness             | С        | .008   | .010     | .015  |  |

| Upper Lead Width           | b1       | .040   | .050     | .070  |  |

| Lower Lead Width           | b        | .014   | .018     | .022  |  |

| Overall Row Spacing §      | eВ       | _      | -        | .430  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B