Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detalls                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 29                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | •                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-SQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0032gpl036t-i-m2 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

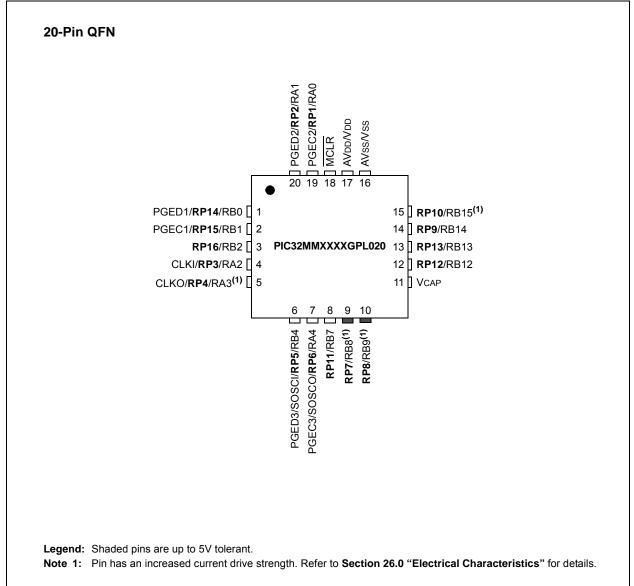

## **Pin Diagrams (Continued)**

| TABLE 3: | COMPLETE PIN FUNCTION DESCRIPTIONS FOR 20-PIN QFN DEVICES |

|----------|-----------------------------------------------------------|

|----------|-----------------------------------------------------------|

| Function                                                                                                   | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGED1/AN2/C1IND/C2INB/RP14/RB0                                                                             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                       | VCAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PGEC1/AN3/C1INC/C2INA/RP15/RB1                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                       | TDO/AN7/LVDIN/ <b>RP12</b> /RB12                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AN4/ <b>RP16</b> /RB2                                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                       | TDI/AN8/ <b>RP13</b> /RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OSC1/CLKI/AN5/C1INB/RP3/OCM1C/RA2                                                                          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                       | CDAC1/AN9/RP9/RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSC2/CLKO/AN6/C1INA/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                       | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PGED3/SOSCI/ <b>RP5</b> /RB4                                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                       | AVss/Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PGEC3/SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                       | AVbd/Vbd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>RP11</b> /RB7                                                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                       | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                       | 19                                                                                                                                                                                                                                                                                                                                                                                                                                       | PGEC2/VREF+/AN0/RP1/OCM1E/INT3/RA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <mark>U1RTS</mark> /U1BCLK/SDO1/<br>C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> | 20                                                                                                                                                                                                                                                                                                                                                                                                                                       | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                            | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0<br>PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1<br>AN4/ <b>RP16</b> /RB2<br>OSC1/CLKI/AN5/C1INB/ <b>RP3</b> /OCM1C/RA2<br>OSC2/CLKO/AN6/C1INA/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup><br>PGED3/SOSCI/ <b>RP5</b> /RB4<br>PGEC3/SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4<br><b>RP11</b> /RB7<br>TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup><br>TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/U1RTS/U1BCLK/SDO1/ | PGED1/AN2/C1IND/C2INB/RP14/RB0         11           PGEC1/AN3/C1INC/C2INA/RP15/RB1         12           AN4/RP16/RB2         13           OSC1/CLKI/AN5/C1INB/RP3/OCM1C/RA2         14           OSC2/CLKO/AN6/C1INA/RP4/OCM1D/RA3 <sup>(1)</sup> 15           PGED3/SOSCI/RP5/RB4         16           PGEC3/SOSCO/SCLKI/RP6/PWRLCLK/RA4         17           RP11/RB7         18           TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup> 19           TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SD01/         20 |

Note 1: Pin has an increased current drive strength.

|          |               |                | Pin                    | Number                        |                |                |                                                 |                |                                                    |  |  |  |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------------------------------------------|----------------|----------------------------------------------------|--|--|--|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type                                     | Buffer<br>Type | Description                                        |  |  |  |

| VCAP     | 11            | 14             | 17                     | 20                            | 22             | 24             | Р                                               | —              | Core voltage regulator filter capacitor connection |  |  |  |

| Vdd      | 17            | 20             | 10,25                  | 13,28                         | 13,23,31       | 13,26,<br>34   | Р                                               | —              | Digital modules power supply                       |  |  |  |

| VREF-    | 20            | 3              | 28                     | 3                             | 34             | 37             | I                                               | ANA            | ADC negative reference                             |  |  |  |

| VREF+    | 19            | 2              | 27                     | 2                             | 33             | 36             | I                                               | ANA            | ADC and DAC positive reference                     |  |  |  |

| Vss      | 16            | 19             | 5,24                   | 8,27                          | 6,12,30        | 6,12,<br>33    | Р                                               | —              | Digital modules ground                             |  |  |  |

| Legend:  | ST = Sc       | hmitt Trig     | iger input             | buffer                        | DIG = Dig      | jital inpu     | al input/output ANA = Analog level input/output |                |                                                    |  |  |  |

TABLE 1-1: PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

© 2015-2016 Microchip Technology Inc.

NOTES:

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC microprocessor core in the PIC32MM0064GPL036 family devices contains several logic blocks, working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Power Management

- microMIPS Instructions Decoder

- Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous Multiply/ Divide Unit (MDU). The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port, and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid Stalls when executing instruction streams where data producing instructions are followed closely by consumers for their results

- Leading zero/one detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The microAptiv UC core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows the long-running MDU operations to be partially masked by system Stalls and/or other Integer Unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, Result/Accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the rs operand. The second number ('16' of 32x16) represents the rt operand. The microAptiv UC core only checks the value of the rt operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back, 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU. Divide operations are implemented with a simple 1-bit-per-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (rs) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16-bit wide rs, 15 iterations are skipped, and for a 24-bit wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline Stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be re-issued), and latency (number of cycles until a result is available) for the microAptiv UC core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL (GPR destination)   | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

#### TABLE 3-1: MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

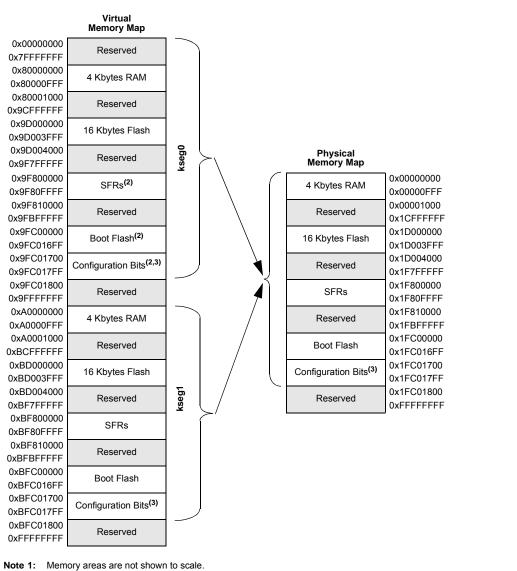

## FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 16 Kbytes OF PROGRAM MEMORY<sup>(1)</sup>

2: This region should be accessed from kseg1 space only.

3: Primary Configuration bits area is located at the address range, from 0x1FC01780 to 0x1FC017E8. Alternate Configuration bits area is located at the address range, from 0x1FC01700 to 0x1FC01768. Refer to Section 4.1 "Alternate Configuration Bits Space" for more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6   | Bit<br>29/21/13/5      | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|---------------------|---------------------|------------------------|-------------------------|-------------------|-------------------|----------------------|------------------|

| 24.24        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 31:24        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 00.40        | U-0                 | U-0                 | U-0                    | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 23:16        | _                   | _                   |                        | _                       |                   | _                 | _                    | —                |

| 45-0         | R/W-0, HC           | R/W-0               | R-0, HS, HC            | R-0, HS, HC             | r-0               | U-0               | U-0                  | U-0              |

| 15:8         | WR <sup>(1,4)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1,2)</sup> | LVDERR <sup>(1,2)</sup> | —                 | _                 | _                    | —                |

| 7.0          | U-0                 | U-0                 | U-0                    | U-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 7:0          |                     | -                   |                        | —                       |                   | NVMOP             | <3:0> <sup>(3)</sup> |                  |

#### REGISTER 5-1: NVMCON: NVM PROGRAMMING CONTROL REGISTER

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit           |  |  |  |

|-------------------|----------------------------|---------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared r = Reserved bit |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 WR: Write Control bit<sup>(1,4)</sup>

- This bit cannot be cleared and can be set only when WREN = 1, and the unlock sequence has been performed. 1 = Initiates a Flash operation

- 0 = Flash operation is complete or inactive

#### bit 14 WREN: Write Enable bit<sup>(1)</sup>

- 1 = Enables writes to the WR bit and disables writes to the NVMOP<3:0> bits

- 0 = Disables writes to the WR bit and enables writes to the NVMOP<3:0> bits

#### bit 13 WRERR: Write Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

- 1 = Program or erase sequence did not complete successfully

- 0 = Program or erase sequence completed normally

#### bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1,2)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation. 1 = Low voltage is detected (possible data corruption if WRERR is set)

- 0 = Voltage level is acceptable for programming

- bit 11 Reserved: Maintain as '0'

- bit 10-4 Unimplemented: Read as '0'

- **Note 1:** These bits are only reset by a Power-on Reset (POR) and are not affected by other Reset sources.

- 2: These bits are cleared by setting NVMOP<3:0> = 0000 and initiating a Flash operation (i.e., WR).

- 3: NVMOP<3:0> bits are write-protected if the WREN bit is set.

- 4: Writes to the WR bit require an unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|--|

| 24.24        | U-0                       | U-0              |  |  |  |  |

| 31:24        | _                 | _                 |                   |                   | _                 | —                 | —                         | _                |  |  |  |  |

| 00.10        | U-0                       | U-0              |  |  |  |  |

| 23:16        | —                 | -                 | _                 |                   | _                 | —                 | —                         | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC               | R-0, HS, HC      |  |  |  |  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | S                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |  |  |

| 7.0          | R-0, HS, HC               | R-0, HS, HC      |  |  |  |  |

| 7:0          | SIRQ<7:0>         |                   |                   |                   |                   |                   |                           |                  |  |  |  |  |

#### REGISTER 7-3: INTSTAT: INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit        |                    |  |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-11 Unimplemented: Read as '0'

bit 10-8 **SRIPL<2:0>:** Requested Priority Level for Single Vector Mode bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

bit 7-0 SIRQ<7:0>: Last Interrupt Request Serviced Status bits 1111111-00000000 = The last interrupt request number serviced by the CPU

Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

#### REGISTER 7-4: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 IPTMR<31:0>: Interrupt Proximity Timer Reload bits

Used by the interrupt proximity timer as a reload value when the interrupt proximity timer is triggered by an interrupt event.

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

## 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

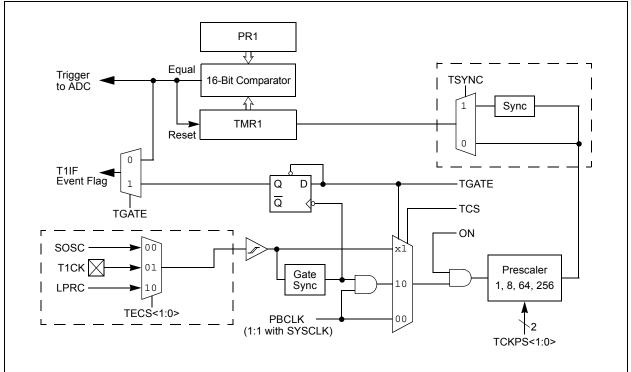

## 10.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0064GPL036 family devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can be clocked from different sources, such as the Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK), Secondary Oscillator (SOSC), T1CK pin or LPRC oscillator.

The following modes are supported by Timer1:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

The timer has a selectable clock prescaler and can operate in Sleep and Idle modes.

### FIGURE 10-1: TIMER1 BLOCK DIAGRAM

## 10.1 Timer1 Control Register

#### TABLE 10-1: TIMER1 REGISTER MAP

| ress<br>)                   | 20                              | e         | Bits         |       |       |       |       |       |      |       |        |      |      | ş      |      |       |      |      |           |

|-----------------------------|---------------------------------|-----------|--------------|-------|-------|-------|-------|-------|------|-------|--------|------|------|--------|------|-------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0000                        | TICON                           | 31:16     | -            | —     | _     | —     | -     | —     | _    | -     | —      | -    | -    | —      | —    | —     | —    | —    | 0000      |

| 8000                        | T1CON                           | 15:0      | ON           | —     | SIDL  | TWDIS | TWIP  | —     | TECS | <1:0> | TGATE  | _    | TCKP | S<1:0> | _    | TSYNC | TCS  | _    | 0000      |

| 8010                        | TMR1                            | 31:16     |              | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _      | _    | _     | _    | _    | 0000      |

| 8010                        |                                 | 15:0      |              |       |       |       |       |       |      | TMR1< | :15:0> |      |      |        |      |       |      |      | 0000      |

| 8020                        | PR1                             | 31:16     | _            | _     |       | _     | —     | _     |      | —     |        | —    | —    | —      |      | _     |      |      | 0000      |

| 0020                        | FKI                             | 15:0      | PR1<15:0> FF |       |       |       |       |       |      |       |        |      | FFFF |        |      |       |      |      |           |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

#### CCPxCON1: CAPTURE/COMPARE/PWMx CONTROL 1 REGISTER (CONTINUED) REGISTER 12-1:

bit 20-16 SYNC<4:0>: CCPx Synchronization Source Select bits

- 11111 = Timer is in the Free-Running mode and rolls over at FFFFh (Timer Period register is ignored) 11110 = Reserved . . . 11100 = Reserved 11011 = Time base is synchronized to the start of ADC conversion 11010 = Reserved 11001 = Time base is synchronized to Comparator 2 11000 = Time base is synchronized to Comparator 1 10111 = Reserved . . . 10010 = Reserved 10001 = Time base is synchronized to CLC2 10001 = Time base is synchronized to CLC1 01111 = Reserved 01110 = Reserved 01101 = Time base is synchronized to the INT4 pin (remappable) 01100 = Time base is synchronized to the INT3 pin 01011 = Time base is synchronized to the INT2 pin 01010 = Time base is synchronized to the INT1 pin 01001 = Time base is synchronized to the INTO pin 01000 = Reserved 00101 = Reserved 00100 = Time base is synchronized to SCCP3 00011 = Time base is synchronized to SCCP2 00010 = Time base is synchronized to MCCP1 00001 = Time base is synchronized to this MCCP/SCCP 00000 = No external synchronization; timer rolls over at FFFFh or matches with the Timer Period register ON: CCPx Module Enable bit<sup>(1)</sup> bit 15 1 = Module is enabled with the operating mode specified by the MOD<3:0> bits 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: CCPx Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12 CCPSLP: CCPx Sleep Mode Enable bit 1 = Module continues to operate in Sleep modes 0 = Module does not operate in Sleep modes bit 11 TMRSYNC: Time Base Clock Synchronization bit 1 = Module time base clock is synchronized to internal system clocks; timing restrictions apply 0 = Module time base clock is not synchronized to internal system clocks bit 10-8 CLKSEL<2:0>: CCPx Time Base Clock Select bits 111 = TCKIA pin (remappable) 110 = TCKIB pin (remappable) 101 = Reserved 100 = Reserved 011 = CLC1 output for MCCP1 and SCCP2/CLC2 output for SCCP3 010 = Secondary Oscillator (SOSC) clock 001 = REFCLKO output clock 000 = System clock (FSYS) Note 1: This control bit has no function in Input Capture modes.

- 2: This control bit has no function when TRIGEN = 0.

- 3: Values greater than '0011' will cause a FIFO buffer overflow in Input Capture mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0                             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | ALRMEN            | CHIME             | _                 | —                 | AMASK<3:0>                        |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ALMRPT            | <sup>-</sup> <7:0> <sup>(1)</sup> |                   |                  |                  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0                             | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | _                 | _                 | WRLOCK <sup>(2)</sup>             | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0                               | U-0               | U-0              | U-0              |

| 7:0          | RTCOE             | OE OUTSEL<2:0>    |                   |                   | _                                 | _                 | _                | _                |

#### REGISTER 15-1: RTCCON1: RTCC CONTROL 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31 ALRMEN: Alarm Enable bit

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 30 **CHIME:** Chime Enable bit

- 1 = Chime is enabled; ALMRPT<7:0> bits are allowed to underflow from '00' to 'FF'

- 0 = Chime is disabled; ALMRPT<7:0> bits stop once they reach '00'

#### bit 29-28 Unimplemented: Read as '0'

- bit 27-24 **AMASK<3:0>:** Alarm Mask Configuration bits

- 11xx = Reserved. do not use

- 101x = Reserved, do not use

- 1001 = Once a year (or once every 4 years when configured for February 29th)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half second

## bit 23-16 ALMRPT<7:0>: Alarm Repeat Counter Value bits<sup>(1)</sup>

11111111 = Alarm will repeat 255 more times

- 11111110 = Alarm will repeat 254 more times

- • •

- 00000010 = Alarm will repeat 2 more times

- 00000001 = Alarm will repeat 1 more time

- 00000000 = Alarm will not repeat

- bit 15 ON: RTCC Enable bit

- 1 = RTCC is enabled and counts from selected clock source

- 0 = RTCC is disabled

- bit 14-12 Unimplemented: Read as '0'

- **Note 1:** The counter decrements on any alarm event. The counter is prevented from rolling over from '00' to 'FF' unless CHIME = 1.

- 2: To clear this bit, an unlock sequence is required. Refer to Section 23.4 "System Registers Write Protection" for details.

#### REGISTER 18-1: CLCxCON: CLCx CONTROL REGISTER (CONTINUED)

- bit 5 **LCPOL:** CLCx Output Polarity Control bit 1 = The output of the module is inverted

- 0 = The output of the module is not inverted

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Cell is a 1-input transparent latch with S and R

- 110 = Cell is a JK flip-flop with R

- 101 = Cell is a 2-input D flip-flop with R

- 100 = Cell is a 1-input D flip-flop with S and R

- 011 = Cell is an SR latch

- 010 = Cell is a 4-input AND

- 001 = Cell is an OR-XOR

- 000 = Cell is a AND-OR

- Note 1: The INTP and INTN bits should not be set at the same time for proper interrupt functionality.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 |                   |                   | D                 | ACDAT<4:0>        |                  |                  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 15:8         | ON                | _                 | _                 | —                 | _                 | —                 | _                | DACOE            |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | REFSE            | EL<1:0>          |

#### REGISTER 20-1: DAC1CON: CDAC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

bit 20-16 **DACDAT<4:0>:** CDAC Voltage Reference Selection bits

11111 = (DACDAT<4:0> \* VREF+/32) or (DACDAT<4:0> \* AVDD/32) volts depending on the REFSEL<1:0> bits •

•

• 00000 = 0.0 volts

bit 15 **ON:** Voltage Reference Enable bit

- 1 = Voltage reference is enabled

- 0 = Voltage reference is disabled

#### bit 14-9 **Unimplemented:** Read as '0'

bit 8 DACOE: CDAC Voltage Reference Output Enable bit

- 1 = Voltage level is output on the CDAC1 pin

- 0 = Voltage level is disconnected from the CDAC1 pin

#### bit 7-2 Unimplemented: Read as '0'

- bit 1-0 REFSEL<1:0>: CDAC Voltage Reference Source Select bits

- 11 = Reference voltage is AVDD

- 10 = No reference is selected output is AVss

- 01 = Reference voltage is the VREF+ input pin voltage

- 00 = No reference is selected output is AVss

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                 | —                 | -                 | -                 | —                 | —                 | -                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | _                 |                   |                   | -                 | -                 |                  | _                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | —                 | _                 |                   |                   | -                 | -                 |                  | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 7:0          |                   |                   |                   |                   | LPBOREN           | RETVR             | BORE             | N<1:0>           |

#### REGISTER 23-3: FPOR/AFPOR: POWER-UP SETTINGS CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit |                                    |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

- bit 31-4 **Reserved:** Program as '1'

- bit 3 LPBOREN: Low-Power BOR Enable bit

- 1 = Low-Power BOR is enabled when the main BOR is disabled 0 = Low-Power BOR is disabled

- bit 2 **RETVR:** Retention Voltage Regulator Enable bit

- 1 = Retention regulator is disabled

- 0 = Retention regulator is enabled and controlled by the RETEN bit during Sleep

- bit 1-0 **BOREN<1:0>:** Brown-out Reset Enable bits

- 11 = Brown-out Reset is enabled in hardware; SBOREN bit is disabled

- 10 = Brown-out Reset is enabled only while device is active and is disabled in Sleep; SBOREN bit is disabled

- 01 = Brown-out Reset is controlled with the SBOREN bit setting

- 00 = Brown-out Reset is disabled in hardware; SBOREN bit is disabled

| <b>Operating Conditions:</b> $-40^{\circ}C < TA < +85^{\circ}C$ (unless otherwise stated) |                        |      |       |      |                 |  |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------|------|-------|------|-----------------|--|--|--|--|

| Parameter No.                                                                             | Typical <sup>(1)</sup> | Max  | Units | Vdd  | Conditions      |  |  |  |  |

| DC40                                                                                      | 0.26                   | 0.46 | mA    | 2.0V | — Fsys = 1 MHz  |  |  |  |  |

| DC40                                                                                      | 0.26                   | 0.46 | mA    | 3.3V |                 |  |  |  |  |

| 5044                                                                                      | 0.85                   | 1.5  | mA    | 2.0V |                 |  |  |  |  |

| DC41                                                                                      | 0.85                   | 1.5  | mA    | 3.3V | Fsys = 8 MHz    |  |  |  |  |

| DC 42                                                                                     | 2.3                    | 3.7  | mA    | 2.0V |                 |  |  |  |  |

| DC42                                                                                      | 2.3                    | 3.7  | mA    | 3.3V | Fsys = 25 MHz   |  |  |  |  |

| DC44                                                                                      | 0.18                   | 0.34 | mA    | 2.0V | – Fsys = 32 kHz |  |  |  |  |

| DC44                                                                                      | 0.18                   | 0.34 | mA    | 3.3V |                 |  |  |  |  |

## TABLE 26-5: IDLE CURRENT (IIDLE)<sup>(2)</sup>

**Note 1:** Data in the "Typical" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Base IIDLE current is measured with:

- Oscillator is configured in EC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 010 and POSCMOD<1:0> (FOSCSEL<9:8>) = 00)

- + OSC1 pin is driven with external square wave with levels from 0.3V to VDD 0.3V

- OSC2 is configured as I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- All I/O pins (excepting OSC1) are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

## TABLE 26-8: I/O PIN INPUT SPECIFICATIONS

| Operati      | <b>Dperating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                       |                    |                    |            |        |                                                   |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|--------------------|------------|--------|---------------------------------------------------|--|--|--|

| Param<br>No. | Symbol                                                                                                                  | Characteristic                                                        | Min                | Typ <sup>(1)</sup> | Мах        | Units  | Conditions                                        |  |  |  |

|              | VIL                                                                                                                     | Input Low Voltage <sup>(2)</sup>                                      |                    |                    |            |        |                                                   |  |  |  |

| DI10         |                                                                                                                         | I/O Pins with ST Buffer                                               | Vss                | _                  | 0.2 Vdd    | V      |                                                   |  |  |  |

| DI15         |                                                                                                                         | MCLR                                                                  | Vss                |                    | 0.2 VDD    | V      |                                                   |  |  |  |

| DI16         |                                                                                                                         | OSC1/CLKI (XT mode)                                                   | Vss                | _                  | 0.2 Vdd    | V      |                                                   |  |  |  |

| DI17         |                                                                                                                         | OSC1/CLKI (HS mode)                                                   | Vss                | —                  | 0.2 VDD    | V      |                                                   |  |  |  |

|              | Viн                                                                                                                     | Input High Voltage <sup>(2)</sup>                                     |                    |                    |            |        |                                                   |  |  |  |

| DI20         |                                                                                                                         | I/O Pins with ST Buffer:<br>without 5V Tolerance<br>with 5V Tolerance | 0.8 Vdd<br>0.8 Vdd |                    | Vdd<br>5.5 | V<br>V |                                                   |  |  |  |

| DI25         |                                                                                                                         | MCLR                                                                  | 0.8 Vdd            | _                  | Vdd        | V      |                                                   |  |  |  |

| DI26         |                                                                                                                         | OSCI/CLKI (XT mode)                                                   | 0.7 Vdd            |                    | Vdd        | V      |                                                   |  |  |  |

| DI27         |                                                                                                                         | OSC1/CLKI (HS mode)                                                   | 0.7 Vdd            | _                  | Vdd        | V      |                                                   |  |  |  |

| DI30         | ICNPU                                                                                                                   | CNPUx Pull-up Current                                                 | _                  | 350                | _          | μA     | VPIN = 0V, VDD = 3.3V                             |  |  |  |

| DI30A        | ICNPD                                                                                                                   | CNPDx Pull-Down Current                                               |                    | 300                | —          | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |

|              | lı∟                                                                                                                     | Input Leakage Current                                                 |                    |                    |            |        |                                                   |  |  |  |

| DI50         |                                                                                                                         | I/O Pins – 5V Tolerant                                                | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V,<br>pin at high-impedance |  |  |  |

| DI51         |                                                                                                                         | I/O Pins – Not 5V Tolerant                                            | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V,<br>pin at high-impedance |  |  |  |

| DI55         |                                                                                                                         | MCLR                                                                  | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |

| DI56         |                                                                                                                         | OSC1/CLKI                                                             | —                  | 0.1                | 1.0        | μA     | VPIN = 3.3V, VDD = 3.3V                           |  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Refer to Table 1-1 for I/O pin buffer types.

# PIC32MM0064GPL036 FAMILY

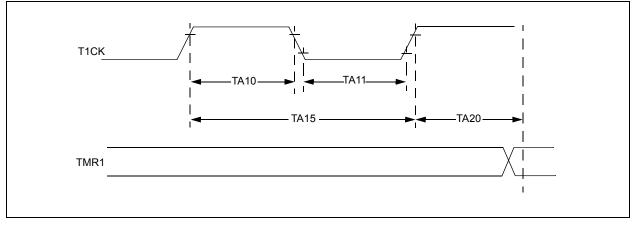

## FIGURE 26-5: TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

#### TABLE 26-23: MCCP/SCCP TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

| Operati       | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                           |                                |    |     |        |                               |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------|----|-----|--------|-------------------------------|--|--|--|--|

| Param.<br>No. | Symbol                                                                                                                  | Characte                                                  | Characteristics <sup>(1)</sup> |    | Max | Units  | Conditions                    |  |  |  |  |

| TA10          | Тскн                                                                                                                    | T1CK High Time                                            | Synchronous                    | 1  | _   | TPBCLK | Must also meet Parameter TA15 |  |  |  |  |

|               |                                                                                                                         |                                                           | Asynchronous                   | 10 | _   | ns     |                               |  |  |  |  |

| TA11          | TCKL                                                                                                                    | T1CK Low Time                                             | Synchronous                    | 1  | _   | TPBCLK | Must also meet Parameter TA15 |  |  |  |  |

|               |                                                                                                                         |                                                           | Asynchronous                   | 10 | _   | ns     |                               |  |  |  |  |

| TA15          | Тскр                                                                                                                    | T1CK Input                                                | Synchronous                    | 2  | _   | TPBCLK |                               |  |  |  |  |

|               | Period                                                                                                                  |                                                           | Asynchronous                   | 20 | _   | ns     |                               |  |  |  |  |

| TA20          | TCKEXTMRL                                                                                                               | Delay from External T1CK Clock<br>Edge to Timer Increment |                                |    | 3   | TPBCLK | Synchronous mode              |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

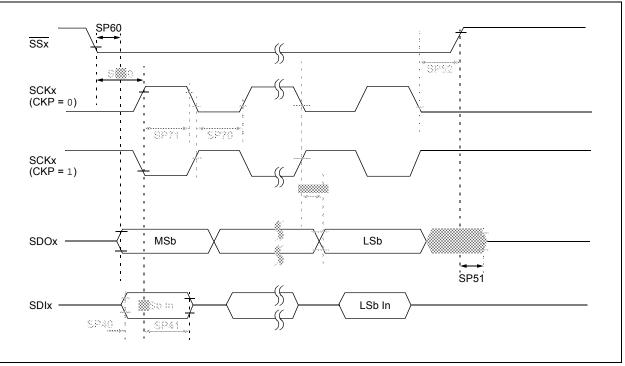

### FIGURE 26-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 26-29: SPIX MODULE SLAVE MODE TIMING REQUIREMENTS

| Operating | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                           |     |      |       |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|------|-------|--|--|--|--|--|

| Param.No. | Symbol                                                                                                                  | Characteristics <sup>(1)</sup>                                            | Min | Max  | Units |  |  |  |  |  |

| SP70      | TscL                                                                                                                    | SCKx Input Low Time                                                       | 10  |      | ns    |  |  |  |  |  |

| SP71      | TscH                                                                                                                    | SCKx Input High Time                                                      | 10  | —    | ns    |  |  |  |  |  |

| SP35      | TscH2doV,<br>TscL2doV                                                                                                   | SDOx Data Output Valid after SCKx Edge                                    | —   | 10   | ns    |  |  |  |  |  |

| SP40      | TDIV2scH,<br>TDIV2scL                                                                                                   | Setup Time of SDIx Data Input to SCKx Edge                                | 0   | —    | ns    |  |  |  |  |  |

| SP41      | TscH2diL,<br>TscL2diL                                                                                                   | Hold Time of SDIx Data Input to SCKx Edge                                 | 7   | —    | ns    |  |  |  |  |  |

| SP50      | TssL2scH,<br>TssL2scL                                                                                                   | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 40  | —    | ns    |  |  |  |  |  |

| SP51      | TssH2doZ                                                                                                                | SSx ↑ to SDOx Output High-Impedance                                       | 2.5 | 12   | ns    |  |  |  |  |  |

| SP52      | TscH2ssH<br>TscL2ssH                                                                                                    | SSx ↑ after SCKx Edge                                                     | 10  | _    | ns    |  |  |  |  |  |

| SP60      | TssL2doV                                                                                                                | SDOx Data Output Valid after SSx Edge                                     | —   | 12.5 | ns    |  |  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

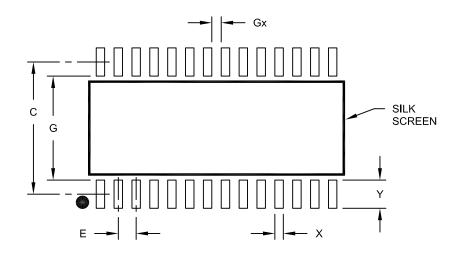

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units  |          |      |      |

|--------------------------|--------|----------|------|------|

| Dimension                | Limits | MIN      | NOM  | MAX  |

| Contact Pitch            | E      | 1.27 BSC |      |      |

| Contact Pad Spacing      | С      |          | 9.40 |      |

| Contact Pad Width (X28)  | X      |          |      | 0.60 |

| Contact Pad Length (X28) | Y      |          |      | 2.00 |

| Distance Between Pads    | Gx     | 0.67     |      |      |

| Distance Between Pads    | G      | 7.40     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A