#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 16                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 20-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl020-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                         | 13  |

|-------|-------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-Bit Microcontrollers             | 19  |

| 3.0   | CPU                                                                     |     |

| 4.0   | Memory Organization                                                     | 33  |

| 5.0   | Flash Program Memory                                                    |     |

| 6.0   | Resets                                                                  | 45  |

| 7.0   | CPU Exceptions and Interrupt Controller                                 | 51  |

| 8.0   | Oscillator Configuration                                                |     |

| 9.0   | I/O Ports                                                               | 77  |

| 10.0  | Timer1                                                                  |     |

| 11.0  | Watchdog Timer (WDT)                                                    |     |

| 12.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)                       |     |

| 13.0  | Serial Peripheral Interface (SPI) and Inter-IC Sound (I <sup>2</sup> S) |     |

| 14.0  | Universal Asynchronous Receiver Transmitter (UART)                      |     |

|       | Real-Time Clock and Calendar (RTCC)                                     |     |

|       | 12-Bit Analog-to-Digital Converter with Threshold Detect                |     |

| 17.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator             |     |

| 18.0  | Configurable Logic Cell (CLC)                                           |     |

| 19.0  | Comparator                                                              |     |

| 20.0  | Control Digital-to-Analog Converter (CDAC)                              |     |

| 21.0  | High/Low-Voltage Detect (HLVD)                                          |     |

| 22.0  | Power-Saving Features                                                   |     |

| 23.0  | Special Features                                                        |     |

| 24.0  | Development Support                                                     |     |

| 25.0  | Instruction Set                                                         |     |

| 26.0  | Electrical Characteristics                                              |     |

|       | Packaging Information                                                   |     |

|       | ndix A: Revision History                                                |     |

|       | ۲                                                                       |     |

|       | Vicrochip Web Site                                                      |     |

|       | omer Change Notification Service                                        |     |

|       | omer Support                                                            |     |

| Produ | uct Identification System                                               | 265 |

# **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,   |

|-------|-----------------------------------------|

|       | browse the documentation section of the |

|       | Microchip web site (www.microchip.com). |

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 60. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS60001336)

- Section 62. "Dual Watchdog Timer" (DS60001365)

|          |               |                | Pin                    | Number                        |                |                |             |                |                                      |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                          |

| PGEC1    | 2             | 5              | 2                      | 5                             | 36             | 39             | Ι           | ST             | ICSP Port 1 programming clock input  |

| PGEC2    | 19            | 2              | 19                     | 22                            | 25             | 28             | I           | ST             | ICSP Port 2 programming clock input  |

| PGEC3    | 7             | 10             | 12                     | 15                            | 16             | 16             | I           | ST             | ICSP Port 3 programming clock input  |

| PGED1    | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | ICSP Port 1 programming data         |

| PGED2    | 20            | 3              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | ICSP Port 2 programming data         |

| PGED3    | 6             | 9              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | ICSP Port 3 programming data         |

| PWRLCLK  | 7             | 10             | 9                      | 12                            | 10             | 10             | I           | ST             | Real-Time Clock 50/60 Hz clock input |

| RA0      | 19            | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA1      | 20            | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA2      | 4             | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA3      | 5             | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA4      | 7             | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA9      | _             | _              | _                      | _                             | 11             | 11             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RB0      | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB1      | 2             | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB2      | 3             | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB3      | _             |                | 4                      | 7                             | 2              | 2              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB4      | 6             | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB5      | _             | _              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB6      | _             |                | 12                     | 15                            | 16             | 16             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB7      | 8             | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB8      | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB9      | 10            | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB10     | _             | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB11     | _             | _              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB12     | 12            | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB13     | 13            | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB14     | 14            | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB15     | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RC0      | —             | _              | _                      | _                             | 3              | 3              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC1      | _             | _              | _                      | _                             | 4              | 4              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC2      | _             | _              | —                      | —                             | 5              | 5              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC3      | —             | _              | _                      | _                             | 14             | 14             | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC8      | _             | _              | _                      | _                             | 20             | 21             | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC9      | _             | _              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         | PORTC digital I/O                    |

| REFCLKI  | 10            | 13             | 15                     | 18                            | 19             | 20             | I           | ST             | Reference clock input                |

| REFCLKO  | 15            | 18             | 23                     | 26                            | 29             | 32             | 0           | DIG            | Reference clock output               |

| Legend:  | ST = Sc       | hmitt Tric     | ger input              | buffer                        | DIG = Dig      | nital innu     | t/output    |                | ANA = Analog level input/output      |

#### **TABLE 1-1:** PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

# 3.2 Architecture Overview

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC microprocessor core in the PIC32MM0064GPL036 family devices contains several logic blocks, working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Power Management

- microMIPS Instructions Decoder

- Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous Multiply/ Divide Unit (MDU). The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port, and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid Stalls when executing instruction streams where data producing instructions are followed closely by consumers for their results

- Leading zero/one detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The microAptiv UC core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows the long-running MDU operations to be partially masked by system Stalls and/or other Integer Unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, Result/Accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the rs operand. The second number ('16' of 32x16) represents the rt operand. The microAptiv UC core only checks the value of the rt operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back, 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU. Divide operations are implemented with a simple 1-bit-per-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (rs) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16-bit wide rs, 15 iterations are skipped, and for a 24-bit wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline Stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be re-issued), and latency (number of cycles until a result is available) for the microAptiv UC core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL (GPR destination)   | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

#### TABLE 3-1: MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Register<br>Number | Register<br>Name                                                                                   | Function                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3                | Reserved                                                                                           | Reserved in the microAptiv™ UC.                                                                                                                                                               |

| 4                  | UserLocal                                                                                          | User information that can be written by privileged software and read via RDHWR, Register 29.                                                                                                  |

| 5-6                | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 7                  | HWREna                                                                                             | Enables access via the RDHWR instruction to selected hardware registers in Non-Privileged mode.                                                                                               |

| 8                  | BadVAddr <sup>(1)</sup>                                                                            | Reports the address for the most recent address related exception.                                                                                                                            |

| 9                  | Count <sup>(1)</sup>                                                                               | Processor cycle count.                                                                                                                                                                        |

| 10                 | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 11                 | Compare <sup>(1)</sup>                                                                             | Timer interrupt control.                                                                                                                                                                      |

| 12                 | Status/<br>IntCtl/<br>SRSCtl/<br>SRSMap1/<br>View_IPL/<br>SRSMAP2                                  | Processor status and control; interrupt control and shadow set control.                                                                                                                       |

| 13                 | Cause <sup>(1)</sup> /<br>View_RIPL                                                                | Cause of last exception.                                                                                                                                                                      |

| 14                 | EPC <sup>(1)</sup>                                                                                 | Program Counter at last exception.                                                                                                                                                            |

| 15                 | PRId/<br>EBase/<br>CDMMBase                                                                        | Processor identification and revision; exception base address; Common Device Memory Map Base register.                                                                                        |

| 16                 | CONFIG/<br>CONFIG1/<br>CONFIG2/<br>CONFIG3/<br>CONFIG7                                             | Configuration registers.                                                                                                                                                                      |

| 7-22               | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 23                 | Debug/<br>Debug2/<br>TraceControl/<br>TraceControl2/<br>UserTraceData1/<br>TraceBPC <sup>(2)</sup> | EJTAG Debug register.<br>EJTAG Debug Register 2.<br>EJTAG Trace Control register.<br>EJTAG Trace Control Register 2.<br>EJTAG User Trace Data 1 register.<br>EJTAG Trace Breakpoint register. |

| 24                 | DEPC <sup>(2)</sup> /<br>UserTraceData2                                                            | Program Counter at last debug exception.<br>EJTAG User Trace Data 2 register.                                                                                                                 |

| 25                 | PerfCtl0/<br>PerfCnt0/<br>PerfCtl1/<br>PerfCnt1                                                    | Performance Counter 0 control.<br>Performance Counter 0.<br>Performance Counter 1 control.<br>Performance Counter 1.                                                                          |

| 26                 | ErrCtl                                                                                             | Software parity check enable.                                                                                                                                                                 |

| 27                 | CacheErr                                                                                           | Records information about SRAM parity errors.                                                                                                                                                 |

| 28-29              | Reserved                                                                                           | Reserved in the PIC32 core.                                                                                                                                                                   |

| 30                 | ErrorEPC <sup>(1)</sup>                                                                            | Program Counter at last error.                                                                                                                                                                |

| 31                 | DeSAVE <sup>(2)</sup>                                                                              | Debug Handler Scratchpad register.                                                                                                                                                            |

### TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used in debug.

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| CpU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | _                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          |                    |                                                                            |                |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                  | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | 31:24 — — — IP3<2:0> |                   |                   |                   |                   |                   | IS3<             | 1:0>             |  |

| 00.40        | U-0                  | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                    | _                 | _                 |                   | IP2<2:0>          | · IS2<1:0>        |                  |                  |  |

| 45.0         | U-0                  | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                    | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |  |

| 7.0          | U-0                  | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                    | _                 | _                 |                   | IP0<2:0>          | IS0<1:0>          |                  |                  |  |

### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 =Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

#### bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

#### bit 23-21 Unimplemented: Read as '0'

- bit 20-18 **IP2<2:0>:** Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

# 9.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

Many of the device pins are shared among the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. Some pins in the devices are 5V tolerant pins. Some of the key features of the I/O ports are:

- Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change-in-Pin State is Detected

- Operation during Sleep and Idle modes

- Fast Bit Manipulation using the CLR, SET and INV registers

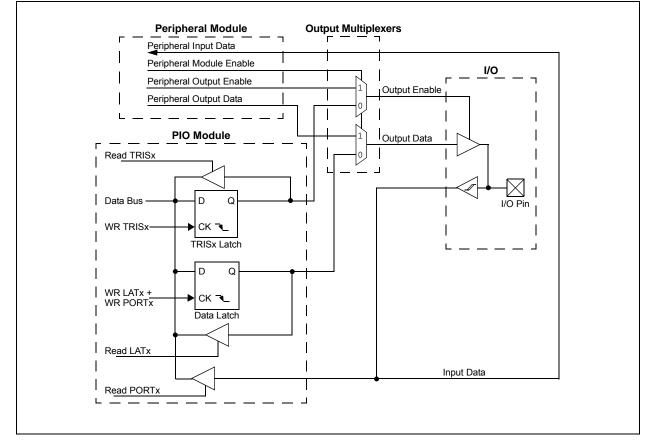

Figure 9-1 illustrates a block diagram of a typical multiplexed I/O port.

#### FIGURE 9-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

# REGISTER 10-1: T1CON: TIMER1 CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer1 External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit

- 1 = External clock is defined by the TECS<1:0> bits

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

# 11.1 Watchdog Timer Control Registers

# TABLE 11-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | ø         |       | Bits                 |                                                  |       |       |       |      |      |      |      | s    |      |      |      |      |      |           |

|---------------------------|-----------------------|-----------|-------|----------------------|--------------------------------------------------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14                | 29/13                                            | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 2500                      | WDTCON <sup>(1)</sup> | 31:16     |       | WDTCLRKEY<15:0> 0000 |                                                  |       |       |       |      |      |      |      |      |      |      |      |      |      |           |

| 3E80                      | WDICON                | 15:0      | ON    |                      | RUNDIV<4:0> CLKSEL<1:0> SLPDIV<4:0> WDTWINEN xx: |       |       |       |      |      |      | xxxx |      |      |      |      |      |      |           |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range                | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04                       | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 31:24                       |                   |                   |                   | WDTCLF            | RKEY<15:8>        |                   |                  |                  |

| 00.40                       | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 23:16                       |                   |                   |                   | WDTCL             | RKEY<7:0>         |                   |                  |                  |

| 45.0                        | R/W-0             | U-0               | U-0               | R-y               | R-y               | R-y               | R-y              | R-y              |

| 15:8                        | ON <sup>(1)</sup> | —                 | _                 |                   |                   | RUNDIV<4:0        | >                |                  |

| 7.0                         | R-y               | R-y               | R-y               | R-y               | R-y               | R-y               | R-y              | R/W-y            |

| 7:0 CLKSEL<1:0> SLPDIV<4:0> |                   |                   |                   |                   |                   |                   |                  | WDTWINEN         |

# REGISTER 11-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Con | y = Values set from Configuration bits on Reset          |  |  |  |  |  |  |

|-------------------|-------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit        | W = Writable bit U = Unimplemented bit, read as '0'      |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |  |  |  |  |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits

To clear the Watchdog Timer to prevent a time-out, software must write the value, 0x5743, to this location using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = The WDT is enabled

0 = The WDT is disabled

bit 14-13 Unimplemented: Read as '0'

bit 12-8 **RUNDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RWDTPS<4:0> Configuration bits in FWDT.

- bit 7-6 **CLKSEL<1:0>:** Shadow Copy of Watchdog Timer Clock Selection Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RCLKSEL<1:0> Configuration bits in FWDT.

- bit 5-1 **SLPDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Sleep/Idle Mode from Configuration bits On Reset, these bits are set to the values of the SWDTPS<4:0> Configuration bits in FWDT.

# bit 0 WDTWINEN: Watchdog Timer Window Enable bit On Reset, this bit is set to the value of the WINDIS Configuration bit in FWDT. 1 = Windowed mode is enabled

0 = Windowed mode is disabled

Note 1: This bit only has control when FWDTEN (FWDT<15>) = 0.

# REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

# REGISTER 13-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when the CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                 |

| 31:24        | _                 | —                 | _                 | -                 | —                 | —                 | -                | _                   |

| 00.40        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0               |

| 23:16        | SLPEN             | ACTIVE            | _                 | _                 | —                 | CLKSE             | L<1:0>           | OVFDIS              |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0               |

| 15:8         | ON                | —                 | SIDL              | IREN              | RTSMD             | —                 | UEN<             | 1:0> <sup>(1)</sup> |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |

|              | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL               |

#### REGISTER 14-1: UXMODE: UARTX MODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

- bit 23 **SLPEN:** Run During Sleep Enable bit

- 1 = UARTx clock runs during Sleep

- 0 = UARTx clock is turned off during Sleep

#### bit 22 ACTIVE: UARTx Running Status bit

- 1 = UARTx is active (UxMODE register shouldn't be updated)

- 0 = UARTx is not active (UxMODE register can be updated)

- bit 21-19 Unimplemented: Read as '0'

#### bit 18-17 CLKSEL<1:0>: UARTx Clock Selection bits

- 11 = The UARTx clock is the Reference Clock Output (REFCLKO)

- 10 = The UARTx clock is the FRC oscillator clock

- 01 = The UARTx clock is the SYSCLK

- 00 = The UARTx clock is the PBCLK (1:1 with SYSCLK)

- bit 16 **OVFDIS:** Run During Overflow Condition Mode bit

- 1 = When an Overflow Error (OERR) condition is detected, the Shift register continues to run to remain synchronized

- 0 = When an Overflow Error (OERR) condition is detected, the Shift register stops accepting new data (Legacy mode)

#### bit 15 **ON:** UARTx Enable bit

- 1 = UARTx is enabled; UARTx pins are controlled by UARTx, as defined by the UEN<1:0> and UTXEN control bits

- UARTx is disabled; all UARTx pins are controlled by the corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: UARTx Stop in Idle Mode bit

- 1 = Discontinues operation when device enters Idle mode

- 0 = Continues operation in Idle mode

- bit 12 IREN: IrDA<sup>®</sup> Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- Note 1: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ADRC              | EXTSAM            | _                 |                   |                   | SAMC<4:0>         |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ADCS<7:0>         |                   |                   |                   |                   |                   |                  |                  |

# REGISTER 16-3: AD1CON3: ADC CONTROL REGISTER 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source (TSRC) bit

- 1 = Clock derived from Fast RC (FRC) oscillator

- 0 = Clock derived from Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK)

#### bit 14 EXTSAM: Extended Sampling Time bit

- 1 = ADC is still sampling after SAMP bit = 0

- 0 = ADC stops sampling when SAMP bit = 0

- bit 13 Unimplemented: Read as '0'

- bit 12-8 SAMC<4:0>: Auto-Sample Time bits

11111 **= 31 T**AD

- •

- .

- 00001 = 1 TAD

00000 = 0 TAD (Not allowed)

# bit 7-0 ADCS<7:0>: ADC Conversion Clock Select bits

- 11111111 = 2 TSRC ADCS<7:0> = 510 TSRC = TAD

- •

- .

00000001 = 2 • TSRC • ADCS<7:0> = 2 • TSRC = TAD 00000000 = 1 • TSRC = TAD

Where TSRC is a period of clock selected by the ADRC bit (AD1CON3<15>).

# 18.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCON

- CLCxSEL

- CLCxGLS

The CLCx Control register (CLCxCON) is used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select register (CLCxGLS) allows the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

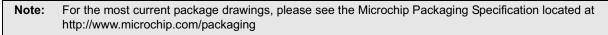

# 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                               | MILLIMETERS      |      |          |      |  |  |

|-------------------------------|------------------|------|----------|------|--|--|

| Dimensior                     | Dimension Limits |      |          | MAX  |  |  |

| Contact Pitch                 | Contact Pitch E  |      | 0.50 BSC |      |  |  |

| Optional Center Pad Width     | W2               |      |          | 2.50 |  |  |

| Optional Center Pad Length T2 |                  |      |          | 2.50 |  |  |

| Contact Pad Spacing C1        |                  |      | 3.93     |      |  |  |

| Contact Pad Spacing           | C2               |      | 3.93     |      |  |  |

| Contact Pad Width             | X1               |      |          | 0.30 |  |  |

| Contact Pad Length            | Y1               |      |          | 0.73 |  |  |

| Distance Between Pads G       |                  | 0.20 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

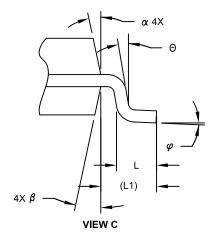

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimensior                | MIN         | NOM       | MAX |      |  |

| Number of Pins           | N           |           | 28  |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | A           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5 Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x1.0mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS          |                |          |      |  |

|-------------------------|----------------------|----------------|----------|------|--|

| Dimensior               | Dimension Limits     |                | NOM      | MAX  |  |

| Number of Terminals     | N                    |                | 36       |      |  |

| Pitch                   | е                    |                | 0.50 BSC |      |  |

| Overall Height          | Α                    | 0.80           | 0.90     | 1.00 |  |

| Standoff                | A1                   | 0.00           | 0.02     | 0.05 |  |

| Terminal Thickness      | A3                   | 0.20 REF       |          |      |  |

| Overall Width           | all Width E 6.00 BSC |                |          |      |  |

| Exposed Pad Width       | E2                   | 3.60 3.70 3.80 |          |      |  |

| Overall Length          | D                    |                | 6.00 BSC |      |  |

| Exposed Pad Length      | D2                   | 3.60           | 3.70     | 3.80 |  |

| Terminal Width          | b                    | 0.18           | 0.25     | 0.30 |  |

| Terminal Length         |                      | 0.50           | 0.60     | 0.75 |  |

| Terminal-to-Exposed-Pad | K                    | 0.45           | 0.55     | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-272B-M2 Sheet 2 of 2

NOTES: