Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 16                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 20-QFN (4x4)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl020-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC32MM0064GPL036 FAMILY

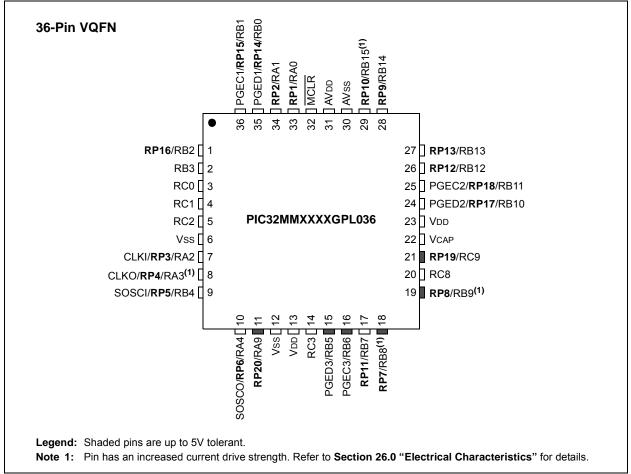

#### Pin Diagrams (Continued)

#### TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN VQFN DEVICES

| Pin | Function                                            | Pin | Function                                                                       |

|-----|-----------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                         | 19  | TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | AN11/C1INA/RB3                                      | 20  | RC8                                                                            |

| 3   | AN12/RC0                                            | 21  | RP19/RC9                                                                       |

| 4   | AN13/RC1                                            | 22  | VCAP                                                                           |

| 5   | RC2                                                 | 23  | VDD                                                                            |

| 6   | Vss                                                 | 24  | PGED2/TDO/ <b>RP17</b> /RB10                                                   |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                         | 25  | PGEC2/TDI/ <b>RP18</b> /RB11                                                   |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 26  | AN7/LVDIN/ <b>RP12</b> /RB12                                                   |

| 9   | SOSCI/ <b>RP5</b> /RB4                              | 27  | AN8/ <b>RP13</b> /RB13                                                         |

| 10  | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                | 28  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                          |

| 11  | <b>RP20</b> /RA9                                    | 29  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>            |

| 12  | Vss                                                 | 30  | AVss                                                                           |

| 13  | Vdd                                                 | 31  | AVDD                                                                           |

| 14  | RC3                                                 | 32  | MCLR                                                                           |

| 15  | PGED3/RB5                                           | 33  | VREF+/AN0/RP1/OCM1E/INT3/RA0                                                   |

| 16  | PGEC3/RB6                                           | 34  | Vref-/AN1/ <b>RP2</b> /OCM1F/RA1                                               |

| 17  | <b>RP11</b> /RB7                                    | 35  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                                        |

| 18  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>         | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                                        |

Note 1: Pin has an increased current drive strength.

|          |               | Pin Number     |                        |                               |                |                |             |                |                                      |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                          |

| PGEC1    | 2             | 5              | 2                      | 5                             | 36             | 39             | Ι           | ST             | ICSP Port 1 programming clock input  |

| PGEC2    | 19            | 2              | 19                     | 22                            | 25             | 28             | I           | ST             | ICSP Port 2 programming clock input  |

| PGEC3    | 7             | 10             | 12                     | 15                            | 16             | 16             | I           | ST             | ICSP Port 3 programming clock input  |

| PGED1    | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | ICSP Port 1 programming data         |

| PGED2    | 20            | 3              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | ICSP Port 2 programming data         |

| PGED3    | 6             | 9              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | ICSP Port 3 programming data         |

| PWRLCLK  | 7             | 10             | 9                      | 12                            | 10             | 10             | I           | ST             | Real-Time Clock 50/60 Hz clock input |

| RA0      | 19            | 2              | 27                     | 2                             | 33             | 36             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA1      | 20            | 3              | 28                     | 3                             | 34             | 37             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA2      | 4             | 7              | 6                      | 9                             | 7              | 7              | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA3      | 5             | 8              | 7                      | 10                            | 8              | 8              | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA4      | 7             | 10             | 9                      | 12                            | 10             | 10             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RA9      | _             | _              | _                      | _                             | 11             | 11             | I/O         | ST/DIG         | PORTA digital I/O                    |

| RB0      | 1             | 4              | 1                      | 4                             | 35             | 38             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB1      | 2             | 5              | 2                      | 5                             | 36             | 39             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB2      | 3             | 6              | 3                      | 6                             | 1              | 1              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB3      | _             |                | 4                      | 7                             | 2              | 2              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB4      | 6             | 9              | 8                      | 11                            | 9              | 9              | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB5      | _             | _              | 11                     | 14                            | 15             | 15             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB6      | _             |                | 12                     | 15                            | 16             | 16             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB7      | 8             | 11             | 13                     | 16                            | 17             | 17             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB8      | 9             | 12             | 14                     | 17                            | 18             | 18             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB9      | 10            | 13             | 15                     | 18                            | 19             | 20             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB10     | _             | —              | 18                     | 21                            | 24             | 27             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB11     | _             | _              | 19                     | 22                            | 25             | 28             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB12     | 12            | 15             | 20                     | 23                            | 26             | 29             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB13     | 13            | 16             | 21                     | 24                            | 27             | 30             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB14     | 14            | 17             | 22                     | 25                            | 28             | 31             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RB15     | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | PORTB digital I/O                    |

| RC0      | —             | _              | _                      | _                             | 3              | 3              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC1      | _             | _              | _                      | _                             | 4              | 4              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC2      | _             | _              | —                      | —                             | 5              | 5              | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC3      | —             | _              | _                      | _                             | 14             | 14             | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC8      | _             | _              | _                      | _                             | 20             | 21             | I/O         | ST/DIG         | PORTC digital I/O                    |

| RC9      | _             | _              | 16                     | 19                            | 21             | 22             | I/O         | ST/DIG         | PORTC digital I/O                    |

| REFCLKI  | 10            | 13             | 15                     | 18                            | 19             | 20             | I           | ST             | Reference clock input                |

| REFCLKO  | 15            | 18             | 23                     | 26                            | 29             | 32             | 0           | DIG            | Reference clock output               |

| Legend:  | ST = Sc       | hmitt Tric     | ger input              | buffer                        | DIG = Dig      | nital innu     | t/output    |                | ANA = Analog level input/output      |

#### **TABLE 1-1:** PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MM0064GPL036 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Capacitor on Internal Voltage Regulator (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Register<br>Number | Register<br>Name                                                                                   | Function                                                                                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3                | Reserved                                                                                           | Reserved in the microAptiv™ UC.                                                                                                                                                               |

| 4                  | UserLocal                                                                                          | User information that can be written by privileged software and read via RDHWR, Register 29.                                                                                                  |

| 5-6                | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 7                  | HWREna                                                                                             | Enables access via the RDHWR instruction to selected hardware registers in Non-Privileged mode.                                                                                               |

| 8                  | BadVAddr <sup>(1)</sup>                                                                            | Reports the address for the most recent address related exception.                                                                                                                            |

| 9                  | Count <sup>(1)</sup>                                                                               | Processor cycle count.                                                                                                                                                                        |

| 10                 | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 11                 | Compare <sup>(1)</sup>                                                                             | Timer interrupt control.                                                                                                                                                                      |

| 12                 | Status/<br>IntCtl/<br>SRSCtl/<br>SRSMap1/<br>View_IPL/<br>SRSMAP2                                  | Processor status and control; interrupt control and shadow set control.                                                                                                                       |

| 13                 | Cause <sup>(1)</sup> /<br>View_RIPL                                                                | Cause of last exception.                                                                                                                                                                      |

| 14                 | EPC <sup>(1)</sup>                                                                                 | Program Counter at last exception.                                                                                                                                                            |

| 15                 | PRId/<br>EBase/<br>CDMMBase                                                                        | Processor identification and revision; exception base address; Common Device Memory Map Base register.                                                                                        |

| 16                 | CONFIG/<br>CONFIG1/<br>CONFIG2/<br>CONFIG3/<br>CONFIG7                                             | Configuration registers.                                                                                                                                                                      |

| 7-22               | Reserved                                                                                           | Reserved in the microAptiv UC.                                                                                                                                                                |

| 23                 | Debug/<br>Debug2/<br>TraceControl/<br>TraceControl2/<br>UserTraceData1/<br>TraceBPC <sup>(2)</sup> | EJTAG Debug register.<br>EJTAG Debug Register 2.<br>EJTAG Trace Control register.<br>EJTAG Trace Control Register 2.<br>EJTAG User Trace Data 1 register.<br>EJTAG Trace Breakpoint register. |

| 24                 | DEPC <sup>(2)</sup> /<br>UserTraceData2                                                            | Program Counter at last debug exception.<br>EJTAG User Trace Data 2 register.                                                                                                                 |

| 25                 | PerfCtl0/<br>PerfCnt0/<br>PerfCtl1/<br>PerfCnt1                                                    | Performance Counter 0 control.<br>Performance Counter 0.<br>Performance Counter 1 control.<br>Performance Counter 1.                                                                          |

| 26                 | ErrCtl                                                                                             | Software parity check enable.                                                                                                                                                                 |

| 27                 | CacheErr                                                                                           | Records information about SRAM parity errors.                                                                                                                                                 |

| 28-29              | Reserved                                                                                           | Reserved in the PIC32 core.                                                                                                                                                                   |

| 30                 | ErrorEPC <sup>(1)</sup>                                                                            | Program Counter at last error.                                                                                                                                                                |

| 31                 | DeSAVE <sup>(2)</sup>                                                                              | Debug Handler Scratchpad register.                                                                                                                                                            |

#### TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used in debug.

#### 7.2 Interrupts

The PIC32MM0064GPL036 family uses fixed offset for vector spacing. For details, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*. Table 7-2 provides the interrupt related vectors and bits information.

|--|

|                           |                                     | Vector | I        | Persistent |                        |             |           |

|---------------------------|-------------------------------------|--------|----------|------------|------------------------|-------------|-----------|

| Interrupt Source          | MPLAB <sup>®</sup> XC32 Vector Name | Number | Flag     | Enable     | e Priority Subpriority |             | Interrupt |

| Core Timer                | _CORE_TIMER_VECTOR                  | 0      | IFS0<0>  | IEC0<0>    | IPC0<4:2>              | IPC0<1:0>   | No        |

| Core Software 0           | _CORE_SOFTWARE_0_VECTOR             | 1      | IFS0<1>  | IEC0<1>    | IPC0<12:10>            | IPC0<9:8>   | No        |

| Core Software 1           | _CORE_SOFTWARE_1_VECTOR             | 2      | IFS0<2>  | IEC0<2>    | IPC0<20:18>            | IPC0<17:16> | No        |

| External 0                | _external_0_vector                  | 3      | IFS0<3>  | IEC0<3>    | IPC0<28:26>            | IPC0<25:24> | No        |

| External 1                | _external_1_vector                  | 4      | IFS0<4>  | IEC0<4>    | IPC1<4:2>              | IPC1<1:0>   | No        |

| External 2                | _EXTERNAL_2_VECTOR                  | 5      | IFS0<5>  | IEC0<5>    | IPC1<12:10>            | IPC1<9:8>   | No        |

| External 3                | _EXTERNAL_3_VECTOR                  | 6      | IFS0<6>  | IEC0<6>    | IPC1<20:18>            | IPC1<17:16> | No        |

| External 4                | _EXTERNAL_4_VECTOR                  | 7      | IFS0<7>  | IEC0<7>    | IPC1<28:26>            | IPC1<25:24> | No        |

| PORTA Change Notification | _CHANGE_NOTICE_A_VECTOR             | 8      | IFS0<8>  | IEC0<8>    | IPC2<4:2>              | IPC2<1:0>   | No        |

| PORTB Change Notification | _CHANGE_NOTICE_B_VECTOR             | 9      | IFS0<9>  | IEC0<9>    | IPC2<12:10>            | IPC2<9:8>   | No        |

| PORTC Change Notification | _CHANGE_NOTICE_C_VECTOR             | 10     | IFS0<10> | IEC0<10>   | IPC2<20:18>            | IPC2<17:16> | No        |

| Timer1                    | _TIMER_1_VECTOR                     | 11     | IFS0<11> | IEC0<11>   | IPC2<28:26>            | IPC2<25:24> | No        |

| Comparator 1              | _COMPARATOR_1_VECTOR                | 12     | IFS0<12> | IEC0<12>   | IPC3<4:2>              | IPC3<1:0>   | No        |

| Comparator 2              | _COMPARATOR_2_VECTOR                | 13     | IFS0<13> | IEC0<13>   | IPC3<12:10>            | IPC3<9:8>   | No        |

| Real-Time Clock Alarm     | _RTCC_VECTOR                        | 14     | IFS0<14> | IEC0<14>   | IPC3<20:18>            | IPC3<17:16> | No        |

| ADC Conversion            | _ADC_VECTOR                         | 15     | IFS0<15> | IEC0<15>   | IPC3<28:26>            | IPC3<25:24> | No        |

| CRC                       | _CRC_VECTOR                         | 16     | IFS0<16> | IEC0<16>   | IPC4<4:2>              | IPC4<1:0>   | Yes       |

| High/Low-Voltage Detect   | _HLVD_VECTOR                        | 17     | IFS0<17> | IEC0<17>   | IPC4<12:10>            | IPC4<9:8>   | Yes       |

| Logic Cell 1              | _CLC1_VECTOR                        | 18     | IFS0<18> | IEC0<18>   | IPC4<20:18>            | IPC4<17:16> | No        |

| Logic Cell 2              | _CLC2_VECTOR                        | 19     | IFS0<19> | IEC0<19>   | IPC4<28:26>            | IPC4<25:24> | No        |

| SPI1 Error                | _SPI1_ERR_VECTOR                    | 20     | IFS0<20> | IEC0<20>   | IPC5<4:2>              | IPC5<1:0>   | Yes       |

| SPI1 Transmission         | _SPI1_TX_VECTOR                     | 21     | IFS0<21> | IEC0<21>   | IPC5<12:10>            | IPC5<9:8>   | Yes       |

| SPI1 Reception            | _SPI1_RX_VECTOR                     | 22     | IFS0<22> | IEC0<22>   | IPC5<20:18>            | IPC5<17:16> | Yes       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | —                 |                   | IP3<2:0>          |                   | IS3<             | 1:0>             |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | _                 | _                 |                   | IP2<2:0>          |                   | IS2<             | 1:0>             |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |

#### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x<sup>(1)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 =Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

#### bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

#### bit 23-21 Unimplemented: Read as '0'

- bit 20-18 **IP2<2:0>:** Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- **Note 1:** This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

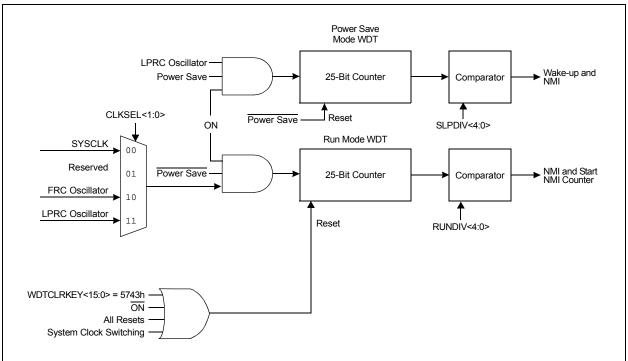

#### 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1           | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|------------------------|-------------------|-------------------|----------------------------|------------------|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | U-0               | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 31:24     | OETRIG            |                   | OSCNT<2:0>        | •                      | -                 | (                 | OUTM<2:0> <sup>(1</sup>    | )                |  |  |

| 00.40     | U-0               | U-0               | R/W-0             | R/W-0                  | R/W-0             | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 23:16     | —                 | —                 | POLACE            | POLBDF <sup>(1)</sup>  | PSSACE<1:0>       |                   | PSSBDF<1:0> <sup>(1)</sup> |                  |  |  |

| 45.0      | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0                        | U-0              |  |  |

| 15:8      | —                 | —                 | -                 | —                      | -                 | —                 | -                          | —                |  |  |

| 7.0       | U-0               | U-0               | R/W-0             | R/W-0                  | R/W-0             | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 7:0       | _                 | —                 |                   | DT<5:0> <sup>(1)</sup> |                   |                   |                            |                  |  |  |

#### REGISTER 12-3: CCPxCON3: CAPTURE/COMPARE/PWMx CONTROL 3 REGISTER

| 1    |      |

|------|------|

| i ea | end: |

|      |      |

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|           | <ul> <li>1 = For Triggered mode (TRIGEN = 1), the module does not drive enabled output pins until triggered</li> <li>0 = Normal output pin operation</li> </ul>                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-28 | OSCNT<2:0>: One-Shot Event Count bits                                                                                                                                                                                                                                                                                                                                                                |

|           | Extends the duration of a one-shot trigger event by an additional n clock cycles (n+1 total cycles).<br>111 = 7 timer count periods (8 cycles total)<br>110 = 6 timer count periods (7 cycles total)<br>101 = 5 timer count periods (6 cycles total)<br>100 = 4 timer count periods (5 cycles total)<br>011 = 3 timer count periods (4 cycles total)<br>010 = 2 timer count periods (3 cycles total) |

001 = 1 timer count period (2 cycles total)

**OETRIG:** PWM Dead-Time Select bit

000 = Does not extend the one-shot trigger event (the event takes 1 timer count period)

- bit 27 Unimplemented: Read as '0'

- bit 26-24 OUTM<2:0>: PWMx Output Mode Control bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Output Scan mode

- 101 = Brush DC Output mode, forward

- 100 = Brush DC Output mode, reverse

- 011 = Reserved

- 010 = Half-Bridge Output mode

- 001 = Push-Pull Output mode

- 000 = Steerable Single Output mode

- bit 23-22 Unimplemented: Read as '0'

```

bit 21 POLACE: CCPx Output Pins, OCxA, OCxC and OCxE, Polarity Control bit

```

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

- bit 20 **POLBDF:** CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit<sup>(1)</sup>

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

```

bit 19-18 PSSACE<1:0>: PWMx Output Pins, OCxA, OCxC and OCxE, Shutdown State Control bits

```

- 11 = Pins are driven active when a shutdown event occurs

- ${\tt 10}$  = Pins are driven inactive when a shutdown event occurs

- 0x = Pins are in a high-impedance state when a shutdown event occurs

- **Note 1:** These bits are implemented in MCCP modules only.

#### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 24.04        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31:24        | _                    |                   | _                 | —                 | —                        | _                 |                  | _                       |

| 00.40        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23:16        | —                    | _                 | —                 | —                 | —                        | _                 | —                | _                       |

| 45.0         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 15:8         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| = 0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   | —                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### REGISTER 13-2: SPIxCON2: SPIx CONTROL REGISTER 2

#### Legend:

| 0                 |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15        | <b>SPISGNEXT:</b> SPIx Sign-Extend Read Data from the RX FIFO bit<br>1 = Data from RX FIFO is sign-extended                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 0 = Data from RX FIFO is not sign-extended                                                                                                                                       |

| bit 14-13     | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 12        | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                                                                 |

|               | <ul><li>1 = Frame error overflow generates error events</li><li>0 = Frame error does not generate error events</li></ul>                                                         |

| bit 11        | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                                                                 |

|               | <ul><li>1 = Receive Overflow (ROV) generates error events</li><li>0 = Receive Overflow does not generate error events</li></ul>                                                  |

| bit 10        | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                                                                 |

|               | <ul><li>1 = Transmit Underrun (TUR) generates error events</li><li>0 = Transmit Underrun does not generate error events</li></ul>                                                |

| bit 9         | IGNROV: Ignore Receive Overflow (ROV) bit (for audio data transmissions)                                                                                                         |

|               | 1 = A ROV is not a critical error; during ROV, data in the FIFO is not overwritten by receive data<br>0 = A ROV is a critical error which stops SPIx operation                   |

| bit 8         | IGNTUR: Ignore Transmit Underrun (TUR) bit (for audio data transmissions)                                                                                                        |

|               | <ul> <li>1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty</li> <li>0 = A TUR is a critical error which stops SPIx operation</li> </ul> |

| bit 7         | AUDEN: Enable Audio Codec Support bit <sup>(1)</sup>                                                                                                                             |

|               | <ul><li>1 = Audio protocol is enabled</li><li>0 = Audio protocol is disabled</li></ul>                                                                                           |

| bit 6-4       | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 3         | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                                                         |

|               | <ul><li>1 = Audio data is mono (each data word is transmitted on both left and right channels)</li><li>0 = Audio data is stereo</li></ul>                                        |

| bit 2         | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 1-0       | AUDMOD<1:0>: Audio Protocol Mode bits <sup>(1,2)</sup><br>11 = PCM/DSP mode<br>10 = Right Justified mode<br>01 = Left Justified mode<br>00 = I <sup>2</sup> S mode               |

| Note 1:<br>2: | These bits can only be written when the ON bit = $0$ .<br>These bits are only valid for AUDEN = $1$ .                                                                            |

**2:** These bits are only valid for AUDEN = 1.

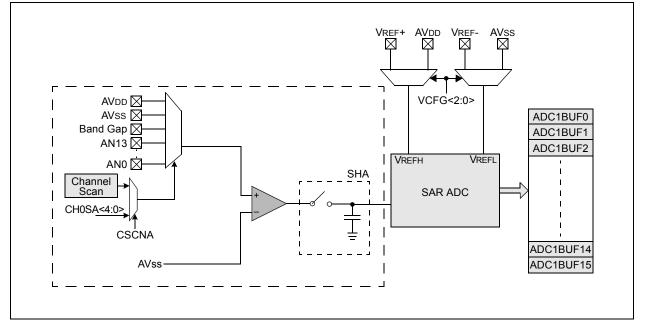

#### 16.0 12-BIT ANALOG-TO-DIGITAL CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

#### 16.1 Introduction

The 12-bit ADC Converter with Threshold Detect includes the following features:

- Successive Approximation Register (SAR)

Conversion

- · User-Selectable Resolution of 10 or 12 Bits

- Conversion Speeds of up to 200 ksps for 12-bit mode and 300 ksps for 10-bit mode

- Up to 17 Analog Inputs (internal and external)

#### FIGURE 16-1: ADC BLOCK DIAGRAM

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold Amplifier (SHA)

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length Configurable Conversion Result

Buffer

- · Eight Options for Result Alignment and Encoding

- Configurable Interrupt Generation

- · Operation during CPU Sleep and Idle modes

Figure 16-1 illustrates a block diagram of the 12-bit ADC. The 12-bit ADC has 14 external analog inputs, AN0 through AN13, and 3 internal analog inputs connected to VDD, VSs and band gap. In addition, there are two analog input pins for external voltage reference connections.

The analog inputs are connected through a multiplexer to the SHA. Unipolar differential conversions are possible on all inputs (see Figure 16-1).

The Automatic Input Scan mode sequentially converts multiple analog inputs. A special control register specifies which inputs will be included in the scanning sequence. The 12-bit ADC is connected to a 16-word result buffer. The 12-bit result is converted to one of eight output formats in either 32-bit or 16-bit word widths.

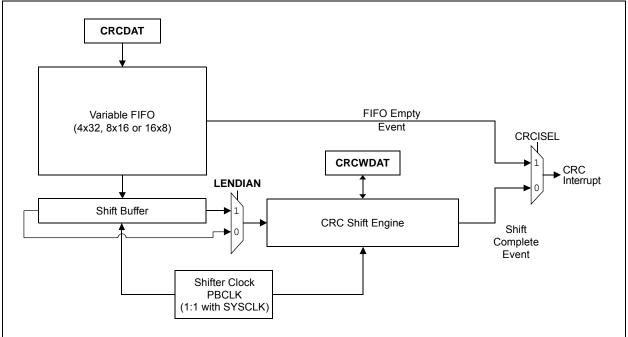

#### 17.0 32-BIT PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 60. "32-Bit Programmable Cyclic Redundancy Check" (DS60001336) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. The 32-bit programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-Programmable CRC Polynomial Equation, up to 32 Bits

- Programmable Shift Direction (little or big-endian)

- Independent Data and Polynomial Lengths

- Configurable Interrupt Output

- Data FIFO

Figure 17-1 displays a simplified block diagram of the CRC generator.

#### FIGURE 17-1: CRC BLOCK DIAGRAM

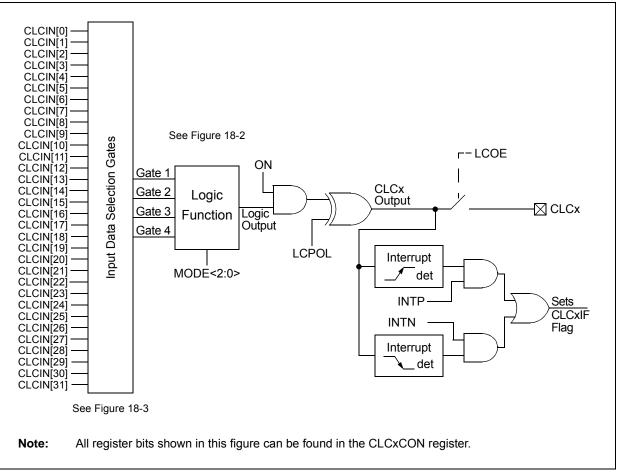

#### 18.0 CONFIGURABLE LOGIC CELL (CLC)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 36. "Configurable Logic Cell" (DS60001363) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

FIGURE 18-1: CLCx MODULE

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flex-ibility and potential in embedded designs since the CLC module can operate outside the limitations of software execution, and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 18-1 shows an overview of the module. Figure 18-3 shows the details of the data source multiplexers and logic input gate connections.

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (CONTINUED)

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin and is compared with 1.2V band gap) 1110 = VDD trip point is  $2.11V^{(1)}$

- 1101 = VDD trip point is  $2.21V^{(1)}$

- 1100 = VDD trip point is 2.30V<sup>(1)</sup>

- 1011 = VDD trip point is 2.40V<sup>(1)</sup>

- 1010 = VDD trip point is  $2.52V^{(1)}$

- 1001 = VDD trip point is 2.63V<sup>(1)</sup>

- $1000 = \text{VDD trip point is } 2.82\text{V}^{(1)}$

- 0111 = VDD trip point is  $2.92V^{(1)}$

- $0110 = VDD trip point is <math>3.13V^{(1)}$

- 0101 = VDD trip point is  $3.44V^{(1)}$

- 0100-0000 = Reserved; do not use

- Note 1: The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in Section 26.0 "Electrical Characteristics" for minimum and maximum values.

#### 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

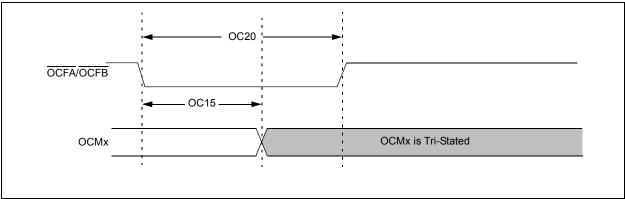

#### TABLE 26-27: MCCP AND SCCP PWM MODE TIMING REQUIREMENTS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |        |                                |     |     |       |  |

|-------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|-----|-----|-------|--|

| Param<br>No.                                                                                                            | Symbol | Characteristics <sup>(1)</sup> | Min | Max | Units |  |

| OC15                                                                                                                    | Tfd    | Fault Input to PWM I/O Change  | _   | 30  | ns    |  |

| OC20                                                                                                                    | TFLT   | Fault Input Pulse Width        | 10  |     | ns    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

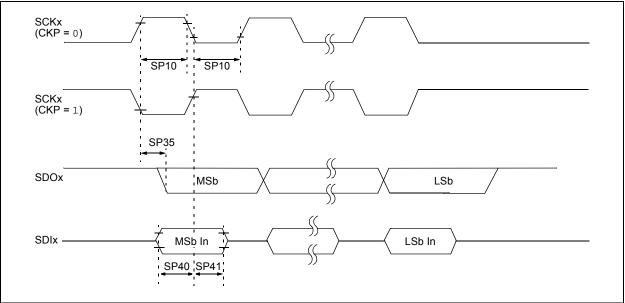

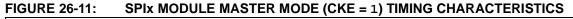

#### FIGURE 26-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

## 27.0 PACKAGING INFORMATION

### 27.1 Package Marking Information

20-Lead SSOP

Example PIC32MM0016 GPL020 \$ 1610017 ()

20-Lead QFN

# Example 32MM0016 GPL020 1610017

#### 28-Lead SPDIP

#### 28-Lead SOIC (7.5 mm)

Example

#### Example

| Legend: | XXX                                           | Customer-specific information                                                                                                                                               |  |  |

|---------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | YY Year code (last 2 digits of calendar year) |                                                                                                                                                                             |  |  |

|         | WW Week code (week of January 1 is week '01') |                                                                                                                                                                             |  |  |

|         | NNN Alphanumeric traceability code            |                                                                                                                                                                             |  |  |

|         | *                                             | All packages are Pb-free                                                                                                                                                    |  |  |

| ł       | be carrie                                     | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information. |  |  |

| CCPxCON3 (Capture/Compare/PWMx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CCPxSTAT (Capture/Compare/PWMx Status) 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CFGCON (Configuration Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLCxCON (CLCx Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLCxGLS (CLCx Gate Logic Input Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLCxSEL (CLCx Input MUX Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLKSTAT (Clock Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CMSTAT (Comparator Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CMxCON (Comparator x Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNCONx (Change Notification Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| for PORTx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CONFIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |