#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 16                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 11x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 20-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl020t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

# 2.1 Basic Connection Requirements

Getting started with the PIC32MM0064GPL036 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Capacitor on Internal Voltage Regulator (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|---------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R/W-1                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | PWPULOCK                  | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |  |  |

| 00.40        | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | PWP<23:16> <sup>(2)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | PWP<15:8> <sup>(2)</sup>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                           |                   |                   | PWP<7             | ′:0> <b>(2)</b>   |                   |                  |                  |  |  |  |  |

#### NVMPWP: NVM PROGRAM FLASH WRITE-PROTECT REGISTER<sup>(1)</sup> **REGISTER 5-6:**

# Lonond

| Legena:           |                  |                                         |  |  |  |  |

|-------------------|------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 31 PWPULOCK: Program Flash Memory Page Write-Protect Unlock bit

- 1 = Register is not locked and can be modified

- 0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any Reset.

- bit 30-24 Unimplemented: Read as '0'

- bit 23-0 PWP<23:0>: Flash Program Write-Protect (Page) Address bits<sup>(2)</sup>

Physical memory below address, 0x1DXXXXXX, is write-protected, where 'XXXXXX' is specified by PWP<23:0>. When the PWP<23:0> bits have a value of '0', write protection is disabled for the entire Program Flash Memory. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

- Note 1: Writes to this register require an NVMKEY unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

- 2: These bits can be modified only when the unlock bit (PWPULOCK) is set.

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| CpU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | _                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          |                    |                                                                            |                |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

# 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

# 9.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

Many of the device pins are shared among the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. Some pins in the devices are 5V tolerant pins. Some of the key features of the I/O ports are:

- Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change-in-Pin State is Detected

- Operation during Sleep and Idle modes

- Fast Bit Manipulation using the CLR, SET and INV registers

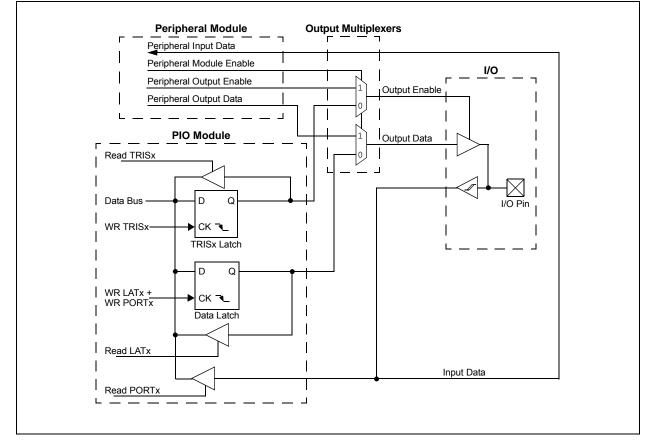

Figure 9-1 illustrates a block diagram of a typical multiplexed I/O port.

### FIGURE 9-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

# TABLE 9-6: PORTC REGISTER MAP

| DS60001324B-pa |

|----------------|

| age            |

| 84             |

| ess                         |                                 | <b>n</b>  | Bits              |       |       |       |                        |       |        |                      |      |      |      |      |      |         |                    |                       |               |

|-----------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|------------------------|-------|--------|----------------------|------|------|------|------|------|---------|--------------------|-----------------------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2    | 17/1               | 16/0                  | All<br>Resets |

| 2800                        | ANSELC                          | 31:16     | _                 | _     | _     | _     | _                      | _     |        | _                    |      | _    | _    | -    | —    | _       |                    | _                     | 0000          |

|                             |                                 | 15:0      | —                 | _     | _     | _     |                        |       | _      | _                    | —    |      |      | _    |      | _       | ANSC<              | 1:0> <sup>(1,2)</sup> | 0003          |

| 2810                        | TRISC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| -0.0                        |                                 | 15:0      | _                 | —     | —     | _     | _                      | _     | TRISC  | :9:8> <b>(1,2)</b>   | —    | _    | —    | _    |      | TRISC<  | 3:0> <b>(1,2)</b>  |                       | 030F          |

| 2820                        | PORTC                           | 31:16     | _                 | —     | —     | _     | _                      | _     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2020                        | TORTO                           | 15:0      | —                 |       |       |       | _                      | _     | RC<9   | :8> <sup>(1,2)</sup> | —    | _    |      | _    |      | RC<3:   | 0> <b>(1,2)</b>    |                       | 0000          |

| 2830                        | LATC                            | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | —    | —    | —    | —    | —       | —                  | —                     | 0000          |

| 2000                        | EATO                            | 15:0      | —                 |       |       |       | _                      | _     | LATC<  | 9:8> <b>(1,2)</b>    | —    | _    |      | _    |      | LATC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2840                        | ODCC                            | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 20 <del>4</del> 0           | 0200                            | 15:0      | —                 |       |       |       | _                      | _     | ODCC<  | :9:8> <b>(1,2)</b>   | —    | _    |      | _    |      | ODCC<   | 3:0> <b>(1,2)</b>  |                       | 0000          |

| 2850                        | CNPUC                           | 31:16     | —                 |       |       |       | _                      | _     | _      | _                    | —    | _    |      | _    |      | _       | _                  | —                     | 0000          |

| 2000                        |                                 | 15:0      | —                 | —     | —     | —     | _                      | _     | CNPUC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPUC   | <3:0>(1,2)         |                       | 0000          |

| 2860                        | CNPDC                           | 31:16     | —                 | —     | —     | _     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | -                  | —                     | 0000          |

| 2000                        | CINFDC                          | 15:0      | —                 | —     | —     | —     | —                      | —     | CNPDC  | <9:8>(1,2)           | —    | _    | —    | _    |      | CNPDC<  | <3:0> <b>(1,2)</b> |                       | 0000          |

| 2870                        | CNCONC                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2070                        | CINCOINC                        | 15:0      | ON <sup>(1)</sup> | —     | —     | —     | CNSTYLE <sup>(1)</sup> | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2880                        | CNEN0C                          | 31:16     | —                 | —     | —     | —     | —                      | —     | —      | —                    | —    | _    | —    | _    | —    | —       | —                  | —                     | 0000          |

| 2000                        | CINEINUC                        | 15:0      | _                 | —     | —     | —     | _                      | _     | CNIE0C | <9:8>(1,2)           | —    |      | _    |      |      | CNIE0C4 | <3:0>(1,2)         |                       | 0000          |

| 2890                        | CNSTATC -                       | 31:16     | _                 | —     | —     | —     | _                      | _     | _      | —                    | —    |      | _    |      | —    | _       |                    | _                     | 0000          |

| 2090                        | CINGTATE                        | 15:0      | —                 | —     | —     | —     | _                      | _     | CNSTAT | C<9:8>(1,2)          | —    | —    | —    |      |      | CNSTATO | <3:0>(1,2)         |                       | 0000          |

| 28A0                        | CNEN1C                          | 31:16     | _                 | -     | _     | -     | -                      | _     | _      | —                    | —    | _    | _    | I    | _    | -       |                    | _                     | 0000          |

| 2040                        | CINENTO                         | 15:0      | _                 | -     | -     | -     | —                      | _     | CNIE1C | <9:8>(1,2)           | _    |      |      |      |      | CNIE1C  | <3:0>(1,2)         |                       | 0000          |

| 28B0                        | CNFC                            | 31:16     | _                 | -     | —     | -     | —                      | _     | —      | —                    | —    |      |      |      | _    | —       | _                  | —                     | 0000          |

| 20BU                        | CINFC                           | 15:0      | _                 | —     | —     | —     | _                      | _     | CNFC<  | :9:8> <b>(1,2)</b>   | _    |      |      |      |      | CNFC<   | 3:0>(1,2)          |                       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **Note 1:** Bits<15,11,9:8,3:0> are not implemented in 20-pin devices.

**2:** Bits<8,3:0> are not implemented in 28-pin devices.

3: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

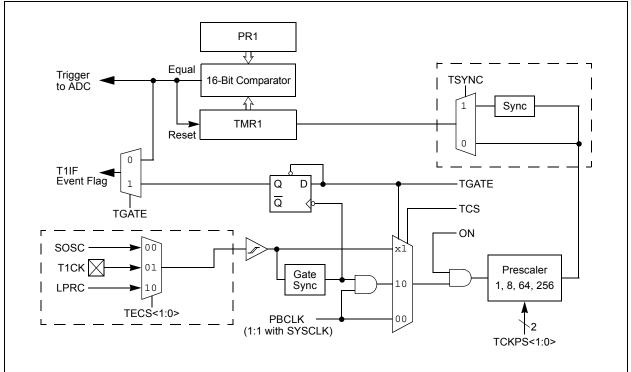

# 10.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0064GPL036 family devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can be clocked from different sources, such as the Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK), Secondary Oscillator (SOSC), T1CK pin or LPRC oscillator.

The following modes are supported by Timer1:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

The timer has a selectable clock prescaler and can operate in Sleep and Idle modes.

# FIGURE 10-1: TIMER1 BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON                | —                 | SIDL              | TWDIS             | TWIP              | —                 | TECS             | i<1:0>           |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | —                 | TSYNC             | TCS              | _                |

### REGISTER 10-1: T1CON: TIMER1 CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer1 On bit

- 1 = Timer1 is enabled

- 0 = Timer1 is disabled

### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Timer1 Stop in Idle Mode bit

- 1 = Discontinues operation when device enters Idle mode

- 0 = Continues operation even in Idle mode

### bit 12 TWDIS: Asynchronous Timer1 Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer mode functionality)

### bit 11 **TWIP:** Asynchronous Timer1 Write in Progress bit

- In Asynchronous Timer1 mode:

- $\ensuremath{\mathtt{1}}$  = Asynchronous write to TMR1 register is in progress

- 0 = Asynchronous write to TMR1 register is complete

In Synchronous Timer1 mode:

This bit is read as '0'.

- bit 10 Unimplemented: Read as '0'

- bit 9-8 **TECS<1:0>:** Timer1 External Clock Selection bits

- 11 = Reserved

- 10 = External clock comes from the LPRC

- 01 = External clock comes from the T1CK Pin

- 00 = External clock comes from the Secondary Oscillator (SOSC)

## bit 7 TGATE: Timer1 Gated Time Accumulation Enable bit

When TCS = 1:

This bit is ignored.

### When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

# bit 6 Unimplemented: Read as '0'

- bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

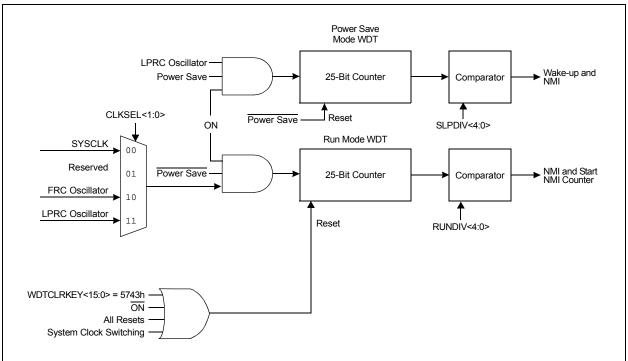

# 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

# REGISTER 12-4: CCPxSTAT: CAPTURE/COMPARE/PWMx STATUS REGISTER (CONTINUED)

| bit 3 | SCEVT: Single Edge Compare Event Status bit                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = A single edge compare event has occurred                                                                                                               |

|       | 0 = A single edge compare event has not occurred                                                                                                           |

| bit 2 | ICDIS: Input Capture Disable bit                                                                                                                           |

|       | <ul> <li>1 = Event on input capture pin does not generate a capture event</li> <li>0 = Event on input capture pin will generate a capture event</li> </ul> |

| bit 1 | ICOV: Input Capture Buffer Overflow Status bit                                                                                                             |

|       | 1 = The input capture FIFO buffer has overflowed                                                                                                           |

|       | 0 = The input capture FIFO buffer has not overflowed                                                                                                       |

| bit 0 | ICBNE: Input Capture Buffer Status bit                                                                                                                     |

|       | 1 = The input capture buffer has data available                                                                                                            |

|       | 0 = The input capture buffer is empty                                                                                                                      |

Note 1: This is not a physical bit location and will always read as '0'. A write of '1' will initiate the hardware event.

#### **SPI Control Registers** 13.1

# TABLE 13-1: SPI1 AND SPI2 REGISTER MAP

| SSS                         |                                 |           |            |         |        |          |          |            |          | Bits      |         |        |        |        |         |          |        |         |            |

|-----------------------------|---------------------------------|-----------|------------|---------|--------|----------|----------|------------|----------|-----------|---------|--------|--------|--------|---------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15      | 30/14   | 29/13  | 28/12    | 27/11    | 26/10      | 25/9     | 24/8      | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2     | 17/1   | 16/0    | All Resets |

| 8080                        | SPI1CON                         | 31:16     | FRMEN      | FRMSYNC | FRMPOL | MSSEN    | FRMSYPW  | FR         | MCNT<2:0 | >         | MCLKSEL | -      | _      | I      | _       | I        | SPIFE  | ENHBUF  | 0000       |

| 0000                        | SPIICON                         | 15:0      | ON         | —       | SIDL   | DISSDO   | MODE32   | MODE16     | SMP      | CKE       | SSEN    | CKP    | MSTEN  | DISSDI | STXISEL | <1:0>    | SRXIS  | EL<1:0> | 0000       |

| 8090                        | SPI1STAT                        | 31:16     | _          | _       | _      |          | RXBL     | JFELM<4:0> |          |           |         |        |        |        | TXBL    | JFELM<4: | 0>     |         | 0000       |

| 0090                        | SFIISTAL                        | 15:0      | _          | _       | _      | FRMERR   | SPIBUSY  |            |          | SPITUR    | SRMT    | SPIROV | SPIRBE |        | SPITBE  |          | SPITBF | SPIRBF  | 0008       |

| 80A0                        | SPI1BUF                         | 31:16     | DATA<31:0> |         |        |          |          |            |          |           |         |        |        |        | 0000    |          |        |         |            |

| 0040                        |                                 | 15:0      | DAIA<51.02 |         |        |          |          |            |          |           |         |        |        |        | 0000    |          |        |         |            |

| 80B0                        | SPI1BRG                         | 31:16     | _          | _       | _      |          | —        | _          |          | —         | _       | _      | —      | _      | —       | —        | _      | —       | 0000       |

| 0000                        | or fibrio                       | 15:0      | —          | —       | —      |          |          |            |          |           | BRG     | <12:0> |        |        |         |          |        |         | 0000       |

| 8000                        | SPI1CON2                        | 31:16     | —          | —       | —      | —        | —        | —          | —        | —         | —       | —      | —      | —      | —       | —        | —      | —       | 0000       |

| 0000                        | 011100112                       | 15:0      | SPISGNEXT  | _       | _      | FRMERREN | SPIROVEN | SPITUREN   | IGNROV   | IGNTUR    | AUDEN   | _      | —      |        | AUDMONO | _        | AUDMO  | OD<1:0> | 0000       |

| 8100                        | SPI2CON                         | 31:16     | FRMEN      | FRMSYNC | FRMPOL | MSSEN    | FRMSYPW  | FR         | MCNT<2:0 | >         | MCLKSEL | _      | —      |        | _       | —        | SPIFE  | ENHBUF  | 0000       |

| 0100                        | 01 120011                       | 15:0      | ON         | —       | SIDL   | DISSDO   | MODE32   | MODE16     | SMP      | CKE       | SSEN    | CKP    | MSTEN  | DISSDI | STXISEL | <1:0>    | SRXIS  | EL<1:0> | 0000       |

| 8110                        | SPI2STAT                        | 31:16     | _          | _       | _      |          | RXBL     | JFELM<4:0> |          |           |         | _      | —      |        | TXBL    | JFELM<4: | 0>     |         | 0000       |

| 0110                        | 01 120 17 11                    | 15:0      | —          | —       | —      | FRMERR   | SPIBUSY  | —          | —        | SPITUR    | SRMT    | SPIROV | SPIRBE | —      | SPITBE  | —        | SPITBF | SPIRBF  | 0008       |

| 8120                        | SPI2BUF                         | 31:16     |            |         |        |          |          |            | D        | ATA<31:0> |         |        |        |        |         |          |        |         | 0000       |

| 0120                        |                                 | 15:0      |            |         |        |          |          |            |          |           |         |        |        |        |         |          |        |         | 0000       |

| 8130                        | SPI2BRG                         | 31:16     | _          | —       | —      |          | —        | —          | —        | —         | —       | —      | —      | —      | —       | —        | —      | —       | 0000       |

| 0.00                        |                                 | 15:0      | —          | —       | —      |          |          |            |          |           | BRG     | <12:0> |        |        |         |          |        |         | 0000       |

| 8140                        | SPI2CON2                        | 31:16     | _          | _       | _      | _        | —        | —          | _        | —         | _       | _      | —      | _      | _       | _        |        | _       | 0000       |

| 3110                        | 5. 1200N2                       | 15:0      | SPISGNEXT  | —       | —      | FRMERREN | SPIROVEN | SPITUREN   | IGNROV   | IGNTUR    | AUDEN   | —      | —      | _      | AUDMONO | —        | AUDMO  | OD<1:0> | 0000       |

PIC32MM0064GPL036 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table, except SPIxBUF, have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

# REGISTER 13-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

### bit 2 Unimplemented: Read as '0'

### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

### Enhanced Buffer mode:

Set when the CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   | HRTEN<2:0>        |                   | HRONE<3:0>        |                   |                  |                  |  |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 |                   | MINTEN<2:0>       | >                 | MINONE<3:0>       |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | SECTE             | EN<3:0>           |                   | SECONE<3:0>       |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

### REGISTER 15-4: RTCTIME/ALMTIME: RTCC/ALARM TIME REGISTERS

### Legend:

| 3                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31 Unimplemented: Read as '0'

- bit 30-28 **HRTEN<2:0>:** Binary Coded Decimal Value of Hours 10-Digit bits Contains a value from 0 to 2.

- bit 27-24 **HRONE<3:0>:** Binary Coded Decimal Value of Hours 1-Digit bits Contains a value from 0 to 9.

- bit 23 Unimplemented: Read as '0'

- bit 22-20 **MINTEN<2:0>:** Binary Coded Decimal Value of Minutes 10-Digit bits Contains a value from 0 to 5.

- bit 19-16 **MINONE<3:0>:** Binary Coded Decimal Value of Minutes 1-Digit bits Contains a value from 0 to 9.

- bit 15-12 **SECTEN<3:0>:** Binary Coded Decimal Value of Seconds 10-Digit bits Contains a value from 0 to 5.

- bit 11-8 **SECONE<3:0>:** Binary Coded Decimal Value of Seconds 1-Digit bits Contains a value from 0 to 9.

- bit 7-0 Unimplemented: Read as '0'

# PIC32MM0064GPL036 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5          | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------|-------------------|----------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0                | R/W-0             | R/W-0                      | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | 31:24 — CSS<30:28> |                   |                            |                   | _                 | _                 | _                | _                |  |

| 00.40        | U-0                | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                  | _                 | _                          | _                 | _                 | _                 | _                | —                |  |

| 45.0         | U-0                | U-0               | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                  | —                 | CSS<13:8> <sup>(1,2)</sup> |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0              | R/W-0             | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                    | CSS<7:0>          |                            |                   |                   |                   |                  |                  |  |

# REGISTER 16-6: AD1CSS: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31 Unimplemented: Read as '0'

bit 30-28 CSS<30:28>: ADC Input Pin Scan Selection bits

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- bit 27-14 Unimplemented: Read as '0'

- bit 13-0 CSS<13:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

- 1 = Selects ANx for the input scan

- 0 = Skips ANx for the input scan

- Note 1: The CSS<13:11> bits are not implemented in 20-pin devices.

- **2:** The CSS<13:12> bits are not implemented in 28-pin devices.

# REGISTER 23-8: DEVID: DEVICE ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|--|

| 04.04        | R-x                      | R-x               | R-x               | R-x               | R-x                      | R-x               | R-x              | R-x              |  |

| 31:24        | VER<3:0> <sup>(1)</sup>  |                   |                   |                   | ID<27:24> <sup>(1)</sup> |                   |                  |                  |  |

| 00.40        | R-x                      | R-x               | R-x               | R-x               | R-x                      | R-x               | R-x              | R-x              |  |

| 23:16        | ID<23:16> <sup>(1)</sup> |                   |                   |                   |                          |                   |                  |                  |  |

| 45.0         | R-x                      | R-x               | R-x               | R-x               | R-x                      | R-x               | R-x              | R-x              |  |

| 15:8         | ID<15:8> <sup>(1)</sup>  |                   |                   |                   |                          |                   |                  |                  |  |

| 7.0          | R-x                      | R-x               | R-x               | R-x               | R-x                      | R-x               | R-x              | R-x              |  |

| 7:0          |                          |                   |                   | ID<7:(            | <sub>)&gt;</sub> (1)     |                   |                  |                  |  |

| Legend: | L | eg | er | ۱d | : |

|---------|---|----|----|----|---|

|---------|---|----|----|----|---|

.

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID bits<sup>(1)</sup>

Note 1: Reset values are dependent on the device variant.

### REGISTER 23-9: SYSKEY: SYSTEM UNLOCK REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | W-0                 | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 31:24        | 31:24 SYSKEY<31:24> |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | W-0                 | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 23:16        | SYSKEY<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | W-0                 | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 15:8         | SYSKEY<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | W-0                 | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 7:0          | SYSKEY<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 SYSKEY<31:0>: Unlock and Lock Key bits

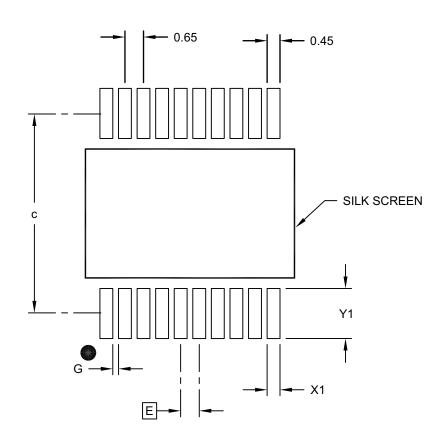

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |      |          |      |

|--------------------------|------------------|------|----------|------|

| Dimensio                 | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X20)  | X1               |      |          | 0.45 |

| Contact Pad Length (X20) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B

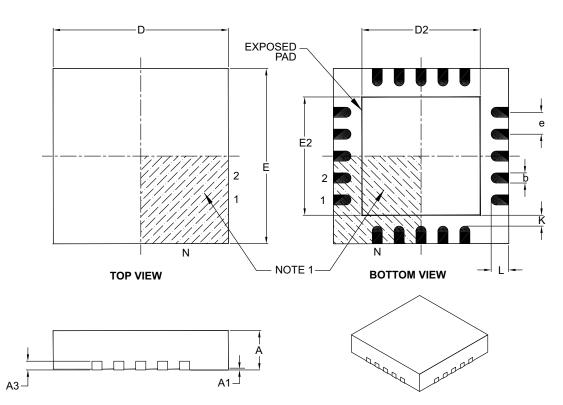

# 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS | 5    |

|------------------------|------------------|----------|-------------|------|

|                        | Dimension Limits | MIN      | NOM         | MAX  |

| Number of Pins         | N                |          | 20          |      |

| Pitch                  | е                |          | 0.50 BSC    |      |

| Overall Height         | А                | 0.80     | 0.90        | 1.00 |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |

| Contact Thickness      | A3               | 0.20 REF |             |      |

| Overall Width          | E                | 4.00 BSC |             |      |

| Exposed Pad Width      | E2               | 2.60     | 2.70        | 2.80 |

| Overall Length         | D                |          | 4.00 BSC    |      |

| Exposed Pad Length     | D2               | 2.60     | 2.70        | 2.80 |

| Contact Width          | b                | 0.18     | 0.25        | 0.30 |

| Contact Length         | L                | 0.30     | 0.40        | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20 – – |             |      |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

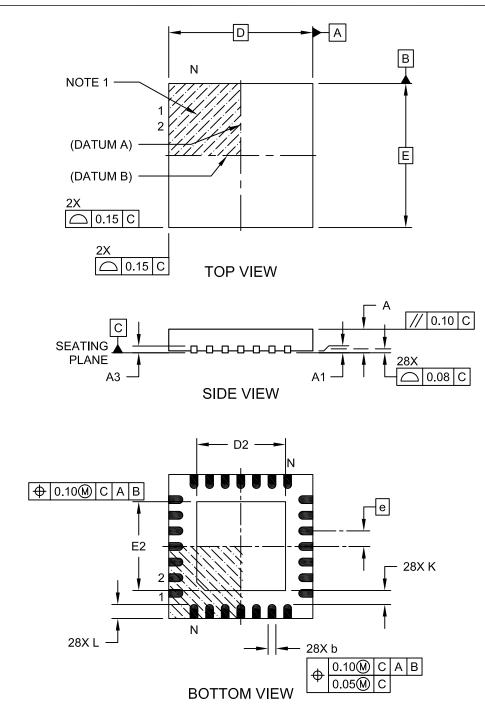

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | MILLIMETERS |      |  |

|-------------------------|--------|----------|-------------|------|--|

| Dimension               | Limits | MIN      | NOM         | MAX  |  |

| Number of Pins          | N      |          | 28          |      |  |

| Pitch                   | е      |          | 0.65 BSC    |      |  |

| Overall Height          | A      | 0.80     | 0.90        | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02        | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF |             |      |  |

| Overall Width           | E      |          | 6.00 BSC    |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70        | 4.20 |  |

| Overall Length          | D      |          | 6.00 BSC    |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70        | 4.20 |  |

| Terminal Width          | b      | 0.23     | 0.30        | 0.35 |  |

| Terminal Length         | L      | 0.50     | 0.55        | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20     | -           | -    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

# 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |          |      |  |

|------------------------|-------------|-----------|----------|------|--|

| Dimension              | Limits      | MIN       | NOM      | MAX  |  |

| Number of Pins         | N           |           | 40       |      |  |

| Pitch                  | е           |           | 0.40 BSC |      |  |

| Overall Height         | Α           | 0.45      | 0.50     | 0.55 |  |

| Standoff               | A1          | 0.00      | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.127 REF |          |      |  |

| Overall Width          | E           |           | 5.00 BSC |      |  |

| Exposed Pad Width      | E2          | 3.60      | 3.70     | 3.80 |  |

| Overall Length         | D           |           | 5.00 BSC |      |  |

| Exposed Pad Length     | D2          | 3.60      | 3.70     | 3.80 |  |

| Contact Width          | b           | 0.15      | 0.20     | 0.25 |  |

| Contact Length         | L           | 0.30      | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20      | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2