Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 22                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10/12b; D/A 1x5b                                                           |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN (6x6)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl028t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

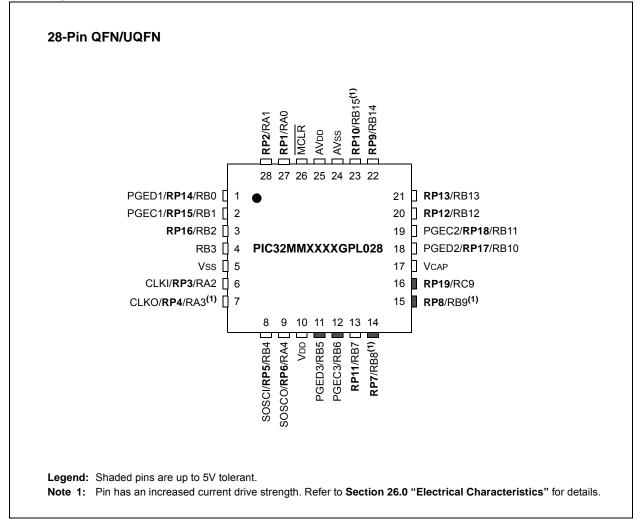

# **Pin Diagrams (Continued)**

#### TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN QFN/UQFN DEVICES

| Pin | Function                                             | Pin | Function                                                                                    |

|-----|------------------------------------------------------|-----|---------------------------------------------------------------------------------------------|

| 1   | PGED1/AN2/C1IND/C2INB <b>/RP14</b> /RB0              | 15  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/<br>INT2/RB9 <sup>(1)</sup> |

| 2   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1              | 16  | RP19/RC9                                                                                    |

| 3   | AN4/C1INB/ <b>RP16</b> /RB2                          | 17  | VCAP                                                                                        |

| 4   | AN11/C1INA/RB3                                       | 18  | PGED2/TDO/ <b>RP17</b> /RB10                                                                |

| 5   | Vss                                                  | 19  | PGEC2/TDI/ <b>RP18</b> /RB11                                                                |

| 6   | OSC1/CLKI/AN5/ <b>RP3</b> /OCM1C/RA2                 | 20  | AN7/LVDIN/ <b>RP12</b> /RB12                                                                |

| 7   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>  | 21  | AN8/ <b>RP13</b> /RB13                                                                      |

| 8   | SOSCI/ <b>RP5</b> /RB4                               | 22  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                       |

| 9   | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                 | 23  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                         |

| 10  | VDD                                                  | 24  | AVss                                                                                        |

| 11  | PGED3/RB5                                            | 25  | AVdd                                                                                        |

| 12  | PGEC3/RB6                                            | 26  | MCLR                                                                                        |

| 13  | RP11/RB7                                             | 27  | VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                                                       |

| 14  | TCK/ <b>RP7</b> /U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup> | 28  | Vref-/AN1/ <b>RP2</b> /OCM1F/RA1                                                            |

Note 1: Pin has an increased current drive strength.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

# 2.1 Basic Connection Requirements

Getting started with the PIC32MM0064GPL036 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Capacitor on Internal Voltage Regulator (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

# 6.1 Reset Control Registers

# TABLE 6-1: RESETS REGISTER MAP

| ress<br>)                   |                                 | a         |       | Bits              |       |       |         |          |      |      |       |      | s    |      |       |        |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------------------|-------|-------|---------|----------|------|------|-------|------|------|------|-------|--------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14             | 29/13 | 28/12 | 27/11   | 26/10    | 25/9 | 24/8 | 23/7  | 22/6 | 21/5 | 20/4 | 19/3  | 18/2   | 17/1  | 16/0  | All Resets |

| 1240                        | RCON                            | 31:16     | PORIO | PORCORE           |       |       | BCFGERR | BCFGFAIL |      | _    |       |      |      |      |       |        |       | _     | C000       |

| 1240                        | RCON                            | 15:0      | _     | _                 | _     |       | —       | _        | CMR  |      | EXTR  | SWR  | —    | WDTO | SLEEP | IDLE   | BOR   | POR   | 0003       |

| 1250                        | RSWRST                          | 31:16     | _     | -                 |       |       | —       | —        | —    | _    | _     |      | —    | —    |       | _      |       | _     | 0000       |

| 1250                        | ROWROI                          | 15:0      | _     | -                 |       |       | —       | —        | —    | _    | _     |      | —    | —    |       | _      |       | SWRST | 0000       |

| 1000                        | RNMICON                         | 31:16     |       | _                 |       | _     | —       | _        | —    | WDTR | SWNMI |      | _    | —    | GNMI  | _      | CF    | WDTS  | 0000       |

| 1200                        | RININICON                       | 15:0      |       | NMICNT<15:0> 0000 |       |       |         |          |      |      |       |      | 0000 |      |       |        |       |       |            |

| 1270                        | PWRCON                          | 31:16     | _     | _                 | _     |       | —       | _        | —    |      | _     |      | —    | —    |       | —      |       | —     | 0000       |

| 1270                        | FWRCON                          | 15:0      | _     | _                 | _     | -     | _       | _        | —    | -    |       | _    | _    | _    | _     | SBOREN | RETEN | VREGS | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

# 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(2)</b>   |                  |                  |

#### **REGISTER 8-6:** OSCTUN: FRC TUNING REGISTER<sup>(1)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-6 Unimplemented: Read as '0'

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized nor tested.

# 9.7 Pin Pull-up and Pull-Down

Each I/O pin also has a weak pull-up and a weak pulldown connected to it. The pull-ups act as a current source, or sink source, connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

# 9.8 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 9.8.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation, "RPn", in their full pin designation, where "RP" designates a Remappable Peripheral and "n" is the remappable port number.

#### 9.8.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (MCCP, SCCP) and others.

In comparison, some digital only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 9.8.3 CONTROLLING PPS

PPS features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

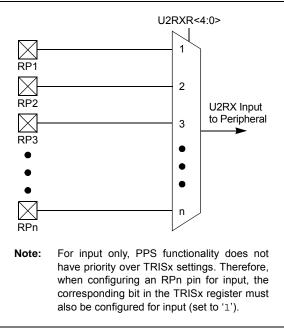

#### 9.8.4 INPUT MAPPING

The RPINRx registers are used to assign the peripheral input to the required remappable pin, RPn (refer to the peripheral inputs and the corresponding RPINRx registers listed in Table 9-2). Each RPINRx register contains sets of 5-bit fields. Programming these bits with the remappable pin number will connect the peripheral to this RPn pin. Example 9-1 and Figure 9-2 illustrate the remappable pin selection for the U2RX input.

#### EXAMPLE 9-1: UART2 RX INPUT ASSIGNMENT TO RP9/RB14 PIN

| RPINR9bits.U2RXR | = | 9; | 11 | connect UART2 RX |

|------------------|---|----|----|------------------|

|                  |   |    | // | input to RP9 pin |

# FIGURE 9-2: REMA

#### REMAPPABLE INPUT EXAMPLE FOR U2RX

#### TABLE 9-2: INPUT PIN SELECTION

| Input Name              | Function Name | Register | Function Bits |

|-------------------------|---------------|----------|---------------|

| External Interrupt 4    | INT4          | RPINR1   | INT4R<4:0>    |

| MCCP1 Input Capture     | ICM1          | RPINR2   | ICM1R<4:0>    |

| SCCP2 Input Capture     | ICM2          | RPINR2   | ICM2R<4:0>    |

| SCCP3 Input Capture     | ICM3          | RPINR3   | ICM3R<4:0>    |

| Output Compare Fault A  | OCFA          | RPINR5   | OCFAR<4:0>    |

| Output Compare Fault B  | OCFB          | RPINR5   | OCFBR<4:0>    |

| CCP Clock Input A       | TCKIA         | RPINR6   | TCKIAR<4:0>   |

| CCP Clock Input B       | TCKIB         | RPINR6   | TCKIBR<4:0>   |

| UART2 Receive           | U2RX          | RPINR9   | U2RXR<4:0>    |

| UART2 Clear-to-Send     | U2CTS         | RPINR9   | U2CTSR<4:0>   |

| SPI2 Data Input         | SDI2          | RPINR11  | SDI2R<4:0>    |

| SPI2 Clock Input        | SCK2IN        | RPINR11  | SCK2INR<4:0>  |

| SPI2 Slave Select Input | SS2IN         | RPINR11  | SS2INR<4:0>   |

| CLC Input A             | CLCINA        | RPINR12  | CLCINAR<4:0>  |

| CLC Input B             | CLCINB        | RPINR12  | CLCINBR<4:0>  |

| Bit<br>Range                | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04                       | W-0                   | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 31:24                       | 31:24 WDTCLRKEY<15:8> |                   |                   |                   |                   |                   |                  |                  |

| 00.40                       | W-0                   | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 23:16                       |                       |                   |                   | WDTCL             | RKEY<7:0>         |                   |                  |                  |

| 45.0                        | R/W-0                 | U-0               | U-0               | R-y               | R-y               | R-y               | R-y              | R-y              |

| 15:8                        | ON <sup>(1)</sup>     | —                 | _                 |                   |                   | RUNDIV<4:0        | >                |                  |

| 7.0                         | R-y                   | R-y               | R-y               | R-y               | R-y               | R-y               | R-y              | R/W-y            |

| 7:0 CLKSEL<1:0> SLPDIV<4:0> |                       |                   |                   |                   |                   |                   |                  | WDTWINEN         |

#### REGISTER 11-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Con | y = Values set from Configuration bits on Reset     |                    |  |  |  |  |

|-------------------|-------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit        | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits

To clear the Watchdog Timer to prevent a time-out, software must write the value, 0x5743, to this location using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = The WDT is enabled

0 = The WDT is disabled

bit 14-13 Unimplemented: Read as '0'

bit 12-8 **RUNDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RWDTPS<4:0> Configuration bits in FWDT.

- bit 7-6 **CLKSEL<1:0>:** Shadow Copy of Watchdog Timer Clock Selection Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RCLKSEL<1:0> Configuration bits in FWDT.

- bit 5-1 **SLPDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Sleep/Idle Mode from Configuration bits On Reset, these bits are set to the values of the SWDTPS<4:0> Configuration bits in FWDT.

# bit 0 WDTWINEN: Watchdog Timer Window Enable bit On Reset, this bit is set to the value of the WINDIS Configuration bit in FWDT. 1 = Windowed mode is enabled

0 = Windowed mode is disabled

Note 1: This bit only has control when FWDTEN (FWDT<15>) = 0.

# 12.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

# 12.1 Introduction

PIC32MM0064GPL036 family devices include three Capture/Compare/PWM/Timer (CCP) modules. These modules are similar to the multipurpose timer modules found on many other 32-bit microcontrollers. They also provide the functionality of the comparable input capture, output compare and general purpose timer peripherals found in all earlier PIC32 devices.

CCP modules can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

There are two different forms of the module, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM/Timer (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM/Timer (MCCPs) output modules can provide up to six outputs and an extended range of output control features, depending on the pin count of the particular device.

All modules (SCCP and MCCP) include these features:

- User-Selectable Clock Inputs, including System Clock and External Clock Input Pins

- Input Clock Prescaler for Time Base

- Output Postscaler for module Interrupt Events or Triggers

- Synchronization Output Signal for Coordinating other MCCP/SCCP modules with User-Configurable Alternate and Auxiliary Source Options

- Fully Asynchronous Operation in all modes and in Low-Power Operation

- Special Output Trigger for ADC Conversions

- 16-Bit and 32-Bit General Purpose Timer modes with Optional Gated Operation for Simple Time Measurements

- · Capture modes:

- Backward compatible with previous input capture peripherals of the PIC32 family

- 16-bit or 32-bit capture of time base on external event

- Up to four-level deep FIFO capture buffer

- Capture source input multiplexer

- Gated capture operation to reduce noise-induced false captures

- · Output Compare/PWM modes:

- Backward compatible with previous output compare peripherals of the PIC32 family

- Single Edge and Dual Edge Compare modes

- Center-Aligned Compare mode

- Variable Frequency Pulse mode

- External Input mode

MCCP modules also include these extended PWM features:

- Single Output Steerable mode

- Brush DC Motor (Forward and Reverse) modes

- Half-Bridge with Dead-Time Delay mode

- Push-Pull PWM mode

- Output Scan mode

- Auto-Shutdown with Programmable Source and Shutdown State

- Programmable Output Polarity

The SCCP and MCCP modules can be operated in only one of the three major modes (Capture, Compare or Timer) at any time. The other modes are not available unless the module is reconfigured.

A conceptual block diagram for the module is shown in Figure 12-1. All three modes use the time base generator and the common Timer register pair (CCPxTMR). Other shared hardware components, such as comparators and buffer registers, are activated and used as a particular mode requires.

## REGISTER 13-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when the CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

NOTES:

# REGISTER 18-3: CLCxGLS: CLCx GATE LOGIC INPUT SELECT REGISTER (CONTINUED)

| bit 20 | G3D3N: Gate 3 Data Source 3 Negated Enable bit                                                                                                        |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = The Data Source 3 inverted signal is enabled for Gate 3                                                                                           |

|        | 0 = The Data Source 3 inverted signal is disabled for Gate 3                                                                                          |

| bit 19 | G3D2T: Gate 3 Data Source 2 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 2 signal is enabled for Gate 3</li><li>0 = The Data Source 2 signal is disabled for Gate 3</li></ul>                      |

| bit 18 | G3D2N: Gate 3 Data Source 2 Negated Enable bit                                                                                                        |

|        | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 3</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 3</li> </ul> |

| bit 17 | G3D1T: Gate 3 Data Source 1 True Enable bit                                                                                                           |

|        | <ul> <li>1 = The Data Source 1 signal is enabled for Gate 3</li> <li>0 = The Data Source 1 signal is disabled for Gate 3</li> </ul>                   |

| bit 16 | <b>G3D1N:</b> Gate 3 Data Source 1 Negated Enable bit                                                                                                 |

| 510 10 | 1 = The Data Source 1 inverted signal is enabled for Gate 3                                                                                           |

|        | 0 = The Data Source 1 inverted signal is disabled for Gate 3                                                                                          |

| bit 15 | G2D4T: Gate 2 Data Source 4 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 4 signal is enabled for Gate 2</li><li>0 = The Data Source 4 signal is disabled for Gate 2</li></ul>                      |

| bit 14 | G2D4N: Gate 2 Data Source 4 Negated Enable bit                                                                                                        |

|        | 1 = The Data Source 4 inverted signal is enabled for Gate 2                                                                                           |

|        | 0 = The Data Source 4 inverted signal is disabled for Gate 2                                                                                          |

| bit 13 | G2D3T: Gate 2 Data Source 3 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 3 signal is enabled for Gate 2</li><li>0 = The Data Source 3 signal is disabled for Gate 2</li></ul>                      |

| bit 12 | G2D3N: Gate 2 Data Source 3 Negated Enable bit                                                                                                        |

|        | <ul><li>1 = The Data Source 3 inverted signal is enabled for Gate 2</li><li>0 = The Data Source 3 inverted signal is disabled for Gate 2</li></ul>    |

| bit 11 | G2D2T: Gate 2 Data Source 2 True Enable bit                                                                                                           |

|        | 1 = The Data Source 2 signal is enabled for Gate 2                                                                                                    |

|        | 0 = The Data Source 2 signal is disabled for Gate 2                                                                                                   |

| bit 10 | G2D2N: Gate 2 Data Source 2 Negated Enable bit                                                                                                        |

|        | <ul><li>1 = The Data Source 2 inverted signal is enabled for Gate 2</li><li>0 = The Data Source 2 inverted signal is disabled for Gate 2</li></ul>    |

| bit 9  | G2D1T: Gate 2 Data Source 1 True Enable bit                                                                                                           |

|        | <ul> <li>1 = The Data Source 1 signal is enabled for Gate 2</li> <li>0 = The Data Source 1 signal is disabled for Gate 2</li> </ul>                   |

| bit 8  | G2D1N: Gate 2 Data Source 1 Negated Enable bit                                                                                                        |

|        | 1 = The Data Source 1 inverted signal is enabled for Gate 2                                                                                           |

|        | 0 = The Data Source 1 inverted signal is disabled for Gate 2                                                                                          |

| bit 7  | G1D4T: Gate 1 Data Source 4 True Enable bit                                                                                                           |

|        | <ul> <li>1 = The Data Source 4 signal is enabled for Gate 1</li> <li>0 = The Data Source 4 signal is disabled for Gate 1</li> </ul>                   |

| bit 6  | G1D4N: Gate 1 Data Source 4 Negated Enable bit                                                                                                        |

|        | <ul> <li>1 = The Data Source 4 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 4 inverted signal is disabled for Gate 1</li> </ul> |

| bit 5  | G1D3T: Gate 1 Data Source 3 True Enable bit                                                                                                           |

|        | <ul> <li>1 = The Data Source 3 signal is enabled for Gate 1</li> <li>0 = The Data Source 3 signal is disabled for Gate 1</li> </ul>                   |

# PIC32MM0064GPL036 FAMILY

#### REGISTER 19-2: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 AND 2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | -                 | _                 | _                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ON                | COE               | CPOL              | —                 | _                 | _                 | CEVT             | COUT             |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | EVPO              | _<1:0>            | _                 | CREF              | _                 | _                 | CCH•             | <1:0>            |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, r   | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Comparator Enable bit

- 1 = Comparator is enabled

- 0 = Comparator is disabled

#### bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is present on the CxOUT pin

- 0 = Comparator output is internal only

- bit 13 CPOL: Comparator Output Polarity Select bit

- 1 = Comparator output is inverted

- 0 = Comparator output is not inverted

#### bit 12-10 Unimplemented: Read as '0'

- bit 9 CEVT: Comparator Event bit

- 1 = Comparator event that is defined by EVPOL<1:0> has occurred; subsequent triggers and interrupts are disabled until the bit is cleared

- 0 = Comparator event has not occurred

- bit 8 **COUT:** Comparator Output bit

$\frac{\text{When CPOL} = 0:}{1 = \text{VIN} + \text{VIN}-}$ 0 = VIN + VIN- $\frac{\text{When CPOL} = 1:}{1 = \text{VIN} + \text{VIN}-}$

0 = VIN + > VIN -

#### REGISTER 19-2: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 AND 2) (CONTINUED)

bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits

11 = Trigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0)10 = Trigger/event/interrupt is generated on transition of the comparator output:

If CPOL = 0 (non-inverted polarity):

High-to-low transition only. If CPOL = 1 (inverted polarity):

Low-to-high transition only.

01 = Trigger/event/interrupt is generated on transition of the comparator output:

If CPOL = 0 (non-inverted polarity):

Low-to-high transition only.

If CPOL = 1 (inverted polarity):

High-to-low transition only.

00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Reference Select bit (non-inverting input)

- 1 = Non-inverting input connects to the internal reference defined by the CVREFSEL bit in the CMSTAT register 0 = Non-inverting input connects to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits

- 11 = Inverting input of the comparator connects to the band gap reference voltage

- 10 = Inverting input of the comparator connects to the CxIND pin

- 01 = Inverting input of the comparator connects to the CxINC pin

- 00 = Inverting input of the comparator connects to the CxINB pin

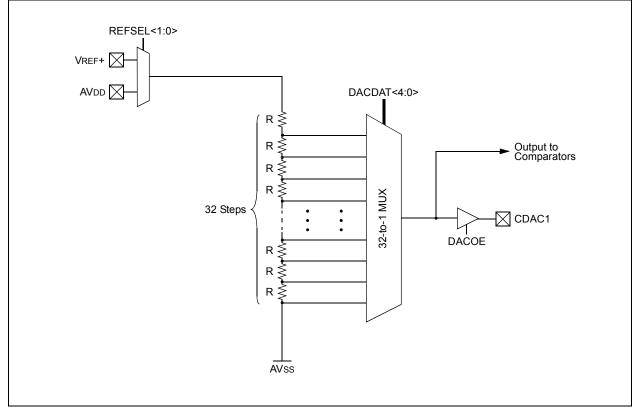

# 20.0 CONTROL DIGITAL-TO-ANALOG CONVERTER (CDAC)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The Control Digital-to-Analog Converter (CDAC) generates analog voltage corresponding to the digital input.

The CDAC has the following features:

- 32 Output Levels are Available

- Internally Connected to Comparators to Conserve Device Pins

- · Output can be Connected to a Pin

A block diagram of the CDAC module is illustrated in Figure 20-1.

# FIGURE 20-1: CDAC BLOCK DIAGRAM

### 22.3 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not take effect and read values are invalid.

To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). To prevent accidental configuration changes under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK bit in PMDCON register (PMDCON<11>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes. To set or clear PMDLOCK, an unlock sequence must be executed. Refer to Section 23.4 "System Registers Write Protection" for details.

Table 22-1 lists the module disable bits and locations for all modules.

| Peripheral                                               | PMDx Bit Name | Register Name and Bit Location |  |

|----------------------------------------------------------|---------------|--------------------------------|--|

| Analog-to-Digital Converter (ADC)                        | ADCMD         | PMD1<0>                        |  |

| Voltage Reference (VR)                                   | VREFMD        | PMD1<12>                       |  |

| High/Low-Voltage Detect (HLVD)                           | HLVDMD        | PMD1<20>                       |  |

| Comparator 1 (CMP1)                                      | CMP1MD        | PMD2<0>                        |  |

| Comparator 2 (CMP2)                                      | CMP2MD        | PMD2<1>                        |  |

| Configurable Logic Cell 1 (CLC1)                         | CLC1MD        | PMD2<24>                       |  |

| Configurable Logic Cell 2 (CLC2)                         | CLC2MD        | PMD2<25>                       |  |

| Multiple Outputs Capture/Compare/PWM/<br>Timer1 (MCCP1)  | CCP1MD        | PMD3<8>                        |  |

| Single Output Capture/Compare/PWM/Timer2<br>(SCCP2)      | CCP2MD        | PMD3<9>                        |  |

| Single Output Capture/Compare/PWM/Timer3 (SCCP3)         | CCP3MD        | PMD3<10>                       |  |

| Timer1 (TMR1)                                            | T1MD          | PMD4<0>                        |  |

| Universal Asynchronous Receiver<br>Transmitter 1 (UART1) | U1MD          | PMD5<0>                        |  |

| Universal Asynchronous Receiver<br>Transmitter 2 (UART2) | U2MD          | PMD5<1>                        |  |

| Serial Peripheral Interface 1 (SPI1)                     | SPI1MD        | PMD5<8>                        |  |

| Serial Peripheral Interface 2 (SPI2)                     | SPI2MD        | PMD5<9>                        |  |

| Real-Time Clock and Calendar (RTCC)                      | RTCCMD        | PMD6<0>                        |  |

| Reference Clock Output (REFCLKO)                         | REFOMD        | PMD6<8>                        |  |

| Programmable Cyclic Redundancy Check<br>(CRC)            | CRCMD         | PMD7<3>                        |  |

### TABLE 22-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS

| Operatin      | <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |                                                                       |                    |                       |       |                                                                                                                                                          |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol                                                                                                                  | Characteristics                                                       | Min.               | Max.                  | Units | Conditions                                                                                                                                               |  |  |  |

| Dl60a         | licl                                                                                                                    | Input Low Injection<br>Current                                        | 0                  | <sub>-5</sub> (1,4)   | mA    | This parameter applies to all pins.                                                                                                                      |  |  |  |

| DI60b         | Іісн                                                                                                                    | Input High Injection<br>Current                                       | 0                  | +5 <sup>(2,3,4)</sup> | mA    | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins and SOSCI. Maximum IICH<br>current for these exceptions is<br>0 mA. |  |  |  |

| DI60c         | ∑ІІСТ                                                                                                                   | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(5)</sup> | +20 <sup>(5)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents from<br>all I/O pins,<br>(   IICL +   IICH   ) $\leq \sum$ IICT                      |  |  |  |

**Note 1:** VIL Source < (Vss - 0.3). Characterized but not tested.

2: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

**3:** Digital 5V tolerant pins do not have an internal high-side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

4: Injection currents can affect the ADC results.

5: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit.

NOTES:

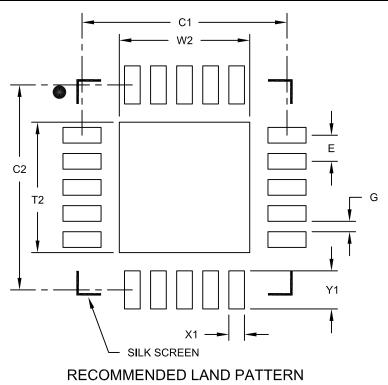

# 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch              | E  | 0.50 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 2.50 |  |

| Optional Center Pad Length | T2 |             |      | 2.50 |  |

| Contact Pad Spacing        | C1 |             | 3.93 |      |  |

| Contact Pad Spacing        | C2 |             | 3.93 |      |  |

| Contact Pad Width          | X1 |             |      | 0.30 |  |

| Contact Pad Length         | Y1 |             |      | 0.73 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0653-2