Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-SQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl036-e-m2 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

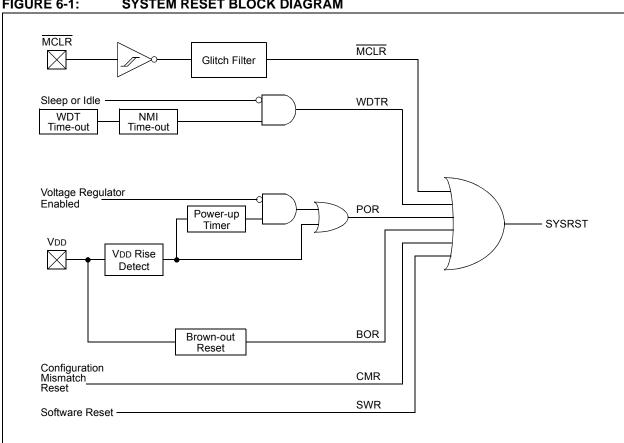

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS60001118) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The device Reset sources are as follows:

- Power-on Reset (POR)

- Master Clear Reset Pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### SYSTEM RESET BLOCK DIAGRAM FIGURE 6-1:

### REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER (CONTINUED)

```

bit 23-20 PRI5SS<3:0>: Interrupt with Priority Level 5 Shadow Set bits<sup>(1)</sup>

1111 = Reserved

0010 = Reserved

0001 = Interrupt with a priority level of 5 uses Shadow Set 1

0000 = Interrupt with a priority level of 5 uses Shadow Set 0

bit 19-16 PRI4SS<3:0>: Interrupt with Priority Level 4 Shadow Set bits<sup>(1)</sup>

1111 = Reserved

0010 = Reserved

0001 = Interrupt with a priority level of 4 uses Shadow Set 1

0000 = Interrupt with a priority level of 4 uses Shadow Set 0

bit 15-12 PRI3SS<3:0>: Interrupt with Priority Level 3 Shadow Set bits<sup>(1)</sup>

1111 = Reserved

0010 = Reserved

0001 = Interrupt with a priority level of 3 uses Shadow Set 1

0000 = Interrupt with a priority level of 3 uses Shadow Set 0

bit 11-8 PRI2SS<3:0>: Interrupt with Priority Level 2 Shadow Set bits<sup>(1)</sup>

1111 = Reserved

.

0010 = Reserved

0001 = Interrupt with a priority level of 2 uses Shadow Set 1

0000 = Interrupt with a priority level of 2 uses Shadow Set 0

PRI1SS<3:0>: Interrupt with Priority Level 1 Shadow Set bits<sup>(1)</sup>

bit 7-4

1111 = Reserved

0010 = Reserved

0001 = Interrupt with a priority level of 1 uses Shadow Set 1

0000 = Interrupt with a priority level of 1 uses Shadow Set 0

bit 3-1

Unimplemented: Read as '0'

bit 0

SS0: Single Vector Shadow Register Set bit

1 = Single vector is presented with a shadow set

0 = Single vector is not presented with a shadow set

```

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

# 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 59. "Oscillators with DCO" (DS60001329) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The PIC32MM0064GPL036 family oscillator system has the following modules and features:

- On-Chip PLL with User-Selectable Multiplier and Output Divider to Boost Operating Frequency on Select Internal and External Oscillator Sources

- Primary High-Frequency Crystal Oscillator

- Secondary Low-Frequency and Low-Power Crystal Oscillator

- On-Chip Fast RC (FRC) Oscillator with User-Selectable Output Divider

- Software-Controllable Switching between Various Clock Sources

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- Flexible Reference Clock Output (REFO)

A block diagram of the oscillator system is provided in Figure 8-1.

# 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MM0064GPL036 family oscillator system includes a Fail-Safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the FRC oscillator and triggers a Non-Maskable Interrupt (NMI). When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode, both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(2)</b>   |                  |                  |

#### **REGISTER 8-6:** OSCTUN: FRC TUNING REGISTER<sup>(1)</sup>

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-6 Unimplemented: Read as '0'

- Note 1: Writes to this register require an unlock sequence. Refer to Section 23.4 "System Registers Write Protection" for details.

- 2: OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized nor tested.

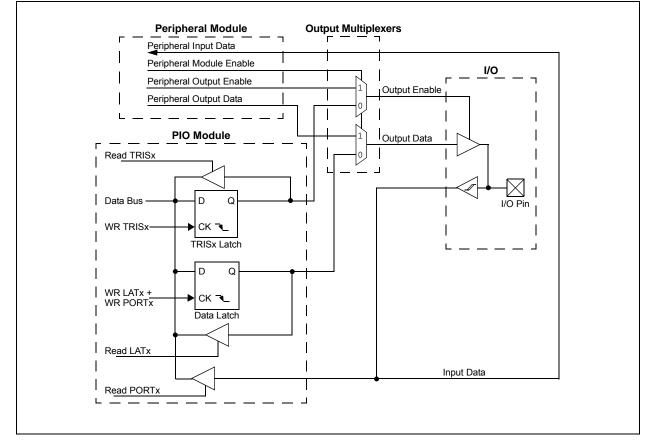

# 9.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

Many of the device pins are shared among the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. Some pins in the devices are 5V tolerant pins. Some of the key features of the I/O ports are:

- Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change-in-Pin State is Detected

- Operation during Sleep and Idle modes

- Fast Bit Manipulation using the CLR, SET and INV registers

Figure 9-1 illustrates a block diagram of a typical multiplexed I/O port.

#### FIGURE 9-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

# 11.1 Watchdog Timer Control Registers

# TABLE 11-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | ø         |       |       |       |       |                                              |       |      |      | Bits    |      |      |      |      |      |      |      | s         |

|---------------------------|-----------------------|-----------|-------|-------|-------|-------|----------------------------------------------|-------|------|------|---------|------|------|------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                                        | 26/10 | 25/9 | 24/8 | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 2500                      | WDTCON <sup>(1)</sup> | 31:16     |       |       |       |       |                                              |       |      | WDTC | LRKEY<1 | 5:0> |      |      |      |      |      |      | 0000      |

| 3E80                      | WDICON                | 15:0      | ON    |       | _     |       | RUNDIV<4:0> CLKSEL<1:0> SLPDIV<4:0> WDTWINEN |       |      |      | xxxx    |      |      |      |      |      |      |      |           |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# 12.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

# 12.1 Introduction

PIC32MM0064GPL036 family devices include three Capture/Compare/PWM/Timer (CCP) modules. These modules are similar to the multipurpose timer modules found on many other 32-bit microcontrollers. They also provide the functionality of the comparable input capture, output compare and general purpose timer peripherals found in all earlier PIC32 devices.

CCP modules can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

There are two different forms of the module, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM/Timer (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM/Timer (MCCPs) output modules can provide up to six outputs and an extended range of output control features, depending on the pin count of the particular device.

All modules (SCCP and MCCP) include these features:

- User-Selectable Clock Inputs, including System Clock and External Clock Input Pins

- Input Clock Prescaler for Time Base

- Output Postscaler for module Interrupt Events or Triggers

- Synchronization Output Signal for Coordinating other MCCP/SCCP modules with User-Configurable Alternate and Auxiliary Source Options

- Fully Asynchronous Operation in all modes and in Low-Power Operation

- Special Output Trigger for ADC Conversions

- 16-Bit and 32-Bit General Purpose Timer modes with Optional Gated Operation for Simple Time Measurements

- · Capture modes:

- Backward compatible with previous input capture peripherals of the PIC32 family

- 16-bit or 32-bit capture of time base on external event

- Up to four-level deep FIFO capture buffer

- Capture source input multiplexer

- Gated capture operation to reduce noise-induced false captures

- · Output Compare/PWM modes:

- Backward compatible with previous output compare peripherals of the PIC32 family

- Single Edge and Dual Edge Compare modes

- Center-Aligned Compare mode

- Variable Frequency Pulse mode

- External Input mode

MCCP modules also include these extended PWM features:

- Single Output Steerable mode

- Brush DC Motor (Forward and Reverse) modes

- Half-Bridge with Dead-Time Delay mode

- Push-Pull PWM mode

- Output Scan mode

- Auto-Shutdown with Programmable Source and Shutdown State

- Programmable Output Polarity

The SCCP and MCCP modules can be operated in only one of the three major modes (Capture, Compare or Timer) at any time. The other modes are not available unless the module is reconfigured.

A conceptual block diagram for the module is shown in Figure 12-1. All three modes use the time base generator and the common Timer register pair (CCPxTMR). Other shared hardware components, such as comparators and buffer registers, are activated and used as a particular mode requires.

# TABLE 12-1: MCCP/SCCP REGISTER MAP (CONTINUED)

|                             | LL 1 <u>2</u> -1.               |           |         |                      |          | ·      |                                         |        |            |      |             |         |         |        |         |          |        |       |               |

|-----------------------------|---------------------------------|-----------|---------|----------------------|----------|--------|-----------------------------------------|--------|------------|------|-------------|---------|---------|--------|---------|----------|--------|-------|---------------|

| ress<br>)                   | 20                              | е         |         |                      |          |        |                                         |        |            |      | Bits        |         |         |        |         |          |        |       |               |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14                | 29/13    | 28/12  | 27/11                                   | 26/10  | 25/9       | 24/8 | 23/7        | 22/6    | 21/5    | 20/4   | 19/3    | 18/2     | 17/1   | 16/0  | All<br>Resets |

| 0260                        |                                 | 31:16     | —       | _                    | —        |        | _                                       | _      | —          | _    | _           | _       | _       | _      | —       | —        | _      | —     | 0000          |

| 0200                        | 0012101                         | 15:0      |         |                      |          |        |                                         |        |            | CN   | /IPA<15:0>  |         |         |        |         |          |        |       | 0000          |

| 0270                        | CCP2RB                          | 31:16     | —       | —                    | —        | —      | —                                       | —      | —          |      | —           | —       |         | —      | —       | —        | —      | —     | 0000          |

| 0210                        |                                 | 15:0      |         | CMPB<15:0> 0000      |          |        |                                         |        |            |      | 0000        |         |         |        |         |          |        |       |               |

| 0280                        | CCP2BUF                         | 31:16     |         | CCP2 BUFH<15:0> 0000 |          |        |                                         |        |            | 0000 |             |         |         |        |         |          |        |       |               |

| 0200                        | 001 2001                        | 15:0      |         | CCP2 BUFL<15:0> 0000 |          |        |                                         |        |            |      | 0000        |         |         |        |         |          |        |       |               |

| 0300                        | CCP3CON1                        | 31:16     | OPSSRC  | RTRGEN               | —        | —      |                                         | OPS<   | 3:0>       |      |             | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >      |       | 0000          |

| 0000                        | 001000111                       | 15:0      | ON      | _                    | SIDL     | CCPSLP | TMRSYNC                                 | С      | LKSEL<2:0> | >    | TMRP        | S<1:0>  | T32     | CCSEL  |         | MOE      | )<3:0> |       | 0000          |

| 0310                        | CCP3CON2                        | 31:16     | OENSYNC | _                    |          | _      | OCAEN ICGSM<1:0> - AUXOUT<1:0> ICS<2:0> |        |            |      |             | 0100    |         |        |         |          |        |       |               |

| 0010                        | 001 000112                      | 15:0      | PWMRSEN | ASDGM                | —        | SSDG   | _                                       | —      | _          | —    |             |         |         | ASDO   | G<7:0>  |          |        |       | 0000          |

| 0320                        | CCP3CON3                        | 31:16     | OETRIG  | 0                    | SCNT<2:0 | >      | _                                       | —      | _          |      | _           | _       | POLACE  | _      | PSSAC   | E<1:0>   | _      |       | 0000          |

| 0020                        |                                 | 15:0      | —       | _                    |          | _      | _                                       | —      | _          |      | _           | _       | _       | _      | _       | —        | _      |       | 0000          |

| 0330                        | CCP3STAT                        | 31:16     | —       | —                    | —        | —      | —                                       | —      | —          | —    | —           | —       | —       | PRLWIP | TMRHWIP | TMRLWIP  | RBWIP  | RAWIP | 0000          |

| 0000                        | 001001/1                        | 15:0      | —       | —                    | —        | —      | —                                       | ICGARM | —          |      | CCPTRIG     | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV   | ICBNE | 0000          |

| 0340                        | CCP3TMR                         | 31:16     |         |                      |          |        |                                         |        |            | CCP3 | TMRH<15:0   | )>      |         |        |         |          |        |       | 0000          |

| 00.0                        | 001 011111                      | 15:0      |         |                      |          |        |                                         |        |            | CCP3 | TMRL<15:0   | )>      |         |        |         |          |        |       | 0000          |

| 0350                        | CCP3PR                          | 31:16     |         |                      |          |        |                                         |        |            |      | 3 PRH<15:0  |         |         |        |         |          |        |       | 0000          |

|                             |                                 | 15:0      |         |                      | 1        |        |                                         |        |            | CCP  | 3 PRL<15:0  | >       |         |        |         |          |        |       | 0000          |

| 0360                        | CCP3RA                          | 31:16     | —       | _                    |          | —      | —                                       | —      | _          | —    | —           | _       | _       | —      | —       | —        | _      | —     | 0000          |

|                             |                                 | 15:0      |         |                      | 1        |        |                                         |        |            | CN   | /IPA<15:0>  |         |         |        |         |          |        |       | 0000          |

| 0370                        | CCP3RB                          | 31:16     | —       |                      |          |        |                                         |        |            |      |             |         |         |        |         |          |        |       |               |

|                             |                                 | 15:0      |         |                      |          |        |                                         |        |            |      |             |         | 0000    |        |         |          |        |       |               |

| 0380                        | CCP3BUF                         | 31:16     |         |                      |          |        |                                         |        |            |      | BUFH<15:(   | -       |         |        |         |          |        |       | 0000          |

|                             |                                 | 15:0      |         |                      |          |        |                                         |        |            | CCP3 | 8 BUFL<15:0 | )>      |         |        |         |          |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### REGISTER 12-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER (CONTINUED)

- bit 14 ASDGM: CCPx Auto-Shutdown Gate Mode Enable bit

- 1 = Waits until the next Time Base Reset or rollover for shutdown to occur

- 0 = Shutdown event occurs immediately

- bit 13 Unimplemented: Read as '0'

- bit 12 SSDG: CCPx Software Shutdown/Gate Control bit

- 1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting the ASDGM bit still applies)

- 0 = Normal module operation

- bit 11-8 Unimplemented: Read as '0'

- bit 7-0 ASDG<7:0>: CCPx Auto-Shutdown/Gating Source Enable bits

- 1xxx xxxx = Auto-shutdown is controlled by the OCFB pin (remappable)

- x1xx xxxx = Auto-shutdown is controlled by the OCFA pin (remappable)

- xx1x xxxx = Auto-shutdown is controlled by CLC1 for MCCP1/SCCP2 and by CLC2 for SCCP3

- xxx1 xxxx = Auto-shutdown is controlled by the SCCP2 output for MCCP1 and by MCCP1 for SCCP2/SCCP3

- xxxx 1xxx = Auto-shutdown is controlled by the SCCP3 output for MCCP1/SCCP2 and by SCCP2 for SCCP3

- xxxx x1xx = Reserved

- xxxx xx1x = Auto-shutdown is controlled by Comparator 2

- xxxx xxx1 = Auto-shutdown is controlled by Comparator 1

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

#### REGISTER 12-3: CCPxCON3: CAPTURE/COMPARE/PWMx CONTROL 3 REGISTER (CONTINUED)

- bit 17-16 **PSSBDF<1:0>:** PWMx Output Pins, OCxB, OCxD and OCxF, Shutdown State Control bits<sup>(1)</sup>

- 11 = Pins are driven active when a shutdown event occurs

- 10 = Pins are driven inactive when a shutdown event occurs

- 0x = Pins are in a high-impedance state when a shutdown event occurs

- bit 15-6 **Unimplemented:** Read as '0'

. . .

bit 5-0 DT<5:0>: PWM Dead-Time Select bits<sup>(1)</sup>

111111 = Insert 63 dead-time delay periods between complementary output signals 111110 = Insert 62 dead-time delay periods between complementary output signals

000010 = Insert 2 dead-time delay periods between complementary output signals 000001 = Insert 1 dead-time delay period between complementary output signals 000000 = Dead-time logic is disabled

Note 1: These bits are implemented in MCCP modules only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        | -                 | _                 |                   |                   | R۷                | (BUFELM<4:0       | )>               |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | _                 | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |

| 15.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         | _                 | _                 |                   | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |  |

#### **REGISTER 13-3:** SPIxSTAT: SPIx STATUS REGISTER

| Legend: C = Clearable bit |                   | C = Clearable bit | HS = Hardware Settable   | bit                |

|---------------------------|-------------------|-------------------|--------------------------|--------------------|

|                           | R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | read as '0'        |

|                           | -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 FRMERR: SPIx Frame Error status bit 1 = Frame error is detected 0 = No frame error is detected This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPIx Activity Status bit

- 1 = SPIx peripheral is currently busy with some transactions

- 0 = SPIx peripheral is currently Idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: SPIx Transmit Underrun (TUR) bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When the SPIx Shift register is empty

- 0 = When the SPIx Shift register is not empty

- bit 6 SPIROV: SPIx Receive Overflow (ROV) Flag bit

- 1 = New data is completely received and discarded; the user software has not read the previous data in the SPIxBUF register

- 0 = No overflow has occurred

- This bit is set in hardware; it can only be cleared (= 0) in software.

- bit 5 SPIRBE: SPIx RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CPU Read Pointer (CRPTR) = SPI Write Pointer (SWPTR))

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   | HRTEN<2:0>        |                   | HRONE<3:0>        |                   |                  |                  |  |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 |                   | MINTEN<2:0>       | >                 | MINONE<3:0>       |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | SECTE             | EN<3:0>           |                   |                   | SECON             | IE<3:0>          |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

#### REGISTER 15-4: RTCTIME/ALMTIME: RTCC/ALARM TIME REGISTERS

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

- bit 30-28 **HRTEN<2:0>:** Binary Coded Decimal Value of Hours 10-Digit bits Contains a value from 0 to 2.

- bit 27-24 **HRONE<3:0>:** Binary Coded Decimal Value of Hours 1-Digit bits Contains a value from 0 to 9.

- bit 23 Unimplemented: Read as '0'

- bit 22-20 **MINTEN<2:0>:** Binary Coded Decimal Value of Minutes 10-Digit bits Contains a value from 0 to 5.

- bit 19-16 **MINONE<3:0>:** Binary Coded Decimal Value of Minutes 1-Digit bits Contains a value from 0 to 9.

- bit 15-12 **SECTEN<3:0>:** Binary Coded Decimal Value of Seconds 10-Digit bits Contains a value from 0 to 5.

- bit 11-8 **SECONE<3:0>:** Binary Coded Decimal Value of Seconds 1-Digit bits Contains a value from 0 to 9.

- bit 7-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 | -                 | —                 | —                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CH0NA<2:0>        |                   |                   | C                 | H0SA<4:0>(1       | )                |                  |

#### REGISTER 16-5: AD1CHS: ADC INPUT SELECT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

- bit 7-5 CH0NA<2:0>: Negative Input Select bits

- 111-001 = Reserved 000 = Negative input is AVss

- bit 4-0 CH0SA<4:0>: Positive Input Select bits<sup>(1)</sup>

- 11111 = Reserved

- 11110 = Positive input is AVDD

- 11101 = Positive input is AVss

- 11100 = Positive input is Band Gap Reference (VBG)

- 11011-01110 = Reserved

- 01101 = Positive input is  $AN13^{(2,3)}$

- 01100 = Positive input is AN12<sup>(2,3)</sup>

- 01011 = Positive input is AN11<sup>(2)</sup>

- 01010 = Positive input is AN10

- 01001 = Positive input is AN9

- 01000 = Positive input is AN8

- 00111 = Positive input is AN7

- 00110 = Positive input is AN6

- 00101 = Positive input is AN5

- 00100 = Positive input is AN4 00011 = Positive input is AN3

- 00011 = Positive input is AN3 00010 = Positive input is AN2

- 00001 = Positive input is AN2

- 00000 = Positive input is AN0

- **Note 1:** The CH0SA<4:0> positive input selection is only used when CSCNA (AD1CON2<10>) = 0 and ASEN (AD1CON5<15>) = 0. The AD1CSS bits specify the positive inputs when CSCNA = 1 or ASEN = 1.

- 2: This option is not implemented in the 20-pin devices.

- 3: This option is not implemented in the 28-pin devices.

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (CONTINUED)

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin and is compared with 1.2V band gap) 1110 = VDD trip point is  $2.11V^{(1)}$

- 1101 = VDD trip point is  $2.21V^{(1)}$

- 1100 = VDD trip point is 2.30V<sup>(1)</sup>

- 1011 = VDD trip point is 2.40V<sup>(1)</sup>

- 1010 = VDD trip point is  $2.52V^{(1)}$

- 1001 = VDD trip point is 2.63V<sup>(1)</sup>

- $1000 = \text{VDD trip point is } 2.82\text{V}^{(1)}$

- 0111 = VDD trip point is  $2.92V^{(1)}$

- $0110 = VDD trip point is <math>3.13V^{(1)}$

- 0101 = VDD trip point is  $3.44V^{(1)}$

- 0100-0000 = Reserved; do not use

- Note 1: The voltage is typical. It is for design guidance only and not tested. Refer to Table 26-13 in Section 26.0 "Electrical Characteristics" for minimum and maximum values.

# 23.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Programming and Diagnostics" (DS61129) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

# 23.1 Configuration Bits

PIC32MM0064GPL036 family devices contain a Boot Flash Memory (BFM) with an associated configuration space. All Configuration Words are listed in Table 23-3 and Table 23-4; Register 23-1 through Register 23-6 describe the configuration options.

# 23.2 Code Execution from RAM

PIC32MM0064GPL036 family devices allow executing the code from RAM. The starting boundary of this special RAM space can be adjusted using the EXECADDR<7:0> bits in the CFGCON register with a 1-Kbyte step. Writing a non-zero value to these bits will move the boundary, effectively reducing the total amount of program memory space in RAM. Refer to Table 23-5 and Register 23-7 for more information.

## 23.3 Device ID

The Device ID identifies the device used. The ID can be read from the DEVID register. The Device IDs for PIC32MM0064GPL036 family devices are listed in Table 23-1. Also refer to Table 23-5 and Register 23-8 for more information.

#### TABLE 23-1: DEVICE IDs FOR PIC32MM0064GPL036 FAMILY DEVICES

| -                 | -          |

|-------------------|------------|

| Device            | DEVID      |

| PIC32MM0016GPL020 | 0x06B04053 |

| PIC32MM0032GPL020 | 0x06B0C053 |

| PIC32MM0064GPL020 | 0x06B14053 |

| PIC32MM0016GPL028 | 0x06B02053 |

| PIC32MM0032GPL028 | 0x06B0A053 |

| PIC32MM0064GPL028 | 0x06B12053 |

| PIC32MM0016GPL036 | 0x06B06053 |

| PIC32MM0032GPL036 | 0x06B0E053 |

| PIC32MM0064GPL036 | 0x06B16053 |

# 23.4 System Registers Write Protection

The critical registers in the PIC32MM0064GPL036 family devices are protected (locked) from an accidental write. If the registers are locked, a special unlock sequence is required to modify the content of these registers.

To unlock the registers, the following steps should be done:

- 1. Disable interrupts prior to the system unlock sequence.

- 2. Execute the system unlock sequence by writing the key values of 0xAA996655 and 0x556699AA to the SYSKEY register, in two back-to-back assembly or 'C' instructions.

- 3. Write the new value to the required register.

- 4. Write a non-key value (such as 0x0000000) to the SYSKEY register to perform a lock.

- 5. Re-enable interrupts.

The registers that require this unlocking sequence are listed in Table 23-2.

| Register<br>Name | Register Description                   | Peripheral |

|------------------|----------------------------------------|------------|

| OSCCON           | Oscillator Control                     | Oscillator |

| SPLLCON          | System PLL Control                     | Oscillator |

| OSCTUN           | FRC Tuning                             | Oscillator |

| PMDCON           | Peripheral Module<br>Disable Control   | PMD        |

| RSWRST           | Software Reset                         | Reset      |

| RPCON            | Peripheral Pin Select<br>Configuration | I/O Ports  |

| RNMICON          | Non-Maskable Interrupt<br>Control      | Reset      |

| PWRCON           | Power Control                          | Reset      |

| RTCCON1          | RTCC Control 1                         | RTCC       |

TABLE 23-2:SYSTEM LOCKED REGISTERS

The SYSKEY register read value indicates the status. A value of '0' indicates the system registers are locked. A value of '1' indicates the system registers are unlocked. For more information about the SYSKEY register, refer to Table 23-5 and Register 23-9.

<sup>© 2015-2016</sup> Microchip Technology Inc.

NOTES:

# PIC32MM0064GPL036 FAMILY

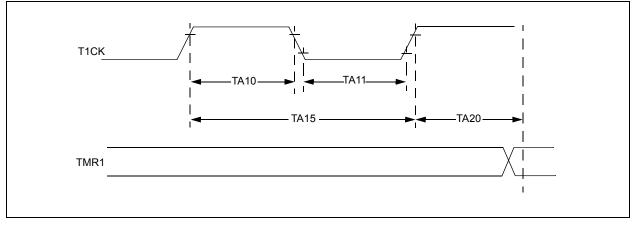

### FIGURE 26-5: TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

#### TABLE 26-23: MCCP/SCCP TIMER1 EXTERNAL CLOCK TIMING CHARACTERISTICS

| <b>Operating Conditions:</b> $2.0V \le VDD \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |           |                                                           |                        |     |     |        |                               |

|-------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------|------------------------|-----|-----|--------|-------------------------------|

| Param.<br>No.                                                                                                           | Symbol    | Characte                                                  | ristics <sup>(1)</sup> | Min | Max | Units  | Conditions                    |

| TA10                                                                                                                    | Тскн      | T1CK High Time                                            | Synchronous            | 1   | _   | TPBCLK | Must also meet Parameter TA15 |

|                                                                                                                         |           |                                                           | Asynchronous           | 10  | _   | ns     |                               |

| TA11                                                                                                                    | TCKL      | T1CK Low Time                                             | Synchronous            | 1   | _   | TPBCLK | Must also meet Parameter TA15 |

|                                                                                                                         |           |                                                           | Asynchronous           | 10  | _   | ns     |                               |

| TA15                                                                                                                    | Тскр      | T1CK Input                                                | Synchronous            | 2   | _   | TPBCLK |                               |

|                                                                                                                         | Period    | Asynchronous                                              | 20                     | _   | ns  |        |                               |

| TA20                                                                                                                    | TCKEXTMRL | Delay from External T1CK Clock<br>Edge to Timer Increment |                        |     | 3   | TPBCLK | Synchronous mode              |

**Note 1:** These parameters are characterized but not tested in manufacturing.

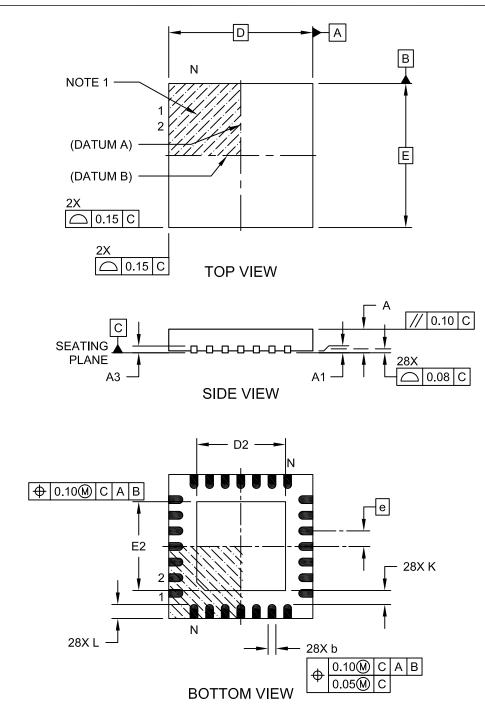

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2

# F

| Fail-Safe Clock Monitor (FSCM) | 65 |

|--------------------------------|----|

| Flash Program Memory           |    |

| Write Protection               |    |

# G

| 19 |

|----|

| 19 |

| 19 |

| 21 |

| 21 |

|    |

| 21 |

|    |

| 21 |

|    |

# н

| High/Low-Voltage Detect (HLVD)1    | 73 |

|------------------------------------|----|

| High/Low-Voltage Detect. See HLVD. |    |

# L

| I/O Ports                              | 77  |

|----------------------------------------|-----|

| Analog/Digital Port Pins Configuration | 78  |

| Open-Drain Configuration               | 78  |

| Parallel I/O (PIO)                     | 78  |

| Pull-up/Pull-Down Pins                 |     |

| Write/Read Timing                      | 78  |

| Input Change Notification (ICN)        | 78  |

| Instruction Set                        | 203 |

| Inter-IC Sound. See I <sup>2</sup> S.  |     |

| Internet Address                       |     |

# Μ

| MCCP/SCCP                                       |     |

|-------------------------------------------------|-----|

| Registers                                       |     |

| Memory Maps                                     |     |

| Devices with 16 Kbytes Program Memory           |     |

| Devices with 32 Kbytes Program Memory           |     |

| Devices with 64 Kbytes Program Memory           |     |

| Memory Organization                             |     |

| Alternate Configuration Bits Space              |     |

| Microchip Internet Web Site                     |     |

| MIPS32® microAptiv™ UC Core Configuration       |     |

| MPLAB Assembler, Linker, Librarian              |     |

| MPLAB ICD 3 In-Circuit Debugger                 | 201 |

| MPLAB PM3 Device Programmer                     | 201 |

| MPLAB REAL ICE In-Circuit Emulator System       | 201 |

| MPLAB X Integrated Development                  |     |

| Environment Software                            |     |

| MPLAB X SIM Software Simulator                  | 201 |

| MPLIB Object Librarian                          | 200 |

| MPLINK Object Linker                            | 200 |

| Multiply/Divide Unit Latencies and Repeat Rates |     |

| 0                                               |     |

| Oscillator Configuration                        | 65  |

| Р                                               |     |

| Package Thermal Resistance                      | 206 |

| Packaging                                       |     |

| Details                                         |     |

| Marking                                         |     |

| Peripheral Pin Select (PPS)                     |     |

| PICkit 3 In-Circuit Debugger/Programmer         |     |

Pinout Description ......14

| Power-Saving Features                     | 177 |

|-------------------------------------------|-----|

| Idle Mode                                 | 177 |

| Low-Power Brown-out Reset                 | 179 |

| On-Chip Voltage Regulator Low-Power Modes | 179 |

| Regulator Retention                       | 179 |

| Regulator Standby                         | 179 |

| Peripheral Module Disable                 |     |

| Sleep Mode                                |     |

| PPS                                       |     |

| Available Peripherals                     | 79  |

| Available Pins                            |     |

| Controlling                               |     |

| Controlling Configuration Changes         |     |

| Input Mapping                             |     |

| Input Pin Selection                       |     |

| Output Mapping                            |     |

| Output Pin Selection                      |     |

| Programming and Diagnostics               |     |

|                                           |     |

## R

| Real-Time Clock and Calendar (RTCC)          | 123 |

|----------------------------------------------|-----|

| Real-Time Clock and Calendar. See RTCC.      |     |

| Register Map                                 |     |

| ADC                                          | 135 |

| Alternate Configuration Words Summary        | 184 |

| Band Gap                                     | 195 |

| CDAC                                         |     |

| CLC1 and CLC2                                | 155 |

| Comparator 1 and 2                           | 164 |

| Configurations Words Summary                 |     |

| CRC                                          | 148 |

| Flash Controller                             | 38  |

| High/Low Voltage Detect                      | 174 |

| Interrupts                                   |     |

| MCCP/SCCP                                    |     |

| Oscillator Configuration                     | 67  |

| Peripheral Module Disable                    |     |

| Peripheral Pin Select                        |     |

| PORTA                                        | 82  |

| PORTB                                        |     |

| PORTC                                        | 84  |

| RAM Configuration, Device ID and System Lock | 192 |

| Reserved Registers                           |     |

| Resets                                       |     |

| RTCC                                         | 124 |

| SPI1 and SPI2                                |     |

| Timer1                                       |     |

| UART1 and UART2                              | 118 |

| UDID                                         | 197 |

| Watchdog Timer                               |     |

| Registers                                    |     |

| AD1CHIT (ADC Compare Hit)                    | 145 |

| AD1CHS (ADC Input Select)                    |     |

| AD1CON1 (ADC Control 1)                      |     |

| AD1CON2 (ADC Control 2)                      |     |

| AD1CON3 (ADC Control 3)                      |     |

| AD1CON5 (ADC Control 5)                      |     |

| AD1CSS (ADC Input Scan Select)               |     |

| ALMDATE (Alarm Date)                         |     |

| ANCFG (Band Gap Control)                     |     |

| CCPxCON1 (Capture/Compare/PWMx               |     |

| Control 1)                                   |     |

| CCPxCON2 (Capture/Compare/PWMx               |     |

| Control 2)                                   | 102 |

|                                              |     |

# **PRODUCT IDENTIFICATION SYSTEM**

| To order or obtain info                                        | rmation, e.g., on pricing or delivery, refer to the factory or the listed sales o                | office.                                                                                                                                                             |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family<br>Key Feature Set _<br>Pin Count<br>Tape and Reel Flag |                                                                                                  | Example:<br>PIC32MM0064GPL036-I/M2:<br>PIC32 General Purpose Device<br>with MIPS32 <sup>®</sup> microAptiv™ UC<br>Core, 64-Kbyte Program Memory,<br>36-Pin Package. |

| Architecture                                                   | MM = MIPS32 <sup>®</sup> microAptiv™ UC CPU Core                                                 |                                                                                                                                                                     |

| Flash Memory Size                                              | 0016 = 16 Kbytes<br>0032 = 32 Kbytes<br>0064 = 64 Kbytes                                         |                                                                                                                                                                     |

| Family                                                         | GP = General Purpose Family                                                                      |                                                                                                                                                                     |

| Key Feature                                                    | L = Up to 25 MHz operating frequency with basic peripheral set of 2 UART<br>and 2 SPI modules    |                                                                                                                                                                     |

| Pin Count                                                      | 020 = 20-pin<br>028 = 28-pin<br>036 = 36/40-pin                                                  |                                                                                                                                                                     |

| Pattern                                                        | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample |                                                                                                                                                                     |