Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | <u>.</u>                                                                         |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10/12b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 40-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 40-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpl036-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MM0064GPL036 FAMILY

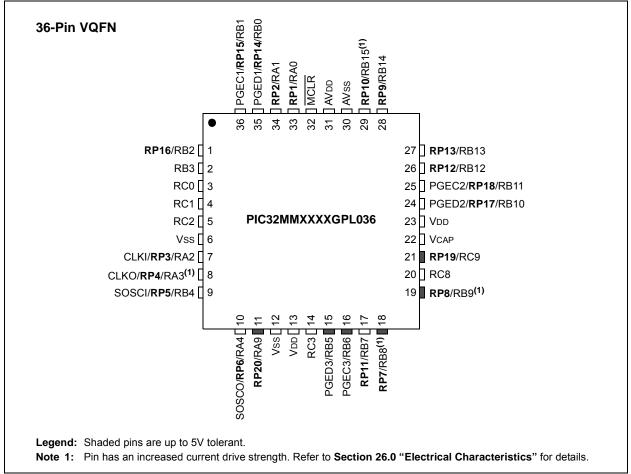

### Pin Diagrams (Continued)

#### TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN VQFN DEVICES

| Pin | Function                                            | Pin | Function                                                                       |

|-----|-----------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                         | 19  | TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | AN11/C1INA/RB3                                      | 20  | RC8                                                                            |

| 3   | AN12/RC0                                            | 21  | RP19/RC9                                                                       |

| 4   | AN13/RC1                                            | 22  | VCAP                                                                           |

| 5   | RC2                                                 | 23  | VDD                                                                            |

| 6   | Vss                                                 | 24  | PGED2/TDO/ <b>RP17</b> /RB10                                                   |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                         | 25  | PGEC2/TDI/ <b>RP18</b> /RB11                                                   |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 26  | AN7/LVDIN/ <b>RP12</b> /RB12                                                   |

| 9   | SOSCI/ <b>RP5</b> /RB4                              | 27  | AN8/ <b>RP13</b> /RB13                                                         |

| 10  | SOSCO/SCLKI/ <b>RP6</b> /PWRLCLK/RA4                | 28  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                          |

| 11  | <b>RP20</b> /RA9                                    | 29  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>            |

| 12  | Vss                                                 | 30  | AVss                                                                           |

| 13  | Vdd                                                 | 31  | AVDD                                                                           |

| 14  | RC3                                                 | 32  | MCLR                                                                           |

| 15  | PGED3/RB5                                           | 33  | VREF+/AN0/RP1/OCM1E/INT3/RA0                                                   |

| 16  | PGEC3/RB6                                           | 34  | Vref-/AN1/ <b>RP2</b> /OCM1F/RA1                                               |

| 17  | <b>RP11</b> /RB7                                    | 35  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                                        |

| 18  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>         | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                                        |

Note 1: Pin has an increased current drive strength.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | NVMDATAx<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMDATAx<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMDATAx<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMDA             | TAx<7:0>          |                   |                  |                  |  |  |

#### **REGISTER 5-4: NVMDATAX: NVM FLASH DATA x REGISTER (x = 0-1)**

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 NVMDATAx<31:0>: NVM Flash Data x bits

Double-Word Program: Writes NVMDATA1:NVMDATA0 to the target Flash address defined in NVMADDR. NVMDATA0 contains the least significant instruction word.

#### REGISTER 5-5: NVMSRCADDR: NVM SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 NVMSRCADDR<31:0>: NVM Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|---------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R/W-1                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | PWPULOCK                  | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |

| 00.40        | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | PWP<23:16> <sup>(2)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | PWP<15:8> <sup>(2)</sup>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                           |                   |                   | PWP<7             | ′:0> <b>(2)</b>   |                   |                  |                  |  |  |

#### NVMPWP: NVM PROGRAM FLASH WRITE-PROTECT REGISTER<sup>(1)</sup> **REGISTER 5-6:**

#### Lonond

| Legena:           |                  |                                         |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31 PWPULOCK: Program Flash Memory Page Write-Protect Unlock bit

- 1 = Register is not locked and can be modified

- 0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any Reset.

- bit 30-24 Unimplemented: Read as '0'

- bit 23-0 PWP<23:0>: Flash Program Write-Protect (Page) Address bits<sup>(2)</sup>

Physical memory below address, 0x1DXXXXXX, is write-protected, where 'XXXXXX' is specified by PWP<23:0>. When the PWP<23:0> bits have a value of '0', write protection is disabled for the entire Program Flash Memory. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

- Note 1: Writes to this register require an NVMKEY unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

- 2: These bits can be modified only when the unlock bit (PWPULOCK) is set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|---------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 31:24        | _                 |                   | —                 | _                 | _                 | _                   | _                   | —                   |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 23:16        | —                 | _                 | _                 | -                 | _                 | —                   | _                   | _                   |

| 45.0         | R/W-1             | U-0               | U-0               | U-0               | U-0               | R/W-1               | R/W-1               | R/W-1               |

| 15:8         | BWPULOCK          | _                 | _                 | _                 | _                 | BWP2 <sup>(2)</sup> | BWP1 <sup>(2)</sup> | BWP0 <sup>(2)</sup> |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |

| 7:0          |                   |                   | _                 | _                 | _                 |                     | _                   | —                   |

# REGISTER 5-7: NVMBWP: NVM BOOT FLASH (PAGE) WRITE-PROTECT REGISTER<sup>(1)</sup>

#### Legend:

| 9                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BWPULOCK:** Boot Alias Write-Protect Unlock bit

- 1 = BWPx bits are not locked and can be modified

- 0 = BWPx bits are locked and cannot be modified

- This bit is only clearable and cannot be set except by any Reset.

- bit 14-11 Unimplemented: Read as '0'

- bit 10 **BWP2:** Boot Alias Page 2 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC00000 through 0x1FC007FF, is enabled 0 = Write protection for physical address, 0x1FC00000 through 0x1FC007FF, is disabled

- bit 9 **BWP1:** Boot Alias Page 1 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC00800 through 0x1FC00FFF, is enabled

- 0 = Write protection for physical address, 0x1FC00800 through 0x1FC00FFF, is disabled

- bit 8 **BWP0:** Boot Alias Page 0 Write-Protect bit<sup>(2)</sup>

- 1 = Write protection for physical address, 0x1FC01000 through 0x1FC017FF, is enabled

- 0 = Write protection for physical address, 0x1FC01000 through 0x1FC017FF, is disabled

- bit 7-0 Unimplemented: Read as '0'

- Note 1: Writes to this register require an NVMKEY unlock sequence. Refer to Section 5.1 "Flash Controller Registers Write Protection" for details.

- 2: These bits can be modified only when the associated unlock bit (BWPULOCK) is set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | ROTRIM<8:1>       |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

#### **REGISTER 8-4: REFO1TRIM: REFERENCE OSCILLATOR TRIM REGISTER**<sup>(1,2,3)</sup>

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

- bit 22-0 Unimplemented: Read as '0'

- **Note 1:** While the ON bit (REFO1CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- Do not write to this register when the ON bit (REFO1CON<15>) is not equal to the ACTIVE bit (REFO1CON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> (REFO1CON<30:16>) = 0.

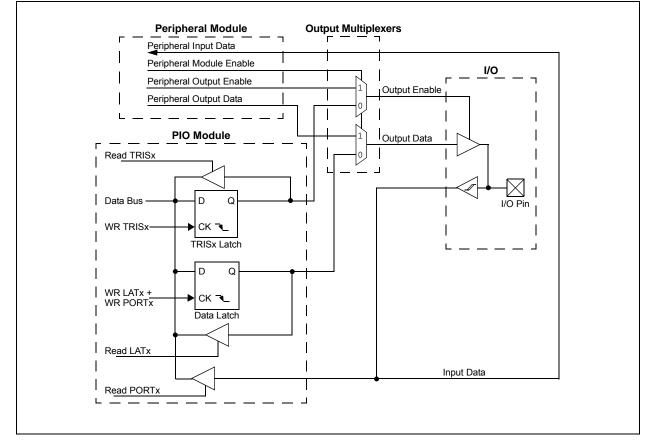

### 9.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

Many of the device pins are shared among the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. Some pins in the devices are 5V tolerant pins. Some of the key features of the I/O ports are:

- Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change-in-Pin State is Detected

- Operation during Sleep and Idle modes

- Fast Bit Manipulation using the CLR, SET and INV registers

Figure 9-1 illustrates a block diagram of a typical multiplexed I/O port.

#### FIGURE 9-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | _                 | CNSTYLE           | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 |                   | _                 |                   |                   |                  |                  |

#### **REGISTER 9-1:** CNCONX: CHANGE NOTIFICATION CONTROL FOR PORTX REGISTER (x = A-C)

| -n = Value at POR | '1' = Bit is set |

|-------------------|------------------|

|                   |                  |

Legend:

R = Readable bit

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notification (CN) Control On bit

1 = CN is enabled

0 = CN is disabled

#### bit 14-12 Unimplemented: Read as '0'

bit 11 **CNSTYLE:** Change Notification Style Selection bit

1 = Edge style (detects edge transitions, CNFx bits are used for a Change Notice event)

W = Writable bit

Mismatch style (detects change from last PORTx read, CNSTATx bits are used for a Change Notification event)

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

bit 10-0 Unimplemented: Read as '0'

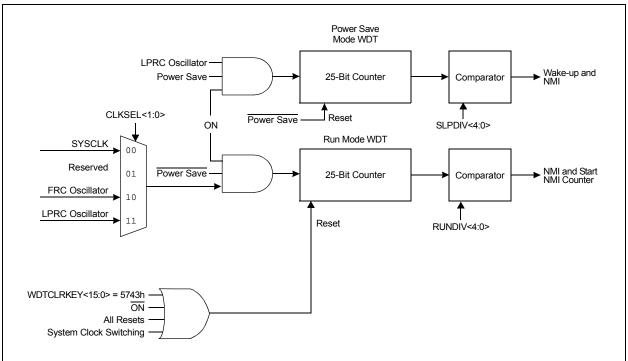

# 11.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

FIGURE 11-1: WATCHDOG TIMER BLOCK DIAGRAM

# 11.1 Watchdog Timer Control Registers

### TABLE 11-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | ø         |       |       |       |       |       |           |      |      | Bits    |        |      |      |           |      |      |          | s         |

|---------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-----------|------|------|---------|--------|------|------|-----------|------|------|----------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7    | 22/6   | 21/5 | 20/4 | 19/3      | 18/2 | 17/1 | 16/0     | All Reset |

| 2500                      | WDTCON <sup>(1)</sup> | 31:16     |       |       |       |       |       |           |      | WDTC | LRKEY<1 | 5:0>   |      |      |           |      |      |          | 0000      |

| 3E80                      | WDICON                | 15:0      | ON    |       | _     |       | RI    | JNDIV<4:( | )>   |      | CLKSE   | L<1:0> |      | SI   | LPDIV<4:0 | >    |      | WDTWINEN | xxxx      |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

#### REGISTER 13-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = SSx pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                                        |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul><li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li><li>0 = SDIx pin is controlled by the SPIx module</li></ul>                                                                                                                                                                                                                                          |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> <li>00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)</li> </ul>                                                          |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 26.0 "Electrical Characteristics"</b> for maximum clock frequency requirements.                                                                                                                                                                                                                                           |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 9.8 "Peripheral Pin Select (PPS)" for more information).

# 15.1 RTCC Control Registers

### TABLE 15-1: RTCC REGISTER MAP

| ess                         |                                 | 6         |        |       |          |         |        |       |        |      | Bits                    |      |            |        |        |      |          |         | ú          |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|---------|--------|-------|--------|------|-------------------------|------|------------|--------|--------|------|----------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12   | 27/11  | 26/10 | 25/9   | 24/8 | 23/7                    | 22/6 | 21/5       | 20/4   | 19/3   | 18/2 | 17/1     | 16/0    | All Resets |

| 0000                        | RTCCON1                         | 31:16     | ALRMEN | CHIME | -        |         |        | AMASK | <3:0>  |      |                         |      |            | ALMRP  | T<7:0> |      |          |         | 0000       |

| 0000                        | RICCONT                         | 15:0      | ON     | _     | _        |         | WRLOCK | _     | —      |      | RTCOE                   |      | OUTSEL<2:0 | >      | —      | —    | _        | —       | 0000       |

| 0010                        | RTCCON2                         | 31:16     |        |       |          |         |        |       |        | DI   | V<15:0>                 |      |            |        |        |      |          |         | 0000       |

| 0010                        | RICCONZ                         | 15:0      |        |       | FDIV<4:0 | )>      |        | —     | —      | _    | —                       | —    | —          | —      | —      | —    | CLKSE    | L<1:0>  | 0000       |

| 0030                        | RTCSTAT                         | 31:16     | —      | —     | _        | _       | —      | _     | —      | _    | —                       | _    | —          | —      | —      | —    | —        | —       | 0000       |

| 0000                        | RIGOLAI                         | 15:0      | —      | —     | —        | —       | —      | _     | —      | —    | —                       | _    | ALMEVT     | —      | —      | SYNC | ALMSYNC  | HALFSEC | 0000       |

| 0040                        | RTCTIME                         | 31:16     | —      | F     | IRTEN<2  | :0>     |        | HRONE | =<3:0> |      | —                       |      | MINTEN<2:0 | >      |        | MINC | NE<3:0>  | -       | xxxx       |

| 0040                        | RIGHME                          | 15:0      |        | SECTE | N<3:0>   |         |        | SECON | E<3:0> |      | _                       | _    | _          |        | _      | —    | —        | —       | xx00       |

| 0050                        | RTCDATE                         | 31:16     |        | YRTE  | N<3:0>   |         |        | YRONE | <3:0>  |      | _                       | _    | _          | MTHTEN |        | MTHC | DNE<3:0> |         | 0000       |

| 0000                        | RIODAIL                         | 15:0      | —      | —     | DAYT     | EN<1:0> |        | DAYON | E<3:0> |      | —                       | _    | _          | —      | —      |      | WDAY<2:0 | >       | 0000       |

| 0060                        | ALMTIME                         | 31:16     | —      | F     | IRTEN<2  | :0>     |        | HRONE | =<3:0> |      | MINTEN<2:0> MINONE<3:0> |      |            | -      | xxxx   |      |          |         |            |

| 0000                        |                                 | 15:0      |        | SECTE | N<3:0>   |         |        | SECON | E<3:0> |      | —                       | _    | —          | —      | —      | _    | _        | —       | xx00       |

| 0070                        | ALMDATE                         | 31:16     | _      | —     | _        | —       | —      | _     | —      | —    | —                       | _    | —          | MTHTEN |        | MTHC | )NE<3:0> |         | 0000       |

| 0070                        |                                 | 15:0      | _      | —     | DAYTI    | EN<1:0> |        | DAYON | E<3:0> |      | —                       | _    | _          | —      | —      |      | WDAY<2:0 | >       | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

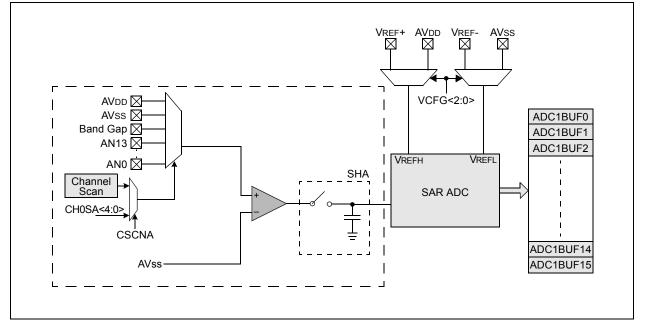

# 16.0 12-BIT ANALOG-TO-DIGITAL CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

#### 16.1 Introduction

The 12-bit ADC Converter with Threshold Detect includes the following features:

- Successive Approximation Register (SAR)

Conversion

- · User-Selectable Resolution of 10 or 12 Bits

- Conversion Speeds of up to 200 ksps for 12-bit mode and 300 ksps for 10-bit mode

- Up to 17 Analog Inputs (internal and external)

#### FIGURE 16-1: ADC BLOCK DIAGRAM

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold Amplifier (SHA)

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length Configurable Conversion Result

Buffer

- · Eight Options for Result Alignment and Encoding

- Configurable Interrupt Generation

- · Operation during CPU Sleep and Idle modes

Figure 16-1 illustrates a block diagram of the 12-bit ADC. The 12-bit ADC has 14 external analog inputs, AN0 through AN13, and 3 internal analog inputs connected to VDD, VSs and band gap. In addition, there are two analog input pins for external voltage reference connections.

The analog inputs are connected through a multiplexer to the SHA. Unipolar differential conversions are possible on all inputs (see Figure 16-1).

The Automatic Input Scan mode sequentially converts multiple analog inputs. A special control register specifies which inputs will be included in the scanning sequence. The 12-bit ADC is connected to a 16-word result buffer. The 12-bit result is converted to one of eight output formats in either 32-bit or 16-bit word widths.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0              | U-0              |

| 31:24        |                   | _                 | —                 |                   | _                   | _                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | —                 | —                 | G4POL               | G3POL               | G2POL            | G1POL            |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | INTP <sup>(1)</sup> | INTN <sup>(1)</sup> |                  | _                |

| 7.0          | R/W-0             | R-0, HS, HC       | R/W-0             | U-0               | U-0                 | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | LCOE              | LCOUT             | LCPOL             | _                 | _                   |                     | MODE<2:0>        |                  |

### REGISTER 18-1: CLCxCON: CLCx CONTROL REGISTER

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable | e bit              |

|-------------------|-----------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-20 Unimplemented: Read as '0'

bit 19 **G4POL:** Gate 4 Polarity Control bit 1 = The output of Channel 4 logic is inverted when applied to the logic cell 0 = The output of Channel 4 logic is not inverted

#### bit 18 **G3POL:** Gate 3 Polarity Control bit

- 1 = The output of Channel 3 logic is inverted when applied to the logic cell

- 0 = The output of Channel 3 logic is not inverted

#### bit 17 G2POL: Gate 2 Polarity Control bit

1 = The output of Channel 2 logic is inverted when applied to the logic cell0 = The output of Channel 2 logic is not inverted

# bit 16 **G1POL:** Gate 1 Polarity Control bit

- 1 = The output of Channel 1 logic is inverted when applied to the logic cell

- 0 = The output of Channel 1 logic is not inverted

#### bit 15 ON: CLCx Enable bit

- 1 = CLCx is enabled and mixing input signals

- 0 = CLCx is disabled and has logic zero outputs

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 INTP: CLCx Positive Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a rising edge occurs on LCOUT

- 0 = Interrupt will not be generated

- bit 10 INTN: CLCx Negative Edge Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt will be generated when a falling edge occurs on LCOUT0 = Interrupt will not be generated

- bit 9-8 Unimplemented: Read as '0'

- bit 7 LCOE: CLCx Port Enable bit

- 1 = CLCx port pin output is enabled

- 0 = CLCx port pin output is disabled

- bit 6 LCOUT: CLCx Data Output Status bit

- 1 = CLCx output high 0 = CLCx output low

- Note 1: The INTP and INTN bits should not be set at the same time for proper interrupt functionality.

# PIC32MM0064GPL036 FAMILY

### REGISTER 23-10: ANCFG: BAND GAP CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   |                   | —                 |                   | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | —                 |                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 |                   | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS, HC     | R/W-0, HS, HC    | U-0              |

| 7:0          | —                 |                   |                   |                   |                   | VBGADC            | VBGCMP           | _                |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

- bit 2 **VBGADC:** ADC Band Gap Enable bit

- 1 = ADC band gap is enabled

- 0 = ADC band gap is disabled

bit 1 **VBGCMP:** Comparator Band Gap Enable bit

- 1 = Comparator band gap is enabled

- 0 = Comparator band gap is disabled

- bit 0 Unimplemented: Read as '0'

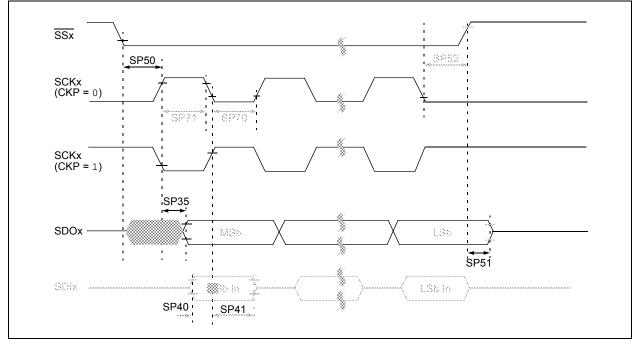

| Operating     | Conditions: 2.0       | $\textrm{V} \leq \textrm{VDD} \leq 3.6\textrm{V},~\textrm{-}40^{\circ}\textrm{C} \leq \textrm{Ta} \leq \textrm{+}85^{\circ}\textrm{C}$ (unless otherwise | e stated) |     |       |

|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                           | Min       | Max | Units |

| SP10          | TscL, TscH            | SCKx Output Low or High Time                                                                                                                             | 10        | —   | ns    |

| SP35          | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                                                                                                                   | —         | 7   | ns    |

| SP36          | TDOV2sc,<br>TDOV2scL  | SDOx Data Output Setup to First SCKx Edge                                                                                                                | 7         | —   | ns    |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                               | 7         | —   | ns    |

| SP41          | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                | 7         | —   | ns    |

#### TABLE 26-28: SPIX MODULE MASTER MODE TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

#### FIGURE 26-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

NOTES:

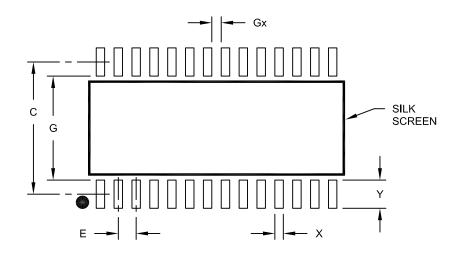

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units            |          |      |      |  |  |

|--------------------------|------------------|----------|------|------|--|--|

| Dimension                | Dimension Limits |          |      |      |  |  |

| Contact Pitch            | E                | 1.27 BSC |      |      |  |  |

| Contact Pad Spacing      | С                |          | 9.40 |      |  |  |

| Contact Pad Width (X28)  | X                |          |      | 0.60 |  |  |

| Contact Pad Length (X28) | Y                |          |      | 2.00 |  |  |

| Distance Between Pads    | Gx               | 0.67     |      |      |  |  |

| Distance Between Pads    | G                | 7.40     |      |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

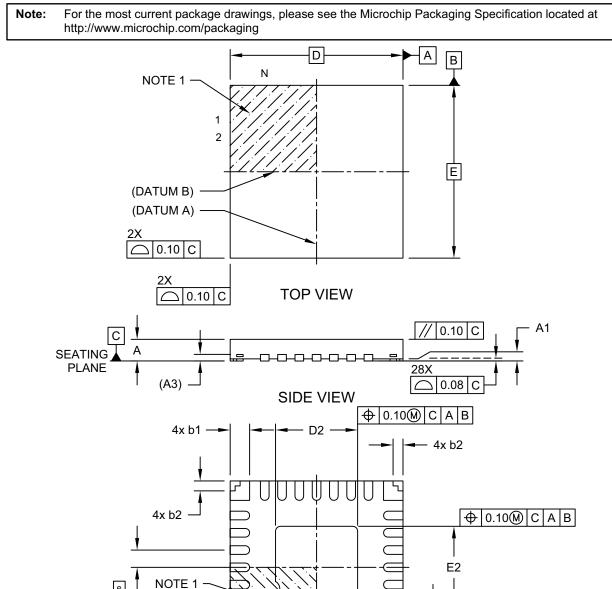

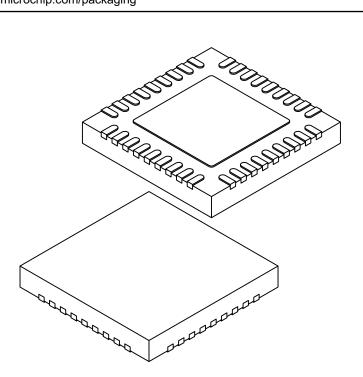

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

<u>e</u>2

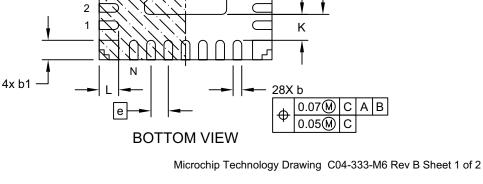

# 36-Terminal Very Thin Plastic Quad Flatpack No-Lead (M2) - 6x6x1.0mm Body [VQFN] SMSC Legacy "Sawn Quad Flatpack No-Lead [SQFN]"

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units    | MILLIMETERS |          |      |  |  |  |

|-------------------------|----------|-------------|----------|------|--|--|--|

| Dimensior               | n Limits | MIN         | NOM      | MAX  |  |  |  |

| Number of Terminals     | Ν        |             | 36       |      |  |  |  |

| Pitch                   | е        |             | 0.50 BSC |      |  |  |  |

| Overall Height          | Α        | 0.80        | 0.90     | 1.00 |  |  |  |

| Standoff                | A1       | 0.00        | 0.02     | 0.05 |  |  |  |

| Terminal Thickness      | A3       | 0.20 REF    |          |      |  |  |  |

| Overall Width           | E        |             | 6.00 BSC |      |  |  |  |

| Exposed Pad Width       | E2       | 3.60        | 3.70     | 3.80 |  |  |  |

| Overall Length          | D        |             | 6.00 BSC |      |  |  |  |

| Exposed Pad Length      | D2       | 3.60        | 3.70     | 3.80 |  |  |  |

| Terminal Width          | b        | 0.18        | 0.25     | 0.30 |  |  |  |

| Terminal Length         | L        | 0.50        | 0.60     | 0.75 |  |  |  |

| Terminal-to-Exposed-Pad | K        | 0.45        | 0.55     | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-272B-M2 Sheet 2 of 2