Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 176-LQFP Exposed Pad                                                                          |

| Supplier Device Package    | 176-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1025dab176t-i-2j             |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 7: PIN NAMES FOR 288-PIN DEVICES (CONTINUED)

| 288-P                | IN LFBGA (BOTTOM VIE                                                                                           | N)  |   |                    |                      |          |

|----------------------|----------------------------------------------------------------------------------------------------------------|-----|---|--------------------|----------------------|----------|

|                      |                                                                                                                | A1  |   |                    | V1                   |          |

| PI                   | C32MZ1025DAA288<br>C32MZ1025DAB288<br>C32MZ1064DAA288                                                          | F6  |   |                    | N6                   |          |

| PI<br>PI<br>PI<br>PI | C32MZ1064DAB288<br>C32MZ2025DAA288<br>C32MZ2025DAB288<br>C32MZ2025DAB288<br>C32MZ2064DAA288<br>C32MZ2064DAB288 | F13 |   |                    | N1                   | 3<br>V18 |

|                      | Polarity Indica                                                                                                | A1  | 8 |                    |                      |          |

| Ball/Pin<br>Number   | Full Pin Name                                                                                                  |     |   | Ball/Pin<br>Number | Full Pin Name        |          |

| V3                   | DDRA15                                                                                                         |     | - | V11                | ERXDV/ECRSDV/RH13    |          |

| V4                   | VDDCORE                                                                                                        |     |   | V12                | ERXD3/RH9            |          |

| V5                   | RTCC/RPD0/RD0                                                                                                  |     |   | V13                | ETXD2/RH0            |          |

| V6                   | SCK4/RD10                                                                                                      |     |   | V14                | ETXD0/RJ8            |          |

| V7                   | GD6/EBIA11/RPF0/PMA11/RF0                                                                                      |     |   | V15                | ETXERR/RJ0           |          |

| V8                   | GD21/EBIA23/RH15                                                                                               |     |   | V16                | ETXEN/RPD6/RD6       |          |

|                      |                                                                                                                |     |   | V17                | GD1/EBID14/PMD14/RA4 |          |

| V9                   | GD3/EBIA8/RPG0/PMA8/RG0                                                                                        |     |   | V 17               |                      |          |

The RPn pins can be used by remappable peripherals. See Table 1 and Table 4 for the available peripherals and 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See 12.0 "I/O Ports" for more information.

**3:** Shaded pins are 5V tolerant.

4: This pin must be tied to Vss through a 20k  $\Omega$  resistor when DDR is not connected in the system.

5: This pin is a No Connect when DDR is not connected in the system.

6: These pins are restricted to input functions only.

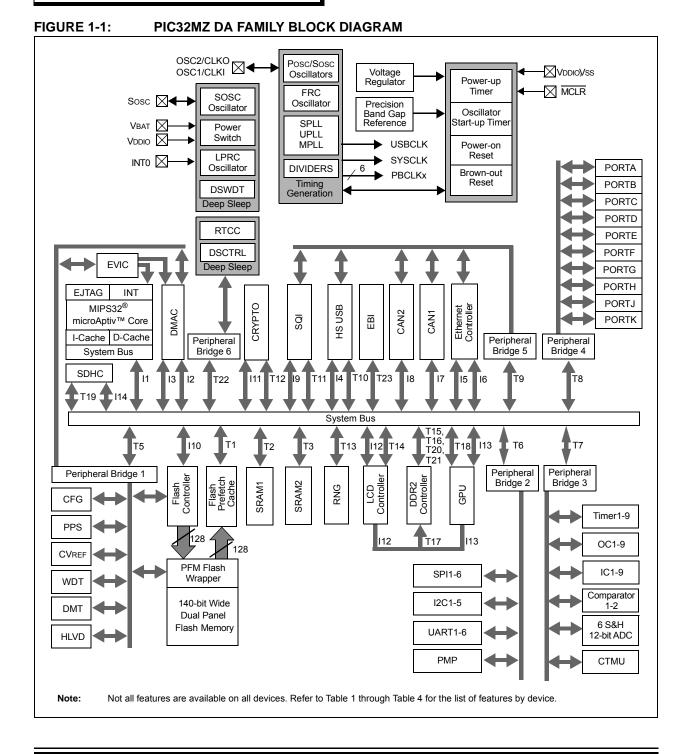

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This data sheet contains device-specific information for the PIC32MZ DA family of devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ DA family of devices.

Table 1-1 through Table 1-24 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 5 through Table 7).

|          |                  | Pin Number        |                  |             | 5.4            |                                                  |

|----------|------------------|-------------------|------------------|-------------|----------------|--------------------------------------------------|

| Pin Name | 169-pin<br>LFBGA | 176-pin<br>LQFP   | 288-pin<br>LFBGA | Pin<br>Type | Buffer<br>Type | Description                                      |

|          |                  |                   | DDR2 S           | SDRAM Co    | ntroller       |                                                  |

| DDRCK    | DDR Internal     | DDR Internal      | K2               | 0           | SSTL           | Differential Clocks                              |

| DDRCK    | to the Package   | to the Package    | K1               | 0           | SSTL           |                                                  |

| DDRCKE   |                  |                   | L2               | 0           | SSTL           | Clock Enable                                     |

| DDRCS0   |                  |                   | N2               | 0           | SSTL           | Chip Select 0                                    |

| DDRRAS   |                  |                   | M1               | 0           | SSTL           | Row Address Strobe                               |

| DDRCAS   |                  |                   | P2               | 0           | SSTL           | Column Address Strobe                            |

| DDRWE    |                  |                   | L1               | 0           | SSTL           | Write Enable Strobe                              |

| DDRLDM   |                  |                   | G3               | 0           | SSTL           | Lower Data Byte Mask                             |

| DDRUDM   |                  |                   | A3               | 0           | SSTL           | Upper Data Byte Mask                             |

| DDRODT   |                  |                   | N1               | 0           | SSTL           | On-Die Termination                               |

| DDRLDQS  |                  |                   | E1               | I/O         | SSTL           | Lower Data Byte Qualifier Strobes (Differential) |

| DDRLDQS  |                  |                   | E2               | I/O         | SSTL           |                                                  |

| DDRUDQS  |                  |                   | B2               | I/O         | SSTL           | Upper Data Byte Qualifier Strobes (Differential) |

| DDRUDQS  |                  |                   | A2               | I/O         | SSTL           |                                                  |

| DDRBA0   |                  |                   | M2               | 0           | SSTL           | Bank Address Select 0                            |

| DDRBA1   |                  |                   | M3               | 0           | SSTL           | Bank Address Select 1                            |

| DDRBA2   |                  |                   | U4               | 0           | SSTL           | Bank Address Select 2                            |

| DDRA0    |                  |                   | R1               | 0           | SSTL           | DDR2 Address Bus                                 |

| DDRA1    |                  |                   | L3               | 0           | SSTL           | -                                                |

| DDRA2    |                  |                   | N3               | 0           | SSTL           |                                                  |

| DDRA3    |                  |                   | R2               | 0           | SSTL           | -                                                |

| DDRA4    |                  |                   | P3               | 0           | SSTL           |                                                  |

| DDRA5    |                  |                   | T1               | 0           | SSTL           |                                                  |

| DDRA6    |                  |                   | U1               | 0           | SSTL           |                                                  |

| DDRA7    |                  |                   | T2               | 0           | SSTL           |                                                  |

| DDRA8    |                  |                   | U2               | 0           | SSTL           |                                                  |

| DDRA9    |                  |                   | R3               | 0           | SSTL           |                                                  |

| DDRA10   | ]                |                   | P1               | 0           | SSTL           |                                                  |

| DDRA11   | ]                |                   | V2               | 0           | SSTL           |                                                  |

| DDRA12   |                  |                   | Т3               | 0           | SSTL           |                                                  |

| DDRA13   |                  |                   | U3               | 0           | SSTL           |                                                  |

| DDRA14   | ]                | ļ [               | T4               | 0           | SSTL           |                                                  |

| DDRA15   |                  | <b>_</b>          | V3               | 0           | SSTL           | ]                                                |

| Legend:  | CMOS = CMOS      | -compatible input | or output        | Analog = A  | nalog input    | P = Power                                        |

### **TABLE 1-22:** DDR2 SDRAM CONTROLLER PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output

9.....

I = Input

TTL = Transistor-transistor Logic input buffer PPS = Peripheral Pin Select SSTL = Stub Series Terminated Logic

#### SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS (CONTINUED) **TABLE 4-8:**

|                                |                                    |           | :                                           | SBTxREGy Reg                 | jister (see Note                           | 7)             |                   |                   | SBTxRD   | y Register                                                      | SBTxWR   | / Register                                                       |

|--------------------------------|------------------------------------|-----------|---------------------------------------------|------------------------------|--------------------------------------------|----------------|-------------------|-------------------|----------|-----------------------------------------------------------------|----------|------------------------------------------------------------------|

| Target<br>Protection<br>Number | Target Description<br>(see Note 5) | Name      | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size | Priority<br>(PRI) | Priority<br>Level | Name     | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name     | Write<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

| 14                             | DSCTRL                             | SBT14REG0 | R                                           | 0x1F8C0000                   | R                                          | 4 KB           | _                 | 0                 | SBT14RD0 | R/W <sup>(1)</sup>                                              | SBT14WR0 | R/W <sup>(1)</sup>                                               |

|                                | RTCC                               | SBT14REG1 | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT14RD1 | R/W <sup>(1)</sup>                                              | SBT14WR1 | R/W <sup>(1)</sup>                                               |

| 15                             | USB                                | SBT15REG0 | R                                           | 0x1F8E0000                   | R                                          | 4 KB           | —                 | 0                 | SBT15RD0 | R/W <sup>(1)</sup>                                              | SBT15WR0 | R/W <sup>(1)</sup>                                               |

|                                | Crypto                             |           | R                                           | 0x1F8E5000                   | R                                          | 4 KB           | _                 | 0                 |          | R/W <sup>(1)</sup>                                              |          | R/W <sup>(1)</sup>                                               |

|                                | RNG                                |           | R                                           | 0x1F8E6000                   | R                                          | 4 KB           | _                 | 0                 |          | R/W <sup>(1)</sup>                                              |          | R/W <sup>(1)</sup>                                               |

|                                | SDHC                               |           | R                                           | 0x1F8EC000                   | R                                          | 4 KB           | —                 | 0                 |          | R/W <sup>(1)</sup>                                              |          | R/W <sup>(1)</sup>                                               |

| 16                             | External Memory via DDR2 and       | SBT16REG0 | R                                           | 0x08000000                   | R                                          | R(4)           | _                 | 0                 | SBT16RD0 | R/W <sup>(1)</sup>                                              | SBT16WR0 | R/W <sup>(1)</sup>                                               |

|                                | DDR2 Targets 3 and 4               | SBT16REG1 | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT16RD1 | R/W <sup>(1)</sup>                                              | SBT16WR1 | R/W <sup>(1)</sup>                                               |

|                                |                                    | SBT16REG2 | R/W                                         | R/W                          | R/W                                        | R/W            | 1                 | 2                 | SBT16RD2 | R/W <sup>(1)</sup>                                              | SBT16WR2 | R/W <sup>(1)</sup>                                               |

|                                |                                    | SBT16REG3 | R/W                                         | R/W                          | R/W                                        | R/W            | 1                 | 2                 | SBT16RD3 | R/W <sup>(1)</sup>                                              | SBT16WR3 | R/W <sup>(1)</sup>                                               |

|                                |                                    | SBT16REG4 | R/W                                         | R/W                          | R/W                                        | R/W            | 1                 | 2                 | SBT16RD4 | R/W <sup>(1)</sup>                                              | SBT16WR4 | R/W <sup>(1)</sup>                                               |

| _egend:                        | R = Read; R/W = Rea                | ad/Write; | 'x' in a registe                            | r name = 0-13;               | 'y' in                                     | a register na  | me = 0-8.         |                   | •        |                                                                 | •        | •                                                                |

Legend:

R = Read; R/W = Read/Write;

Note 1: Reset values for these bits are '0', '1', '1', '1', respectively.

2:

The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset. The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset. 3:

Refer to the Device Memory Map (Figure 4-1) for specific device memory sizes and start addresses. 4:

5: See Table 4-2 for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

7: The 'x' in the SBTxREGy, SBTxRDy, and SBTxWRy registers represents the target protection number and not the actual target number (e.g., for SQI 'x' = 13 and not 11, whereas 11 is the actual target number).

### TABLE 4-10: SYSTEM BUS TARGET PROTECTION GROUP 0 (T0PGV0 - T0PGV3) REGISTER MAP

|                             | LL <del>4</del> -10. | 010       |       | 000   |       |          |          |       | 0 (101 |      | <u>oi oi o</u> , |       |          | -11  |        |        |         |        |               |

|-----------------------------|----------------------|-----------|-------|-------|-------|----------|----------|-------|--------|------|------------------|-------|----------|------|--------|--------|---------|--------|---------------|

| ess                         |                      | 0         |       |       |       |          |          |       |        |      | Bits             |       |          |      |        |        |         |        |               |

| Virtual Address<br>(BF8F_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9   | 24/8 | 23/7             | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             | SBT0ELOG1            | 31:16     | MULTI | —     | —     | —        |          | CODE  | <3:0>  |      | _                |       |          | —    | —      |        | —       |        | 0000          |

| 0020                        | 8020 SBT0ELOG1       |           |       |       |       | INI      | FID<7:0> |       |        |      |                  | REGIO | N<3:0>   |      | —      | С      | MD<2:0> |        | 0000          |

| 8024                        | SBT0ELOG2            | 31:16     |       | —     | _     | _        | _        | _     | _      |      | _                |       |          | _    | —      |        | _       |        | 0000          |

| 0024                        | 3BTUELOG2            | 15:0      |       | —     | _     | _        | _        | _     | _      |      | _                |       |          | _    | —      |        | GROU    | P<1:0> | 0000          |

| 8028                        | SBT0ECON             | 31:16     | _     | —     | —     | —        | —        | —     | —      | ERRP | _                |       | _        | _    | —      |        | _       |        | 0000          |

| 0020                        | SEIVECON             | 15:0      |       | —     | _     | _        | _        | _     | _      |      | _                |       |          | _    | —      |        | _       |        | 0000          |

| 8030                        | SBT0ECLRS            | 31:16     |       | —     | _     | _        | _        | _     | _      |      | _                |       |          | _    | —      |        | _       |        | 0000          |

| 8030                        | SBIUECLKS            | 15:0      |       | —     | _     | _        | _        | _     | _      |      | _                |       |          | _    | —      |        | _       | CLEAR  | 0000          |

| 8038                        | SBT0ECLRM            | 31:16     |       | —     | —     | —        | —        | —     | —      | —    | —                | —     | —        | —    | —      | —      | —       | —      | 0000          |

| 0030                        | SBIULCERM            | 15:0      |       | —     | —     | —        | —        | —     | —      | —    | —                | —     | —        | —    | —      | —      | —       | CLEAR  | 0000          |

| 8040                        | SBT0REG0             | 31:16     |       |       |       |          |          |       |        | BA   | SE<21:6>         |       |          |      |        |        |         |        | xxxx          |

| 0040                        | SBIOKEGO             | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI    | —    |                  |       | SIZE<4:0 | >    |        | —      | —       | —      | xxxx          |

| 8050                        | SBT0RD0              | 31:16     | —     |       | —     | —        | —        | —     | —      | _    | _                | _     | _        | —    | —      | _      | _       | _      | xxxx          |

| 0000                        | SBIORED              | 15:0      | —     |       | —     | —        | —        | —     | —      | _    | _                | _     | _        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8058                        | SBT0WR0              | 31:16     | —     |       | —     | —        | —        | —     | —      | _    | _                | _     | _        | —    | —      | _      | —       |        | xxxx          |

| 0000                        | 36100010             | 15:0      | —     | —     | —     | —        | —        | _     | —      | _    | _                | _     | _        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8060                        | SBT0REG1             | 31:16     |       |       |       |          |          |       |        | BA   | SE<21:6>         |       |          |      |        |        |         |        | xxxx          |

| 0000                        | OBTINEOT             | 15:0      |       |       | BA    | SE<5:0>  |          |       | PRI    | _    |                  |       | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |

| 8070                        | SBT0RD1              | 31:16     | _     | —     | —     | —        | —        | —     | —      | _    | _                | _     | _        | —    | —      | —      | —       | —      | xxxx          |

| 0010                        | GETUKET              | 15:0      | —     | _     | —     | —        | _        | —     | —      | _    | —                | _     | _        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8078                        | SBT0WR1              | 31:16     | —     | _     | —     | —        | _        | —     | —      | _    | —                | _     | _        | —    | —      | _      | —       | _      | xxxx          |

| 0070                        | 00100011             | 15:0      | —     | —     | —     | —        | —        | —     | —      | —    | _                | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

PIC32MZ Graphics (DA) Family

DS60001361F-page 78

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-8 for the actual reset values.

### REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

### bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

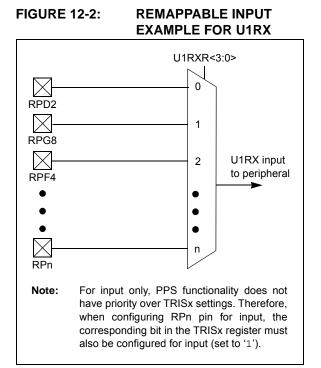

## 12.4.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 12-1, are used to configure peripheral input mapping (see Register 12-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 12-1.

For example, Figure 12-2 illustrates the remappable pin selection for the U1RX input.

## TABLE 12-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection |

|--------------|----------|-------------|---------------------------------------|

| RPD2         | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                     |

| RPG8         | RPG8R    | RPG8R<3:0>  | 0001 = U3TX<br>0010 = U4RTS           |

| RPF4         | RPF4R    | RPF4R<3:0>  | 0011 = Reserved                       |

| RPF1         | RPF1R    | RPF1R<3:0>  | 0100 = Reserved                       |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0101 = SDO1                           |

| RPB10        | RPB10R   | RPB10R<3:0> | 0110 = SDO2<br>0111 = SDO3            |

| RPB5         | RPB5R    | RPB5R<3:0>  | 1000 = Reserved                       |

| RPC1         | RPC1R    | RPC1R<3:0>  | 1001 = SDO5                           |

| RPD14        | RPD14R   | RPD14R<3:0> | 1010 = SS6<br>1011 = OC3              |

| RPG1         | RPG1R    | RPG1R<3:0>  | 1100 <b>=</b> OC6                     |

| RPA14        | RPA14R   | RPA14R<3:0> | 1101 = REFCLKO4                       |

| RPD6         | RPD6R    | RPD6R<3:0>  | 1110 = C2OUT<br>1111 = C1TX           |

| RPD3         | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                     |

| RPG7         | RPG7R    | RPG7R<3:0>  | 0001 = U1TX<br>0010 = U2RTS           |

| RPF5         | RPF5R    | RPF5R<3:0>  | 0011 = U5TX                           |

| RPD11        | RPD11R   | RPD11R<3:0> | 0100 = U6RTS                          |

| RPF0         | RPF0R    | RPF0R<3:0>  |                                       |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0111 = SDO3                           |

| RPE5         | RPE5R    | RPE5R<3:0>  | 1000 = SDO4                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 1001 = SDO5<br>1010 = Reserved        |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1011 = OC4                            |

| RPG0         | RPG0R    | RPG0R<3:0>  | 1100 = OC7<br>1101 = Reserved         |

| RPA15        | RPA15R   | RPA15R<3:0> | 1101 = Reserved                       |

| RPD7         | RPD7R    | RPD7R<3:0>  | 1111 = REFCLKO1                       |

NOTES:

## REGISTER 25-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

### REGISTER 29-32: ADCANCON: ADC ANALOG WARM-UP CONTROL REGISTER (CONTINUED)

- ANEN7: Shared ADC (ADC7) Analog and Bias Circuitry Enable bit

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

- bit 5-6 Unimplemented: Read as '0'

bit 7

- bit 4-0 **ANEN4: ANEN0:** ADC4-ADC0 Analog and Bias Circuitry Enable bits

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            |                   | FSEL15<4:0>       |                   |                  |                  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | FLTEN14           | MSEL1             | 4<1:0>            | FSEL14<4:0>       |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            |                   | F                 | SEL13<4:0>        |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7.0          | FLTEN12           | MSEL1             | 2<1:0>            | FSEL12<4:0>       |                   |                   |                  |                  |  |  |  |  |

## REGISTER 30-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31    | FLTEN15: Filter 15 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected                                                                                          |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

| bit 23    | FLTEN14: Filter 14 Enable bit                                                                                            |

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 20-16 | <b>FSEL14&lt;4:0&gt;:</b> FIFO Selection bits                                                                            |

| 511 20 10 | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           |                                                                                                                          |

|           | 00001 = Message matching filter is stored in EIEO buffer 1                                                               |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 31-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 |                   |                   | _                 | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 |                   |                   | _                 | —                | —                |  |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | HTEN              | MPEN              | —                 | NOTPM             | PMMODE<3:0>       |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |  |

### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **HTEN:** Enable Hash Table Filtering bit

- 1 = Enable Hash Table Filtering

- 0 = Disable Hash Table Filtering

- bit 14 **MPEN:** Magic Packet<sup>™</sup> Enable bit 1 = Enable Magic Packet Filtering 0 = Disable Magic Packet Filtering

- 0 = Disable Magic Packet Filtering

- bit 13 Unimplemented: Read as '0'

- bit 12 NOTPM: Pattern Match Inversion bit

1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 **PMMODE<3:0>:** Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)<sup>(1,3)</sup>

- 1000 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Hash Table Filter match)<sup>(1,1)</sup>

- 0111 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0110 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0101 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0100 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0011 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0010 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches)<sup>(1)</sup>

- 0000 = Pattern Match is disabled; pattern match is always unsuccessful

Note 1: XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | —                 | BPORCHX<10:8>     |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | BPORCHX<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | —                 | _                 | _                 | —                 | BPORCHY<10:8>     |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | BPORCHY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### **REGISTER 36-7:** GLCDBPORCH: GRAPHICS LCD CONTROLLER BACK PORCH REGISTER

# Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 **BPORCHX<10:0>:** X Dimension Back Porch Lines bits These bits specify the front porch X dimension lines.

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **BPORCHY<10:0>:** Y Dimension Back Porch Pixel Clocks bits These bits specify the front porch Y dimension pixel clocks.

## REGISTER 36-8: GLCDCURSOR: GRAPHICS LCD CONTROLLER CURSOR REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | CURSORX<10:8>     |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CURSORX<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | —                 | —                 | _                 | —                 | _                 | CURSORY<10:8>     |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CURSOR            | Y<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 **CURSORX<10:0>:** Cursor X Dimension Position bits These bits specify the X dimension position of the cursor

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **CURSORY<10:0>:** Cursor Y Dimension Position bits These bits specify the Y dimension position of the cursor NOTES:

# TABLE 39-1: SDHC SFR SUMMARY (CONTINUED)

|                    |                  |           |       |                 |       |       |       |       |      |      | Bits       |      |      |      |      |        |       |        |            |

|--------------------|------------------|-----------|-------|-----------------|-------|-------|-------|-------|------|------|------------|------|------|------|------|--------|-------|--------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7       | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1  | 16/0   | All Resets |

| 0054               | SDHC             | 31:16     | _     | _               | -     |       | _     | _     | -    | _    | _          | _    | —    | _    | _    | _      | -     | _      | 0000       |

| C054               |                  | 15:0      | _     | _               | _     | _     | —     | _     | _    | _    | _          | _    | —    | —    |      | ALMERR | AERRS | T<1:0> | 0000       |

| 0050               | SDHC             | 31:16     |       | ADDR<31:16> 000 |       |       |       |       |      |      |            |      | 0000 |      |      |        |       |        |            |

| C058               | 8 AABBB          | 15:0      |       |                 |       |       |       |       |      |      | ADDR<15:0> |      |      |      |      |        |       |        | 0000       |

Legend: '—' = unimplemented; read as '0'.

| REGISTER 39-13: | SDHCCAP: SDHC CAPABILITIES REG | GISTER |

|-----------------|--------------------------------|--------|

|-----------------|--------------------------------|--------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-1, HS          |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | _                 | —                | VOLT3V3          |  |  |

| 00.40        | R-x, HS           | U-0               | R-x, HS           | U-0               | R-x, HS           | U-0               | R-0, HS          | R-0, HS          |  |  |

| 23:16        | SRESUME           | —                 | HISPEED           | —                 | ADMA2             | _                 | MBLE             | N<1:0>           |  |  |

| 15:0         | U-0               | U-0               | R-x, HS           | R-x, HS           | R-x, HS           | R-x, HS           | R-x, HS          | R-x, HS          |  |  |

| 15:8         | —                 | —                 | BASECLK<5:0>      |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | TOCLKU            | _                 |                   |                   | TOCLKF            | REQ<5:0>          |                  |                  |  |  |

| Legend:           |                  | HS = Hardware settable             |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-25 Unimplemented: Read as '0'

- bit 24 VOLT3V3: 3.3V Voltage Support bit

- 1 = Voltage of 3.3V is supported

- bit 23 SRESUME: Suspend/Resume Support bit

- 1 = Suspend/resume is supported

- 0 = Suspend/resume is not supported

- bit 22 Unimplemented: Read as '0'

- bit 21 HISPEED: High-speed Support bit

- 1 = High speed is supported

- 0 = High speed is not supported

- bit 20 Unimplemented: Read as '0'

- bit 19 ADMA2: ADMA2 Support bit

- 1 = ADMA2 is supported

- 0 = ADMA2 is not supported

- bit 18 Unimplemented: Read as '0'

### bit 17-16 MBLEN<1:0>: Maximum Block Length bits

- 11 = Reserved

- 10 = 2048

- 01 = 1024

- 00 = 512

- bit 15-14 Unimplemented: Read as '0'

### bit 13-8 BASECLK<5:0>: Base Clock Frequency for SDCLK bits

bit 6 Unimplemented: Read as '0'

bit 7

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | r-0               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 22:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 |                   |                   |                   | —                 | _                 | _                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 |                   |                   | _                 | _                 |                   |                  | _                |

## REGISTER 41-1: DEVSIGN0/ADEVSIGN0: DEVICE SIGNATURE WORD 0 REGISTER

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31 Reserved: Write as '0'

bit 30-0 Reserved: Write as '1'

**Note:** The DEVSIGN1 through DEVSIGN3 and ADEVSIGN1 through ADEVSIGN3 registers are used for Quad Word programming operation when programming the DEVSIGN0/ADESIGN0 registers, and do not contain any valid information.

# REGISTER 41-2: DEVCP0/ADEVCP0: DEVICE CODE-PROTECT 0 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | r-1               | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | —                 | —                 | CP                | _                 | _                 | —                | _                |

| 22:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | _                 | —                 | —                 | -                 | —                 | _                 | —                | _                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | _                 | —                 | —                 | _                 | —                 | _                 | —                | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 |                   | _                 | _                 | _                 |                  | _                |

| Legend:           | r = Reserved bit | P = Programmable bit     | le bit             |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-29 Reserved: Write as '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-0 Reserved: Write as '1'

**Note:** The DEVCP1 through DEVCP3 and ADEVCP1 through ADEVCP3 registers are used for Quad Word programming operation when programming the DEVCP0/ADEVCP0 registers, and do not contain any valid information.

| DC CHA | ARACT | ERISTICS                                                                                                                                                                                                                                                                                                | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |       |                            |  |

|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------|--|

| Param. | Sym.  | Characteristic                                                                                                                                                                                                                                                                                          | Min.                                                                                                                                                                            | Тур. | Max. | Units | Conditions <sup>(1)</sup>  |  |

|        |       | Output High Voltage<br>I/O Pins<br>4x Sink Driver Pins -<br>RA0-RA3, RA9, RA10, RA14, RA15<br>RB0, RB4, RB6, RB7, RB10, RB11, RB12,<br>RB14<br>RC12-RC15<br>RD6, RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8, RF12<br>RG15<br>RH0, RH1, RH4-RH14<br>RJ0-RJ2, RJ8, RJ9, RJ11                            | 2.4                                                                                                                                                                             | _    | _    | V     | IOH ≥ -10 mA, VDDIO = 3.3\ |  |

| DO20   | Vон   | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pins -<br>RA4, RA5<br>RB2, RB3, RB5, RB8, RB9, RB13, RB14,<br>RB15<br>RC1-RC4<br>RD0-RD3, RD9, RD10, RD12, RD13<br>RE0-RE7<br>RF0, RF1, RF4, RF5, RF13<br>RG0, RG1, RG6, RG7, RG8, RG9<br>RH2, RH3, RH7, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7 | 2.4                                                                                                                                                                             | _    | _    | V     | IOH ≥ -15 mA, VDDIO = 3.3V |  |

|        |       | Output High Voltage<br>I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RD4, RD5<br>RG12-RG14                                                                                                                                                                                                       | 2.4                                                                                                                                                                             | _    | _    | V     | IOH ≥ -20 mA, VDDIO = 3.3\ |  |

# TABLE 44-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

# TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                                                                                 | Update Description                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25.0 "Parallel Master Port (PMP)"                                                                            | The All Resets value for bits 15:0 of the PMSTAT register in the Parallel Master Port Register Map was updated (see Table 25-1).                                                                                     |

| 26.0 "External Bus Interface (EBI)"                                                                          | The All Resets values were updated in the EBI Register Map (see Table 26-2).                                                                                                                                         |

| 29.0 "12-bit High-Speed<br>Successive Approximation<br>Register (SAR) Analog-to-<br>Digital Converter (ADC)" | The All Resets values for the ADCCON1 and ADCxTIME registers were updated<br>and the Virtual Addresses for the ADCxCFG, ADCSYSCFGx, and ADCDATAx<br>registers were updated in the ADC Register Map (see Table 29-1). |

| 34.0 "High/Low-Voltage Detect<br>(HLVD)"                                                                     | The chapter was renamed and the introduction was updated.                                                                                                                                                            |

|                                                                                                              | The HLVDCON register was updated (see Table 34-1 and Register 34-1).                                                                                                                                                 |

|                                                                                                              | High/Low-Voltage Detect (HLVD) Module Block Diagram was updated (see Figure 34-1)                                                                                                                                    |

| 36.0 "Graphics LCD (GLCD)<br>Controller"                                                                     | The Graphics LCD Controller Register Map was updated (see Table 36-1).                                                                                                                                               |

|                                                                                                              | These registers were updated:                                                                                                                                                                                        |

|                                                                                                              | <ul> <li>Register 36-2: "GLCDCLKCON: Graphics LCD Controller Clock Control<br/>Register"</li> </ul>                                                                                                                  |

|                                                                                                              | <ul> <li>Register 36-4: "GLCDRES: Graphics LCD Controller Resolution Register"</li> <li>Register 36-5: "GLCDFPORCH: Graphics LCD Controller Front Porch<br/>Register"</li> </ul>                                     |

|                                                                                                              | <ul> <li>Register 36-6: "GLCDBLANKING: Graphics LCD Controller Blanking<br/>Register"</li> </ul>                                                                                                                     |

|                                                                                                              | <ul> <li>Register 36-7: "GLCDBPORCH: Graphics LCD Controller Back Porch<br/>Register"</li> </ul>                                                                                                                     |

|                                                                                                              | • Register 36-8: "GLCDCURSOR: Graphics LCD Controller Cursor Register"                                                                                                                                               |

|                                                                                                              | <ul> <li>Register 36-10: "GLCDLxstart: graphics lcd controller layer 'x' start<br/>register ('x' = 0-2)"</li> </ul>                                                                                                  |

|                                                                                                              | <ul> <li>Register 36-11: "GLCDLxsize: graphics lcd controller layer 'x' size register<br/>('x' = 0-2)"</li> </ul>                                                                                                    |

|                                                                                                              | <ul> <li>Register 36-14: "GLCDLxres: graphics lcd controller layer 'x' resolution<br/>register ('x' = 0-2)"</li> </ul>                                                                                               |

| 37.0 "2-D Graphics<br>Processing Unit (GPU)"                                                                 | The introduction was updated.                                                                                                                                                                                        |

| 39.0 "Secure Digital Host<br>Controller (SDHC)"                                                              | The SDHC block diagram was updated (see Figure 39-1).                                                                                                                                                                |

|                                                                                                              | The SDHC Register Map was updated (see Table 39-1).                                                                                                                                                                  |

|                                                                                                              | The bit values for the CDSLVL bit in the SDHCSTAT1 register were updated (see Register 39-6).                                                                                                                        |

|                                                                                                              | The SDHCCAP register was updated (see Register 39-13).                                                                                                                                                               |

| 40.0 "Power-Saving Features"                                                                                 | 40.2.3 "Deep Sleep Mode" was updated.                                                                                                                                                                                |

|                                                                                                              | References to High-Voltage Detect were removed in the PMD Register Summary (Table 40-2) and the PMD Bits and Locations (Table 40-3).                                                                                 |

| 41.0 "Special Features"                                                                                      | The CFGCON2 register was updated (see Table 41-3 and Register 41-12).                                                                                                                                                |