Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 640K × 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 169-LFBGA                                                                                     |

| Supplier Device Package    | 169-LFBGA (11x11)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1064daa169-i-hf              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

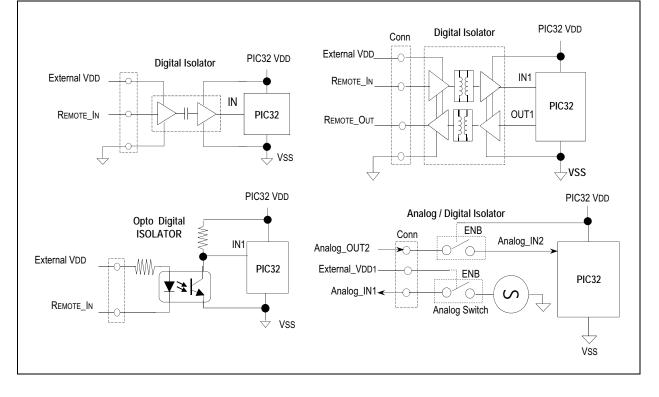

#### TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits | Inductive Coupling | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х                  |                     |               | _                     |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х                  | _                   | _             | —                     |

| ISO721                                              | _                  | Х                   | _             | —                     |

| LTV-829S (2 Channel)                                | _                  |                     | Х             | —                     |

| LTV-849S (4 Channel)                                | _                  |                     | Х             | —                     |

| FSA266 / NC7WB66                                    | —                  | —                   | _             | Х                     |

#### FIGURE 2-6:

## EXAMPLE DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

# 7.2 Interrupts

The PIC32MZ DA family uses variable offsets for vector spacing. This allows the interrupt vector spacing to be configured according to application needs. A unique interrupt vector offset can be set for each vector using its associated OFFx register.

# TABLE 7-2: INTERRUPT IRQ, VECTOR AND BIT LOCATION

For details on the Variable Offset feature, refer to **8.5.2** "Variable Offset" in Section 8. "Interrupt Controller" (DS60001108) of the "*PIC32 Family Reference Manual*".

Table 7-2 provides the Interrupt IRQ, vector and bit location information.

| In terms ( <b>0</b>             | XO20 Vester Name              | IRQ    | Maatan#           |          | Interru  | pt Bit Location | 1            | Persistent |

|---------------------------------|-------------------------------|--------|-------------------|----------|----------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | #      | Vector #          | Flag     | Enable   | Priority        | Sub-priority | Interrupt  |

|                                 | Highest                       | Natura | al Order Priority |          |          |                 |              |            |

| Core Timer Interrupt            | _CORE_TIMER_VECTOR            | 0      | OFF000<17:1>      | IFS0<0>  | IEC0<0>  | IPC0<4:2>       | IPC0<1:0>    | No         |

| Core Software Interrupt 0       | _CORE_SOFTWARE_0_VECTOR       | 1      | OFF001<17:1>      | IFS0<1>  | IEC0<1>  | IPC0<12:10>     | IPC0<9:8>    | No         |

| Core Software Interrupt 1       | _CORE_SOFTWARE_1_VECTOR       | 2      | OFF002<17:1>      | IFS0<2>  | IEC0<2>  | IPC0<20:18>     | IPC0<17:16>  | No         |

| External Interrupt 0            | _EXTERNAL_0_VECTOR            | 3      | OFF003<17:1>      | IFS0<3>  | IEC0<3>  | IPC0<28:26>     | IPC0<25:24>  | No         |

| Timer1                          | _TIMER_1_VECTOR               | 4      | OFF004<17:1>      | IFS0<4>  | IEC0<4>  | IPC1<4:2>       | IPC1<1:0>    | No         |

| Input Capture 1 Error           | _INPUT_CAPTURE_1_ERROR_VECTOR | 5      | OFF005<17:1>      | IFS0<5>  | IEC0<5>  | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| Input Capture 1                 | _INPUT_CAPTURE_1_VECTOR       | 6      | OFF006<17:1>      | IFS0<6>  | IEC0<6>  | IPC1<20:18>     | IPC1<17:16>  | Yes        |

| Output Compare 1                | _OUTPUT_COMPARE_1_VECTOR      | 7      | OFF007<17:1>      | IFS0<7>  | IEC0<7>  | IPC1<28:26>     | IPC1<25:24>  | No         |

| External Interrupt 1            | _EXTERNAL_1_VECTOR            | 8      | OFF008<17:1>      | IFS0<8>  | IEC0<8>  | IPC2<4:2>       | IPC2<1:0>    | No         |

| Timer2                          | _TIMER_2_VECTOR               | 9      | OFF009<17:1>      | IFS0<9>  | IEC0<9>  | IPC2<12:10>     | IPC2<9:8>    | No         |

| Input Capture 2 Error           | _INPUT_CAPTURE_2_ERROR_VECTOR | 10     | OFF010<17:1>      | IFS0<10> | IEC0<10> | IPC2<20:18>     | IPC2<17:16>  | Yes        |

| Input Capture 2                 | _INPUT_CAPTURE_2_VECTOR       | 11     | OFF011<17:1>      | IFS0<11> | IEC0<11> | IPC2<28:26>     | IPC2<25:24>  | Yes        |

| Output Compare 2                | _OUTPUT_COMPARE_2_VECTOR      | 12     | OFF012<17:1>      | IFS0<12> | IEC0<12> | IPC3<4:2>       | IPC3<1:0>    | No         |

| External Interrupt 2            | _EXTERNAL_2_VECTOR            | 13     | OFF013<17:1>      | IFS0<13> | IEC0<13> | IPC3<12:10>     | IPC3<9:8>    | No         |

| Timer3                          | _TIMER_3_VECTOR               | 14     | OFF014<17:1>      | IFS0<14> | IEC0<14> | IPC3<20:18>     | IPC3<17:16>  | No         |

| Input Capture 3 Error           | _INPUT_CAPTURE_3_ERROR_VECTOR | 15     | OFF015<17:1>      | IFS0<15> | IEC0<15> | IPC3<28:26>     | IPC3<25:24>  | Yes        |

| Input Capture 3                 | _INPUT_CAPTURE_3_VECTOR       | 16     | OFF016<17:1>      | IFS0<16> | IEC0<16> | IPC4<4:2>       | IPC4<1:0>    | Yes        |

| Output Compare 3                | _OUTPUT_COMPARE_3_VECTOR      | 17     | OFF017<17:1>      | IFS0<17> | IEC0<17> | IPC4<12:10>     | IPC4<9:8>    | No         |

| External Interrupt 3            | _EXTERNAL_3_VECTOR            | 18     | OFF018<17:1>      | IFS0<18> | IEC0<18> | IPC4<20:18>     | IPC4<17:16>  | No         |

| Timer4                          | _TIMER_4_VECTOR               | 19     | OFF019<17:1>      | IFS0<19> | IEC0<19> | IPC4<28:26>     | IPC4<25:24>  | No         |

| Input Capture 4 Error           | _INPUT_CAPTURE_4_ERROR_VECTOR | 20     | OFF020<17:1>      | IFS0<20> | IEC0<20> | IPC5<4:2>       | IPC5<1:0>    | Yes        |

| Input Capture 4                 | _INPUT_CAPTURE_4_VECTOR       | 21     | OFF021<17:1>      | IFS0<21> | IEC0<21> | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| Output Compare 4                | _OUTPUT_COMPARE_4_VECTOR      | 22     | OFF022<17:1>      | IFS0<22> | IEC0<22> | IPC5<20:18>     | IPC5<17:16>  | No         |

Note 1: Not all interrupt sources are available on all devices. See the Family Features tables (Table 1 through Table 2) for the list of available peripherals.

2: Upon Reset, the GLCD interrupt (both HSYNC and VSYNC) are persistent. However, through the IRQCON bit (GLCDINT<31>), the type of interrupt can be changed to non-persistent.

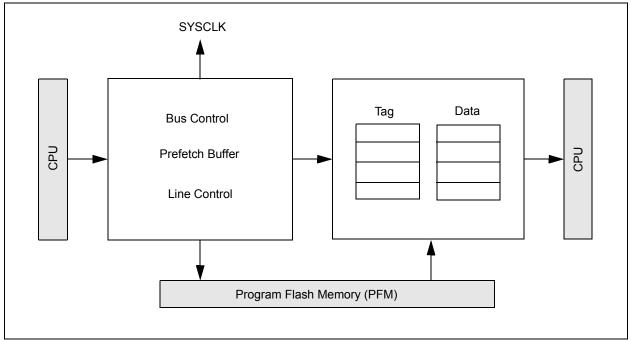

# 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Prefetch module is a performance enhancing module that is included in PIC32MZ DA family devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

## 9.1 Features

The Prefetch module includes the following key features:

- 4x16 byte fully-associative lines

- One line for CPU instructions

- One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- · Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

#### FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        |                   | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:           |                  |                                         |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

When CRCTYP (DCRCCON<5>) = 1 (CRC module is in IP Header mode):

Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<5>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        |                   | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<5>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<5>) = 0</u> (CRC module is in LFSR mode):

1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

|                    |                  | 1 1           |                     |                     |             |                |              |              |               |        | Bits            |      |         |      |       |         |        |       |            |

|--------------------|------------------|---------------|---------------------|---------------------|-------------|----------------|--------------|--------------|---------------|--------|-----------------|------|---------|------|-------|---------|--------|-------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range     | 31/15               | 30/14               | 29/13       | 28/12          | 27/11        | 26/10        | 25/9          | 24/8   | 23/7            | 22/6 | 21/5    | 20/4 | 19/3  | 18/2    | 17/1   | 16/0  | All Resets |

| 3248               | USB              | 31:16         |                     |                     |             |                |              |              |               | DMA    | ADDR<31:16      | >    |         |      |       |         |        |       | 0000       |

| 5240               | DMA5A            | 15:0          |                     |                     |             |                |              |              |               | DMA    | ADDR<15:0       | >    |         |      |       |         |        |       | 0000       |

| 324C               | USB              | 31:16         |                     |                     |             |                |              |              |               | DMAG   | COUNT<31:10     | 6>   |         |      |       |         |        |       | 0000       |

| 02.0               | DMA5N            | 15:0          |                     |                     |             |                |              |              |               |        |                 |      |         |      | 0000  |         |        |       |            |

| 3254               | USB              | 31:16         | _                   |                     |             | —              | -            | _            | _             | -      | _               | _    | —       | —    | _     |         | _      | _     | 0000       |

|                    | DMA6C            | 15:0          | —                   | —                   | —           | —              | —            | DMABRS       | STM<1:0>      | DMAERR |                 |      | EP<3:0> |      | DMAIE | DMAMODE | DMADIR | DMAEN | 0000       |

| 3258               | USB              | 31:16         |                     |                     |             |                |              |              |               |        | ADDR<31:16      |      |         |      |       |         |        |       | 0000       |

|                    | DMA6A            | 15:0          |                     |                     |             |                |              |              |               |        | ADDR<15:0>      |      |         |      |       |         |        |       | 0000       |

| 325C               | USB              | 31:16         |                     |                     |             |                |              |              |               |        | COUNT<31:10     |      |         |      |       |         |        |       | 0000       |

|                    | DMA6N            | 15:0          |                     |                     |             |                | 1            |              |               |        | COUNT<15:0      |      |         |      |       |         |        |       | 0000       |

| 3264               | USB              | 31:16         | _                   | -                   |             | -              | -            | —            | —             | -      | _               | —    |         | —    | -     | —       | —      | —     | 0000       |

|                    | DMA7C            | 15:0          | _                   | -                   | —           | _              | -            | DMABRS       | STM<1:0>      | DMAERR |                 |      | EP<3:0> |      | DMAIE | DMAMODE | DMADIR | DMAEN | _          |

| 3268               | USB<br>DMA7A     | 31:16         |                     | DMAADDR<31:16> 0000 |             |                |              |              |               |        |                 |      |         |      |       |         |        |       |            |

|                    |                  | 15:0          |                     | DMAADDR<15:0> 0000  |             |                |              |              |               |        |                 |      |         | _    |       |         |        |       |            |

| 326C               | USB<br>DMA7N     | 31:16         |                     |                     |             |                |              |              |               |        | COUNT<31:10     |      |         |      |       |         |        |       | 0000       |

|                    |                  | 15:0          |                     |                     | -           |                | 1            |              |               |        | COUNT<15:0      | >    |         | 1    |       | -       | 1      |       | 0000       |

| 3274               | USB<br>DMA8C     | 31:16         | _                   | _                   | -           | _              | _            |              | -             | -      | _               | —    | -       | _    |       | -       |        |       | 0000       |

|                    |                  | 15:0          | _                   | —                   | -           | —              | -            | DIMABRS      | STM<1:0>      | DMAERR | ADDR<31:16      |      | EP<3:0> |      | DMAIE | DMAMODE | DMADIR | DMAEN | 0000       |

| 3278               | USB<br>DMA8A     | 31:16<br>15:0 |                     |                     |             |                |              |              |               |        | ADDR<31:16      |      |         |      |       |         |        |       | 0000       |

|                    |                  | 31:16         |                     |                     |             |                |              |              |               |        | COUNT<31:10     |      |         |      |       |         |        |       | 0000       |

| 327C               | USB<br>DMA8N     | 15:0          |                     |                     |             |                |              |              |               |        | COUNT<31.10     |      |         |      |       |         |        |       | 0000       |

|                    |                  | 31:16         | _                   |                     | _           |                |              |              |               |        | COUNT<15.0      | _    | _       | I    | _     |         |        | _     | 0000       |

| 3304               | USB<br>E1RPC     | 15:0          | _                   |                     | _           | _              | _            |              | _             |        | —<br>KTCNT<15:0 |      | _       | _    | _     | _       | _      | _     | 0000       |

|                    |                  | 31:16         | _                   |                     |             |                |              |              |               | _      |                 | _    | _       | _    | _     |         |        |       | 0000       |

| 3308               | USB<br>E2RPC     | 15:0          |                     |                     |             |                |              |              |               |        | KTCNT<15:0      |      |         |      |       |         |        |       | 0000       |

|                    | LICD             | 31:16         | _                   | _                   | _           | _              | _            | _            | _             | _      | _               | _    | _       | _    | _     | _       | _      | _     | 0000       |

| 330C               | E3RPC            | 15:0          |                     |                     |             |                |              |              |               |        | KTCNT<15:0      |      |         |      |       |         |        |       | 0000       |

|                    | USB              | 31:16         | _                   | _                   | _           | _              | _            | _            | _             |        | —               | _    | _       | _    | _     | _       | _      | _     | 0000       |

| 3310               | E4RPC            | 15:0          |                     |                     |             |                |              |              |               |        |                 |      | 0000    |      |       |         |        |       |            |

|                    | USB              | 31:16         |                     |                     |             |                |              |              |               |        |                 | 0000 |         |      |       |         |        |       |            |

| 3314               | E5RPC            | 15:0          | 15:0 RQPKTCNT<15:0> |                     |             |                |              |              |               |        |                 |      | 0000    |      |       |         |        |       |            |

|                    | USB              | 31:16         | _                   | _                   | _           | _              | _            | _            | _             | _      | _               | _    | _       | _    | _     | _       | _      | _     | 0000       |

| 3318               | E6RPC            | 15:0          | RQPKTCNT<15:0> 0000 |                     |             |                |              |              |               |        |                 |      |         |      |       |         |        |       |            |

|                    | USB              | 31:16         | 16                  |                     |             |                |              |              |               | _      |                 |      |         |      |       |         |        |       |            |

| 331C               | E7RPC            | 15:0          |                     | RQPKTCNT<15:0> 0000 |             |                |              |              |               |        |                 |      |         |      |       |         |        |       |            |

| Leger              | nd: ×            | = unkno       | wn value on         | Reset; — = uni      | implemented | d. read as '0' | . Reset valu | es are showr | n in hexadeci | mal.   |                 |      |         |      |       |         |        |       |            |

Note

1: 2: 3: 4: Device mode.

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

## TABLE 16-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |       |       |       |       |       |       |      | Bi    | ts     |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|-------|--------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

| 4A00                        | OC6CON                          | 31:16         | _     | -     | —     | -     | -     | _     | -    | _     | _      | l    | —    | —     | —      |      | —        | _    | 0000         |

| 17 10 0                     | 000001                          | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —      | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 4A10                        | OC6R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC6R  | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 4A20                        | OC6RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC6RS | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 4000                        | OC7CON                          | 31:16         | _     | -     | _     | -     |       | _     |      | -     | _      | -    | —    | _     | _      |      | —        |      | 0000         |

| +000                        | 007000                          | 15:0          | ON    | _     | SIDL  | _     | —     | —     | —    | —     | —      | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 4C10                        | OC7R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC7R  | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 4C20                        | OC7RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC7RS | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 4500                        | 00000                           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | —    | —     | _      | _    | —        | _    | 0000         |

| 4E00                        | OC8CON                          | 15:0          | ON    | _     | SIDL  | _     | _     | —     | —    | _     | _      | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 4E10                        | OC8R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC8R  | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 4E20                        | OC8RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC8RS | <31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 5000                        | 00000                           | 31:16         | _     | _     | _     | —     | _     | —     | —    | —     | _      | _    | —    | —     | _      | _    | —        | _    | 0000         |

| 5000                        | OC9CON                          | 15:0          | ON    |       | SIDL  |       |       | _     |      |       | _      |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 5010                        | OC9R                            | 31:16         |       |       |       |       |       |       |      | OC9R  | 31.0>  |      |      |       |        |      |          |      | xxxx         |

| 5010                        | JOBIN                           | 15:0          |       |       |       |       |       |       |      | COSK  | -01.02 |      |      |       |        |      |          |      | xxxx         |

| 5020                        | OC9RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC9RS | <31:0> |      |      |       |        |      |          |      | xxxx         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | -                 | —                 | —                 |                  | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | —                 | _                 | _                | _                |

| 45.0         | R-0, HS, HC       | R-0, HS, HC       | R/C-0, HS, HC     | U-0               | U-0               | R/C-0, HS         | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ACKSTAT           | TRSTAT            | ACKTIM            | _                 | —                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS, SC     | R/C-0, HS, SC     | R-0, HS, HC       | R/C-0, HS, HC     | R/C-0, HS, HC     | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

# REGISTER 23-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared    | SC = Software Cleared |

|-------------------|-------------------|--------------------------|-----------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'            |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | C = Clearable bit     |

## bit 31-16 Unimplemented: Read as '0'

| 51-10     | oninplemented. Read as 0                                                                                                                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                      |

|           | 1 = NACK received from slave                                                                                                                                                                     |

|           | 0 = ACK received from slave                                                                                                                                                                      |

|           | Hardware set or clear at end of slave Acknowledge.                                                                                                                                               |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                          |

|           | 1 = Master transmit is in progress (8 bits + ACK)                                                                                                                                                |

|           | 0 = Master transmit is not in progress                                                                                                                                                           |

|           | Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.                                                                                                    |

| bit 13    | ACKTIM: Acknowledge Time Status bit (Valid in I <sup>2</sup> C Slave mode only)                                                                                                                  |

|           | <ul> <li>1 = I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8th falling edge of SCL clock</li> <li>0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCL clock</li> </ul> |

| bit 12-11 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                                             |

|           | 1 = A bus collision has been detected during a master operation                                                                                                                                  |

|           | 0 = No collision<br>Hardware set at detection of bus collision.                                                                                                                                  |

|           |                                                                                                                                                                                                  |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                                                  |

|           | 1 = General call address was received                                                                                                                                                            |

|           | <ul> <li>0 = General call address was not received</li> <li>Hardware set when address matches general call address. Hardware clear at Stop detection.</li> </ul>                                 |

| bit 8     | ADD10: 10-bit Address Status bit                                                                                                                                                                 |

|           | 1 = 10-bit address was matched                                                                                                                                                                   |

|           | 0 = 10-bit address was not matched                                                                                                                                                               |

|           | Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                                                   |

| bit 7     | IWCOL: Write Collision Detect bit                                                                                                                                                                |

|           | 1 = An attempt to write the I2CxTRN register failed because the $I^2C$ module is busy                                                                                                            |

|           | 0 = No collision                                                                                                                                                                                 |

|           | Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).                                                                                                                 |

| bit 6     | I2COV: Receive Overflow Flag bit                                                                                                                                                                 |

|           | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                                               |

|           | Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                    |

|           |                                                                                                                                                                                                  |

|           |                                                                                                                                                                                                  |

|           |                                                                                                                                                                                                  |

## FIGURE 27-9: FORMAT OF BD\_MSG\_LEN

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   | MSG_LENGTH<31:24> |                   |                   |                   |                   |                  |                  |

| 23-16        |                   |                   |                   | MSG_LENG          | TH<23:16>         |                   |                  |                  |

| 15-8         |                   | MSG_LENGTH<15:8>  |                   |                   |                   |                   |                  |                  |

| 7-0          |                   | MSG_LENGTH<7:0>   |                   |                   |                   |                   |                  |                  |

bit 31-0 MSG\_LENGTH: Total Message Length

Total message length for the hash and HMAC algorithms in bytes. Total number of crypto bytes in case of GCM algorithm (LEN-C).

## FIGURE 27-10: FORMAT OF BD\_ENC\_OFF

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   | ENCR_OFFSET<31:24> |                   |                   |                   |                   |                  |                  |

| 23-16        |                   |                    | ļ                 | ENCR_OFF          | SET<23:16>        |                   |                  |                  |

| 15-8         |                   | ENCR_OFFSET<15:8>  |                   |                   |                   |                   |                  |                  |

| 7-0          |                   | ENCR_OFFSET<7:0>   |                   |                   |                   |                   |                  |                  |

#### bit 31-0 ENCR\_OFFSET: Encryption Offset

Encryption offset for the multi-task test cases (both encryption and authentication). The number of AAD bytes in the case of GCM algorithm (LEN-A).

# 29.0 12-BIT HIGH-SPEED SUCCESSIVE APPROXIMATION REGISTER (SAR) ANALOG-TO-DIGITAL CONVERTER (ADC)

This data sheet summarizes the features Note: of the PIC32MZ DA family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-bit High-Speed Section 22. Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" (DS60001344) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The 12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) includes the following features:

- 12-bit resolution

- Six ADC modules with dedicated Sample and Hold (S&H) circuits

- Two dedicated ADC modules can be combined in Turbo mode to provide double conversion rate (clock sources for combined ADCs must be synchronous)

- Up to 45 analog input sources, in addition to the internal CTMU, VBAT, internal voltage reference and internal temperature sensor

- Single-ended and/or differential inputs

- Can operate during Sleep mode

- Supports touch sense applications

- · Six digital comparators

- · Six digital filters supporting two modes:

- Oversampling mode

- Averaging mode

- 16-word FIFO on ADC0 through ADC4 for increased throughput

- Early interrupt generation resulting in faster processing of converted data

- Designed for motor control, power conversion, and general purpose applications

- · Operation during Sleep and Idle modes

A simplified block diagram of the ADC module is illustrated in Figure 29-1.

The 12-bit HS SAR ADC has up to five dedicated ADC modules (ADC0-ADC4) and one shared ADC module (ADC7). The dedicated ADC modules use a single input (or its alternate) and are intended for high-speed and precise sampling of time-sensitive or transient inputs. The the shared ADC module incorporates a multiplexer on the input to facilitate a larger group of inputs, with slower sampling, and provides flexible automated scanning option through the input scan logic.

For each ADC module, the analog inputs are connected to the S&H capacitor. The clock, sampling time, and output data resolution for each ADC module can be set independently. The ADC module performs the conversion of the input analog signal based on the configurations set in the registers. When conversion is complete, the final result is stored in the result buffer for the specific analog input and is passed to the digital filter and digital comparator if configured to use data from this particular sample. Input to ADCx mapping is illustrated in Figure 29-2.

## 29.1 Activation Sequence

**Step 1:** Initialize the ADC calibration values by copying them from the factory programmed DEVADCx Flash locations starting at 0xBFC45000 into the ADCxCFG registers starting at 0xBF887D00. Then, configure the AICPMPEN bit (ADCCON1<12> and the IOANCPEN bit (CFGCON<7>) = 1 if and only if VDD is less than 2.5V. The default is '0', which assumes VDD is greater than or equal to 2.5V.

**Step 2:** The user writes all the essential ADC configuration SFRs including the ADC control clock and all ADC core clocks setup:

- ADCCON1, keeping the ON bit = 0

- ADCCON2, especially paying attention to ADC-DIV<6:0> and SAMC<9:0>

- ADCANCON, keeping all analog enables ANENx bit = 0, WKUPCLKCNT bit = 0xA

- ADCCON3, keeping all DIGEN5x = 0, especially paying attention to ADCSEL<1:0>, CONCLKDIV <5:0>, and VREFSEL<2:0>

- ADCxTIME, ADCDIVx<6:0>, and SAMCx<9:0>

- ADCTRGMODE, ADCIMCONX, ADCTRGSNS, ADCCSSX, ADCGIRQENX, ADCTRGX, ADC-BASE

- · Comparators, filters, and so on

**Step 3:** The user sets the ANENx bit to '1' for the ADC SAR Cores needed (which internally in the ADC module enables the control clock to generate by division the core clocks for the desired ADC SAR Cores, which in turn enables the bias circuitry for these ADC SAR Cores).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 31:24        | —                 |                   | -                 | —                 | —                 | —                 | SH4AL            | .T<1:0>          |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | SH3ALT<1:0>       |                   | SH2ALT<1:0>       |                   | SH1ALT<1:0>       |                   | SH0ALT<1:0>      |                  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | STRGEN4           | STRGEN3           | STRGEN2           | STRGEN1          | STRGEN0          |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   | _                 | SSAMPEN4          | SSAMPEN3          | SSAMPEN2          | SSAMPEN1         | SSAMPEN0         |

#### REGISTER 29-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-26 Unimplemented: Read as ' '

bit 25-24 SH4ALT<1:0>: ADC4 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN49

- 00 **= AN4**

bit 23-22 SH3ALT<1:0>: ADC3 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN48

- 00 **= AN3**

bit 21-20 SH2ALT<1:0>: ADC2 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN47

- 00 **= AN2**

#### bit 19-18 SH1ALT<1:0>: ADC1 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN46

- 00 **= AN1**

bit 17-16 SH0ALT<1:0>: ADC0 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 **= AN45**

- 00 **= AN0**

- bit 15-13 Unimplemented: Read as ' '

bit 12 **STRGEN4:** ADC4 Presynchronized Triggers bit 1 = ADC4 uses presynchronized triggers 0 = ADC4 does not use presynchronized triggers

- bit 11 STRGEN3: ADC3 Presynchronized Triggers bit 1 = ADC3 uses presynchronized triggers 0 = ADC3 does not use presynchronized triggers

- bit 10 STRGEN2: ADC2 Presynchronized Triggers bit

- 1 = ADC2 uses presynchronized triggers

- 0 = ADC2 does not use presynchronized triggers

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL <sup>-</sup> | 7<1:0>            |                   | F                 | SEL7<4:0>         |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            |                   | F                 | SEL5<4:0>         |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | FLTEN4            | MSEL              | 4<1:0>            |                   | F                 | SEL4<4:0>         |                  |                  |

## REGISTER 30-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| -n = valu  | e at POR I = Bit is set                                                        | 0 = Bit is cleared           | x = Bit is unknown                 |

|------------|--------------------------------------------------------------------------------|------------------------------|------------------------------------|

|            |                                                                                |                              |                                    |

| bit 31     | FLTEN7: Filter 7 Enable bit                                                    |                              |                                    |

|            | 1 = Filter is enabled                                                          |                              |                                    |

|            | 0 = Filter is disabled                                                         |                              |                                    |

| bit 30-29  | MSEL7<1:0>: Filter 7 Mask Select bits                                          | S                            |                                    |

|            | 11 = Acceptance Mask 3 selected                                                |                              |                                    |

|            | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected             |                              |                                    |

|            | 00 = Acceptance Mask 0 selected                                                |                              |                                    |

| bit 28-24  | FSEL7<4:0>: FIFO Selection bits                                                |                              |                                    |

|            | 11111 = Message matching filter is st                                          | ored in FIFO buffer 31       |                                    |

|            | 11110 = Message matching filter is st                                          | ored in FIFO buffer 30       |                                    |

|            | •                                                                              |                              |                                    |

|            | •                                                                              |                              |                                    |

|            | •                                                                              |                              |                                    |

|            | 00001 = Message matching filter is st                                          |                              |                                    |

|            | 00000 = Message matching filter is st                                          | ored in FIFO buffer 0        |                                    |

| bit 23     | FLTEN6: Filter 6 Enable bit                                                    |                              |                                    |

|            | <ol> <li>Filter is enabled</li> <li>Filter is disabled</li> </ol>              |                              |                                    |

| hit 22-21  | <b>MSEL6&lt;1:0&gt;:</b> Filter 6 Mask Select bit                              | e                            |                                    |

| 011 22-2 1 | 11 = Acceptance Mask 3 selected                                                | 5                            |                                    |

|            | 10 = Acceptance Mask 2 selected                                                |                              |                                    |

|            | 01 = Acceptance Mask 1 selected                                                |                              |                                    |

|            | 00 = Acceptance Mask 0 selected                                                |                              |                                    |

| bit 20-16  | FSEL6<4:0>: FIFO Selection bits                                                |                              |                                    |

|            | 11111 = Message matching filter is st                                          |                              |                                    |

|            | 11110 = Message matching filter is st                                          | ored in FIFO buffer 30       |                                    |

|            | •                                                                              |                              |                                    |

|            | •                                                                              |                              |                                    |

|            | • • • • • • • • • • • • • • • • • • •                                          | orod in EIEO huffor 1        |                                    |

|            | 00001 = Message matching filter is st<br>00000 = Message matching filter is st |                              |                                    |

|            |                                                                                |                              |                                    |

| Note:      | The bits in this register can only be m                                        | odified if the corresponding | filter enable (FLTENn) bit is '0'. |

|            |                                                                                |                              |                                    |

| REGISTER 31-16: | ETHRXOVFLOW: ETHERNET CONTROLLER RECEIVE OVERFLOW STATISTICS |

|-----------------|--------------------------------------------------------------|

|                 | REGISTER                                                     |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0      |                   |                   |                   | RXOVFLW           | CNT<15:8>         |                   |                  |                  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | RXOVFLW           | /CNT<7:0>         |                   |                  |                  |

# Legend:

| Legena.           |                  |                                         |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RXOVFLWCNT<15:0>:** Dropped Receive Frames Count bits Increment counter for frames accepted by the RX filter and subsequently dropped due to internal receive error (RXFIFO overrun). This event also sets the RXOVFLW bit (ETHIRQ<0>) interrupt flag.

Note 1: This register is only used for RX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

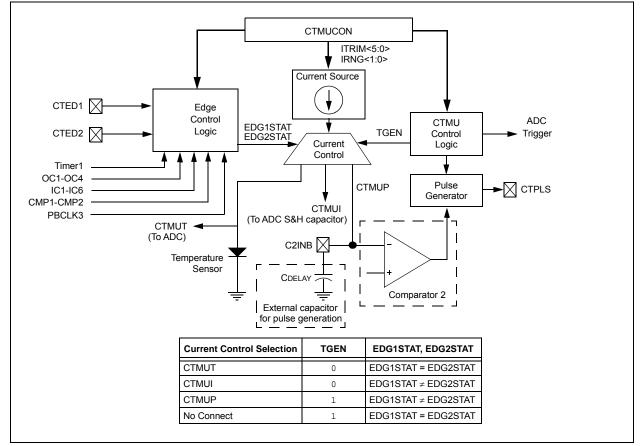

# 35.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

FIGURE 35-1: CTMU BLOCK DIAGRAM

The CTMU module includes the following key features:

- Up to 35 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 35-1.

#### REGISTER 36-3: GLCDBGCOLOR: GRAPHICS LCD CONTROLLER BACKGROUND COLOR REGISTER

|              |                   | LOIGIEI           |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | RED<              | 7:0>              |                   |                  |                  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | GREEN<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | BLUE<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | ALPHA             | <7:0>             |                   |                  |                  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 RED<7:0>: Color Red as Background bits

These bits specify that the color red is to be used as the background color.

- bit 23-16 **GREEN<7:0>:** Color Green as Background bits These bits specify that the color green is to be used as the background color.

- bit 15-8 **BLUE<7:0>:** Color Blue as Background bits These bits specify that the color blue is to be used as the background color.

- bit 7-0 **ALPHA<7:0>:** Color Alpha as Background bits These bits specify that the color alpha is to be used as the background color.

- Note: If all of the bits in this register are set (RED, GREEN, BLUE and ALPHA), RGBA color is used as the background.

#### REGISTER 36-4: GLCDRES: GRAPHICS LCD CONTROLLER RESOLUTION REGISTER

|              |                                    |                   |                   |                   | -                 |                   |                  |                  |  |  |  |

|--------------|------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | U-0                                | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | <sup>4</sup> — — — — — — RESX<10:8 |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RESX<7:0>                          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                              | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |  |  |  |

| 15:8         | _                                  | —                 | —                 | _                 | —                 | RESY<10:8>        |                  |                  |  |  |  |

| 7:0          | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | RESY<7:0>                          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 **RESX<10:0>:** X Dimension Pixel Resolution bits

These bits specify the pixel resolution for the X dimension.

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **RESY<10:0>:** Y Dimension Pixel Resolution bits These bits specify the pixel resolution for the Y dimension.

# REGISTER 36-17: GLCDCLUTx: GRAPHICS LCD CONTROLLER GLOBAL COLOR LOOKUP TABLE REGISTER x ('x'=0-255)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | -                 | —                | _                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | RED<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | GREEN<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   | BLUE<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |   |

|-------------------|------------------|------------------------|--------------------|---|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown | l |

bit 31-24 Unimplemented: Read as '0'

bit 23-16 **RED<7:0>:** Global Color Lookup Table Red Component bits

bit 15-8 GREEN<7:0>: Global Color Lookup Table Green Component bits

bit 7-0 BLUE<7:0>: Global Color Lookup Table Blue Component bits

# TABLE 38-1: DDR SDRAM CONTROLLER REGISTER SUMMARY (CONTINUED)

|                             | DLE 30-1.        |           |       |              |              |               |          | •••            |              | Bi             |          |          |               |               |                |               |               |               |            |

|-----------------------------|------------------|-----------|-------|--------------|--------------|---------------|----------|----------------|--------------|----------------|----------|----------|---------------|---------------|----------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14        | 29/13        | 28/12         | 27/11    | 26/10          | 25/9         | 24/8           | 23/7     | 22/6     | 21/5          | 20/4          | 19/3           | 18/2          | 17/1          | 16/0          | All Resets |

|                             | DDR              | 31:16     | _     |              | -            | -             | _        |                | -            | _              | _        | -        | -             | -             |                | WAIT          | <8:5>         |               | 0000       |

| 80E8                        | DDR<br>CMD210    | 15:0      |       |              | WAIT<4:0>    |               |          | BNK            | ADDRCMD      | <2:0>          |          |          |               | MDADDRH       | ICMD<7:0>      |               |               |               | 0000       |

| 80EC                        | DDR              | 31:16     | _     | _            | _            | _             | _        | _              | —            | —              | _        | —        | _             | _             |                | WAIT          | <8:5>         |               | 0000       |

| OUEC                        | CMD211           | 15:0      |       |              | WAIT<4:0>    |               |          | BNK            | ADDRCMD      | <2:0>          |          |          |               | MDADDRH       | ICMD<7:0>      |               |               |               | 0000       |

| 80F0                        | DDR              | 31:16     | _     | -            | -            | -             | —        | -              | -            | —              | _        | -        | -             | -             |                | WAIT          | <8:5>         |               | 0000       |

| 001 0                       | CMD212           | 15:0      |       |              | WAIT<4:0>    |               |          | BNK            | ADDRCMD      | <2:0>          |          |          |               | MDADDRH       | ICMD<7:0>      |               |               |               | 0000       |

| 80F4                        | DDR              | 31:16     | —     | —            | _            | _             |          | _              | _            | —              | —        | —        | _             | _             |                | WAIT          | <8:5>         |               | 0000       |

| 001 4                       | CMD213           | 15:0      |       |              | WAIT<4:0>    |               |          | BNK            | ADDRCMD      | <2:0>          |          |          |               | MDADDRH       | ICMD<7:0>      |               |               |               | 0000       |